Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | HC08                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 8MHz                                                      |

| Connectivity               | -                                                         |

| Peripherals                | LVD, POR, PWM                                             |

| Number of I/O              | 13                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 128 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 6x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | 16-PDIP                                                   |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908qy4ampe |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MC68HC908QY4A MC68HC908QT4A MC68HC908QY2A MC68HC908QT2A MC68HC908QY1A MC68HC908QT1A

**Data Sheet**

M68HC08 Microcontrollers

MC68HC908QY4A Rev. 3 03/2010

freescale.com

**Table of Contents**

# Chapter 16 Electrical Specifications

| Introduction                             | 155                        |

|------------------------------------------|----------------------------|

| Absolute Maximum Ratings                 | 155                        |

| Functional Operating Range               | 156                        |

| Thermal Characteristics                  | 156                        |

| 5-V DC Electrical Characteristics        | 157                        |

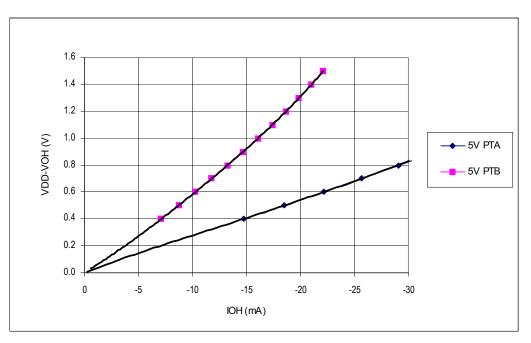

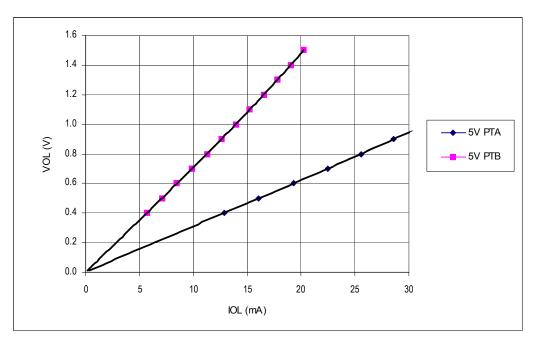

| Typical 5-V Output Drive Characteristics | 158                        |

| 5-V Control Timing                       | 159                        |

| 3-V DC Electrical Characteristics        | 160                        |

| Typical 3-V Output Drive Characteristics | 161                        |

| 3-V Control Timing                       | 162                        |

| Oscillator Characteristics               | 163                        |

| Supply Current Characteristics           | 165                        |

| ADC10 Characteristics.                   | 167                        |

| Timer Interface Module Characteristics   | 169                        |

| Memory Characteristics                   | 170                        |

|                                          | Oscillator Characteristics |

### Chapter 17

### Ordering Information and Mechanical Specifications

| 17.1   | Introduction                                            | 171 |

|--------|---------------------------------------------------------|-----|

| 17.2   | Ordering Information                                    | 171 |

| 17.3   | Orderable Part Numbering System                         | 172 |

|        | Consumer and Industrial Orderable Part Numbering System |     |

| 17.3.2 | Automotive Orderable Part Number System                 | 172 |

| 17.4   | Mechanical Drawings                                     | 172 |

# Appendix A 908QTA/QYxA Conversion Guidelines

| A.1     | Introduction                                     | 1 |

|---------|--------------------------------------------------|---|

| A.2     | Benefits of the Enhanced QYxA 19                 | 1 |

| A.2.1   | New Analog-to-Digital Converter Module (ADC) 19  | 1 |

| A.2.1.1 | Registers Affected                               | 2 |

| A.2.2   | Enhanced Oscillator Module (OSC) 19              | 3 |

| A.2.2.1 | Registers Affected                               | 3 |

| A.2.3   | Improved Auto Wakeup Module (AWU) 19             | 4 |

| A.2.3.1 | Registers Affected                               | 4 |

| A.2.4   | New Power-on Reset Module (POR) 19               | 4 |

| A.2.5   | Keyboard Interface Module (KBI) Functionality 19 |   |

| A.2.5.1 | Registers Affected                               | 5 |

| A.2.6   | On-Chip Routine Enhancements 19                  | 5 |

| A.3     | Conversion Considerations 19                     | 6 |

| A.4     | Code Changes Checklist                           | 6 |

| A.5     | Development Tools                                | 7 |

| A.6     | Differences in Packaging 19                      | 7 |

### **Direct Page Registers**

| Addr.                 | Register Name                                           |                           | Bit 7                                                                                                                                               | 6     | 5     | 4         | 3          | 2     | 1     | Bit 0                                        |

|-----------------------|---------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------|------------|-------|-------|----------------------------------------------|

|                       | LVI Status Register                                     | Read:                     | LVIOUT                                                                                                                                              | 0     | 0     | 0         | 0          | 0     | 0     | R                                            |

| \$FE0C                | (LVISR)                                                 | Write:                    |                                                                                                                                                     |       |       |           |            |       |       |                                              |

|                       | See page 91.                                            | Reset:                    | 0                                                                                                                                                   | 0     | 0     | 0         | 0          | 0     | 0     | 0                                            |

| \$FE0D<br>↓<br>\$FE0F | Reserved                                                |                           |                                                                                                                                                     |       |       |           |            |       |       |                                              |

| \$FFBE                | FLASH Block Protect<br>Register (FLBPR)<br>See page 34. | Read:<br>Write:           | BPR7                                                                                                                                                | BPR6  | BPR5  | BPR4      | BPR3       | BPR2  | BPR1  | BPR0                                         |

|                       | See paye 34.                                            | Reset:                    |                                                                                                                                                     |       |       | Unaffecte | d by reset |       |       |                                              |

| \$FFBF                | Reserved                                                |                           |                                                                                                                                                     |       |       |           |            |       |       |                                              |

|                       |                                                         | г                         |                                                                                                                                                     |       | [     | [         | [          | 1     | 1     | ,                                            |

| \$FFC0                | Internal Oscillator Trim<br>(Factory Programmed         | Read:<br>Write:           | TRIM7                                                                                                                                               | TRIM6 | TRIM5 | TRIM4     | TRIM3      | TRIM2 | TRIM1 | TRIM0                                        |

|                       | VDD = 3.0 V)                                            | Reset:                    |                                                                                                                                                     |       |       | Unaffecte | d by reset |       |       | <u>.                                    </u> |

| \$FFC1                | Internal Oscillator Trim<br>(Factory Programmed         | Read:<br>Write:           | TRIM7                                                                                                                                               | TRIM6 | TRIM5 | TRIM4     | TRIM3      | TRIM2 | TRIM1 | TRIM0                                        |

|                       | VDD = 5.0 V)                                            | Reset:                    |                                                                                                                                                     |       |       | Unaffecte | d by reset |       |       | L]                                           |

| \$FFFF                | COP Control Register<br>(COPCTL)<br>See page 63.        | Read:<br>Write:<br>Reset: | LOW BYTE OF RESET VECTOR     WRITING CLEARS COP COUNTER (ANY VALUE)     Unaffected by reset     = Unimplemented   R     = Reserved   U = Unaffected |       |       |           |            |       |       |                                              |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 5)

break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

### 3.7 I/O Signals

The ADC10 module shares its pins with general-purpose input/output (I/O) port pins. See Figure 3-1 for port location of these shared pins. The ADC10 on this MCU uses  $V_{DD}$  and  $V_{SS}$  as its supply and reference pins. This MCU does not have an external trigger source.

### 3.7.1 ADC10 Analog Power Pin (V<sub>DDA</sub>)

The ADC10 analog portion uses  $V_{DDA}$  as its power pin. In some packages,  $V_{DDA}$  is connected internally to  $V_{DD}$ . If externally available, connect the  $V_{DDA}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDA}$  for good results.

NOTE

If externally available, route  $V_{DDA}$  carefully for maximum noise immunity and place bypass capacitors as near as possible to the package.

### 3.7.2 ADC10 Analog Ground Pin (V<sub>SSA</sub>)

The ADC10 analog portion uses  $V_{SSA}$  as its ground pin. In some packages,  $V_{SSA}$  is connected internally to  $V_{SS}$ . If externally available, connect the  $V_{SSA}$  pin to the same voltage potential as  $V_{SS}$ .

In cases where separate power supplies are used for analog and digital power, the ground connection between these supplies should be at the  $V_{SSA}$  pin. This should be the only ground connection between these supplies if possible. The  $V_{SSA}$  pin makes a good single point ground location.

### 3.7.3 ADC10 Voltage Reference High Pin (V<sub>REFH</sub>)

$V_{REFH}$  is the power supply for setting the high-reference voltage for the converter. In some packages,  $V_{REFH}$  is connected internally to  $V_{DDA}$ . If externally available,  $V_{REFH}$  may be connected to the same potential as  $V_{DDA}$ , or may be driven by an external source that is between the minimum  $V_{DDA}$  spec and the  $V_{DDA}$  potential ( $V_{REFH}$  must never exceed  $V_{DDA}$ ).

### NOTE

Route  $V_{REFH}$  carefully for maximum noise immunity and place bypass capacitors as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the V<sub>REFH</sub> and V<sub>REFL</sub> loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between V<sub>REFH</sub> and V<sub>REFL</sub> and must be placed as close as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

### 3.7.4 ADC10 Voltage Reference Low Pin (V<sub>REFL</sub>)

$V_{REFL}$  is the power supply for setting the low-reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSA}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSA}$ . There will be a brief current associated with  $V_{REFL}$  when the sampling capacitor is

**Configuration Register (CONFIG)**

### Chapter 7 Central Processor Unit (CPU)

### 7.1 Introduction

The M68HC08 CPU (central processor unit) is an enhanced and fully object-code-compatible version of the M68HC05 CPU. The *CPU08 Reference Manual* (document order number CPU08RM/AD) contains a description of the CPU instruction set, addressing modes, and architecture.

### 7.2 Features

Features of the CPU include:

- Object code fully upward-compatible with M68HC05 Family

- 16-bit stack pointer with stack manipulation instructions

- 16-bit index register with x-register manipulation instructions

- 8-MHz CPU internal bus frequency

- 64-Kbyte program/data memory space

- 16 addressing modes

- Memory-to-memory data moves without using accumulator

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- Enhanced binary-coded decimal (BCD) data handling

- Modular architecture with expandable internal bus definition for extension of addressing range beyond 64 Kbytes

- Low-power stop and wait modes

### 7.3 CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

**Central Processor Unit (CPU)**

| Source                                                                                          | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   | Effect<br>on CCR |    |   |    | Address<br>Mode                                     | Opcode                                           | Operand                                         | es                                   |

|-------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------------------|----|---|----|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                            | operation                        | Becomption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | v | Н | I                | Ν  | z | С  | Add<br>Mod                                          | Opc                                              | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR opr,X<br>CLR X<br>CLR opr,SP                | Clear                            | $\begin{array}{c} M \leftarrow \$00 \\ A \leftarrow \$00 \\ X \leftarrow \$00 \\ H \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \end{array}$                                                                                                                                                                                                                                                                                                                                           | 0 | _ | _                | 0  | 1 | _  | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F                 | dd<br>ff<br>ff                                  | 3<br>1<br>1<br>3<br>2<br>4           |

| CMP #opr<br>CMP opr<br>CMP opr,<br>CMP opr,X<br>CMP opr,X<br>CMP ,X<br>CMP opr,SP<br>CMP opr,SP | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t | _ | _                | ţ  | ţ | ţ  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>E1<br>F1<br>9EE1<br>9ED1       | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                    | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                                                                           | 0 | _ | _                | ţ  | ţ | 1  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

| CPHX #opr<br>CPHX opr                                                                           | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ţ | - | -                | \$ | ţ | ţ  | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3<br>4                               |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX ,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ţ | _ | _                | ţ  | ţ | ţ  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| DAA                                                                                             | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U | - | -                | 1  | 1 | \$ | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel       | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 3 + \mathit{rel} ? (\mathit{result}) \neq 0 \\ PC \leftarrow (PC) + 4 + \mathit{rel} ? (\mathit{result}) \neq 0 \end{array}$ | _ | _ | _                | _  | _ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 5<br>3<br>3<br>5<br>4<br>6           |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                    | Decrement                        | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                   | ţ | - | _                | ţ  | ţ | -  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

| DIV                                                                                             | Divide                           | $A \leftarrow (H:A)/(X)$<br>H $\leftarrow$ Remainder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - | - | -                | -  | t | ţ  | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR ,X<br>EOR opr,SP<br>EOR opr,SP  | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 | _ | _                | ţ  | ţ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2 3 4 4 3 2 4 5                      |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                    | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                   | ţ | _ | _                | ţ  | ţ | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

### External Interrupt (IRQ)

### 8.4 Interrupts

The following IRQ source can generate interrupt requests:

• Interrupt flag (IRQF) — The IRQF bit is set when the IRQ pin is asserted based on the IRQ mode. The IRQ interrupt mask bit, IMASK, is used to enable or disable IRQ interrupt requests.

### 8.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 8.5.1 Wait Mode

The IRQ module remains active in wait mode. Clearing IMASK in INTSCR enables IRQ interrupt requests to bring the MCU out of wait mode.

### 8.5.2 Stop Mode

The IRQ module remains active in stop mode. Clearing IMASK in INTSCR enables IRQ interrupt requests to bring the MCU out of stop mode.

### 8.6 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

### 8.7 I/O Signals

The IRQ module does not share its pin with any module on this MCU.

### 8.7.1 IRQ Input Pins (IRQ)

The IRQ pin provides a maskable external interrupt source. The IRQ pin contains an internal pullup device.

## Chapter 9 Keyboard Interrupt Module (KBI)

### 9.1 Introduction

The keyboard interrupt module (KBI) provides independently maskable external interrupts.

The KBI shares its pins with general-purpose input/output (I/O) port pins. See Figure 9-1 for port location of these shared pins.

### 9.2 Features

Features of the keyboard interrupt module include:

- Keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Programmable edge-only or edge and level interrupt sensitivity

- Edge sensitivity programmable for rising or falling edge

- Level sensitivity programmable for high or low level

- Pullup or pulldown device automatically enabled based on the polarity of edge or level detect

- Exit from low-power modes

### 9.3 Functional Description

The keyboard interrupt module controls the enabling/disabling of interrupt functions on the KBI pins. These pins can be enabled/disabled independently of each other. See Figure 9-2.

### 9.3.1 Keyboard Operation

Writing to the KBIEx bits in the keyboard interrupt enable register (KBIER) independently enables or disables each KBI pin. The polarity of the keyboard interrupt is controlled using the KBIPx bits in the keyboard interrupt polarity register (KBIPR). Edge-only or edge and level sensitivity is controlled using the MODEK bit in the keyboard status and control register (KBISCR).

Enabling a keyboard interrupt pin also enables its internal pullup or pulldown device based on the polarity enabled. On falling edge or low level detection, a pullup device is configured. On rising edge or high level detection, a pulldown device is configured.

The keyboard interrupt latch is set when one or more enabled keyboard interrupt inputs are asserted.

- If the keyboard interrupt sensitivity is edge-only, for KBIPx = 0, a falling (for KBIPx = 1, a rising) edge on a keyboard interrupt input does not latch an interrupt request if another enabled keyboard pin is already asserted. To prevent losing an interrupt request on one input because another input remains asserted, software can disable the latter input while it is asserted.

- If the keyboard interrupt is edge and level sensitive, an interrupt request is present as long as any enabled keyboard interrupt input is asserted.

### Keyboard Interrupt Module (KBI)

### 9.3.2 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pullup or pulldown device to pull the pin to its deasserted level. Therefore a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting IMASKK in KBSCR.

- 2. Enable the KBI polarity by setting the appropriate KBIPx bits in KBIPR.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in KBIER.

- 4. Write to ACKK in KBSCR to clear any false interrupts.

- 5. Clear IMASKK.

An interrupt signal on an edge sensitive pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge and level sensitive pin must be acknowledged after a delay that depends on the external load.

### 9.4 Interrupts

The following KBI source can generate interrupt requests:

Keyboard flag (KEYF) — The KEYF bit is set when any enabled KBI pin is asserted based on the KBI mode and pin polarity. The keyboard interrupt mask bit, IMASKK, is used to enable or disable KBI interrupt requests.

### 9.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

### 9.5.1 Wait Mode

The KBI module remains active in wait mode. Clearing IMASKK in KBSCR enables keyboard interrupt requests to bring the MCU out of wait mode.

### 9.5.2 Stop Mode

The KBI module remains active in stop mode. Clearing IMASKK in KBSCR enables keyboard interrupt requests to bring the MCU out of stop mode.

### 9.6 KBI During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

**Oscillator (OSC) Module**

### Chapter 12 Input/Output Ports (PORTS)

### 12.1 Introduction

The MC68HC08QY1A, MC68HC08QY2A and MC68HC08QY4A have thirteen bidirectional input-output (I/O) pins and one input only pin. The MC68HC08QT1A, MC68HC08QT2A and MC68HC08QT4A has five bidirectional I/O pins and one input only pin. All I/O pins are programmable as inputs or outputs.

### 12.2 Unused Pin Termination

Input pins and I/O port pins that are not used in the application must be terminated. This prevents excess current caused by floating inputs, and enhances immunity during noise or transient events. Termination methods include:

- 1. Configuring unused pins as outputs and driving high or low;

- 2. Configuring unused pins as inputs and enabling internal pull-ups;

- 3. Configuring unused pins as inputs and using external pull-up or pull-down resistors.

Never connect unused pins directly to V<sub>DD</sub> or V<sub>SS</sub>.

Since some general-purpose I/O pins are not available on all packages, these pins must be terminated as well. Either method 1 or 2 above are appropriate.

### 12.3 Port A

Port A is an 6-bit special function port that shares its pins with the keyboard interrupt (KBI) module (see Chapter 9 Keyboard Interrupt Module (KBI), the 2-channel timer interface module (TIM) (see Chapter 14 Timer Interface Module (TIM)), the 10-bit ADC (see Chapter 3 Analog-to-Digital Converter (ADC10) Module), the external interrupt (IRQ) pin (see Chapter 8 External Interrupt (IRQ)), the reset (RST) pin enabled using a configuration register (see Chapter 5 Configuration Register (CONFIG)) and the oscillator pins (see Chapter 11 Oscillator (OSC) Module).

Each port A pin also has a software configurable pullup device if the corresponding port pin is configured as an input port.

### NOTE

### PTA2 is input only.

When the IRQ function is enabled in the configuration register 2 (CONFIG2), bit 2 of the port A data register (PTA) will always read a logic 0. In this case, the BIH and BIL instructions can be used to read the logic level on the PTA2 pin. When the IRQ function is disabled, these instructions will behave as if the PTA2 pin is a logic 1. However, reading bit 2 of PTA will read the actual logic level on the pin.

#### System Integration Module (SIM)

### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

### 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

### 13.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

### 13.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power- consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

### 13.7.1 Wait Mode

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

| ADDRESS BUS | WAIT ADDR |        | DR + 1 | SAME  | X    | SAM | E X  |

|-------------|-----------|--------|--------|-------|------|-----|------|

| DATA BUS    | PREVIOUS  | S DATA |        | ODE X | SAME |     | SAME |

| R/W         |           |        | /      |       |      |     |      |

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

### Figure 13-14. Wait Mode Entry Timing

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred.

**Timer Interface Module (TIM)**

### 14.7 I/O Signals

The TIM module can share its pins with the general-purpose I/O pins. See Figure 14-1 for the port pins that are shared.

### 14.7.1 TIM Channel I/O Pins (TCH1:TCH0)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. TCH0 can be configured as buffered output compare or buffered PWM pin.

### 14.7.2 TIM Clock Pin (TCLK)

TCLK is an external clock input that can be the clock source for the counter instead of the prescaled internal bus clock. Select the TCLK input by writing 1s to the three prescaler select bits, PS[2:0]. 14.8.1 TIM Status and Control Register The minimum TCLK pulse width is specified in the Timer Interface Module Characteristics table in the Electricals section. The maximum TCLK frequency is the least of 4 MHz or bus frequency ÷ 2.

### 14.8 Registers

The following registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM control registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

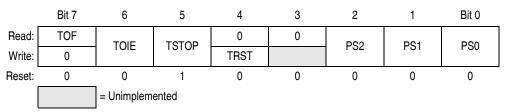

### 14.8.1 TIM Status and Control Register

The TIM status and control register (TSC) does the following:

- Enables TIM overflow interrupts

- Flags TIM overflows

- Stops the counter

- Resets the counter

- Prescales the counter clock

### Figure 14-4. TIM Status and Control Register (TSC)

### TOF — TIM Overflow Flag Bit

This read/write flag is set when the counter reaches the modulo value programmed in the TIM counter modulo registers. Clear TOF by reading the TSC register when TOF is set and then writing a 0 to TOF.

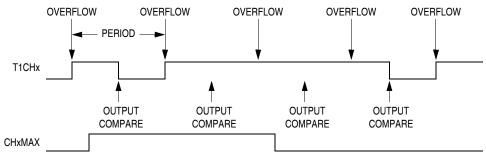

### TOVx — Toggle-On-Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the counter overflows. When channel x is an input capture channel, TOVx has no effect.

- 1 = Channel x pin toggles on TIM counter overflow.

- 0 = Channel x pin does not toggle on TIM counter overflow.

### NOTE

When TOVx is set, a counter overflow takes precedence over a channel x output compare if both occur at the same time.

### CHxMAX — Channel x Maximum Duty Cycle Bit

When the TOVx bit is at 1, setting the CHxMAX bit forces the duty cycle of buffered and unbuffered PWM signals to 100%. As Figure 14-11 shows, the CHxMAX bit takes effect in the cycle after it is set or cleared. The output stays at the 100% duty cycle level until the cycle after CHxMAX is cleared.

Figure 14-11. CHxMAX Latency

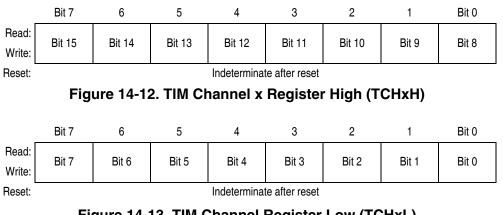

### 14.8.5 TIM Channel Registers

These read/write registers contain the captured counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Electrical Specifications

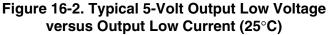

Figure 16-1. Typical 5-Volt Output High Voltage versus Output High Current (25°C)

#### **Electrical Specifications**

| Characteristic                       | Conditions  | Symbol          | Min  | Typ <sup>(1)</sup> | Max  | Unit | Comment                             |               |

|--------------------------------------|-------------|-----------------|------|--------------------|------|------|-------------------------------------|---------------|

| Integral per linearity               | 10-bit mode | INL             | 0    | ±0.5               | _    | LSB  |                                     |               |

| Integral non-linearity               | 8-bit mode  |                 | 0    | ±0.3               |      | LOD  |                                     |               |

| Zero-scale error                     | 10-bit mode | E <sub>zs</sub> | 0    | ±0.5               |      | LSB  | V <sub>ADIN</sub> = V <sub>SS</sub> |               |

| Zero-scale error                     | 8-bit mode  | ⊢zs             | 0    | ±0.3               | _    | LOD  | VADIN - VSS                         |               |

| Full-scale error                     | 10-bit mode | E <sub>FS</sub> | 0    | ±0.5               |      | LSB  | $V_{ADIN} = V_{DD}$                 |               |

|                                      | 8-bit mode  | ⊢FS             | 0    | ±0.3               | _    | LOD  |                                     |               |

| Quantization error                   | 10-bit mode | E <sub>Q</sub>  | E    | _                  | —    | ±0.5 | LSB                                 | 8-bit mode is |

| Quantization enor                    | 8-bit mode  |                 | _    | —                  | ±0.5 |      | not truncated                       |               |

| Input lookago orror                  | 10-bit mode | E <sub>IL</sub> | 0    | ±0.2               | ±5   | LSB  | Pad leakage <sup>(5)</sup>          |               |

| Input leakage error                  | 8-bit mode  |                 | 0    | ±0.1               | ±1.2 |      | * R <sub>AS</sub>                   |               |

| Bandgap voltage input <sup>(6)</sup> |             | V <sub>BG</sub> | 1.17 | 1.245              | 1.32 | V    |                                     |               |

Typical values assume V<sub>DD</sub> = 5.0 V, temperature = 25•C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

Incremental I<sub>DD</sub> added to MCU mode current.

3. Values are based on characterization results, not tested in production.

4. Reference the ADC module specification for more information on calculating conversion times.

5. Based on typical input pad leakage current.

6. LVI must be enabled, (LVIPWRD = 0, in CONFIG1). Voltage input to ADCH4:0 = \$1A, an ADC conversion on this channel allows user to determine supply voltage.

## Chapter 17 Ordering Information and Mechanical Specifications

### 17.1 Introduction

This section contains order numbers for the MC68HC908QY1A, MC68HC908QY2A, MC68HC908QY4A, MC68HC908QT1A, MC68HC908QT2A, and MC69HC908QT4A. Dimensions are given for:

- 8-pin plastic dual in-line package (PDIP)

- 8-pin small outline integrated circuit (SOIC) package

- 8-pin dual flat no lead (DFN) package

- 16-pin PDIP

- 16-pin SOIC

- 16-pin thin shrink small outline package (TSSOP)

### 17.2 Ordering Information

### Table 17-1. Consumer and Industrial Device Numbering System

| Device Number | ADC | FLASH Memory | Packages <sup>(1)</sup> |

|---------------|-----|--------------|-------------------------|

| MC908QT1A     | —   | 1536 bytes   | 8-pins                  |

| MC908QT2A     | Yes | 1536 bytes   | PDIP, SOIC,             |

| MC908QT4A     | Yes | 4096 bytes   | and DFN                 |

| MC908QY1A     | —   | 1536 bytes   | 16-pins                 |

| MC908QY2A     | Yes | 1536 bytes   | PDIP, SOIC,             |

| MC908QY4A     | Yes | 4096 bytes   | and TSSOP               |

1. See Table 17-3 for package information.

| Device Number | ADC | FLASH Memory | Packages <sup>(1)</sup> |

|---------------|-----|--------------|-------------------------|

| S908QY2A      | Yes | 1536 bytes   | 16-pins                 |

| S908QY4A      | Yes | 4096 bytes   | TSSOP and SOIC          |

1. See Table 17-3 for package information.

**Ordering Information and Mechanical Specifications**

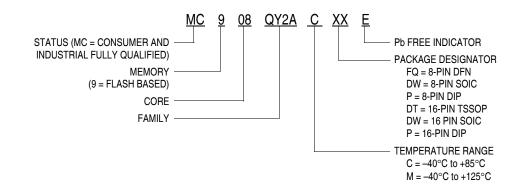

### 17.3 Orderable Part Numbering System

### 17.3.1 Consumer and Industrial Orderable Part Numbering System

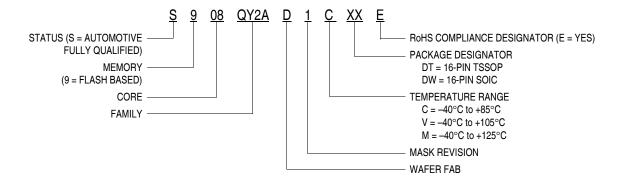

### 17.3.2 Automotive Orderable Part Number System

### **17.4 Mechanical Drawings**

The following pages contain mechanical specifications for MC68HC908QY4/QTA series package options. See Table 17-3 for the document numbers that correspond to each package type.

| Table 17-3. | Package | Information |

|-------------|---------|-------------|

|-------------|---------|-------------|

| Pin Count | Туре  | Designator | Document No. |

|-----------|-------|------------|--------------|

| 8         | PDIP  | Р          | 98ASB42420B  |

| 8         | SOIC  | DW         | 98ASH70107A  |

| 8         | DFN   | FQ         | 98ARL10557D  |

| 16        | PDIP  | Р          | 98ASB42431B  |

| 16        | SOIC  | DW         | 98ASB42567B  |

| 16        | TSSOP | DT         | 98ASH70247A  |

**Ordering Information and Mechanical Specifications**

Case 948F page 1 of 3