Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | <u> </u>                                                              |

| RAM Size                   | 24К х 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 1x12b, 1x16b; D/A 1x12b                                           |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f372cbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.13 16-bit sigma delta analog-to-digital converters (SDADC)

Up to three 16-bit sigma-delta analog-to-digital converters are embedded in the STM32F37x. They have up to two separate supply voltages allowing the analog function voltage range to be independent from the STM32F37x power supply. They share up to 21 input pins which may be configured in any combination of single-ended (up to 21) or differential inputs (up to 11).

The conversion speed is up to 16.6 ksps for each SDADC when converting multiple channels and up to 50 ksps per SDADC if single channel conversion is used. There are two conversion modes: single conversion mode or continuous mode, capable of automatically scanning any number of channels. The data can be automatically stored in a system RAM buffer, reducing the software overhead.

A timer triggering system can be used in order to control the start of conversion of the three SDADCs and/or the 12-bit fast ADC. This timing control is very flexible, capable of triggering simultaneous conversions or inserting a programmable delay between the ADCs.

Up to two external reference pins (VREFSD+, VREFSD-) and an internal 1.2/1.8 V reference can be used in conjunction with a programmable gain (x0.5 to x32) in order to fine-tune the input voltage range of the SDADC.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 40 kHz)

- The high-speed external clock divided by 32

## 3.19 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard (up to 100 kHz), fast (up to 400 kHz) and fast mode + (up to 1 MHz) modes with 20 mA output drive. They support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15 I <sup>2</sup> C peripheral clocks                                  |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled              |

Table 6.

Comparison of I<sup>2</sup>C analog and digital filters

In addition, they provide hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeout verifications and ALERT protocol management. They also have a clock domain independent from the CPU clock, allowing the application to wake up the MCU from Stop mode on address match.

The I<sup>2</sup>C interfaces can be served by the DMA controller

Refer to *Table 7* for the differences between I2C1 and I2C2.

### Table 7. STM32F37x I<sup>2</sup>C implementation

| I <sup>2</sup> C features <sup>(1)</sup>                    | I2C1 | I2C2 |

|-------------------------------------------------------------|------|------|

| 7-bit addressing mode                                       | Х    | Х    |

| 10-bit addressing mode                                      | Х    | Х    |

| Standard mode (up to 100 kbit/s)                            | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                | Х    | Х    |

| Fast Mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    |

| Independent clock                                           | Х    | Х    |

| SMBus                                                       | Х    | Х    |

| Wakeup from STOP                                            | Х    | Х    |

1. X = supported.

# Table 13. Alternate functions for port PB

| Pin<br>Name | AF0               | AF1            | AF2            | AF3            | AF4           | AF5                    | AF6                    | AF7        | AF8           | AF9            | AF10           | AF11          | AF15     |

|-------------|-------------------|----------------|----------------|----------------|---------------|------------------------|------------------------|------------|---------------|----------------|----------------|---------------|----------|

| PB0         |                   |                | TIM3_CH3       | TSC_<br>G3_IO3 |               | SPI_MOSI/<br>I2S1_SD   |                        |            |               |                | TIM3_<br>CH2   |               | EVENTOUT |

| PB1         |                   |                | TIM3_CH4       | TSC_<br>G3_IO4 |               |                        |                        |            |               |                |                |               | EVENTOUT |

| PB2         |                   |                |                |                |               |                        |                        |            |               |                |                |               | EVENTOUT |

| PB3         | JTDO/<br>TRACESWO | TIM2_<br>CH2   | TIM4_ETR       | TSC_<br>G5_IO1 |               | SPI1_SCK/<br>I2S1_CK   | SPI3_SCK/<br>I2S3_CK   | USART2_TX  |               | TIM13_<br>CH1  | TIM3_<br>ETR   |               | EVENTOUT |

| PB4         | JTRST             | TIM16_<br>CH1  | TIM3_CH1       | TSC_<br>G5_IO2 |               | SPI1_MISO<br>/I2S1_MCK | SPI3_MISO/<br>I2S3_MCK | USART2_RX  |               | TIM15_<br>CH1N | TIM17<br>_BKIN |               | EVENTOUT |

| PB5         |                   | TIM16_<br>BKIN | TIM3_CH2       |                | I2C1_<br>SMBA | SPI1_MOSI<br>/I2S1_SD  | SPI3_MOSI<br>/I2S3_SD  | USART2_CK  |               |                | TIM17<br>_CH1  | TIM19<br>_ETR | EVENTOUT |

| PB6         |                   | TIM16_<br>CH1N | TIM4_CH1       | TSC_<br>G5_IO3 | I2C1_<br>SCL  |                        |                        | USART1_TX  |               | TIM15_<br>CH1  | TIM3_<br>CH3   | TIM19<br>_CH1 | EVENTOUT |

| PB7         |                   | TIM17_<br>CH1N | TIM4_CH2       | TSC_<br>G5_IO4 | I2C1_<br>SDA  |                        |                        | USART1_RX  |               | TIM15_<br>CH2  | TIM3_<br>CH4   | TIM19<br>_CH2 | EVENTOUT |

| PB8         |                   | TIM16_<br>CH1  | TIM4_CH3       | TSC_<br>SYNC   | I2C1_<br>SCL  | SPI2_SCK/<br>I2S2_CK   | CEC                    | USART3_TX  | COMP1<br>_OUT | CAN_<br>RX     |                | TIM19<br>_CH3 | EVENTOUT |

| PB9         |                   | TIM17_<br>CH1  | TIM4_CH4       |                | I2C1_<br>SDA  | SPI2_NSS/<br>I2S2_WS   | IR-OUT                 | USART3_RX  | COMP2<br>_OUT | CAN_<br>TX     |                | TIM19<br>_CH4 | EVENTOUT |

| PB10        |                   | TIM2_<br>CH3   |                | TSC_<br>SYNCH  |               | SPI2_SCK/<br>I2S2_CK   | CEC                    | USART3_TX  |               |                |                |               | EVENTOUT |

| PB14        |                   | TIM15_<br>CH1  |                | TSC_<br>G6_IO1 |               | SPI2_MISO<br>/I2S2_MCK |                        | USART3_RTS |               | TIM12_<br>CH1  |                |               | EVENTOUT |

| PB15        |                   | TIM15_<br>CH2  | TIM15_<br>CH1N | TSC_<br>G6_IO2 |               | SPI2_MOSI<br>/I2S2_SD  |                        |            |               | TIM12_<br>CH2  |                |               | EVENTOUT |

STM32F37x

| Pin Name | AF0 | AF1      | AF2          | AF3        | AF4 | AF5                | AF6                | AF7       |

|----------|-----|----------|--------------|------------|-----|--------------------|--------------------|-----------|

| PC0      |     | EVENTOUT | TIM5_CH1_ETR |            |     |                    |                    |           |

| PC1      |     | EVENTOUT | TIM5_CH2     |            |     |                    |                    |           |

| PC2      |     | EVENTOUT | TIM5_CH3     |            |     | SPI2_MISO/I2S2_MCK |                    |           |

| PC3      |     | EVENTOUT | TIM5_CH4     |            |     | SPI2_MOSI/I2S2_SD  |                    |           |

| PC4      |     | EVENTOUT | TIM13_CH1    | TSC_G3_IO1 |     |                    |                    | USART1_TX |

| PC5      |     | EVENTOUT |              | TSC_G3_IO2 |     |                    |                    | USART1_R> |

| PC6      |     | EVENTOUT | TIM3_CH1     |            |     | SPI1_NSS/I2S1_WS   |                    |           |

| PC7      |     | EVENTOUT | TIM3_CH2     |            |     | SPI1_SCK/I2S1_CK   |                    |           |

| PC8      |     | EVENTOUT | TIM3_CH3     |            |     | SPI1_MISO/I2S1_MCK |                    |           |

| PC9      |     | EVENTOUT | TIM3_CH4     |            |     | SPI1_MOSI/I2S1_SD  |                    |           |

| PC10     |     | EVENTOUT | TIM19_CH1    |            |     |                    | SPI3_SCK/I2S3_CK   | USART3_T> |

| PC11     |     | EVENTOUT | TIM19_CH2    |            |     |                    | SPI3_MISO/I2S3_MCK | USART3_R  |

| PC12     |     | EVENTOUT | TIM19_CH3    |            |     |                    | SPI3_MOSI/I2S3_SD  | USART3_Cł |

| PC13     |     |          |              |            |     |                    |                    |           |

| PC14     |     |          |              |            |     |                    |                    |           |

| PC15     |     | 1        |              |            |     |                    |                    |           |

Table 14 Alternate functions for port PC

S

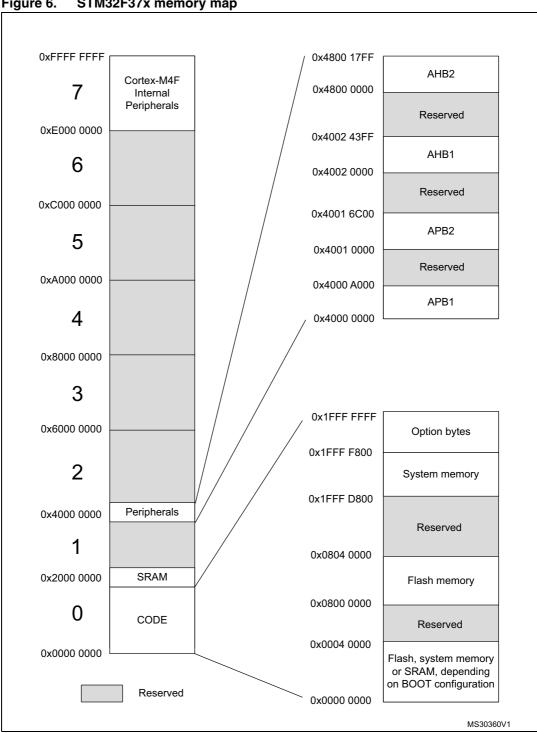

#### **Memory mapping** 5

Doc ID 022691 Rev 3

# 6.3 Operating conditions

## 6.3.1 General operating conditions

## Table 22. General operating conditions

| Symbol                          | Parameter                                                                                | Conditions                                                                | Min   | Max                         | Unit |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------|-----------------------------|------|--|--|--|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                                             |                                                                           | 0     | 72                          |      |  |  |  |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                                            |                                                                           | 0     | 36                          | MHz  |  |  |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                                            |                                                                           | 0     | 72                          |      |  |  |  |

| $V_{DD}$                        | Standard operating voltage                                                               | Must have a potential equal to or lower than $V_{\mbox{\scriptsize DDA}}$ | 2     | 3.6                         | V    |  |  |  |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC and DAC used)                                           | Must have a potential equal                                               | 2.4   | 3.6                         | v    |  |  |  |

| V DDA`´                         | Analog operating voltage<br>(ADC and DAC not used)                                       | to or higher than V <sub>DD</sub>                                         | 2     | 3.6                         | v    |  |  |  |

| N/                              | VDDSD12 operating voltage<br>(SDADC used)                                                | Must have a potential equal                                               | 2.2   | 3.6                         | v    |  |  |  |

| V <sub>DDSD12</sub>             | (SDADC not used)                                                                         | 2.0                                                                       | 3.6   | v                           |      |  |  |  |

| V                               | VDDSD3 operating voltage<br>(SDADC used)                                                 | Must have a potential equal                                               | 2.2   | 3.6                         | v    |  |  |  |

| V DDSD3                         | VDDSD3 operating voltage<br>(SDADC not used)                                             |                                                                           | 2.0   | 3.6                         | v    |  |  |  |

| V <sub>BAT</sub>                | Backup operating voltage                                                                 |                                                                           | 1.65  | 3.6                         | V    |  |  |  |

|                                 | Input voltage on FT and FTf pins <sup>(2)</sup>                                          |                                                                           | - 0.3 | 5.5                         |      |  |  |  |

|                                 | Input voltage on TTa pins                                                                |                                                                           | - 0.3 | V <sub>DDA</sub> + 0.3      |      |  |  |  |

| V <sub>IN</sub>                 | Input voltage on TC pins on SDADCx channels inputs <sup>(3)</sup>                        |                                                                           | - 0.3 | V <sub>DDSDx</sub><br>+ 0.3 | V    |  |  |  |

|                                 | Input voltage on BOOT0 pin                                                               |                                                                           | 0     | 5.5                         |      |  |  |  |

|                                 | Input voltage on any other pin                                                           |                                                                           | - 0.3 | V <sub>DD</sub> +<br>0.3    |      |  |  |  |

|                                 |                                                                                          | LQFP100                                                                   |       | 434                         |      |  |  |  |

| Р                               | Power dissipation at $T_A = 85 \text{ °C}$<br>for suffix 6 or $T_A = 105 \text{ °C}$ for | LQFP64                                                                    |       | 444                         | m\\/ |  |  |  |

| P <sub>D</sub>                  | suffix $7^{(4)}$                                                                         | LQFP48                                                                    |       | 364                         | mW   |  |  |  |

|                                 |                                                                                          | BGA100                                                                    |       | 338                         |      |  |  |  |

|                                 | Ambient temperature for 6 suffix                                                         | Maximum power dissipation                                                 | -40   | 85                          | °C   |  |  |  |

| Та                              | version                                                                                  | Low power dissipation <sup>(5)</sup>                                      | -40   | 105                         |      |  |  |  |

| IA IA                           | Ambient temperature for 7 suffix                                                         | Maximum power dissipation                                                 | -40   | 105                         | °C   |  |  |  |

|                                 | version                                                                                  | Low power dissipation <sup>(5)</sup>                                      | -40   | 125                         |      |  |  |  |

### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 52: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC and SDADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode. Under reset conditions all I/Os are configured in input floating mode - so if some inputs do not have a defined voltage level then they can generate additional consumption. This consumption is visible on V<sub>DD</sub> supply and also on V<sub>DDSDx</sub> supply because some I/Os are powered from SDADCx supply (all I/Os which have SDADC analog input functionality).

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 36: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{\text{DD}}$  is the MCU supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$ +  $C_S$

$C_S$  is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 41*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter               | Conditions <sup>(1)</sup>                          | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-------------------------|----------------------------------------------------|--------------------|-----|--------------------|------|

|                                     |                         | LSEDRV[1:0]=00<br>lower driving capability         |                    | 0.5 | 0.9                |      |

|                                     | LSE current consumption | LSEDRV[1:0]= 01<br>medium low driving capability   |                    |     | 1                  |      |

| I <sub>DD</sub>                     |                         | LSEDRV[1:0] = 10<br>medium high driving capability |                    |     | 1.3                | μA   |

|                                     |                         | LSEDRV[1:0]=11<br>higher driving capability        |                    |     | 1.6                |      |

|                                     | Oscillator              | LSEDRV[1:0]=00<br>lower driving capability         | 5                  |     |                    |      |

| ~                                   |                         | LSEDRV[1:0]= 01<br>medium low driving capability   | 8                  |     |                    | μA/V |

| 9 <sub>m</sub>                      | transconductance        | LSEDRV[1:0] = 10<br>medium high driving capability | 15                 |     |                    | μΑνν |

|                                     |                         | LSEDRV[1:0]=11<br>higher driving capability        | 25                 |     |                    |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time            | V <sub>DD</sub> is stabilized                      |                    | 2   |                    | S    |

| Table 41. | LSE oscillator characteristics | (f <sub>I SF</sub> = 32.768 kHz) |

|-----------|--------------------------------|----------------------------------|

|-----------|--------------------------------|----------------------------------|

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol Parameter | Conditions | Monitored                                         | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ] | Unit     |      |

|------------------|------------|---------------------------------------------------|------------------------------------------------|----------|------|

|                  | Farameter  | Contailons                                        | frequency band                                 | 8/72 MHz | Unit |

|                  |            | 0.1 to 30 MHz                                     | 9                                              |          |      |

| 6                | Peak level | $V_{DD} = 3.3 V, T_A = 25 °C,$<br>LQFP100 package | 30 to 130 MHz                                  | 26       | dBµV |

| S <sub>EMI</sub> | reak level | compliant with IEC<br>61967-2                     | 130 MHz to 1 GHz                               | 30       |      |

|                  |            |                                                   | SAE EMI Level                                  | 4        | -    |

Table 48. EMI characteristics

### 6.3.12 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

Table 49.ESD absolute maximum ratings

| Symbol                | Ratings | Conditions                                                                                         | Class | Maximum value <sup>(1)</sup> | Unit |

|-----------------------|---------|----------------------------------------------------------------------------------------------------|-------|------------------------------|------|

| V <sub>ESD(HBM)</sub> | _       | T <sub>A</sub> = +25 °C, conforming<br>to JESD22-A114                                              | 2     | 2000                         |      |

| V <sub>ESD(CDM)</sub> |         | $T_A = +25$ °C, conforming<br>to JESD22-C101,<br>LQFP100, LQFP64,<br>LQFP48 and BGA100<br>packages | II    | 500                          | V    |

|                       |         | T <sub>A</sub> = +25 °C, conforming<br>to JESD22-C101,<br>WLCSP66 package                          | II    | 250                          |      |

1. Data based on characterization results, not tested in production.

### 6.3.16 Communications interfaces

### I<sup>2</sup>C interface characteristics

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under ambient temperature,  $f_{PCLK1}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

The I<sup>2</sup>C interface meets the requirements of the standard I<sup>2</sup>C communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" opendrain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 56*. Refer also to *Section 6.3.14: I/O port characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standa           | rd mode             | Fast m           | ode                | Fast mode Plus   |                    | Unit |

|--------------------------------------------|-----------------------------------------|------------------|---------------------|------------------|--------------------|------------------|--------------------|------|

| Symbol                                     | Parameter                               | Min              | Max                 | Min              | Max                | Min              | Max                | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7              |                     | 1.3              |                    | 0.5              |                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0              |                     | 0.6              |                    | 0.26             |                    | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250              |                     | 100              |                    | 50               |                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(2)</sup> | 3450 <sup>(3)</sup> | 0 <sup>(2)</sup> | 900 <sup>(3)</sup> | 0 <sup>(4)</sup> | 450 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                  | 1000                |                  | 300                |                  | 120                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                  | 300                 |                  | 300                |                  | 120                |      |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0              |                     | 0.6              |                    | 0.26             |                    |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7              |                     | 0.6              |                    | 0.26             |                    | μs   |

| t <sub>su(STO)</sub>                       | Stop condition setup time               | 4.0              |                     | 0.6              |                    | 0.26             |                    | μs   |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7              |                     | 1.3              |                    | 0.5              |                    | μS   |

| C <sub>b</sub>                             | Capacitive load for each bus line       |                  | 400                 |                  | 400                |                  | 550                | pF   |

#### Table 56. $I^2C$ characteristics<sup>(1)</sup>

The I<sup>2</sup>C characteristics are the requirements from I<sup>2</sup>C bus specification rev03. They are guaranteed by design when I2Cx\_TIMING register is correctly programmed (Refer to reference manual). These characteristics are not tested in production.

2. The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The device must internally provide a hold time of at least 120ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 58* for SPI or in *Table 59* for  $I^2S$  are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

Refer to *Section 6.3.14: I/O port characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                                                     | Parameter                           | Conditions                                            | Min            | Max            | Unit |

|----------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|----------------|----------------|------|

| fsck                                                                       |                                     | Master mode                                           |                | 18             | MHz  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> (1)                              | SPI clock frequency                 | Slave mode                                            | 18             |                |      |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub> (1)                             | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            |                | 8              | ns   |

| DuCy(SCK) <sup>(1)</sup>                                                   | SPI slave input clock<br>duty cycle | Slave mode                                            | 30             | 70             | %    |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                                        | NSS setup time                      | Slave mode                                            | 2Tpclk         |                |      |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                                         | NSS hold time                       | Slave mode                                            | 4Tpclk         |                |      |

| t <sub>w(SCKH)</sub> <sup>(1)</sup><br>t <sub>w(SCKL)</sub> <sup>(1)</sup> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2<br>- 3 | Tpclk/2<br>+ 3 |      |

|                                                                            | Data input actus time               | Master mode                                           | 5.5            |                |      |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)                         | Data input setup time               | Slave mode                                            | 6.5            |                |      |

| t <sub>h(MI)</sub> <sup>(1)</sup>                                          | Data input hald time                | Master mode                                           | 5              |                |      |

| t <sub>h(SI)</sub> <sup>(1)</sup>                                          | Data input hold time                | Slave mode                                            | 5              |                | ns   |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                                       | Data output access time             | Slave mode, f <sub>PCLK</sub> = 24 MHz                | 0              | 4Tpclk         |      |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>                                     | Data output disable time            | Slave mode                                            | 0              | 24             |      |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                          | Data output valid time              | Slave mode (after enable edge)                        |                | 39             |      |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                          | Data output valid time              | Master mode (after enable edge)                       |                | 3              |      |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                          | Data output hold time               | Slave mode (after enable edge)                        | 15             |                | 1    |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                          | Data output hold time               | Master mode (after enable edge)                       | 4              |                | 1    |

Table 58. SPI characteristics

1. Data based on characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

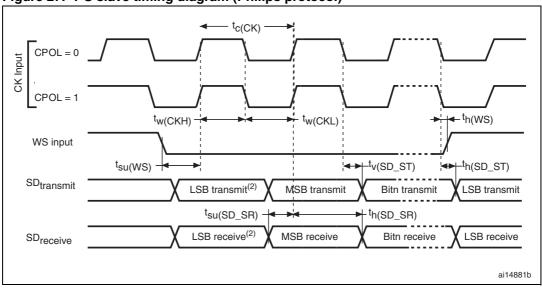

Figure 27. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at  $0.5V_{DD}$  level and with external C<sub>L</sub> = 30 pF.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

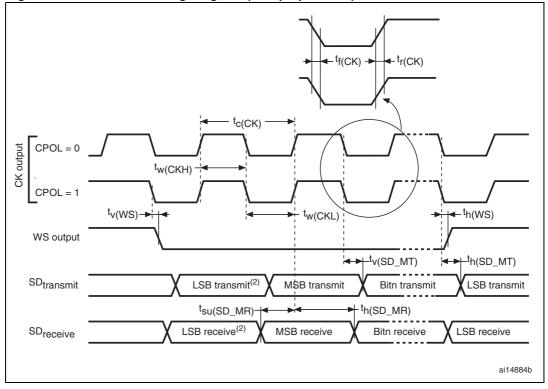

### Figure 28. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at  $0.5V_{DD}$  level and with external C<sub>L</sub> = 30 pF.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

### 6.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 60* are preliminary values derived from tests performed under ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 22*.

*Note:* It is recommended to perform a calibration after each power-up.

| Symbol                           | Parameter                                          | Conditions                                            | Min                                                         | Тур                | Max                | Unit               |

|----------------------------------|----------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|

| $V_{DDA}$                        | Power supply                                       |                                                       | 2.4                                                         |                    | 3.6                | V                  |

| $V_{REF+}$                       | Positive reference voltage                         |                                                       | 2.4                                                         |                    | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin          |                                                       |                                                             | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μΑ                 |

| f <sub>ADC</sub>                 | ADC clock frequency                                |                                                       | 0.6                                                         |                    | 14                 | MHz                |

| $f_{S}^{(2)}$                    | Sampling rate                                      |                                                       | 0.05                                                        |                    | 1                  | MHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                         | f <sub>ADC</sub> = 14 MHz                             |                                                             |                    | 823                | kHz                |

| 'TRIG                            |                                                    |                                                       |                                                             |                    | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range                           |                                                       | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) |                    | $V_{REF+}$         | v                  |

| R <sub>SRC</sub> <sup>(2)</sup>  | Signal source impedance                            | See <i>Equation 1</i> and <i>Table 61</i> for details |                                                             |                    | 50                 | kΩ                 |

| $R_{ADC}^{(2)}$                  | Sampling switch resistance                         |                                                       |                                                             |                    | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor                 |                                                       |                                                             |                    | 8                  | pF                 |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time                                   | f <sub>ADC</sub> = 14 MHz                             | 5.9                                                         |                    |                    | μs                 |

| <sup>I</sup> CAL`´               |                                                    |                                                       | 83                                                          |                    |                    | 1/f <sub>ADC</sub> |

| t <sub>lat</sub> (2)             | Injection trigger conversion                       | f <sub>ADC</sub> = 14 MHz                             |                                                             |                    | 0.214              | μs                 |

| 'lat` '                          | latency                                            |                                                       |                                                             |                    | 2 <sup>(3)</sup>   | 1/f <sub>ADC</sub> |

| ↓ (2)                            | Regular trigger conversion                         | f <sub>ADC</sub> = 14 MHz                             |                                                             |                    | 0.143              | μs                 |

| t <sub>latr</sub> (2)            | latency                                            |                                                       |                                                             |                    | 2 <sup>(3)</sup>   | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Sampling time                                      | $f_{ADC} = 14 \text{ MHz}$                            | 0.107                                                       |                    | 17.1               | μs                 |

| IS(=/                            | Sampling une                                       |                                                       | 1.5                                                         |                    | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                      |                                                       | 0                                                           | 0                  | 1                  | μs                 |

|                                  | Total conversion time                              | f <sub>ADC</sub> = 14 MHz                             | 1                                                           |                    | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time<br>(including sampling time) |                                                       | 14 to 252 (t <sub>S</sub> for sa<br>successive approx       |                    |                    | 1/f <sub>ADC</sub> |

#### Table 60. ADC characteristics

1. Based on characterization, not tested in production.

2. Guaranteed by design, not tested in production.

3. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 60

### 6.3.23 USB characteristics

#### Table 71. USB startup time

| Symbol                              | Parameter                    | Max | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design, not tested in production.

#### Table 72. USB DC electrical characteristics

| Symbol                         | Parameter                                           | Conditions                                                     | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |  |

|--------------------------------|-----------------------------------------------------|----------------------------------------------------------------|---------------------|---------------------|------|--|--|

| Input levels                   |                                                     |                                                                |                     |                     |      |  |  |

| V <sub>DD</sub>                | USB operating voltage <sup>(2)</sup>                |                                                                | 3.0 <sup>(3)</sup>  | 3.6                 | V    |  |  |

| V <sub>DI</sub> <sup>(4)</sup> | Differential input sensitivity (for USB compliance) | I(USB_DP, USB_DM)                                              | 0.2                 |                     |      |  |  |

| V <sub>CM</sub> <sup>(4)</sup> | Differential common mode range                      | Includes V <sub>DI</sub> range                                 | 0.8                 | 2.5                 | V    |  |  |

| $V_{SE}^{(4)}$                 | Single ended receiver threshold                     |                                                                | 1.3                 | 2.0                 |      |  |  |

| Output levels                  |                                                     |                                                                |                     |                     |      |  |  |

| V <sub>OL</sub>                | Static output level low                             | $\rm R_L$ of 1.5 k\Omega to 3.6 $\rm V^{(5)}$                  |                     | 0.3                 | v    |  |  |

| V <sub>OH</sub>                | Static output level high                            | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}^{(5)}$ | 2.8                 | 3.6                 | V    |  |  |

1. All the voltages are measured from the local ground potential.

2. To be compliant with the USB 2.0 full-speed electrical specification, the USB\_DP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

3. The STM32F3xxx USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

4. Guaranteed by design, not tested in production.

5. R<sub>L</sub> is the load connected on the USB drivers

| Symbol             | Parameter                        |                   |                 | Con                           | ditions                                  |                                             | Min               | Тур             | Max      | Unit                        | Note                     |                              |           |           |           |                                          |           |           |           |          |  |                    |

|--------------------|----------------------------------|-------------------|-----------------|-------------------------------|------------------------------------------|---------------------------------------------|-------------------|-----------------|----------|-----------------------------|--------------------------|------------------------------|-----------|-----------|-----------|------------------------------------------|-----------|-----------|-----------|----------|--|--------------------|

|                    |                                  |                   |                 | f <sub>ADC</sub> =<br>1.5 MHz |                                          | V <sub>REFSD+</sub> =<br>3.3 <sup>(2)</sup> | 76                | 77              |          |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | ٥                 | gain =1         | f <sub>ADC</sub> = 6          | V <sub>REFSD+</sub> = 1.2 <sup>(3)</sup> | 75                                          | 76                |                 |          |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | al mod            | 0,              | MHz                           |                                          | V <sub>REFSD+</sub> =<br>3.3                | 76                | 77              |          |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | Differential mode |                 | f <sub>ADC</sub> = 6          |                                          | V <sub>REFSD+</sub> = 1.2 <sup>(3)</sup>    | 70                | 74              |          |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    | Signal to                        | Ō                 | gain =8         | MHz                           |                                          | V <sub>REFSD+</sub> =<br>3.3                | 79                | 85              |          |                             | ENOB =                   |                              |           |           |           |                                          |           |           |           |          |  |                    |

| SINAD<br>(4)       | noise and<br>distortion<br>ratio |                   | 0,              | f <sub>ADC</sub> =<br>1.5 MHz | V <sub>DDSDx</sub><br>= 3.3              | V <sub>REFSD+</sub> =<br>3.3 <sup>(2)</sup> | 75                | 81              |          | dB                          | SINAD/6.0<br>2<br>-0.292 |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  |                   |                 | f <sub>ADC</sub> =<br>1.5MHz  |                                          | V <sub>REFSD+</sub> =<br>3.3                | 72                | 73              |          |                             | -0.292                   |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | d mode            | gain =1         | f <sub>ADC</sub> =            |                                          | V <sub>REFSD+</sub> = 1.2 <sup>(3)</sup>    | 68                | 71              |          |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    | Single ended mode                |                   | ended           |                               | 0                                        | 5                                           | 5                 | 6               | J        | 6 MHz                       |                          | V <sub>REFSD+</sub> =<br>3.3 | 72        | 73        |           |                                          |           |           |           |          |  |                    |

|                    |                                  | Single            | n =8            | f <sub>ADC</sub> =            |                                          | V <sub>REFSD+</sub> = 1.2 <sup>(3)</sup>    | 60                | 64              |          |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  |                   |                 |                               |                                          |                                             |                   |                 | gain     | 6 MHz                       |                          | V <sub>REF</sub> = 3.3       | 67        | 72        |           |                                          |           |           |           |          |  |                    |

|                    |                                  |                   |                 | f <sub>ADC</sub> =<br>1.5 MHz |                                          | V <sub>REFSD+</sub> =<br>3.3 <sup>(2)</sup> |                   | -77             | -76      |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | fferential mode   | fferential mode | fferential mode               | fferential mode                          | fferential mode                             | Differential mode | fferential mode | n        | ٥.                          | ۵.                       | ¢)                           | gain =1   | fade =    |           | V <sub>REFSD+</sub> = 1.2 <sup>(3)</sup> |           | -77       | -76       |          |  |                    |

|                    |                                  |                   |                 |                               |                                          |                                             |                   |                 | 0        | f <sub>ADC</sub> =<br>6 MHz |                          | V <sub>REFSD+</sub> =<br>3.3 |           | -77       | -76       | 1                                        |           |           |           |          |  |                    |

|                    |                                  |                   |                 |                               |                                          |                                             |                   |                 | fferenti | fferenti                    | fferenti                 | ifferenti                    | ifferenti | ifferenti | ifferenti | ifferenti                                | ifferenti | ifferenti | ifferenti | fferenti |  | f <sub>ADC</sub> = |

| THD <sup>(4)</sup> | Total<br>harmonic                |                   | gain =8         | f <sub>ADC</sub> =<br>6 MHz   | V <sub>DDSDx</sub>                       | V <sub>REFSD+</sub> =<br>3.3                |                   | -93             | -80      | dB                          |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    | distortion                       |                   |                 | f <sub>ADC</sub> =<br>1.5 MHz | = 3.3                                    | V <sub>REFSD+</sub> =<br>3.3 <sup>(2)</sup> |                   | -93             | -83      | - an                        |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | de                | <del>-</del>    | f <sub>ADC</sub> =            |                                          | V <sub>REFSD+</sub> = 1.2 <sup>(3)</sup>    |                   | -72             | -68      |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | ed moc            | gain =1         | 6 MHz                         |                                          | V <sub>REFSD+</sub> =<br>3.3                |                   | -74             | -72      |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | Single ended mode | gain =8         | f <sub>ADC</sub> =            |                                          | V <sub>REFSD+</sub> = 1.2 <sup>(3)</sup>    |                   | -66             | -61      |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

|                    |                                  | Sin               | gain            | 6 MHz                         |                                          | V <sub>REFSD+</sub> =<br>3.3                |                   | -75             | -70      |                             |                          |                              |           |           |           |                                          |           |           |           |          |  |                    |

Table 74.

SDADC characteristics (continued)<sup>(1)</sup>

1. Data based on characterization results, not tested in production.

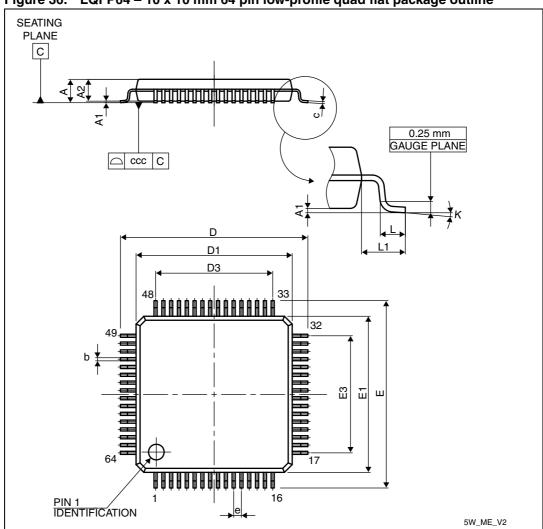

Figure 36. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 78. | LQFP64 – 10 x 10 mm low-profile quad flat package mechanical data | 3 |

|-----------|-------------------------------------------------------------------|---|

|-----------|-------------------------------------------------------------------|---|

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|--|--|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |  |  |  |

| А      |       |             | 1.60  |        |                       | 0.0630 |  |  |  |

| A1     | 0.05  |             | 0.15  | 0.0020 |                       | 0.0059 |  |  |  |

| A2     | 1.350 | 1.40        | 1.45  | 0.0531 | 0.0551                | 0.0571 |  |  |  |

| b      | 0.17  | 0.22        | 0.27  | 0.0067 | 0.0087                | 0.0106 |  |  |  |

| с      | 0.09  |             | 0.20  | 0.0035 |                       | 0.0079 |  |  |  |

| D      | 11.80 | 12.00       | 12.20 | 0.4646 | 0.4724                | 0.4803 |  |  |  |

| D1     | 9.80  | 10.00       | 10.20 | 0.3858 | 0.3937                | 0.4016 |  |  |  |

| D3     |       | 7.50        |       |        | 0.2953                |        |  |  |  |

| Symbol |      | millimeters |      |        | inches <sup>(1)</sup> | ches <sup>(1)</sup> |  |  |

|--------|------|-------------|------|--------|-----------------------|---------------------|--|--|

| Symbol | Min  | Тур         | Max  | Min    | Тур                   | Max                 |  |  |

| е      |      | 0.50        |      |        | 0.0197                |                     |  |  |

| L      | 0.45 | 0.60        | 0.75 | 0.0177 | 0.0236                | 0.0295              |  |  |

| L1     |      | 1.00        |      |        | 0.0394                |                     |  |  |

| К      | 0°   | 3.5°        | 7°   | 0°     | 3.5°                  | 7°                  |  |  |

| ccc    |      |             | 0.08 |        |                       | 0.0031              |  |  |

Table 79. LQFP48 – 7 x 7 mm, low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

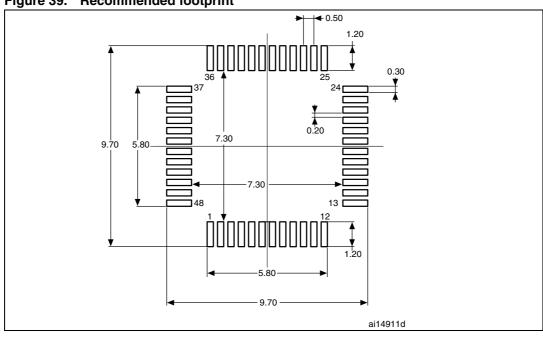

### Figure 39. Recommended footprint

1. Dimensions are in millimeters.

### 7.2.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Part numbering*.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F37x at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 82$  °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 3 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 2 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

$P_{INTmax} = 50 \text{ mA} \times 3.5 \text{ V} = 175 \text{ mW}$

$P_{IOmax} = 3 \times 8 \text{ mA} \times 0.4 \text{ V} + 2 \times 20 \text{ mA} \times 1.3 \text{ V} = 61.6 \text{ mW}$

This gives:  $P_{INTmax} = 175 \text{ mW}$  and  $P_{IOmax} = 61.6 \text{ mW}$ :

$P_{Dmax} = 175 + 61.6 = 236.6 \text{ mW}$

Thus:  $P_{Dmax} = 236.6 \text{ mW}$

Using the values obtained in *Table 80* T<sub>Jmax</sub> is calculated as follows:

For LQFP64, 45°C/W

T<sub>Jmax</sub> = 82 °C + (45°C/W × 236.6 mW) = 82 °C + 10.65 °C = 92.65 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Section 8: Part numbering*).

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 115 \text{ °C}$  (measured according to JESD51-2),  $I_{DDmax} = 20 \text{ mA}$ ,  $V_{DD} = 3.5 \text{ V}$ , maximum 9 I/Os used at the same time in output at low level with  $I_{OL} = 8 \text{ mA}$ ,  $V_{OL} = 0.4 \text{ V}$   $P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$   $P_{IOmax} = 9 \times 8 \text{ mA} \times 0.4 \text{ V} = 28.8 \text{ mW}$ This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 28.8 \text{ mW}$ :  $P_{Dmax} = 70 + 28.8 = 98.8 \text{ mW}$ s:  $P_{Dmax} = -98.8 \text{ mW}$

Thus:  $P_{Dmax} = 98.8 \text{ mW}$

# 8 Part numbering

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Table 81.     | Ordering information schem             |       | _ |     | _ |   | - |   |

|---------------|----------------------------------------|-------|---|-----|---|---|---|---|

| Example:      |                                        | STM32 | F | 372 | R | 8 | Т | 6 |

| Device fam    | ily<br>RM-based 32-bit microcontroller |       |   |     |   |   |   |   |

| 511032 = A    | RM-based 32-bit microcontroller        |       |   |     |   |   |   |   |

| Product typ   |                                        |       |   |     |   |   |   |   |

| F = Genera    | l-purpose                              |       |   |     |   |   |   |   |

| Sub-family    |                                        |       |   |     |   |   |   |   |

| 372 = STM     |                                        |       |   |     |   |   |   |   |

| 373 = STM3    |                                        |       |   |     |   |   |   |   |

| Pin count     |                                        |       |   |     |   |   |   |   |

| C = 48 pins   |                                        |       |   |     |   |   |   |   |

| R = 64 pins   |                                        |       |   |     |   |   |   |   |

| V = 100 pin   | S                                      |       |   |     |   |   |   |   |

| Code size     |                                        |       |   |     |   |   |   |   |

| 8 = 64 Kbyt   | es of Flash memory                     |       |   |     |   |   |   |   |

| B = 128 Kb    | ytes of Flash memory                   |       |   |     |   |   |   |   |

| C = 256 Kb    | ytes of Flash memory                   |       |   |     |   |   |   |   |

| Package       |                                        |       |   |     |   |   |   |   |

| T = LQFP      |                                        |       |   |     |   |   |   |   |

| H = BGA       |                                        |       |   |     |   |   |   |   |

| Temperatu     | re range                               |       |   |     |   |   |   |   |

| 6 = Industria | al temperature range, -40 to 85 °C     |       |   |     |   |   |   |   |

| 7 = Industria | al temperature range, -40 to 105 °C    |       |   |     |   |   |   |   |

| Options       |                                        |       |   |     |   |   |   |   |

xxx = programmed parts TR = tape and real

57

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Dec-2012 | 3        | Updated Table 2: Device overview, capacitive sensing<br>channels peripheral added.<br>Updated Table 3: Capacitive sensing GPIOs available on<br>STM32F37x devices<br>Updated Table 3: Capacitive sensing GPIOs available on<br>STM32F37x devices<br>Updated Table 2: Current characteristics<br>Updated Table 20: Current characteristics<br>Updated Table 20: Current characteristics<br>Updated Table 22: General operating conditions<br>Updated Table 22: General operating conditions<br>Updated Table 22: Typical and maximum VDD consumption in<br>Stop and Standby modes<br>Updated Table 30: Typical and maximum current consumption<br>from VBAT supply<br>Added Figure 11: Typical VBAT current consumption (LSE<br>and RTC ON/LSEDRV[1:0]='00')<br>Updated Table 33: Typical current consumption in Run mode,<br>code with data processing running from Flash<br>Table 34: Typical current consumption in Sleep mode, code<br>running from Flash or RAM<br>Added Table 35: Switching output I/O current consumption<br>Added Table 36: Peripheral current consumption<br>Figure 16: HSI oscillator accuracy characterization results<br>Updated Section 6.3.6: Wakeup time from low-power mode<br>Updated Table 37: Low-power mode wakeup timings<br>Updated Table 37: LOw-power mode wakeup timings<br>Updated Table 47: EMS characteristics<br>Updated Table 47: LOS current injection susceptibility<br>Updated Table 52: I/O static characteristics<br>Updated Table 52: I/O static characteristics<br>Updated Table 53: Output voltage characteristics -<br>CMOS port, Figure 18: TC and TTa I/O input characteristics -<br>CMOS port, Figure 18: TC and TTa I/O input characteristics -<br>Updated Table 53: Output voltage characteristics<br>Updated Table 55: NRST pin characteristics<br>Updated Table 55: NRST pin characteristics<br>Updated Table 54: I/O AC characteristics<br>Updated Table 53: DAC characteristics<br>Updated Table 54: LOFP100 – 14 x 14 mm 100 pin low-profile<br>quad flat package outline, Figure 9: LQFP64 – 10 x 10 mm 64<br>pin low-profile quad flat package outline and Figure 11:<br>LQFP48 – 7 x 7 mm, 48 pin low-profile quad flat package<br>euchina<br>Updated Table 21: LQFP100 – 14 x 14 mm low-profil |

Table 82. Document revision history

Doc ID 022691 Rev 3