Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessorARM Cortex@-M4Core Size32-Bit Single-CoreSpeed2MHzConnectivityCANbus, PC, IrDA, LINbus, SPI, UART/USART, USBPeripheralsDMA, PS, POR, PWM, WDTNumber of I/O52Program Memory Size56KB (256K x 8)Program Memory TypeFLASHEERPOM Size-Nufage Supply (Vcc/Vdd)2V ~ 3.6VVoltage Supply (Vcc/Vdd)Voltage Supply (Vcc/Vdd)Operating Temperature40° c ~ 85° C (TA)Nounting TypeSuface MountProgram Grape64 LQFPSupplier Device Package64-LQFP (Inx10)Supplier Device Package64-LQFP (Inx10)Processor64-LQFP (Inx10) | Details                    |                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed72MHzConnectivityCANbus, I²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsDMA, I²S, POR, PWM, WDTNumber of I/O52Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                         | Product Status             | Obsolete                                                              |

| Speed72MHzConnectivityCANbus, IPC, IrDA, LINbus, SPI, UART/USART, USBPeripheralsDMA, IPS, POR, PWM, WDTNumber of I/O52Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                  | Core Processor             | ARM® Cortex®-M4                                                       |

| ConnectivityCANbus, I²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsDMA, I²S, POR, PWM, WDTNumber of I/O52Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type64-LQFPEakage / Case64-LQFP (10x10)                                                                                                                                                   | Core Size                  | 32-Bit Single-Core                                                    |

| PeripheralsDMA, I²S, POR, PWM, WDTNumber of I/O52Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                                                                                       | Speed                      | 72MHz                                                                 |

| Number of I/O52Program Memory Size256KB (256K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K × 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type64-LQFPSuppler Device Package64-LQFP (10x10)                                                                                                                                                                                                                                       | Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                                                                                                                                        | Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Program Memory TypeFLASHEEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                             | Number of I/O              | 52                                                                    |

| EEPROM Size-RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                   | Program Memory Size        | 256KB (256K x 8)                                                      |

| RAM Size32K x 8Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                 | Program Memory Type        | FLASH                                                                 |

| Voltage - Supply (Vcc/Vdd)2V ~ 3.6VData ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                | EEPROM Size                | -                                                                     |

| Data ConvertersA/D 1x12b, 1x16b; D/A 1x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                   | RAM Size                   | 32K x 8                                                               |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                             | Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                                                    | Data Converters            | A/D 1x12b, 1x16b; D/A 1x12b                                           |

| Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Oscillator Type            | Internal                                                              |

| Package / Case     64-LQFP       Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mounting Type              | Surface Mount                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Package / Case             | 64-LQFP                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f372rct6                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Supplier Device Package    | 64-LQFP (10x10)                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f372rct6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction                                                                           |

|---|-------|-----------------------------------------------------------------------------------|

| 2 | Desc  | ription                                                                           |

| 3 | Func  | tional overview                                                                   |

|   | 3.1   | ARM® Cortex <sup>TM</sup> -M4F core with embedded Flash and SRAM $\dots \dots 12$ |

|   | 3.2   | Memory protection unit                                                            |

|   | 3.3   | Embedded Flash memory 13                                                          |

|   | 3.4   | Cyclic redundancy check (CRC) calculation unit                                    |

|   | 3.5   | Embedded SRAM                                                                     |

|   | 3.6   | Boot modes                                                                        |

|   | 3.7   | Power management                                                                  |

|   |       | 3.7.1 Power supply schemes                                                        |

|   |       | 3.7.2 Power supply supervisor                                                     |

|   |       | 3.7.3 Voltage regulator                                                           |

|   |       | 3.7.4 Low-power modes                                                             |

|   | 3.8   | Clocks and startup                                                                |

|   | 3.9   | General-purpose input/outputs (GPIOs)                                             |

|   | 3.10  | Direct memory access (DMA) 16                                                     |

|   | 3.11  | Interrupts and events 16                                                          |

|   |       | 3.11.1 Nested vectored interrupt controller (NVIC)                                |

|   |       | 3.11.2 Extended interrupt/event controller (EXTI)                                 |

|   | 3.12  | 12-bit analog-to-digital converter (ADC) 17                                       |

|   |       | 3.12.1 Temperature sensor                                                         |

|   |       | 3.12.2 Internal voltage reference (V <sub>REFINT</sub> )                          |

|   |       | 3.12.3 V <sub>BAT</sub> battery voltage monitoring                                |

|   | 3.13  | 16-bit sigma delta analog-to-digital converters (SDADC) 18                        |

|   | 3.14  | Digital-to-analog converter (DAC) 19                                              |

|   | 3.15  | Fast comparators (COMP)    19                                                     |

|   | 3.16  | Touch sensing controller (TSC) 20                                                 |

|   | 3.17  | Timers and watchdogs 21                                                           |

|   |       | 3.17.1 General-purpose timers (TIM2 to TIM5, TIM12 to TIM17, TIM19) 22            |

## **3** Functional overview

## **3.1** ARM<sup>®</sup> Cortex<sup>™</sup>-M4F core with embedded Flash and SRAM

The ARM Cortex-M4F processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM Cortex-M4F 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded ARM core, the STM32F37x family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the STM32F37x family.

## 3.2 Memory protection unit

The memory protection unit (MPU) is used to separate the processing of tasks from the data protection. The MPU can manage up to 8 protection areas that can all be further divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The memory protection unit is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

The Cortex-M4F processor is a high performance 32-bit processor designed for the microcontroller market. It offers significant benefits to developers, including:

- Outstanding processing performance combined with fast interrupt handling

- Enhanced system debug with extensive breakpoint and trace capabilities

- Efficient processor core, system and memories

- Ultralow power consumption with integrated sleep modes

- Platform security robustness with optional integrated memory protection unit (MPU).

With its embedded ARM core, the STM32F37x devices are compatible with all ARM development tools and software.

## 3.7 Power management

### 3.7.1 **Power supply schemes**

- $V_{DD}$ : external power supply for I/Os and the internal regulator. It is provided externally through  $V_{DD}$  pins, and can be 2.0 to 3.6 V.

- V<sub>DDA</sub> = 2.0 to 3.6 V:

- external analog power supplies for Reset blocks, RCs and PLL

- supply voltage for 12-bit ADC, DACs and comparators (minimum voltage to be applied to V<sub>DDA</sub> is 2.4 V when the 12-bit ADC and DAC are used).

- V<sub>DDSD12</sub> and V<sub>DDSD3</sub> = 2.2 to 3.6 V: supply voltages for SDADC1/2 and SDADCD3 sigma delta ADCs. Independent from V<sub>DD</sub>/V<sub>DDA</sub>.

- $V_{BAT} = 1.65$  to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers when V<sub>DD</sub> is not present.

### 3.7.2 Power supply supervisor

- The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when VDD is below a specified threshold, VPOR/PDR, without the need for an external reset circuit. The POR monitors only the V<sub>DD</sub> supply voltage. During the startup phase it is required that V<sub>DDA</sub> should arrive first and be greater than or equal to V<sub>DD</sub>.

- The PDR monitors both the V<sub>DD</sub> and V<sub>DDA</sub> supply voltages, however the V<sub>DDA</sub> power supply supervisor can be disabled (by programming a dedicated Option bit) to reduce the power consumption if the application design ensures that V<sub>DDA</sub> is higher than or equal to V<sub>DD</sub>.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}$  power supply and compares it to the VPVD threshold. An interrupt can be generated when  $V_{DD}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 3.7.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR), and power-down.

- The MR mode is used in the nominal regulation mode (Run)

- The LPR mode is used in Stop mode.

- The power-down mode is used in Standby mode: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The voltage regulator is always enabled after reset. It is disabled in Standby mode.

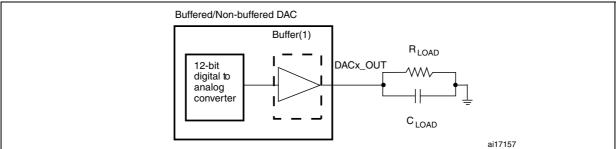

## 3.14 Digital-to-analog converter (DAC)

The devices feature up to two 12-bit buffered DACs with three output channels that can be used to convert three digital signals into three analog voltage signal outputs. The internal structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital Interface supports the following features:

- Up to two DAC converters with three output channels:

- DAC1 with two output channels

- DAC2 with one output channel.

- 8-bit or 10-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- triangular-wave generation

- Dual DAC channel independent or simultaneous conversions (DAC1 only)

- DMA capability for each channel

- External triggers for conversion

## 3.15 Fast comparators (COMP)

The STM32F37x embeds up to 2 comparators with rail-to-rail inputs and high-speed output. The reference voltage can be internal or external (delivered by an I/O).

The threshold can be one of the following:

- DACs channel outputs

- External I/O

- Internal reference voltage (V\_{REFINT}) or submultiple (1/4 V\_{REFINT}, 1/2 V\_{REFINT} and 3/4 V\_{REFINT})

The comparators can be combined into a window comparator.

Both comparators can wake up the device from Stop mode and generate interrupts and breaks for the timers.

## 3.25 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

## 3.26 Embedded trace macrocell<sup>™</sup>

The ARM embedded trace macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F37x through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

| Pin Name | AF0 | AF1      | AF2          | AF3        | AF4 | AF5                | AF6                | AF7       |

|----------|-----|----------|--------------|------------|-----|--------------------|--------------------|-----------|

| PC0      |     | EVENTOUT | TIM5_CH1_ETR |            |     |                    |                    |           |

| PC1      |     | EVENTOUT | TIM5_CH2     |            |     |                    |                    |           |

| PC2      |     | EVENTOUT | TIM5_CH3     |            |     | SPI2_MISO/I2S2_MCK |                    |           |

| PC3      |     | EVENTOUT | TIM5_CH4     |            |     | SPI2_MOSI/I2S2_SD  |                    |           |

| PC4      |     | EVENTOUT | TIM13_CH1    | TSC_G3_IO1 |     |                    |                    | USART1_TX |

| PC5      |     | EVENTOUT |              | TSC_G3_IO2 |     |                    |                    | USART1_R> |

| PC6      |     | EVENTOUT | TIM3_CH1     |            |     | SPI1_NSS/I2S1_WS   |                    |           |

| PC7      |     | EVENTOUT | TIM3_CH2     |            |     | SPI1_SCK/I2S1_CK   |                    |           |

| PC8      |     | EVENTOUT | TIM3_CH3     |            |     | SPI1_MISO/I2S1_MCK |                    |           |

| PC9      |     | EVENTOUT | TIM3_CH4     |            |     | SPI1_MOSI/I2S1_SD  |                    |           |

| PC10     |     | EVENTOUT | TIM19_CH1    |            |     |                    | SPI3_SCK/I2S3_CK   | USART3_T> |

| PC11     |     | EVENTOUT | TIM19_CH2    |            |     |                    | SPI3_MISO/I2S3_MCK | USART3_R  |

| PC12     |     | EVENTOUT | TIM19_CH3    |            |     |                    | SPI3_MOSI/I2S3_SD  | USART3_Cł |

| PC13     |     |          |              |            |     |                    |                    |           |

| PC14     |     |          |              |            |     |                    |                    |           |

| PC15     |     | 1        |              |            |     |                    |                    |           |

Table 14 Alternate functions for port PC

S

#### **Memory mapping** 5

Doc ID 022691 Rev 3

| Bus    | Boundary address          | Size | Peripheral |

|--------|---------------------------|------|------------|

|        | 0x4000 5800 - 0x4000 5BFF | 1 KB | I2C2       |

|        | 0x4000 5400 - 0x4000 57FF | 1 KB | I2C1       |

|        | 0x4000 4C00 - 0x4000 53FF | 2 KB | Reserved   |

|        | 0x4000 4800 - 0x4000 4BFF | 1 KB | USART3     |

|        | 0x4000 4400 - 0x4000 47FF | 1 KB | USART2     |

|        | 0x4000 4000 - 0x4000 43FF | 1 KB | Reserved   |

|        | 0x4000 3C00 - 0x4000 3FFF | 1 KB | SPI3/I2S3  |

|        | 0x4000 3800 - 0x4000 3BFF | 1 KB | SPI2/I2S2  |

|        | 0x4000 3400 - 0x4000 37FF | 1 KB | Reserved   |

|        | 0x4000 3000 - 0x4000 33FF | 1 KB | IWWDG      |

| APB1   | 0x4000 2C00 - 0x4000 2FFF | 1 KB | WWDG       |

| 7.1 01 | 0x4000 2800 - 0x4000 2BFF | 1 KB | RTC        |

|        | 0x4000 2400 - 0x4000 27FF | 1 KB | Reserved   |

|        | 0x4000 2000 - 0x4000 23FF | 1 KB | TIM14      |

|        | 0x4000 1C00 - 0x4000 1FFF | 1 KB | TIM13      |

|        | 0x4000 1800 - 0x4000 1BFF | 1 KB | TIM12      |

|        | 0x4000 1400 - 0x4000 17FF | 1 KB | TIM7       |

|        | 0x4000 1000 - 0x4000 13FF | 1 KB | TIM6       |

|        | 0x4000 0C00 - 0x4000 0FFF | 1 KB | TIM5       |

|        | 0x4000 0800 - 0x4000 0BFF | 1 KB | TIM4       |

|        | 0x4000 0400 - 0x4000 07FF | 1 KB | ТІМЗ       |

|        | 0x4000 0000 - 0x4000 03FF | 1 KB | TIM2       |

### Table 18. STM32F37x peripheral register boundary addresses (continued)

Depending on the SDADCx operation mode, there can be more constraints between  $V_{\text{REFSD+}}$ ,  $V_{\text{DDSD12}}$  and  $V_{\text{DDSD3}}$  which are described in reference manual RM0313.

Table 20.Current characteristics

| Symbol                | Ratings                                                                           | Max.  | Unit |

|-----------------------|-----------------------------------------------------------------------------------|-------|------|

| $I_{VDD(\Sigma)}$     | Total current into sum of all VDD_x and VDDSDx power lines $(source)^{(1)}$       | 160   |      |

| $I_{VSS(\Sigma)}$     | Total current out of sum of all VSS_x and VSSSD ground lines $({\rm sink})^{(1)}$ | -160  |      |

| I <sub>VDD(PIN)</sub> | Maximum current into each VDD_x or VDDSDx power pin (source) <sup>(1)</sup>       | 100   |      |

| I <sub>VSS(PIN)</sub> | Maximum current out of each VSS_x or VSSSD ground pin $(sink)^{(1)}$              | -100  |      |

|                       | Output current sunk by any I/O and control pin                                    | 25    |      |

| I <sub>IO(PIN)</sub>  | Output current source by any I/O and control pin                                  | - 25  | mA   |

| ΣI                    | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>       | 80    |      |

| $\Sigma I_{IO(PIN)}$  | Total output current sourced by sum of all IOs and control pins <sup>(2)</sup>    | -80   |      |

|                       | Injected current on FT, FTf and B pins <sup>(3)</sup>                             | -5/+0 |      |

| I <sub>INJ(PIN)</sub> | Injected current on TC and RST pin <sup>(4)</sup>                                 | ± 5   |      |

|                       | Injected current on TTa pins <sup>(5)</sup>                                       | ± 5   |      |

| $\Sigma I_{INJ(PIN)}$ | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>           | ± 25  |      |

VDDSD12 is the external power supply for PB2, PB10, and PE7 to PE15 I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>). VDDSD3 is the external power supply for PB14 to PB15 and PD8 to PD15 I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>). V<sub>DD</sub> (VDD\_x) is the external power supply for all remaining I/O pins (the I/O pin ground is internally connected to V<sub>SS</sub>).

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

- A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 19: Voltage characteristics* for the maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub>>V<sub>DDA</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ</sub>(PIN) must never be exceeded. Refer also to *Table 19: Voltage characteristics* for the maximum allowed input voltage values. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 62*.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

Table 21.Thermal characteristics

# 6.3 Operating conditions

## 6.3.1 General operating conditions

## Table 22. General operating conditions

| Symbol                          | Parameter                                                                                | Conditions                                                                | Min   | Max                         | Unit |

|---------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------|-----------------------------|------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                                             |                                                                           | 0     | 72                          |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                                            |                                                                           | 0     | 36                          | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                                            |                                                                           | 0     | 72                          |      |

| $V_{DD}$                        | Standard operating voltage                                                               | Must have a potential equal to or lower than $V_{\mbox{\scriptsize DDA}}$ | 2     | 3.6                         | V    |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC and DAC used)                                           | Must have a potential equal                                               | 2.4   | 3.6                         | v    |

| V DDA`´                         | Analog operating voltage<br>(ADC and DAC not used)                                       | to or higher than V <sub>DD</sub>                                         | 2     | 3.6                         | v    |

| N/                              | VDDSD12 operating voltage<br>(SDADC used)                                                | Must have a potential equal                                               | 2.2   | 3.6                         | v    |

| V <sub>DDSD12</sub>             | VDDSD12 operating voltage<br>(SDADC not used)                                            | to or lower than V <sub>DDA</sub>                                         | 2.0   | 3.6                         | v    |

| V                               | VDDSD3 operating voltage<br>(SDADC used)                                                 | Must have a potential equal                                               | 2.2   | 3.6                         | v    |

| V <sub>DDSD3</sub>              | VDDSD3 operating voltage<br>(SDADC not used)                                             |                                                                           |       | 3.6                         | v    |

| V <sub>BAT</sub>                | Backup operating voltage                                                                 |                                                                           | 1.65  | 3.6                         | V    |

|                                 | Input voltage on FT and FTf pins <sup>(2)</sup>                                          |                                                                           | - 0.3 | 5.5                         |      |

|                                 | Input voltage on TTa pins                                                                |                                                                           | - 0.3 | V <sub>DDA</sub> + 0.3      |      |

| V <sub>IN</sub>                 | Input voltage on TC pins on SDADCx channels inputs <sup>(3)</sup>                        |                                                                           | - 0.3 | V <sub>DDSDx</sub><br>+ 0.3 | V    |

|                                 | Input voltage on BOOT0 pin                                                               |                                                                           | 0     | 5.5                         |      |

|                                 | Input voltage on any other pin                                                           |                                                                           | - 0.3 | V <sub>DD</sub> +<br>0.3    |      |

|                                 |                                                                                          | LQFP100                                                                   |       | 434                         |      |

| Р                               | Power dissipation at $T_A = 85 \text{ °C}$<br>for suffix 6 or $T_A = 105 \text{ °C}$ for | LQFP64                                                                    |       | 444                         | m\\/ |

| P <sub>D</sub>                  | suffix $7^{(4)}$                                                                         | LQFP48                                                                    |       | 364                         | mW   |

|                                 |                                                                                          | BGA100                                                                    |       | 338                         |      |

|                                 | Ambient temperature for 6 suffix                                                         | Maximum power dissipation                                                 | -40   | 85                          | °C   |

| Та                              | version                                                                                  | Low power dissipation <sup>(5)</sup>                                      | -40   | 105                         |      |

| IA IA                           | Ambient temperature for 7 suffix                                                         | Maximum power dissipation                                                 | -40   | 105                         | °C   |

|                                 | version                                                                                  | Low power dissipation <sup>(5)</sup>                                      | -40   | 125                         |      |

|                                               |                                                                                |                                                              |                   | 1                      |                         |      |

|-----------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol                                        | Parameter                                                                      | Conditions                                                   | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Unit |

|                                               |                                                                                |                                                              | 72 MHz            | 61.4                   | 28.8                    |      |

|                                               |                                                                                |                                                              | 64 MHz            | 55.4                   | 25.9                    |      |

|                                               |                                                                                | Running from HSE crystal clock 8 MHz,                        | 48 MHz            | 42.3                   | 20.0                    |      |

|                                               |                                                                                | code executing from                                          | 32 MHz            | 28.7                   | 13.8                    |      |

|                                               |                                                                                | Flash, PLL on                                                | 24 MHz            | 21.9                   | 10.7                    |      |

|                                               | Supply current in<br>Run mode from                                             |                                                              | 16 MHz            | 14.8                   | 7.4                     |      |

| I <sub>DD</sub>                               | V <sub>DD</sub> supply                                                         |                                                              | 8 MHz             | 7.8                    | 4.1                     | mA   |

|                                               |                                                                                | Duration from UCE                                            | 4 MHz             | 4.6                    | 2.6                     |      |

|                                               |                                                                                | Running from HSE crystal clock 8 MHz,                        | 2 MHz             | 2.9                    | 1.8                     |      |

|                                               |                                                                                | code executing from<br>Flash, PLL off                        | 1 MHz             | 2.0                    | 1.3                     |      |

|                                               |                                                                                | FIASH, FLL OII                                               | 500 kHz           | 1.5                    | 1.1                     |      |

|                                               |                                                                                |                                                              | 125 kHz           | 1.2                    | 1.0                     |      |

|                                               |                                                                                |                                                              | 72 MHz            | 243.3                  | 242.4                   |      |

|                                               |                                                                                | Running from HSE                                             | 64 MHz            | 214.3                  | 213.3                   |      |

|                                               |                                                                                | crystal clock 8 MHz,<br>code executing from<br>Flash, PLL on | 48 MHz            | 159.3                  | 158.3                   |      |

|                                               |                                                                                |                                                              | 32 MHz            | 107.7                  | 107.3                   |      |

|                                               |                                                                                |                                                              | 24 MHz            | 82.8                   | 82.6                    |      |

| I <sub>DDA</sub> <sup>(1)(2)</sup>            | Supply current in<br>Run mode from                                             |                                                              | 16 MHz            | 58.4                   | 58.2                    |      |

| 'DDA                                          | V <sub>DDA</sub> supply                                                        |                                                              | 8 MHz             | 1.2                    | 1.2                     |      |

|                                               |                                                                                | Running from HSE                                             | 4 MHz             | 1.2                    | 1.2                     | μA   |

|                                               |                                                                                | crystal clock 8 MHz,                                         | 2 MHz             | 1.2                    | 1.2                     |      |

|                                               |                                                                                | code executing from<br>Flash, PLL off                        | 1 MHz             | 1.2                    | 1.2                     |      |

|                                               |                                                                                |                                                              | 500 kHz           | 1.2                    | 1.2                     |      |

|                                               |                                                                                |                                                              | 125 kHz           | 1.2                    | 1.2                     |      |

| I <sub>SDADC12</sub> +<br>I <sub>SDADC3</sub> | Supply currents in Run mode from $V_{DDSD12}$ and $V_{DDSD3}$ (SDADCs are off) |                                                              | -                 | 2.5                    | 1                       |      |

# Table 33.Typical current consumption in Run mode, code with data processing running from<br/>Flash

1.  $V_{DDA}$  monitoring is off,  $V_{DDSD12}$  monitoring is off.

2. When peripherals are enabled, power consumption of the analog part of peripherals such as ADC, DACs, Comparators, etc. is not included. Refer to those peripherals characteristics in the subsequent sections.

### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 52: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC and SDADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode. Under reset conditions all I/Os are configured in input floating mode - so if some inputs do not have a defined voltage level then they can generate additional consumption. This consumption is visible on V<sub>DD</sub> supply and also on V<sub>DDSDx</sub> supply because some I/Os are powered from SDADCx supply (all I/Os which have SDADC analog input functionality).

### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 36: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load  $V_{\text{DD}}$  is the MCU supply voltage

f<sub>SW</sub> is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$ +  $C_S$

$C_S$  is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 53* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*. All I/Os are CMOS and TTL compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                               | Conditions                                                  | Min                  | Max | Unit |

|-----------------------------------|---------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                 | CMOS port <sup>(3)</sup>                                    | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                 | TTL port <sup>(3)</sup>                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                  | -   |      |

| V <sub>OL</sub> <sup>(2)(5)</sup> | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +20 mA                                    | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(4)(5)</sup> | Output high level voltage for an I/O pin                | 2.7 V < V <sub>DD</sub> < 3.6 V                             | V <sub>DD</sub> -1.3 | -   |      |

| V <sub>OL</sub> <sup>(2)(5)</sup> | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +6 mA                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(4)(5)</sup> | Output high level voltage for an I/O pin                | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OLFM+</sub> <sup>(2)</sup> | Output low level voltage for a FTf I/O pins in FM+ mode | I <sub>IO</sub> = +20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | -                    | 0.4 |      |

Table 53. Output voltage characteristics <sup>(1)</sup>

VDDSD12 is the external power supply for PB2, PB10, and PE7 to PE15 I/O pins (the I/O ground pin is internally connected to VSS). VDDSD3 is the external power supply for PB14 to PB15 and PD8 to PD15 I/O pins (the I/O ground pin is internally connected to VSS). For those pins all V<sub>DD</sub> supply references in this table are related to their given VDDSDx power supply.

2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 20* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

3. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

4. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 20* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

5. Data based on design simulation.

### Note:

I/O pins are powered from V<sub>DD</sub> voltage except pins which can be used as SDADC inputs:

- PB2, PB10 and PE7 to PE15 I/O pins are powered from VDDSD12.

- PB14 to PB15 and PD8 to PD15 I/O pins are powered from VDDSD3. All I/O pin ground is internally connected to  $V_{SS}$ .

$V_{DD}$  mentioned in the Table 53 represents power voltage for a given I/O pin (VDD or VDDSD12 or VDDSD3).

## 6.3.16 Communications interfaces

### I<sup>2</sup>C interface characteristics

Unless otherwise specified, the parameters given in *Table 56* are derived from tests performed under ambient temperature,  $f_{PCLK1}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

The I<sup>2</sup>C interface meets the requirements of the standard I<sup>2</sup>C communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" opendrain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 56*. Refer also to *Section 6.3.14: I/O port characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standard mode    |                     | Fast m           | ode                | Fast mode Plus   |                    | Unit |

|--------------------------------------------|-----------------------------------------|------------------|---------------------|------------------|--------------------|------------------|--------------------|------|

| Symbol                                     | Parameter                               | Min              | Max                 | Min              | Max                | Min              | Max                | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7              |                     | 1.3              |                    | 0.5              |                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0              |                     | 0.6              |                    | 0.26             |                    | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250              |                     | 100              |                    | 50               |                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(2)</sup> | 3450 <sup>(3)</sup> | 0 <sup>(2)</sup> | 900 <sup>(3)</sup> | 0 <sup>(4)</sup> | 450 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                  | 1000                |                  | 300                |                  | 120                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                  | 300                 |                  | 300                |                  | 120                |      |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0              |                     | 0.6              |                    | 0.26             |                    |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7              |                     | 0.6              |                    | 0.26             |                    | μs   |

| t <sub>su(STO)</sub>                       | Stop condition setup time               | 4.0              |                     | 0.6              |                    | 0.26             |                    | μs   |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7              |                     | 1.3              |                    | 0.5              |                    | μS   |

| C <sub>b</sub>                             | Capacitive load for each bus line       |                  | 400                 |                  | 400                |                  | 550                | pF   |

### Table 56. $I^2C$ characteristics<sup>(1)</sup>

The I<sup>2</sup>C characteristics are the requirements from I<sup>2</sup>C bus specification rev03. They are guaranteed by design when I2Cx\_TIMING register is correctly programmed (Refer to reference manual). These characteristics are not tested in production.

2. The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The device must internally provide a hold time of at least 120ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

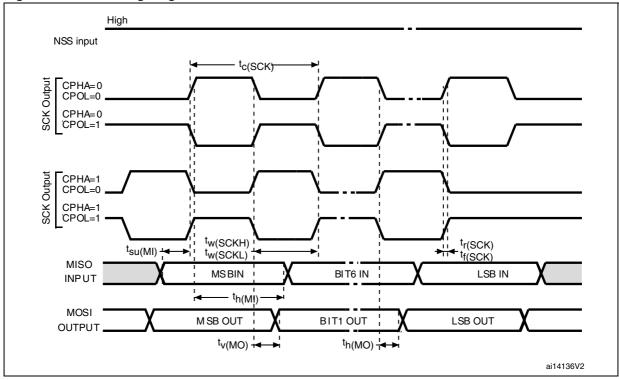

Figure 26. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at  $0.5V_{DD}$  level and with external  $C_L$  = 30 pF.

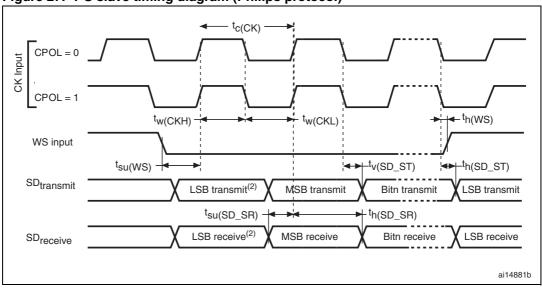

Figure 27. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at  $0.5V_{DD}$  level and with external C<sub>L</sub> = 30 pF.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

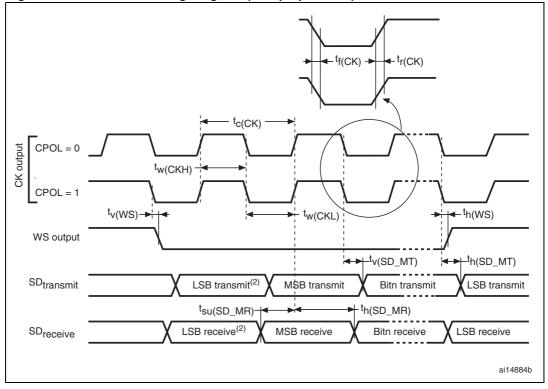

### Figure 28. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at  $0.5V_{DD}$  level and with external C<sub>L</sub> = 30 pF.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

## 6.3.18 DAC electrical specifications

| Table 63. DAC characteristics | Table 63. | DAC characteristics |

|-------------------------------|-----------|---------------------|

|-------------------------------|-----------|---------------------|

| Symbol                           | Parameter                                                                                                    | Min | Тур | Max                      | Unit         | Comments                                                                                                                       |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                 | Analog supply voltage                                                                                        | 2.4 | -   | 3.6                      | V            |                                                                                                                                |

| V <sub>REF+</sub>                | Reference supply voltage                                                                                     | 2.4 | -   | 3.6                      | V            | $V_{REF+}$ must always be below $V_{DDA}$                                                                                      |

| V <sub>SSA</sub>                 | Ground                                                                                                       | 0   | -   | 0                        | V            |                                                                                                                                |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer ON                                                                                | 5   | -   |                          | kΩ           |                                                                                                                                |

| R <sub>O</sub> <sup>(1)</sup>    | Impedance output with buffer<br>OFF                                                                          | -   | -   | 15                       |              | When the buffer is OFF, the Minimum resistive load between DAC_OUT and V <sub>SS</sub> to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | -   | -   | 50                       | pF           | Maximum capacitive load at<br>DAC_OUT pin (when the buffer is<br>ON).                                                          |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                        | V            | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input code                                    |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> – 0.2   | v            | (0x0E0) to (0xF1C) at $V_{REF+} = 3.6 V$<br>and (0x155) and (0xEAB) at $V_{REF+} = 2.4 V$                                      |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 |                          | mV           | It gives the maximum output                                                                                                    |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage<br>with buffer OFF                                                                    | -   |     | V <sub>REF+</sub> – 1LSB | V            | excursion of the DAC.                                                                                                          |

| I <sub>DDVREF+</sub> (3)         | DAC DC current<br>consumption in quiescent<br>mode (Standby mode)                                            | -   |     | 220                      |              | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs                   |

|                                  | DAC DC current                                                                                               | -   |     | 380                      | μA           | With no load, middle code (0x800) on the inputs                                                                                |

| I <sub>DDA</sub> <sup>(3)</sup>  | consumption in quiescent<br>mode <sup>(2)</sup>                                                              | -   |     | 480                      | μA           | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs                   |

| DNL <sup>(3)</sup>               | Differential non linearity<br>Difference between two                                                         | -   |     | ±0.5                     | LSB          | Given for the DAC in 10-bit configuration                                                                                      |

|                                  | consecutive code-1LSB)                                                                                       | -   |     | ±2                       | LSB          | Given for the DAC in 12-bit configuration                                                                                      |

|                                  | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                       |              | Given for the DAC in 10-bit configuration                                                                                      |

| INL <sup>(3)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                       | $1 \times R$ | Given for the DAC in 12-bit configuration                                                                                      |

| Symbol                               | Parameter                                                                                                                                                          | Min | Тур | Max  | Unit | Comments                                                                                                                        |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------|

| Offset <sup>(3)</sup>                | Offset error                                                                                                                                                       | -   | -   | ±10  | mV   |                                                                                                                                 |

|                                      | (difference between<br>measured value at Code<br>(0x800) and the ideal value =<br>$V_{REF+}/2$ )                                                                   | -   | -   | ±3   |      | Given for the DAC in 10-bit at V <sub>REF+</sub><br>= 3.6 V                                                                     |

|                                      |                                                                                                                                                                    | -   | -   | ±12  | LSB  | Given for the DAC in 12-bit at V <sub>REF+</sub><br>= 3.6 V                                                                     |

| Gain<br>error <sup>(3)</sup>         | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12bit configuration                                                                                        |

| <sup>t</sup> settling <sup>(3)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | -   | 3   | 4    | μs   | $C_{LOAD} \leq 50$ pF, $R_{LOAD} \geq 5$ k $\Omega$                                                                             |

| Update<br>rate <sup>(3)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | $C_{LOAD} \leq 50 \text{ pF, } R_{LOAD} \geq 5 \text{ k}\Omega$                                                                 |

| t <sub>wakeup</sub> (3)              | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50 \text{ pF}, \text{ R}_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and<br>highest possible ones. |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement                                                                                   | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                                |

Table 63. DAC characteristics (continued)

1. Guaranteed by design, not tested in production.

2. Quiescent mode refers to the state of the DAC keeping a steady value on the output, so no dynamic consumption is involved.

3. Guaranteed by characterization, not tested in production.

| Figure 31. | 12-bit buffered /non-buffered DAC |

|------------|-----------------------------------|

|------------|-----------------------------------|

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

## 6.3.19 Comparator characteristics

Table 64. Comparator characteristics

| Symbol                   | Parameter                                                         | Conditions                                            |                     |  | Тур | Max <sup>(1)</sup> | Unit  |

|--------------------------|-------------------------------------------------------------------|-------------------------------------------------------|---------------------|--|-----|--------------------|-------|

| V <sub>DDA</sub>         | Analog supply voltage                                             |                                                       |                     |  |     | 3.6                |       |

| V <sub>IN</sub>          | Comparator input voltage range                                    |                                                       |                     |  |     | V <sub>DDA</sub>   | v     |

| V <sub>BG</sub>          | Scaler input voltage                                              |                                                       |                     |  | 1.2 |                    |       |

| V <sub>SC</sub>          | Scaler offset voltage                                             |                                                       |                     |  | ±5  | ±10                | mV    |

| t <sub>S_SC</sub>        | Scaler startup time from power down                               |                                                       |                     |  |     | 0.1                | ms    |

| t <sub>START</sub>       | Comparator startup time                                           | Startup time to reach propagation delay specification |                     |  |     | 60                 | μs    |

|                          |                                                                   | Ultra-low power mode                                  |                     |  | 2   | 4.5                |       |

|                          | Propagation delay for<br>200 mV step with 100 mV<br>overdrive     | Low power mode                                        |                     |  | 0.7 | 1.5                | μs    |

|                          |                                                                   | Medium power mode                                     |                     |  | 0.3 | 0.6                |       |

|                          |                                                                   |                                                       | $V_{DDA} \ge 2.7 V$ |  | 50  | 100                |       |

| +                        |                                                                   | High speed mode $V_{DDA} < 2.7 V$                     |                     |  | 100 | 240                | ns    |

| t <sub>D</sub>           | Propagation delay for full<br>range step with 100 mV<br>overdrive | Ultra-low power mode                                  |                     |  | 2   | 7                  |       |

|                          |                                                                   | Low power mode                                        |                     |  | 0.7 | 2.1                | μs    |

|                          |                                                                   | Medium power mode                                     |                     |  | 0.3 | 1.2                |       |

|                          |                                                                   | High speed mode                                       | $V_{DDA} \ge 2.7 V$ |  | 90  | 180                | ns    |

|                          |                                                                   | r light speed mode                                    | $V_{DDA}$ < 2.7 V   |  | 110 | 300                |       |

| V <sub>offset</sub>      | Comparator offset error                                           |                                                       |                     |  | ±4  | ±10                | mV    |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient                              |                                                       |                     |  | 18  |                    | µV/°C |

|                          |                                                                   | Ultra-low power mode                                  |                     |  | 1.2 | 1.5                | μA    |

|                          | COMP current consumption                                          | Low power mode                                        |                     |  | 3   | 5                  |       |

| I <sub>DD(COMP)</sub>    |                                                                   | Medium power mode                                     |                     |  | 10  | 15                 |       |

|                          |                                                                   | High speed mode                                       |                     |  | 75  | 100                |       |

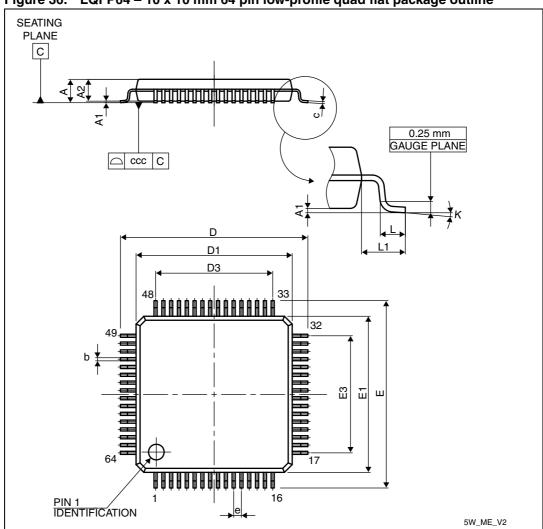

Figure 36. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 78. | LQFP64 – 10 x 10 mm low-profile quad flat package mechanical data | 3 |

|-----------|-------------------------------------------------------------------|---|

|-----------|-------------------------------------------------------------------|---|

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |  |

| А      |             |       | 1.60  |                       |        | 0.0630 |  |

| A1     | 0.05        |       | 0.15  | 0.0020                |        | 0.0059 |  |

| A2     | 1.350       | 1.40  | 1.45  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.17        | 0.22  | 0.27  | 0.0067                | 0.0087 | 0.0106 |  |

| с      | 0.09        |       | 0.20  | 0.0035                |        | 0.0079 |  |

| D      | 11.80       | 12.00 | 12.20 | 0.4646                | 0.4724 | 0.4803 |  |

| D1     | 9.80        | 10.00 | 10.20 | 0.3858                | 0.3937 | 0.4016 |  |

| D3     |             | 7.50  |       |                       | 0.2953 |        |  |