Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 84                                                                    |

| Program Memory Size        | 256КВ (256К х 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | <u>.</u>                                                              |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 1x12b, 1x16b; D/A 1x12b                                           |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-UFBGA                                                             |

| Supplier Device Package    | 100-UFBGA (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f372vch6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Do not reconfigure GPIO pins which are not present on 48 and 64 pin packages to the analog mode. Additional current consumption in the range of tens of  $\mu$ A per pin can be observed if V<sub>DDA</sub> is higher than V<sub>DDIO</sub>.

# 3.10 Direct memory access (DMA)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The two DMAs can be used with the main peripherals: SPIs, I2Cs, USARTs, DACs, ADC, SDADCs, general-purpose timers.

# 3.11 Interrupts and events

### 3.11.1 Nested vectored interrupt controller (NVIC)

The STM32F37x devices embed a nested vectored interrupt controller (NVIC) able to handle up to 60 maskable interrupt channels and 16 priority levels.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.11.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 29 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 84 GPIOs can be connected to the 16 external interrupt lines.

# 3.13 16-bit sigma delta analog-to-digital converters (SDADC)

Up to three 16-bit sigma-delta analog-to-digital converters are embedded in the STM32F37x. They have up to two separate supply voltages allowing the analog function voltage range to be independent from the STM32F37x power supply. They share up to 21 input pins which may be configured in any combination of single-ended (up to 21) or differential inputs (up to 11).

The conversion speed is up to 16.6 ksps for each SDADC when converting multiple channels and up to 50 ksps per SDADC if single channel conversion is used. There are two conversion modes: single conversion mode or continuous mode, capable of automatically scanning any number of channels. The data can be automatically stored in a system RAM buffer, reducing the software overhead.

A timer triggering system can be used in order to control the start of conversion of the three SDADCs and/or the 12-bit fast ADC. This timing control is very flexible, capable of triggering simultaneous conversions or inserting a programmable delay between the ADCs.

Up to two external reference pins (VREFSD+, VREFSD-) and an internal 1.2/1.8 V reference can be used in conjunction with a programmable gain (x0.5 to x32) in order to fine-tune the input voltage range of the SDADC.

# 3.16 Touch sensing controller (TSC)

The devices provide a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect the presence of a finger near an electrode which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the electrode capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

Up to 24 touch sensing electrodes can be controlled by the TSC. The touch sensing I/Os are organized in 8 acquisition groups, with up to 4 I/Os in each group.

| Group | Capacitive sensing signal name | Pin name | Group | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|----------|-------|--------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0      |       | TSC_G5_IO1                     | PB3         |

| 1     | TSC_G1_IO2                     | PA1      | 5     | TSC_G5_IO2                     | PB4         |

| 1     | TSC_G1_IO3                     | PA2      | 5     | TSC_G5_IO3                     | PB6         |

|       | TSC_G1_IO4                     | PA3      |       | TSC_G5_IO4                     | PB7         |

|       | TSC_G2_IO1                     | PA4      |       | TSC_G6_IO1                     | PB14        |

| 2     | TSC_G2_IO2                     | PA5      | 6     | TSC_G6_IO2                     | PB15        |

| 2     | TSC_G2_IO3                     | PA6      |       | TSC_G6_IO3                     | PD8         |

|       | TSC_G2_IO4                     | PA7      |       | TSC_G6_IO4                     | PD9         |

|       | TSC_G3_IO1                     | PC4      |       | TSC_G7_IO1                     | PE2         |

| 3     | TSC_G3_IO2                     | PC5      | 7     | TSC_G7_IO2                     | PE3         |

| 5     | TSC_G3_IO3                     | PB0      | /     | TSC_G7_IO3                     | PE4         |

|       | TSC_G3_IO4                     | PB1      |       | TSC_G7_IO4                     | PE5         |

|       | TSC_G4_IO1                     | PA9      |       | TSC_G8_IO1                     | PD12        |

| 4     | TSC_G4_IO2                     | PA10     | 8     | TSC_G8_IO2                     | PD13        |

| +     | TSC_G4_IO3                     | PA13     | 0     | TSC_G8_IO3                     | PD14        |

|       | TSC_G4_IO4                     | PA14     |       | TSC_G8_IO4                     | PD15        |

Table 3.

Capacitive sensing GPIOs available on STM32F37x devices

|                                       | Number of capacitive sensing channels |             |             |  |  |

|---------------------------------------|---------------------------------------|-------------|-------------|--|--|

| Analog I/O group                      | STM32F37xCx                           | STM32F37xRx | STM32F37xVx |  |  |

| G1                                    | 3                                     | 3           | 3           |  |  |

| G2                                    | 2                                     | 3           | 3           |  |  |

| G3                                    | 1                                     | 3           | 3           |  |  |

| G4                                    | 3                                     | 3           | 3           |  |  |

| G5                                    | 3                                     | 3           | 3           |  |  |

| G6                                    | 2                                     | 2           | 3           |  |  |

| G7                                    | 0                                     | 0           | 3           |  |  |

| G8                                    | 0                                     | 0           | 3           |  |  |

| Number of capacitive sensing channels | 14                                    | 17          | 24          |  |  |

Table 4.

No. of capacitive sensing channels available on STM32F37x devices

# 3.17 Timers and watchdogs

The STM32F37x includes two 32-bit and nine 16-bit general-purpose timers, three basic timers, two watchdog timers and a SysTick timer. The table below compares the features of the advanced control, general purpose and basic timers.

| Table 5. Timer feature compa | arison |

|------------------------------|--------|

|------------------------------|--------|

| Timer type          | Timer                   | Counter resolution | Counter<br>type      | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>Channels | Complementary outputs |

|---------------------|-------------------------|--------------------|----------------------|---------------------------------------|------------------------------|---------------------------------|-----------------------|

| General-<br>purpose | TIM2<br>TIM5            | 32-bit             | Up, Down,<br>Up/Down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | 0                     |

| General-<br>purpose | TIM3,<br>TIM4,<br>TIM19 | 16-bit             | Up, Down,<br>Up/Down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | 0                     |

| General-<br>purpose | TIM12                   | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | No                           | 2                               | 0                     |

| General-<br>purpose | TIM15                   | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 2                               | 1                     |

| General-<br>purpose | TIM13,<br>TIM14         | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | No                           | 1                               | 0                     |

# 3.20 Universal synchronous/asynchronous receiver transmitter (USART)

The STM32F37x embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3).

All USARTs interfaces are able to communicate at speeds of up to 9 Mbit/s.

They provide hardware management of the CTS and RTS signals, they support IrDA SIR ENDEC, the multiprocessor communication mode, the single-wire half-duplex communication mode, Smart Card mode (ISO 7816 compliant), autobaudrate feature and have LIN Master/Slave capability. The USART interfaces can be served by the DMA controller.

Refer to Table 8 for the features of USART1, USART2 and USART3.

| USART modes/features <sup>(1)</sup>         | USART1 | USART2 | USART3 |

|---------------------------------------------|--------|--------|--------|

| Hardware flow control for modem             | Х      | Х      | Х      |

| Continuous communication using DMA          | Х      | Х      | Х      |

| Multiprocessor communication                | Х      | Х      | Х      |

| Synchronous mode                            | Х      | Х      | Х      |

| Smartcard mode                              | Х      | Х      | Х      |

| Single-wire half-duplex communication       | Х      | Х      | Х      |

| IrDA SIR ENDEC block                        | Х      | Х      | Х      |

| LIN mode                                    | Х      | Х      | Х      |

| Dual clock domain and wakeup from Stop mode | Х      | Х      | Х      |

| Receiver timeout interrupt                  | Х      | Х      | Х      |

| Modbus communication                        | Х      | Х      | Х      |

| Auto baud rate detection                    | Х      | Х      | Х      |

| Driver Enable                               | Х      | Х      | Х      |

Table 8. STM32F37x USART implementation

1. X = supported.

# 3.21 Serial peripheral interface (SPI)/Inter-integrated sound interfaces (I<sup>2</sup>S)

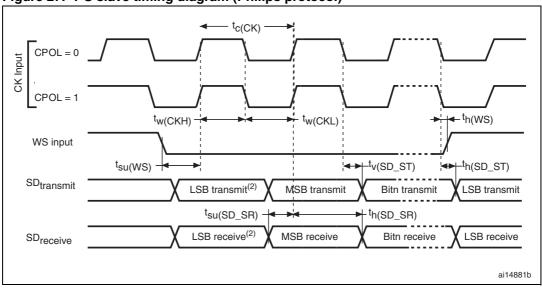

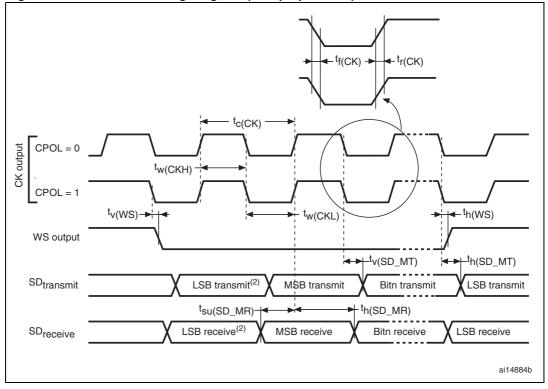

Up to three SPIs are able to communicate at up to 18 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The SPIs can be served by the DMA controller.

Three standard I<sup>2</sup>S interfaces (multiplexed with SPI1, SPI2 and SPI3) are available, that can be operated in master or slave mode. These interfaces can be configured to operate with 16/32 bit resolution, as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in

| Bus    | Boundary address          | Size | Peripheral |

|--------|---------------------------|------|------------|

|        | 0x4000 5800 - 0x4000 5BFF | 1 KB | I2C2       |

|        | 0x4000 5400 - 0x4000 57FF | 1 KB | I2C1       |

|        | 0x4000 4C00 - 0x4000 53FF | 2 KB | Reserved   |

|        | 0x4000 4800 - 0x4000 4BFF | 1 KB | USART3     |

|        | 0x4000 4400 - 0x4000 47FF | 1 KB | USART2     |

|        | 0x4000 4000 - 0x4000 43FF | 1 KB | Reserved   |

|        | 0x4000 3C00 - 0x4000 3FFF | 1 KB | SPI3/I2S3  |

|        | 0x4000 3800 - 0x4000 3BFF | 1 KB | SPI2/I2S2  |

|        | 0x4000 3400 - 0x4000 37FF | 1 KB | Reserved   |

|        | 0x4000 3000 - 0x4000 33FF | 1 KB | IWWDG      |

| APB1   | 0x4000 2C00 - 0x4000 2FFF | 1 KB | WWDG       |

| 7.1 01 | 0x4000 2800 - 0x4000 2BFF | 1 KB | RTC        |

|        | 0x4000 2400 - 0x4000 27FF | 1 KB | Reserved   |

|        | 0x4000 2000 - 0x4000 23FF | 1 KB | TIM14      |

|        | 0x4000 1C00 - 0x4000 1FFF | 1 KB | TIM13      |

|        | 0x4000 1800 - 0x4000 1BFF | 1 KB | TIM12      |

|        | 0x4000 1400 - 0x4000 17FF | 1 KB | TIM7       |

|        | 0x4000 1000 - 0x4000 13FF | 1 KB | TIM6       |

|        | 0x4000 0C00 - 0x4000 0FFF | 1 KB | TIM5       |

|        | 0x4000 0800 - 0x4000 0BFF | 1 KB | TIM4       |

|        | 0x4000 0400 - 0x4000 07FF | 1 KB | ТІМЗ       |

|        | 0x4000 0000 - 0x4000 03FF | 1 KB | TIM2       |

## Table 18. STM32F37x peripheral register boundary addresses (continued)

# 6.3 Operating conditions

# 6.3.1 General operating conditions

## Table 22. General operating conditions

| Symbol                          | Parameter                                                                                | Conditions                                                                | Min   | Max                         | Unit |  |

|---------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------|-----------------------------|------|--|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                                             |                                                                           | 0     | 72                          |      |  |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                                            |                                                                           | 0     | 36                          | MHz  |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                                            |                                                                           | 0     | 72                          |      |  |

| $V_{DD}$                        | Standard operating voltage                                                               | Must have a potential equal to or lower than $V_{\mbox{\scriptsize DDA}}$ | 2     | 3.6                         | V    |  |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC and DAC used)                                           | Must have a potential equal                                               | 2.4   | 3.6                         | v    |  |

| V DDA`´                         | Analog operating voltage<br>(ADC and DAC not used)                                       | to or higher than V <sub>DD</sub>                                         | 2     | 3.6                         | v    |  |

| N/                              | VDDSD12 operating voltage<br>(SDADC used)                                                | Must have a potential equal                                               | 2.2   | 3.6                         | v    |  |

| V <sub>DDSD12</sub>             | VDDSD12 operating voltage<br>(SDADC not used)                                            | to or lower than V <sub>DDA</sub>                                         | 2.0   | 3.6                         | v    |  |

| V                               | VDDSD3 operating voltage<br>(SDADC used)                                                 | Must have a potential equal                                               | 2.2   | 3.6                         | v    |  |

| V <sub>DDSD3</sub>              | VDDSD3 operating voltage<br>(SDADC not used)                                             | to or lower than V <sub>DDA</sub>                                         | 2.0   | 3.6                         | v    |  |

| V <sub>BAT</sub>                | Backup operating voltage                                                                 |                                                                           | 1.65  | 3.6                         | V    |  |

|                                 | Input voltage on FT and FTf pins <sup>(2)</sup>                                          |                                                                           | - 0.3 | 5.5                         |      |  |

|                                 | Input voltage on TTa pins                                                                |                                                                           | - 0.3 | V <sub>DDA</sub> + 0.3      |      |  |

| V <sub>IN</sub>                 | Input voltage on TC pins on SDADCx channels inputs <sup>(3)</sup>                        |                                                                           | - 0.3 | V <sub>DDSDx</sub><br>+ 0.3 | V    |  |

|                                 | Input voltage on BOOT0 pin                                                               |                                                                           | 0     | 5.5                         |      |  |

|                                 | Input voltage on any other pin                                                           |                                                                           | - 0.3 | V <sub>DD</sub> +<br>0.3    |      |  |

|                                 |                                                                                          | LQFP100                                                                   |       | 434                         |      |  |

| Р                               | Power dissipation at $T_A = 85 \text{ °C}$<br>for suffix 6 or $T_A = 105 \text{ °C}$ for | LQFP64                                                                    |       | 444                         | m\\/ |  |

| P <sub>D</sub>                  | suffix $7^{(4)}$                                                                         | LQFP48                                                                    |       | 364                         | mW   |  |

|                                 |                                                                                          | BGA100                                                                    |       | 338                         |      |  |

|                                 | Ambient temperature for 6 suffix                                                         | Maximum power dissipation                                                 | -40   | 85                          | °C   |  |

| Та                              | version                                                                                  | Low power dissipation <sup>(5)</sup>                                      | -40   | 105                         |      |  |

| IA IA                           | Ambient temperature for 7 suffix                                                         | Maximum power dissipation                                                 | -40   | 105                         | °C   |  |

|                                 | version                                                                                  | Low power dissipation <sup>(5)</sup>                                      | -40   | 125                         |      |  |

#### 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 24* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

| Symbol                               | Parameter                 | Conditions   | Min                | Тур  | Max  | Unit |

|--------------------------------------|---------------------------|--------------|--------------------|------|------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup>  | Power on/power down reset | Falling edge | 1.8 <sup>(2)</sup> | 1.88 | 1.96 | V    |

| V POR/PDR                            | threshold                 | Rising edge  | 1.84               | 1.92 | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(3)</sup>  | PDR hysteresis            |              |                    | 40   |      | mV   |

| t <sub>RSTTEMPO</sub> <sup>(3)</sup> | POR reset temporization   |              | 1.5                | 2.5  | 4.5  | ms   |

Table 24.

Embedded reset and power control block characteristics

1. The PDR detector monitors  $V_{DD}$ ,  $V_{DDA}$  and  $V_{DDSD12}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{DD}$ .

2. The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR/PDR}}$  value.

3. Guaranteed by design, not tested in production.

| Symbol                              | Parameter                         | Conditions   | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------------------|-----------------------------------|--------------|--------------------|------|--------------------|------|

| V                                   | PVD threshold 0                   | Rising edge  | 2.1                | 2.18 | 2.26               | V    |

| V <sub>PVD0</sub>                   |                                   | Falling edge | 2                  | 2.08 | 2.16               | V    |

| M                                   | PVD threshold 1                   | Rising edge  | 2.19               | 2.28 | 2.37               | V    |

| V <sub>PVD1</sub>                   |                                   | Falling edge | 2.09               | 2.18 | 2.27               | V    |

| V                                   | PVD threshold 2                   | Rising edge  | 2.28               | 2.38 | 2.48               | V    |

| V <sub>PVD2</sub>                   |                                   | Falling edge | 2.18               | 2.28 | 2.38               | V    |

| M                                   | PVD threshold 3                   | Rising edge  | 2.38               | 2.48 | 2.58               | V    |

| V <sub>PVD3</sub>                   |                                   | Falling edge | 2.28               | 2.38 | 2.48               | V    |

| M                                   | PVD threshold 4                   | Rising edge  | 2.47               | 2.58 | 2.69               | V    |

| V <sub>PVD4</sub>                   |                                   | Falling edge | 2.37               | 2.48 | 2.59               | V    |

| M                                   | PVD threshold 5                   | Rising edge  | 2.57               | 2.68 | 2.79               | V    |

| V <sub>PVD5</sub>                   |                                   | Falling edge | 2.47               | 2.58 | 2.69               | V    |

| M                                   | PVD threshold 6                   | Rising edge  | 2.66               | 2.78 | 2.9                | V    |

| V <sub>PVD6</sub>                   |                                   | Falling edge | 2.56               | 2.68 | 2.8                | V    |

| V                                   | V <sub>PVD7</sub> PVD threshold 7 | Rising edge  | 2.76               | 2.88 | 3                  | V    |

| V PVD7                              |                                   | Falling edge | 2.66               | 2.78 | 2.9                | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis                    |              |                    | 100  |                    | mV   |

| IDD(PVD) <sup>(2)</sup>             | PVD current consumption           |              |                    | 0.15 | 0.26               | μA   |

#### Table 25. Programmable voltage detector characteristics

1. Data based on characterization results only, not tested in production.

2. Guaranteed by design, not tested in production.

## 6.3.4 Embedded reference voltage

The parameters given in *Table 27* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

| Table 26. | Embedded internal reference voltage calibration values |

|-----------|--------------------------------------------------------|

|-----------|--------------------------------------------------------|

| Calibration value name | Description                                                              | Memory address            |

|------------------------|--------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 30 °C<br>V <sub>DDA</sub> = 3.3 V | 0x1FFF F7BA - 0x1FFF F7BB |

#### Table 27. Embedded internal reference voltage

| Symbol                                | Parameter                                                     | Conditions                        | Min  | Тур  | Max                 | Unit   |  |

|---------------------------------------|---------------------------------------------------------------|-----------------------------------|------|------|---------------------|--------|--|

| V                                     | Internal reference voltage                                    | −40 °C < T <sub>A</sub> < +105 °C | 1.16 | 1.21 | 1.26                | V      |  |

| V <sub>REFINT</sub>                   | Internal reference voltage                                    | −40 °C < T <sub>A</sub> < +85 °C  | 1.16 | 1.2  | 1.24 <sup>(1)</sup> | v      |  |

| T <sub>S_vrefint</sub> <sup>(2)</sup> | ADC sampling time when reading the internal reference voltage |                                   | 17.1 | -    | -                   | μs     |  |

| V <sub>REFINT_s</sub> <sup>(3)</sup>  | Internal reference voltage spread over the temperature range  | $V_{DD} = 3 V \pm 10 mV$          | -    |      | 10                  | mV     |  |

| T <sub>Coeff</sub> <sup>(3)</sup>     | Temperature coefficient                                       |                                   | -    |      | 100                 | ppm/°C |  |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                                  |                                   | -    |      | 10                  | μs     |  |

1. Data based on characterization results, not tested in production.

2. Shortest sampling time can be determined in the application by multiple iterations.

3. Guaranteed by design, not tested in production.

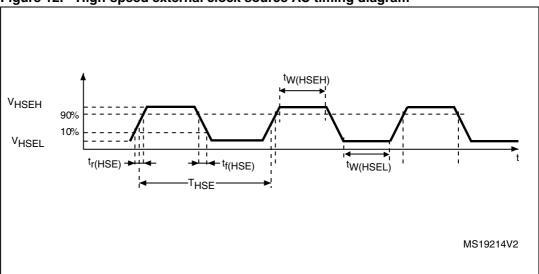

Figure 12. High-speed external clock source AC timing diagram

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 13*.

| Symbol                                       | Parameter <sup>(1)</sup>                | Conditions                  | Min                | Тур  | Мах                | Unit |

|----------------------------------------------|-----------------------------------------|-----------------------------|--------------------|------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User External clock source<br>frequency | al clock source 32.768 1000 |                    | 1000 | kHz                |      |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage   |                             | 0.7V <sub>DD</sub> |      | V <sub>DD</sub> V  |      |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage    |                             | $V_{SS}$           |      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time               |                             | 450                |      |                    |      |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time              |                             |                    |      | 50 ns              |      |

Table 39. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

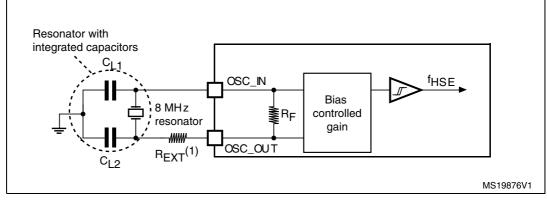

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 14*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

*Note:* For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

#### Table 50. Electrical sensitivities

| Symbol | Parameter             | Conditions                            | Class      |

|--------|-----------------------|---------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105$ °C conforming to JESD78A | II level A |

#### 6.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence or oscillator frequency deviation).

The test results are given in Table 51.

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 53* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22*. All I/Os are CMOS and TTL compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                               | Conditions                                                  | Min                  | Max | Unit |

|-----------------------------------|---------------------------------------------------------|-------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                 | CMOS port <sup>(3)</sup>                                    | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                 | TTL port <sup>(3)</sup>                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(4)</sup>    | Output high level voltage for an I/O pin                | I <sub>IO</sub> = +8 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V  | 2.4                  | -   |      |

| V <sub>OL</sub> <sup>(2)(5)</sup> | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +20 mA                                    | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(4)(5)</sup> | Output high level voltage for an I/O pin                | 2.7 V < V <sub>DD</sub> < 3.6 V                             | V <sub>DD</sub> -1.3 | -   |      |

| V <sub>OL</sub> <sup>(2)(5)</sup> | Output low level voltage for an I/O pin                 | I <sub>IO</sub> = +6 mA                                     | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(4)(5)</sup> | Output high level voltage for an I/O pin                | 2 V < V <sub>DD</sub> < 2.7 V                               | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OLFM+</sub> <sup>(2)</sup> | Output low level voltage for a FTf I/O pins in FM+ mode | I <sub>IO</sub> = +20 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | -                    | 0.4 |      |

Table 53. Output voltage characteristics <sup>(1)</sup>

VDDSD12 is the external power supply for PB2, PB10, and PE7 to PE15 I/O pins (the I/O ground pin is internally connected to VSS). VDDSD3 is the external power supply for PB14 to PB15 and PD8 to PD15 I/O pins (the I/O ground pin is internally connected to VSS). For those pins all V<sub>DD</sub> supply references in this table are related to their given VDDSDx power supply.

2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 20* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

3. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

4. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 20* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

5. Data based on design simulation.

#### Note:

I/O pins are powered from V<sub>DD</sub> voltage except pins which can be used as SDADC inputs:

- PB2, PB10 and PE7 to PE15 I/O pins are powered from VDDSD12.

- PB14 to PB15 and PD8 to PD15 I/O pins are powered from VDDSD3. All I/O pin ground is internally connected to  $V_{SS}$ .

$V_{DD}$  mentioned in the Table 53 represents power voltage for a given I/O pin (VDD or VDDSD12 or VDDSD3).

| Symbol          | Parameter                                                         | Min | Мах | Unit |

|-----------------|-------------------------------------------------------------------|-----|-----|------|

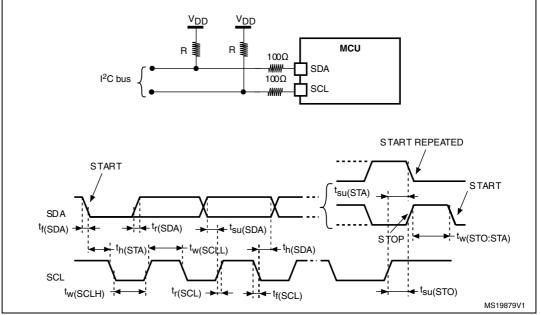

| t <sub>SP</sub> | Pulse width of spikes that are<br>suppressed by the analog filter | 50  | 260 | ns   |

#### Table 57. $I^2C$ analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 58* for SPI or in *Table 59* for  $I^2S$  are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*.

Refer to *Section 6.3.14: I/O port characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                                                     | Parameter                           | Conditions                                            | Min            | Max            | Unit |

|----------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------|----------------|----------------|------|

| f <sub>scк</sub>                                                           | SPI clock frequency                 | Master mode                                           |                | 18             | MHz  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> <sup>(1)</sup>                   | SFI Clock frequency                 | Slave mode                                            |                | 18             |      |

| <sup>t</sup> r(SCK)<br>t <sub>f(SCK)</sub> (1)                             | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            |                | 8              | ns   |

| DuCy(SCK) <sup>(1)</sup>                                                   | SPI slave input clock<br>duty cycle | Slave mode                                            | 30             | 70             | %    |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                                        | NSS setup time                      | Slave mode                                            | 2Tpclk         |                |      |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                                         | NSS hold time                       | Slave mode                                            | 4Tpclk         |                |      |

| t <sub>w(SCKH)</sub> <sup>(1)</sup><br>t <sub>w(SCKL)</sub> <sup>(1)</sup> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2<br>- 3 | Tpclk/2<br>+ 3 |      |

|                                                                            | Data input actus tima               | Master mode                                           | 5.5            |                |      |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)                         | Data input setup time               | Slave mode                                            | 6.5            |                |      |

| t <sub>h(MI)</sub> <sup>(1)</sup>                                          | Data input hald time                | Master mode                                           | 5              |                |      |

| t <sub>h(SI)</sub> <sup>(1)</sup>                                          | Data input hold time                | Slave mode                                            | 5              |                | ns   |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                                       | Data output access time             | Slave mode, f <sub>PCLK</sub> = 24 MHz                | 0              | 4Tpclk         |      |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>                                     | Data output disable time            | Slave mode                                            | 0              | 24             |      |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                          | Data output valid time              | Slave mode (after enable edge)                        |                | 39             | 1    |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                          | Data output valid time              | Master mode (after enable edge)                       |                | 3              | 1    |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                          | Data output hold time               | Slave mode (after enable edge)                        | 15             |                | 1    |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                          | Data output hold time               | Master mode (after enable edge)                       | 4              |                | 1    |

Table 58. SPI characteristics

1. Data based on characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

Figure 27. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at  $0.5V_{DD}$  level and with external C<sub>L</sub> = 30 pF.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Figure 28. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at  $0.5V_{DD}$  level and with external C<sub>L</sub> = 30 pF.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Symbol               | Parameter                        | Conditions                                                 | Min                                                       | Тур   | Max                             | Unit                                                              | Note                                                   |

|----------------------|----------------------------------|------------------------------------------------------------|-----------------------------------------------------------|-------|---------------------------------|-------------------------------------------------------------------|--------------------------------------------------------|

|                      |                                  | Fast mode (f <sub>ADC</sub> = 6 MHz)                       |                                                           | 800   | 1200                            |                                                                   |                                                        |

|                      | Supply                           | Slow mode (f <sub>ADC</sub> = 1.5 MHz)                     |                                                           |       | 600                             |                                                                   |                                                        |

| I <sub>DDSDx</sub>   | current<br>(V <sub>DDSDx</sub> = | Standby                                                    |                                                           |       | 200                             | μA                                                                |                                                        |

|                      | 3.3 V)                           | Power down                                                 |                                                           |       | 2.5                             |                                                                   |                                                        |

|                      |                                  | SD_ADC off                                                 |                                                           |       | 1                               |                                                                   |                                                        |

|                      | Common                           | Single ended mode (zero reference)                         | V <sub>SSA</sub>                                          |       | V <sub>REFSD+</sub><br>/gain    |                                                                   | Voltage on                                             |

| V <sub>AIN</sub>     | input<br>voltage<br>range        | Single ended offset mode                                   | V <sub>SSA</sub>                                          |       | V <sub>REFSD+</sub><br>/gain/2  | V                                                                 | AINP or<br>AINN pin                                    |

|                      | <u> </u>                         | Differential mode                                          | $V_{SSA}$                                                 |       | V <sub>DDSDx</sub>              |                                                                   |                                                        |

| V <sub>DIFF</sub>    | Differential<br>input<br>voltage | Differential mode only                                     | ifferential mode only -V <sub>REF</sub><br>SD+/<br>gain/2 |       | V <sub>REFSD+</sub> /<br>gain/2 |                                                                   | Differential<br>voltage<br>between<br>AINP and<br>AINN |

|                      |                                  | Slow mode (f <sub>ADC</sub> = 1.5 MHz)                     |                                                           | 4.166 |                                 |                                                                   | f <sub>ADC</sub> /360                                  |

|                      | Sampling<br>rate                 | Slow mode one channel only<br>(f <sub>ADC</sub> = 1.5 MHz) |                                                           |       |                                 |                                                                   | f <sub>ADC</sub> /120                                  |

| f <sub>S</sub>       |                                  | Fast mode multiplexed channel (f <sub>ADC</sub> = 6 MHz)   |                                                           | 16.66 | 6 k                             |                                                                   | f <sub>ADC</sub> /360                                  |

|                      |                                  | Fast mode one channel only<br>(f <sub>ADC</sub> = 6 MHz)   |                                                           | 50    |                                 |                                                                   | f <sub>ADC</sub> /120                                  |

| t <sub>CONV</sub>    | Conversion<br>time               |                                                            |                                                           | 1/fs  |                                 | s                                                                 |                                                        |

|                      | Analog                           | One channel, gain = 0.5,<br>f <sub>ADC</sub> = 1.5 MHz     |                                                           | 540   |                                 |                                                                   | see<br>reference                                       |

| Rain                 | input<br>impedance               | One channel, gain = 0.5, $f_{ADC} = 6 \text{ MHz}$         |                                                           | 135   |                                 | kΩ                                                                | manual for detailed                                    |

|                      |                                  | One channel, gain = 8, $f_{ADC}$ = 6 MHz                   |                                                           | 47    |                                 |                                                                   | description                                            |

| t <sub>CALIB</sub>   | Calibration time                 | $f_{ADC} = 6$ MHz, one offset calibration                  | = 6 MHz, one offset calibration 5120                      |       | μs                              | 30720/f <sub>ADC</sub>                                            |                                                        |

| t <sub>STAB</sub>    | Stabilization time               | From power down f <sub>ADC</sub> = 6 MHz                   | pm power down $f_{ADC} = 6 \text{ MHz}$ 100               |       | μs                              | 600/f <sub>ADC</sub> ,<br>75/f <sub>ADC</sub> if<br>SLOWCK<br>= 1 |                                                        |

|                      | Wakeup                           | f <sub>ADC</sub> = 6 MHz                                   |                                                           | 50    |                                 |                                                                   | 300/f <sub>ADC</sub>                                   |

| t <sub>STANDBY</sub> | from<br>standby<br>time          | f <sub>ADC</sub> = 1.5 MHz                                 |                                                           | 50    |                                 | μs                                                                | 75/f <sub>ADC</sub> if<br>SLOWCK<br>= 1                |

Table 74.

SDADC characteristics (continued)<sup>(1)</sup>

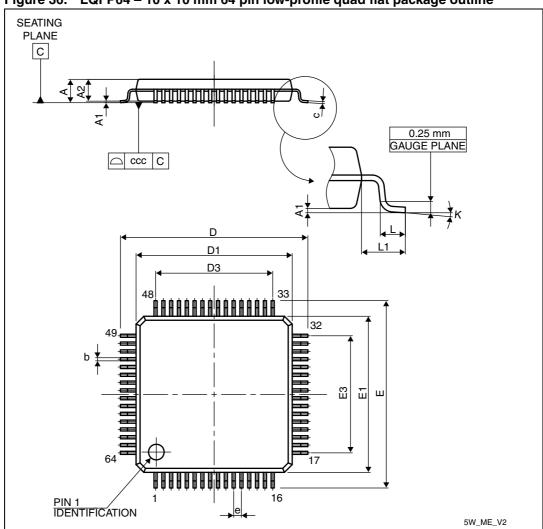

Figure 36. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 78. | LQFP64 – 10 x 10 mm low-profile quad flat package mechanical data | 3 |

|-----------|-------------------------------------------------------------------|---|

|-----------|-------------------------------------------------------------------|---|

| Symbol | millimeters |       |       |        |        |        |

|--------|-------------|-------|-------|--------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min    | Тур    | Мах    |

| А      |             |       | 1.60  |        |        | 0.0630 |

| A1     | 0.05        |       | 0.15  | 0.0020 |        | 0.0059 |

| A2     | 1.350       | 1.40  | 1.45  | 0.0531 | 0.0551 | 0.0571 |

| b      | 0.17        | 0.22  | 0.27  | 0.0067 | 0.0087 | 0.0106 |

| с      | 0.09        |       | 0.20  | 0.0035 |        | 0.0079 |

| D      | 11.80       | 12.00 | 12.20 | 0.4646 | 0.4724 | 0.4803 |

| D1     | 9.80        | 10.00 | 10.20 | 0.3858 | 0.3937 | 0.4016 |

| D3     |             | 7.50  |       |        | 0.2953 |        |

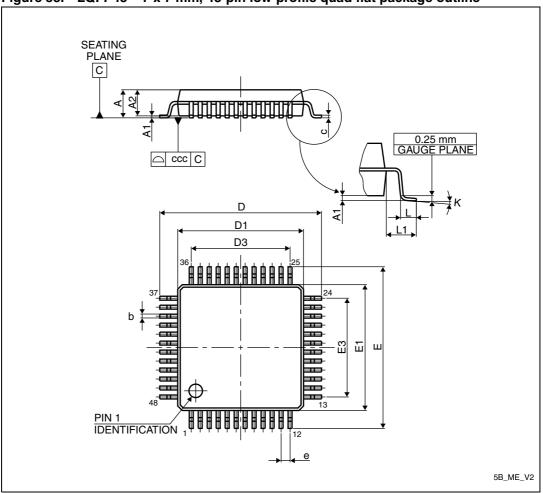

Figure 38. LQFP48 – 7 x 7 mm, 48-pin low-profile quad flat package outline

1. Drawing is not to scale.

Table 79. LQFP48 – 7 x 7 mm, low-profile quad flat package mechanical data

| Symbol |      | millimeters |      |        | inches <sup>(1)</sup> |        |  |  |

|--------|------|-------------|------|--------|-----------------------|--------|--|--|

| Symbol | Min  | Тур         | Max  | Min    | Тур                   | Max    |  |  |

| А      |      |             | 1.60 |        |                       | 0.0630 |  |  |

| A1     | 0.05 |             | 0.15 | 0.0020 |                       | 0.0059 |  |  |

| A2     | 1.35 | 1.40        | 1.45 | 0.0531 | 0.0551                | 0.0571 |  |  |

| b      | 0.17 | 0.22        | 0.27 | 0.0067 | 0.0087                | 0.0106 |  |  |

| С      | 0.09 |             | 0.20 | 0.0035 |                       | 0.0079 |  |  |

| D      | 8.80 | 9.00        | 9.20 | 0.3465 | 0.3543                | 0.3622 |  |  |

| D1     | 6.80 | 7.00        | 7.20 | 0.2677 | 0.2756                | 0.2835 |  |  |

| D3     |      | 5.50        |      |        | 0.2165                |        |  |  |

| Е      | 8.80 | 9.00        | 9.20 | 0.3465 | 0.3543                | 0.3622 |  |  |

| E1     | 6.80 | 7.00        | 7.20 | 0.2677 | 0.2756                | 0.2835 |  |  |

| E3     |      | 5.50        |      |        | 0.2165                |        |  |  |

| Date        | Revision     | Changes                                                                                                                                                |

|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |              | Filled values in <i>Table 70: WWDG min-max timeout value @72</i><br><i>MHz (PCLK)</i>                                                                  |

|             |              | Filled values in Table 58: SPI characteristics                                                                                                         |

|             |              | Filled values in Table 59: I2S characteristics                                                                                                         |

|             |              | Replaced Table 60: ADC characteristics                                                                                                                 |

|             |              | Added values in <i>Table 74: SDADC characteristics</i>                                                                                                 |

|             |              | Modified footnote in Table 75: VREFSD+ pin characteristics                                                                                             |

|             |              | Replaced 'AIN' with 'SRC' in <i>Table 61: RSRC max for fADC = 14 MHz</i> and <i>Figure 30: Typical connection diagram using the ADC</i>                |

|             |              | Reordered chapters and Cover page features.                                                                                                            |

|             |              | Added subsection to GPIOS in <i>Table 2: Device overview</i>                                                                                           |

|             |              | Aligned SRAM with USB in Figure 1: Block diagram                                                                                                       |

|             |              | Added "Do not reconfigure" sentence in <i>Section 3.9:</i><br><i>General-purpose input/outputs (GPIOs)</i>                                             |

|             |              | Added Table 7: STM32F37x I2C implementation                                                                                                            |

|             |              | Added Table 8: STM32F37x USART implementation                                                                                                          |

|             | 2<br>(conťď) | Merged SPI and I2S into one section                                                                                                                    |

|             |              | Reshaped Figure 5: STM32F37x BGA100 pinout and removed ADC10                                                                                           |

| 07-Sep-2012 |              | Added notes column, modified I/O structure values and pin, function names, removed TIM1_TX & TIM1_RX in <i>Table 11: STM32F37x pin definitions</i>     |

|             |              | Added the note "do not reconfigure" after <i>Table 11:</i><br><i>STM32F37x pin definitions</i>                                                         |

|             |              | Modified "x_CK" occurrences to "I2Sx_CK" in <i>Table 12:</i><br>Alternate functions for port PA to <i>Table 17:</i> Alternate<br>functions for port PF |

|             |              | Added two GP I/Os in <i>Table 9: Power supply scheme</i>                                                                                               |

|             |              | Added Caution after Table 9: Power supply scheme                                                                                                       |

|             |              | Added Max values in <i>Table 23: Operating conditions at power</i><br>up / power-down                                                                  |

|             |              | Modified <sup>(1)</sup> footnote in <i>Table 24: Embedded reset and power</i> control block characteristics                                            |

|             |              | Added row to Table 27: Embedded internal reference voltage                                                                                             |

|             |              | Added the note "It is recommended" under Table 51: I/O current injection susceptibility                                                                |

|             |              | Modified Table 51: I/O current injection susceptibility                                                                                                |

|             |              | Modified temperature and current values in <i>Section 7.2.2:</i><br>Selecting the product temperature range                                            |

|             |              | Added crystal EPSON-TOYOCOM bullet under <i>Typical current</i> consumption                                                                            |

|             |              | Modified Figure 9: Power supply scheme                                                                                                                 |

|             |              | Removed Boot 0 section                                                                                                                                 |

|             |              | Modified Table 73: USB: Full-speed electrical characteristics                                                                                          |

Table 82. Document revision history