Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                     |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | CPU16                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 16MHz                                                                   |

| Connectivity               | EBI/EMI, SCI, SPI                                                       |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 132-BQFP Bumpered                                                       |

| Supplier Device Package    | 132-PQFP (24.13x24.13)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc16z1ceh16 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### LIST OF TABLES (Continued) Title

#### Table

Page

| A-4       Typical Ratings, 20.97-MHz Operation       A-3         A-5       Typical Ratings, 25.17-MHz       A-4         A-6       Thermal Characteristics       A-5         A-7       Low Voltage Clock Control Timing       A-6         A-8       16.78-MHz Clock Control Timing       A-7         -9       20.97-MHz Clock Control Timing       A-8         A-10       25.17-MHz Clock Control Timing       A-8         A-11       Low Voltage 16.78-MHz DC Characteristics       A-10         A-12       16.78-MHz DC Characteristics       A-14         A-13       20.97-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-14         A-14       25.17-MHz AC Timing       A-23         A-16       16.78-MHz AC Timing       A-23         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-37         A-21       20.97-MHz Background Debug Mode Timing       A-34         A-22       25.17-MHz Background Debug Mode Timing       A-40         A-24       16.78-MHz Background Debug Mode Tim                                           | A-3  | Typical Ratings, 5V, 16.78-MHz OperationA-3 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------|

| A-6       Thermal Characteristics       A-5         A-7       Low Voltage Clock Control Timing       A-6         A-8       16.78-MHz Clock Control Timing       A-7         A-9       20.97-MHz Clock Control Timing       A-8         A-10       25.17-MHz Clock Control Timing       A-9         A-11       Low Voltage 16.78-MHz DC Characteristics       A-10         A-12       16.78-MHz DC Characteristics       A-11         A-13       20.97-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-16         A-15       Low Voltage 16.78-MHz AC Timing       A-12         A-16       16.78-MHz AC Timing       A-23         A-17       20.97-MHz AC Timing       A-24         A-18       25.17-MHz AC Timing       A-25         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-34         A-21       16.78-MHz Background Debug Mode Timing       A-38         A-22       15.17-MHz Background Debug Mode Timing       A-44         A-23       Low Voltage ECLK Bus Timing       A-44         A-24       16.78-MHz ECLK Bus Timing       A-42         A-25       17-MHz                                           |      |                                             |

| A-7       Low Voltage Clock Control Timing       A-6         A-8       16.78-MHz Clock Control Timing       A-7         A-9       20.97-MHz Clock Control Timing       A-8         A-10       25.17-MHz Clock Control Timing       A-9         A-11       Low Voltage 16.78-MHz DC Characteristics       A-10         A-12       16.78-MHz DC Characteristics       A-11         A-13       20.97-MHz DC Characteristics       A-12         A-14       25.17-MHz DC Characteristics       A-14         A-15       Low Voltage 16.78-MHz AC Timing       A-14         A-14       25.17-MHz DC Characteristics       A-16         A-15       Low Voltage 16.78-MHz AC Timing       A-21         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-24         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-21       20.97-MHz AC Timing       A-34         A-22       25.17-MHz Background Debug Mode Timing       A-38         A-23       Low Voltage ECLK Bus Timing       A-40         A-24       16.78-MHz ECLK Bus Timing       A-41         A-25       20.97-MHz ECLK Bus Timing       A-42         A-24       16.78-MHz ECLK Bus                                            | -    |                                             |

| A-8       16.78-MHz Clock Control Timing       A-7         A-9       20.97-MHz Clock Control Timing       A-8         A-10       25.17-MHz Clock Control Timing       A-9         A-11       Low Voltage 16.78-MHz DC Characteristics       A-10         A-12       16.78-MHz DC Characteristics       A-11         A-13       20.97-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-14         A-15       Low Voltage 16.78-MHz AC Timing       A-19         A-16       16.78-MHz AC Timing       A-21         A-17       20.97-MHz AC Timing       A-21         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-23         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-38         A-21       20.97-MHz Background Debug Mode Timing       A-44         A-22       25.17-MHz Background Debug Mode Timing       A-43         A-23       Low Voltage ECLK Bus Timing       A-44         A-24       26.17-MHz ECLK Bus Timing       A-41         A-25       20.97-MHz ECLK Bus Timing       A-44         A-26       25.17-MHz ECL                                           | -    |                                             |

| A-9       20.97-MHz Clock Control Timing       A-8         A-10       25.17-MHz Clock Control Timing       A-9         A-11       Low Voltage 16.78-MHz DC Characteristics       A-10         A-12       16.78-MHz DC Characteristics       A-12         A-13       20.97-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-16         A-15       Low Voltage 16.78-MHz AC Timing       A-23         A-16       7.97-MHz AC Timing       A-23         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-23         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-38         A-21       20.97-MHz Background Debug Mode Timing       A-38         A-22       25.17-MHz Background Debug Mode Timing       A-44         A-23       Low Voltage ECLK Bus Timing       A-44         A-24       16.78-MHz ECLK Bus Timing       A-42         A-25       25.17-MHz Background Debug Mode Timing       A-42         A-24       16.78-MHz ECLK Bus Timing       A-42         A-25       25.1                                           | A-7  | Low Voltage Clock Control TimingA-6         |

| A-10       25.17-MHz Clock Control Timing       A-9         A-11       Low Voltage 16.78-MHz DC Characteristics       A-10         A-12       16.78-MHz DC Characteristics       A-12         A-13       20.97-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-16         A-14       25.17-MHz DC Characteristics       A-16         A-15       Low Voltage 16.78-MHz AC Timing       A-23         A-16       16.78-MHz AC Timing       A-23         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-23         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-37         A-21       20.97-MHz Background Debug Mode Timing       A-38         A-22       25.17-MHz Background Debug Mode Timing       A-40         A-24       16.78-MHz ECLK Bus Timing       A-40         A-25       17-MHz ECLK Bus Timing       A-41         A-26       25.17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-42         A-27       Low Voltage QSPI Timing       A-43         A-28       QSPI Timing                                                 | A-8  | 16.78-MHz Clock Control TimingA-7           |

| A-11       Low Voltage 16.78-MHz DC Characteristics       A-10         A-12       16.78-MHz DC Characteristics       A-12         A-13       20.97-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-16         A-15       Low Voltage 16.78-MHz AC Timing       A-19         A-16       16.78-MHz AC Timing       A-23         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-23         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-37         A-21       20.97-MHz Background Debug Mode Timing       A-38         A-22       25.17-MHz Background Debug Mode Timing       A-38         A-23       Low Voltage ECLK Bus Timing       A-40         A-24       16.78-MHz ECLK Bus Timing       A-42         A-25       17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-42         A-27       Low Voltage OSPI Timing       A-43         A-28       QSPI Timing                                                      | A-9  | 20.97-MHz Clock Control Timing              |

| A-11       Low Voltage 16.78-MHz DC Characteristics       A-10         A-12       16.78-MHz DC Characteristics       A-12         A-13       20.97-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-16         A-15       Low Voltage 16.78-MHz AC Timing       A-19         A-16       16.78-MHz AC Timing       A-23         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-23         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-37         A-21       20.97-MHz Background Debug Mode Timing       A-38         A-22       25.17-MHz Background Debug Mode Timing       A-38         A-23       Low Voltage ECLK Bus Timing       A-40         A-24       16.78-MHz ECLK Bus Timing       A-42         A-25       17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-42         A-27       Low Voltage OSPI Timing       A-43         A-28       QSPI Timing                                                      | A-10 | 25.17-MHz Clock Control Timing              |

| A-12       16.78-MHz DC Characteristics       A-12         A-13       20.97-MHz DC Characteristics       A-14         A-14       25.17-MHz DC Characteristics       A-16         A-15       Low Voltage 16.78-MHz AC Timing       A-17         A-16       16.78-MHz AC Timing       A-21         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-25         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-38         A-21       20.97-MHz Background Debug Mode Timing       A-38         A-22       25.17-MHz Background Debug Mode Timing       A-38         A-23       Low Voltage ECLK Bus Timing       A-40         A-24       16.78-MHz ECLK Bus Timing       A-41         A-25       17-MHz ECLK Bus Timing       A-42         A-24       25.17-MHz ECLK Bus Timing       A-42         A-25       20.97-MHz ECLK Bus Timing       A-42         A-26       21.7-MHz ECLK Bus Timing       A-42         A-27       Low Voltage QSPI Timing       A-43         A-28       QSPI Timing       A-44 <td>A-11</td> <td>Low Voltage 16.78-MHz DC Characteristics</td> | A-11 | Low Voltage 16.78-MHz DC Characteristics    |

| A-14       25.17-MHz DC Characteristics       A-16         A-15       Low Voltage 16.78-MHz AC Timing       A-19         A-16       16.78-MHz AC Timing       A-21         A-17       20.97-MHz AC Timing       A-23         A-18       25.17-MHz AC Timing       A-23         A-19       Low Voltage 16.78-MHz Background Debug Mode Timing       A-37         A-20       16.78-MHz Background Debug Mode Timing       A-37         A-21       20.97-MHz Background Debug Mode Timing       A-38         A-22       25.17-MHz Background Debug Mode Timing       A-38         A-23       Low Voltage ECLK Bus Timing       A-40         A-24       16.78-MHz ECLK Bus Timing       A-41         A-25       20.97-MHz ECLK Bus Timing       A-41         A-26       25.17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-42         A-26       25.17-MHz ECLK Bus Timing       A-43         A-27       Low Voltage QSPI Timing       A-44         A-28       QSPI Timing       A-46         A-29       Low Voltage ADC DC Electrical Characteristics       A-53         A-31       General-Purpose Timer AC Characteristics (Operating)       A-63         A-32       ADC Max                                           | A-12 |                                             |

| A-15Low Voltage 16.78-MHz AC TimingA-19A-1616.78-MHz AC TimingA-21A-1720.97-MHz AC TimingA-23A-1825.17-MHz AC TimingA-25A-19Low Voltage 16.78-MHz Background Debug Mode TimingA-37A-2016.78-MHz Background Debug Mode TimingA-37A-2120.97-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-38A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-42A-27Low Voltage QSPI TimingA-42A-28QSPI TimingA-44A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-33ADC Maximum RatingsA-62A-34Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-355V ADC DC Electrical Characteristics (Operating)A-63A-36ADC AC Characteristics (Operating)A-64A-36ADC Conversion Characteristics (Operating)A-66A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-36ADC Conversion Characteristics (Operating)A-67B-1Module Address MapD-1                                                                                                                                                                                   | A-13 | 20.97-MHz DC Characteristics                |

| A-15Low Voltage 16.78-MHz AC TimingA-19A-1616.78-MHz AC TimingA-21A-1720.97-MHz AC TimingA-23A-1825.17-MHz AC TimingA-25A-19Low Voltage 16.78-MHz Background Debug Mode TimingA-37A-2016.78-MHz Background Debug Mode TimingA-37A-2120.97-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-38A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-42A-27Low Voltage QSPI TimingA-42A-28QSPI TimingA-44A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-33ADC Maximum RatingsA-62A-34Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-355V ADC DC Electrical Characteristics (Operating)A-63A-36ADC AC Characteristics (Operating)A-64A-36ADC Conversion Characteristics (Operating)A-66A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-36ADC Conversion Characteristics (Operating)A-67B-1Module Address MapD-1                                                                                                                                                                                   | A-14 | 25.17-MHz DC Characteristics                |

| A-1616.78-MHz AC TimingA-21A-1720.97-MHz AC TimingA-23A-1825.17-MHz AC TimingA-25A-19Low Voltage 16.78-MHz Background Debug Mode TimingA-37A-2016.78-MHz Background Debug Mode TimingA-37A-2120.97-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-38A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-40A-2520.97-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-43A-27Low Voltage QSPI TimingA-44A-28QSPI TimingA-45A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-31General-Purpose Timer AC Characteristics (Operating)A-63A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-64A-36ADC COnversion Characteristics (Operating)A-66A-37Low Voltage ADC Conversion Characteristics (Operating)A-67B-1Module Address MapD-1Module Address MapD-1                                                                                                                                                                                                                                                                  | A-15 |                                             |

| A-1720.97-MHz AC TimingA-23A-1825.17-MHz AC TimingA-25A-19Low Voltage 16.78-MHz Background Debug Mode TimingA-37A-2016.78-MHz Background Debug Mode TimingA-37A-2120.97-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-40A-2416.78-MHz ECLK Bus TimingA-40A-2520.97-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-41A-2625.17-MHz ECLK Bus TimingA-42A-27Low Voltage QSPI TimingA-43A-27Low Voltage SPI TimingA-46A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage ADC DC Electrical CharacteristicsA-53A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-66A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                          |      |                                             |

| A-1825.17-MHz AC TimingA-25A-19Low Voltage 16.78-MHz Background Debug Mode TimingA-37A-2016.78-MHz Background Debug Mode TimingA-37A-2120.97-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-38A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-42A-27Low Voltage QSPI TimingA-43A-28QSPI TimingA-44A-29Low Voltage QSPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-31General-Purpose Timer AC Characteristics (Operating)A-63A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-35SV ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-66A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-34ADC Conversion Characteristics (Operating)A-66A-36ADC Conversion Characteristics (Operating)A-67B-1Module Address MapD-1                                                                                                                               | -    | <b>U</b>                                    |

| A-19Low Voltage 16.78-MHz Background Debug Mode TimingA-37A-2016.78-MHz Background Debug Mode TimingA-37A-2120.97-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-38A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-42A-27Low Voltage QSPI TimingA-43A-28QSPI TimingA-445A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-30SPI TimingA-45A-31General-Purpose Timer AC Characteristics (Operating)A-63A-32Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-35SV ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-66A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                 |      |                                             |

| A-2016.78-MHz Background Debug Mode TimingA-37A-2120.97-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-38A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-43A-27Low Voltage QSPI TimingA-44A-28QSPI TimingA-45A-29Low Voltage QSPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage ADC DC Electrical Characteristics (Operating)A-62A-31General-Purpose Timer AC Characteristics (Operating)A-63A-31Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-64A-355V ADC DC Electrical Characteristics (Operating)A-64A-36ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                             | -    |                                             |

| A-2120.97-MHz Background Debug Mode TimingA-38A-2225.17-MHz Background Debug Mode TimingA-38A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-43A-27Low Voltage QSPI TimingA-45A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-30SPI TimingA-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-355V ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                      | -    |                                             |

| A-2225.17-MHz Background Debug Mode TimingA-38A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-43A-27Low Voltage QSPI TimingA-45A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-29Low Voltage SPI TimingA-46A-30SPI TimingA-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-64A-355V ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                      |      |                                             |

| A-23Low Voltage ECLK Bus TimingA-40A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-43A-27Low Voltage QSPI TimingA-45A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-46A-30SPI TimingA-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-35SV ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                             |

| A-2416.78-MHz ECLK Bus TimingA-41A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-43A-27Low Voltage QSPI TimingA-45A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-46A-29SPI TimingA-50A-30SPI TimingA-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-35SV ADC DC Electrical Characteristics (Operating)A-63A-36ADC AC Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                             |

| A-2520.97-MHz ECLK Bus TimingA-42A-2625.17-MHz ECLK Bus TimingA-43A-27Low Voltage QSPI TimingA-45A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-49A-30SPI TimingA-49A-31General-Purpose Timer AC CharacteristicsA-50A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-355V ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _    |                                             |

| A-2625.17-MHz ECLK Bus TimingA-43A-27Low Voltage QSPI TimingA-45A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-49A-30SPI TimingA-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-355V ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | · · · · · · · · · · · · · · · · · · ·       |

| A-27Low Voltage QSPI TimingA-45A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-49A-30SPI TimingA-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-355V ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -    | •                                           |

| A-28QSPI TimingA-46A-29Low Voltage SPI TimingA-49A-30SPI TimingA-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-35SV ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                             |

| A-29Low Voltage SPI TimingA-49A-30SPI TimingA-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-35SV ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-64A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                                             |

| A-30SPI Timing.A-50A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-355V ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | • • • • • • • • • • • • • • • • • • •       |

| A-31General-Purpose Timer AC CharacteristicsA-53A-32ADC Maximum RatingsA-62A-33Low Voltage ADC DC Electrical Characteristics (Operating)A-63A-34Low Voltage ADC AC Characteristics (Operating)A-63A-35SV ADC DC Electrical Characteristics (Operating)A-64A-36ADC AC Characteristics (Operating)A-65A-37Low Voltage ADC Conversion Characteristics (Operating)A-66A-38ADC Conversion Characteristics (Operating)A-67B-1M68HC16 Z-Series Ordering InformationB-8D-1Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -    |                                             |

| <ul> <li>A-32 ADC Maximum Ratings</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                             |

| <ul> <li>A-33 Low Voltage ADC DC Electrical Characteristics (Operating)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                                             |

| <ul> <li>A-34 Low Voltage ADC AC Characteristics (Operating)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                             |

| <ul> <li>A-35 5V ADC DC Electrical Characteristics (Operating)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                             |

| <ul> <li>A-36 ADC AC Characteristics (Operating)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                             |

| <ul> <li>A-37 Low Voltage ADC Conversion Characteristics (Operating)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                                             |

| <ul> <li>A-38 ADC Conversion Characteristics (Operating)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | ADC AC Characteristics (Operating)          |

| <ul><li>B-1 M68HC16 Z-Series Ordering Information</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                             |

| D-1 Module Address MapD-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A-38 | ADC Conversion Characteristics (Operating)  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | B-1  | M68HC16 Z-Series Ordering InformationB-8    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D-1  | Module Address MapD-1                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D-2  |                                             |

| Mnemonic | Operation                    | Description                                                    | Address  |        | Instruction   |        |   |          | Con | ditior | n Co | des |   | _ |

|----------|------------------------------|----------------------------------------------------------------|----------|--------|---------------|--------|---|----------|-----|--------|------|-----|---|---|

|          |                              |                                                                | Mode     | Opcode | Operand       | Cycles | s | ΜV       | н   | EV     | Ν    | z   | v | C |

| LDAB     | Load B                       | $(M) \Rightarrow B$                                            | IND8, X  | C5     | ff            | 6      | _ | <u> </u> | -   |        | Δ    | Δ   | 0 | Δ |

|          |                              |                                                                | IND8, Y  | D5     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND8, Z  | E5     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IMM8     | F5     | ii            | 2      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, X | 17C5   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Y | 17D5   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Z | 17E5   | 9999          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | EXT      | 17F5   | hh ll         | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | E, X     | 27C5   | _             | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | E, Y     | 27D5   | _             | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | E, Z     | 27E5   | _             | 6      |   |          |     |        |      |     |   |   |

| LDD      | Load D                       | $(M:M+1) \Rightarrow D$                                        | IND8, X  | 85     | ff            | 6      | — | _        | _   | _      | Δ    | Δ   | 0 | - |

|          |                              | , ,                                                            | IND8, Y  | 95     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND8, Z  | A5     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IMM16    | 37B5   | jj kk         | 4      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, X | 37C5   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Y | 37D5   | 9999          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Z | 37E5   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | EXT      | 37F5   | hh ll         | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | E, X     | 2785   | _             | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | E, Y     | 2795   | _             | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | E, Z     | 27A5   | _             | 6      |   |          |     |        |      |     |   |   |

| LDE      | Load E                       | $(M:M+1) \Rightarrow E$                                        | IMM16    | 3735   | jj kk         | 4      |   |          |     |        | Δ    | Δ   | 0 | _ |

| LDL      | LUdu L                       | $(M : M + 1) \rightarrow L$                                    | IND16, X | 3745   |               | 6      |   |          |     |        |      | Δ   | 0 |   |

|          |                              |                                                                | IND16, Y | 3755   | 9999          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Z | 3765   | 9999          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | EXT      | 3775   | gggg<br>hh ll | 6      |   |          |     |        |      |     |   |   |

| LDED     | Lood Constant                | $(M:M+1) \Rightarrow E$                                        |          |        |               | 8      |   |          |     |        |      |     |   | _ |

| LDED     | Load Concatenated<br>E and D | $(M : M + 1) \Rightarrow E$<br>$(M + 2 : M + 3) \Rightarrow D$ | EXT      | 2771   | hh ll         | o      | _ | _        | _   | _      | _    | _   | _ |   |

| L DI II  |                              |                                                                |          | 0700   |               | 0      |   |          |     |        |      |     |   |   |

| LDHI     | Initialize H and I           | $(M:M+1)_X\RightarrowH\:R$                                     | INH      | 27B0   | -             | 8      | _ | _        | _   | _      |      | _   | _ |   |

|          |                              | $(M:M+1)_Y \Rightarrow I\;R$                                   |          |        |               |        |   |          |     |        |      |     |   |   |

| LDS      | Load SP                      | $(M:M+1) \Rightarrow SP$                                       | IND8, X  | CF     | ff            | 6      | — | _        | _   | _      | Δ    | Δ   | 0 | - |

|          |                              |                                                                | IND8, Y  | DF     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND8, Z  | EF     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, X | 17CF   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Y | 17DF   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Z | 17EF   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | EXT      | 17FF   | hh ll         | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IMM16    | 37BF   | jj kk         | 4      |   |          |     |        |      |     |   |   |

| LDX      | Load IX                      | $(M : M + 1) \Rightarrow IX$                                   | IND8, X  | CC     | ff            | 6      | — | _        | _   |        | Δ    | Δ   | 0 |   |

|          |                              |                                                                | IND8, Y  | DC     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND8, Z  | EC     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IMM16    | 37BC   | jj kk         | 4      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, X | 17CC   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Y | 17DC   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Z | 17EC   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | EXT      | 17FC   | hh ll         | 6      |   |          |     |        |      |     |   |   |

| LDY      | Load IY                      | $(M:M+1) \Rightarrow IY$                                       | IND8, X  | CD     | ff            | 6      | — | _        | _   | _      | Δ    | Δ   | 0 | 7 |

|          |                              |                                                                | IND8, Y  | DD     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND8, Z  | ED     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IMM16    | 37BD   | jj kk         | 4      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, X | 17CD   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Y | 17DD   | 9999          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Z | 17ED   | gggg          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | EXT      | 17FD   | hh ll         | 6      |   |          |     |        |      |     |   |   |

| LDZ      | Load IZ                      | $(M:M+1) \Rightarrow IZ$                                       | IND8, X  | CE     | ff            | 6      | — | _        | _   | _      | Δ    | Δ   | 0 | - |

|          |                              | . ,                                                            | IND8, Y  | DE     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND8, Z  | EE     | ff            | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IMM16    | 37BE   | jj kk         | 4      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, X | 17CE   | 9999          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Y | 17DE   | 9999          | 6      |   |          |     |        |      |     |   |   |

|          |                              |                                                                | IND16, Z | 17EE   | 9999          | 6      |   |          |     |        |      |     |   |   |

| 1        |                              |                                                                |          |        |               |        |   |          |     |        |      |     |   |   |

### Table 4-2 Instruction Set Summary (Continued)

### NOTE

The external bus interface does not latch data when an external bus cycle is terminated by a bus error. When this occurs during an instruction prefetch, the IMB precharge state (bus pulled high, or \$FF) is latched into the CPU16 instruction register, with indeterminate results.

### 5.6.5.2 Double Bus Faults

Exception processing for bus error exceptions follows the standard exception processing sequence. Refer to **4.13 Exceptions** for more information. However, two special cases of bus error, called double bus faults, can abort exception processing.

BERR assertion is not detected until an instruction is complete. The BERR latch is cleared by the first instruction of the BERR exception handler. Double bus fault occurs in two ways:

- 1. When bus error exception processing begins, and a second BERR is detected before the first instruction of the exception handler is executed.

- 2. When one or more bus errors occur before the first instruction after a RESET exception is executed.

Multiple bus errors within a single instruction that can generate multiple bus cycles cause a single bus error exception after the instruction has been executed.

Immediately after assertion of a second BERR, the MCU halts and drives the HALT line low. Only a reset can restart a halted MCU. However, bus arbitration can still occur. Refer to **5.6.6 External Bus Arbitration** for more information. A bus error or address error that occurs after exception processing has been completed (during the execution of the exception handler routine, or later) does not cause a double bus fault. The MCU continues to retry the same bus cycle as long as the external hardware requests it.

## 5.6.5.3 Halt Operation

When HALT is asserted while BERR is not asserted, the MCU halts external bus activity after negation of DSACK. The MCU may complete the current word transfer in progress. For a long-word to byte transfer, this could be after S2 or S4. For a word to byte transfer, activity ceases after S2.

Negating and reasserting HALT according to timing requirements provides single-step (bus cycle to bus cycle) operation. The HALT signal affects external bus cycles only, so that a program that does not use external bus can continue executing. During dy-namically-sized 8-bit transfers, external bus activity may not stop at the next cycle boundary. Occurrence of a bus error while HALT is asserted causes the CPU16 to process a bus error exception.

When the MCU completes a bus cycle while the HALT signal is asserted, the data bus goes into a high-impedance state and the AS and DS signals are driven to their inactive states. Address, function code, size, and read/write signals remain in the same state.

M68HC16 Z SERIES USER'S MANUAL

#### SYSTEM INTEGRATION MODULE

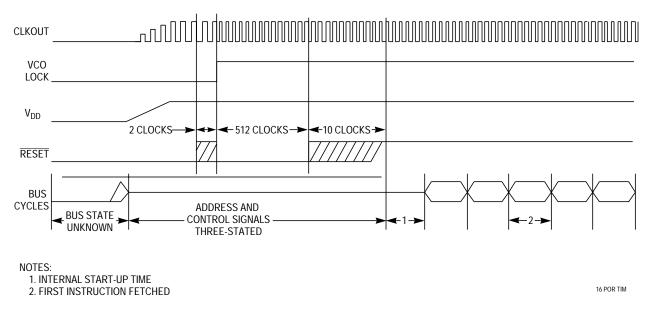

The SIM clock synthesizer provides clock signals to the other MCU modules. After the clock is running and MSTRST is asserted for at least four clock cycles, these modules reset.  $V_{DD}$  ramp time and VCO frequency ramp time determine how long the four cycles take. Worst case is approximately 15 milliseconds. During this period, module port pins may be in an indeterminate state. While input-only pins can be put in a known state by external pull-up resistors, external logic on input/output or output-only pins during this time must condition the lines. Active drivers require high-impedance buffers or isolation resistors to prevent conflict.

Figure 5-20 is a timing diagram for power-on reset. It shows the relationships between RESET,  $V_{DD}$ , and bus signals.

#### Figure 5-20 Power-On Reset

#### 5.7.8 Use of the Three-State Control Pin

Asserting the three-state control (TSC) input causes the MCU to put all output drivers in a disabled, high-impedance state. The signal must remain asserted for approximately ten clock cycles in order for drivers to change state.

When the internal clock synthesizer is used (MODCLK held high during reset), synthesizer ramp-up time affects how long the ten cycles take. Worst case is approximately 20 milliseconds from TSC assertion.

When an external clock signal is applied (MODCLK held low during reset), pins go to high-impedance state as soon after TSC assertion as approximately ten clock pulses have been applied to the EXTAL pin.

Go to: www.freescale.com

STANDBY RAM MODULE

For More Information On This Product, Go to: www.freescale.com

To ensure that the MCCI stops in a known state, assert the STOP bit before executing the CPU LPSTOP instruction. Before asserting the STOP bit, disable the SPI (clear the SPE bit) and disable the SCI receivers and transmitters (clear the RE and TE bits). Complete transfers in progress before disabling the SPI and SCI interfaces.

Once the STOP bit is asserted, it can be cleared by system software or by reset.

## 10.2.1.2 Privilege Levels

The supervisor bit (SUPV) in the MMCR has no effect since the CPU16 operates only in the supervisor mode.

## 10.2.1.3 MCCI Interrupts

The interrupt request level of each of the three MCCI interfaces can be programmed to a value of zero (interrupts disabled) through seven (highest priority). These levels are selected by the ILSCIA and ILSCIB fields in the SCI interrupt level register (ILSCI) and the ILSPI field in the SPI interrupt level register (ILSPI). In case two or more MCCI submodules request an interrupt simultaneously and are assigned the same interrupt request level, the SPI submodule is given the highest priority and SCIB is given the lowest.

When an interrupt is requested which is at a higher level than the interrupt mask in the CPU status register, the CPU initiates an interrupt acknowledge cycle. During this cycle, the MCCI compares its interrupt request level to the level recognized by the CPU. If a match occurs, arbitration with other modules begins.

Interrupting modules present their arbitration number on the IMB, and the module with the highest number wins. The arbitration number for the MCCI is programmed into the interrupt arbitration (IARB) field of the MMCR. Each module should be assigned a unique arbitration number. The reset value of the IARB field is \$0, which prevents the MCCI from arbitrating during an interrupt acknowledge cycle. The IARB field should be initialized by system software to a value from \$F (highest priority) through \$1 (lowest priority). Otherwise, the CPU identifies any interrupts generated as spurious and takes a spurious-interrupt exception.

If the MCCI wins the arbitration, it generates an interrupt vector that uniquely identifies the interrupting serial interface. The six MSBs are read from the interrupt vector (INTV) field in the MCCI interrupt vector register (MIVR). The two LSBs are assigned by the MCCI according to the interrupting serial interface, as indicated in Table 10-1.

## Table 10-1 MCCI Interrupt Vectors

| Interface | INTV[1:0] |

|-----------|-----------|

| SCIA      | 00        |

| SCIB      | 01        |

| SPI       | 10        |

MULTICHANNEL COMMUNICATION INTERFACE

#### **10.5 MCCI Initialization**

After reset, the MCCI remains in an idle state. Several registers must be initialized before serial operations begin. A general sequence guide for initialization follows.

- A. Global

- 1. Configure MMCR

- a. Write an interrupt arbitration number greater than zero into the IARB field. b. Clear the STOP bit if it is not already cleared.

- 2. Interrupt vector and interrupt level registers (MIVR, ILSPI, and ILSCI) a. Write the SPI/SCI interrupt vector into MIVR.

- b. Write the SPI interrupt request level into the ILSPI and the interrupt request levels for the two SCI interfaces into the ILSCI.

- 3. Port data register

- a. Write a data word to PORTMC.

- b. Read a port pin state from PORTMCP.

- 4. Pin control registers

- a. Establish the direction of MCCI pins by writing to the MDDR.

- b. Assign pin functions by writing to the MPAR.

- B. Serial Peripheral Interface

- 1. Configure SPCR

- a. Write a transfer rate value into the BAUD field.

- b. Determine clock phase (CPHA) and clock polarity (CPOL).

- c. Specify an 8- or 16-bit transfer (SIZE) and MSB- or LSB-first transfer mode (LSBF).

- d. Select master or slave operating mode (MSTR).

- e. Enable or disable wired-OR operation (WOMP).

- f. Enable or disable SPI interrupts (SPIE).

- g. Enable the SPI by setting the SPE bit.

- C. Serial Communication Interface (SCIA/SCIB)

- 1. To transmit, read the SCSR, and then write transmit data to the SCDR. This clears the TDRE and TC indicators in the SCSR.

- a. SCI control register 0 (SCCR0)

- b. Write a baud rate value into the BR field.

- 2. Configure SCCR1

- a. Select 8- or 9-bit frame format (M).

- b. Determine use (PE) and type (PT) of parity generation or detection.

- c. To receive, set the RE and RIE bits in SCCR1. Select use (RWU) and type (WAKE) of receiver wakeup. Select idle-line detection type (ILT) and enable or disable idle-line interrupt (ILIE).

- d. To transmit, set TE and TIE bits in SCCR1, and enable or disable WOMC and TCIE bits. Disable break transmission (SBK) for normal operation.

GENERAL-PURPOSE TIMER For More Information On This Product, Go to: www.freescale.com

## Table A-7 Low Voltage Clock Control Timing

(V<sub>DD</sub> and V<sub>DDSYN</sub> = 2.7 to 3.6 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>)

| Num | Characteristic                                                                                                                                                                                  | Symbol            | Min                                                             | Max                                             | Unit       |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------|-------------------------------------------------|------------|