Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 20MHz                                                  |

| Connectivity               | EBI/EMI, UART/USART                                    |

| Peripherals                | -                                                      |

| Number of I/O              | 24                                                     |

| Program Memory Size        | -                                                      |

| Program Memory Type        | ROMIess                                                |

| EEPROM Size                | -                                                      |

| RAM Size                   | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Through Hole                                           |

| Package / Case             | 40-DIP (0.620", 15.75mm)                               |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86c9320psc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PRODUCT SPECIFICATION

# Z86C93

# CMOS Z8® MULTIPLY/DIVIDE MICROCONTROLLER

## **FEATURES**

- Complete microcontroller, up to 24 I/O lines, and up to 64 Kbytes of addressable external space each for program and data memory.

- 16-bit x 16-bit hardwired multiplier with 32-bit product in 17 clock cycles.

- 32-bit x 16-bit hardwired divider with 16-bit quotient and 16-bit remainder in 20 clock cycles.

- 256-byte register file, including 236 general-purpose registers, up to three I/O port registers and 16 status and control registers.

- 17-byte Expanded Register File, including two generalpurpose registers and 15 status and control registers.

- Vectored, priority interrupts for I/O, counter/timers and UART.

- On-chip oscillator that accepts crystal or external clock drive.

- Two 16-bit counter timers with 6-bit prescalers.

- Third 16-bit counter/timer with 4-bit prescaler, one capture register and a fast decrement mode.

- Register Pointer for short, fast instructions that can access any one of the sixteen working register groups.

- Additional emulation signals SCLK, IACK, and /SYNC are made available.

- Two low power standby modes, STOP and HALT

- Full-duplex UART

- 3.3 ± 10% volt operation at 25 MHz

- $\blacksquare$  5.0  $\pm$  10% volt operation at 20, 25 and 33 MHz

# **GENERAL DESCRIPTION**

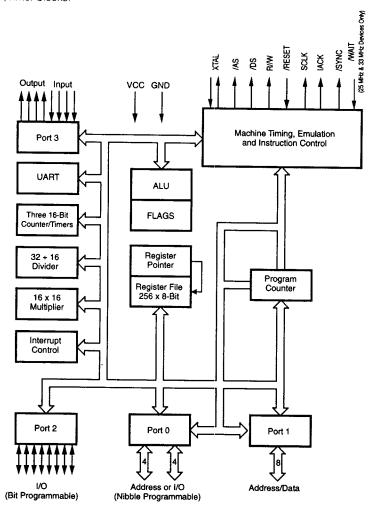

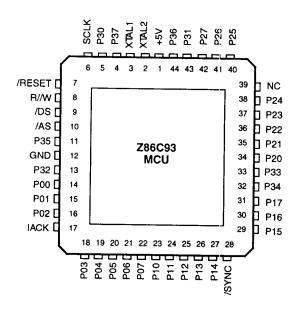

The Z86C93 is a CMOS ROMless Z8 microcontroller enhanced with a hardwired 16-bit x 16-bit multiplier and 32-bit/16-bit divider and three 16-bit counter timers (Figure 1). A capture register and a fast decrement mode is also provided. It is offered in 40-pin PDIP, 44-pin PLCC, 44-pin QFP and 48-pin VQFP (Figures 2, 3, 4, 5 and 6). Besides the four additional signals (SCLK, IACK, /SYNC and /WAIT), the Z86C93 is compatible with the Z86C91, yet it offers a much more powerful mathematical capability.

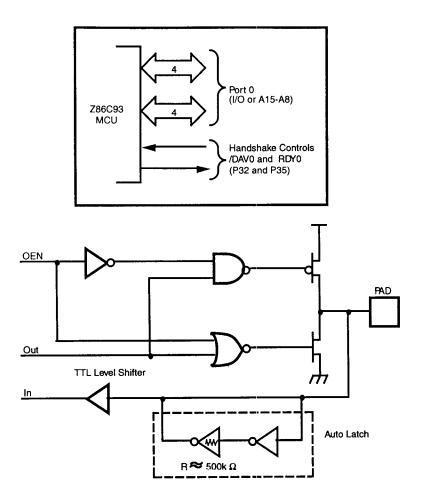

The Z86C93 provides up to 16 output address lines permitting an address space of up to 64 Kbytes of data and program memory each. Eight address outputs (AD7-AD0) are provided by a multiplexed, 8-bit, Address/Data bus. The remaining 8 bits can be provided by the software configuration of Port 0 to output address bits A15-A8.

# **GENERAL DESCRIPTION** (Continued)

There are 256 registers located on-chip and organized as 236 general-purpose registers, 16 control and status registers, and four I/O port registers. The register file can be divided into sixteen groups of 16 working registers each. Configuration of the registers in this manner allows the use of short format instructions; in addition, any of the individual registers can be accessed directly. There are an additional 17 registers implemented in the Expanded Register File in Banks D and E. Two of the registers may be used as general-purpose registers, while 15 registers supply the data and control functions for the Multiply/ Divide Unit and Counter/Timer blocks.

### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit                | Device          |

|------------|------------------------|-----------------|

| Power      | V <sub>cc</sub><br>GND | V <sub>DO</sub> |

| Ground     | GND                    | V <sub>ss</sub> |

Figure 1. Functional Block Diagram

# PIN DESCRIPTION (Continued)

Figure 4. 44-Pin PLCC

Table 2. 44-Pin PLCC Pin Identification

| No | Symbol          | Function            | Direction | No    | Symbol  | Function             | Direction |

|----|-----------------|---------------------|-----------|-------|---------|----------------------|-----------|

| 1  | V <sub>cc</sub> | Power Supply        | Input     | 14-16 | P00-P02 | Port 0 pin 0,1,2     | In/Output |

| 2  | XTĂĽ2           | Crystal, Osc. Clock | Output    | 17    | IACK    | Int. Acknowledge     | Output    |

| 3  | XTAL1           | Crystal, Osc. Clock | Input     | 18-22 | P03-P07 | Port 0 pin 3,4,5,6,7 | In/Output |

| 4  | P37             | Port 3 pin 7        | Output    | 23-27 | P10-P14 | Port 1 pin 0,1,2,3,4 | In/Output |

| 5  | P30             | Port 3 pin 0        | Input     | 28    | /SYNC   | Synchronize Pin      | Output    |

| 6  | SCLK            | System Clock        | Output    | 29-31 | P15-P17 | Port 1 pin 5,6,7     | In/Output |

| 7  | /RESET          | Reset               | Input     | 32    | P34     | Port 3 pin 4         | Output    |

| 8  | R//W            | Read/Write          | Output    | 33    | P33     | Port 3 pin 3         | Input     |

| 9  | /DS             | Data Strobe         | Output    | 34-38 | P20-P24 | Port 2 pin 0,1,2,3,4 | In/Output |

| 10 | /AS             | Address Strobe      | Output    | 39    | N/C     | Not Connected (20 MH |           |

| 11 | P35             | Port 3 pin 5        | Output    | -     | M/AIT   | WAIT (25 or 33 MHz)  | Input     |

| 12 | GND             | Ground GND          | Input     | 40-42 | P25-P27 | Port 2 pin 5,6,7     | In/Output |

| 13 | P32             | Port 3 pin 2        | Input     | 43    | P31     | Port 3 pin 1         | Input     |

|    |                 | <del></del>         |           | 44    | P36     | Port 3 pin 6         | Output    |

Figure 7. Port 0 Configuration

# PIN FUNCTIONS (Continued)

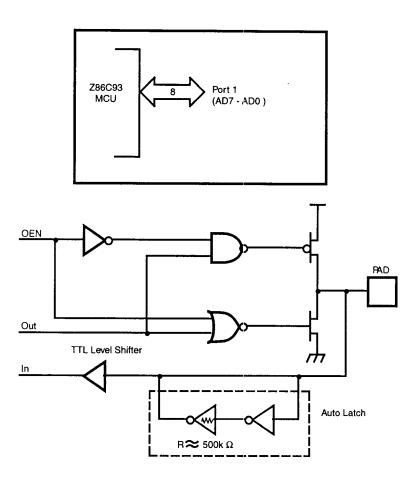

Port 1. (P10-P17). Port 1 is an 8-bit, TTL compatible port. It has multiplexed Address (A7-A0) and Data (D7-D0) ports for interfacing external memory (Figure 8).

If more than 256 external locations are required, Port 0 must output the additional lines.

Figure 8. Port 1 Configuration

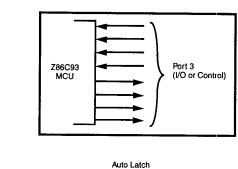

Port 3 P30-P37. Port 3 is an 8-bit, TTL compatible four fixed input and four fixed output ports. These eight I/O lines have four fixed (P30-P33) input and four fixed (P34-P37) output

ports. Port 3 pins P30 and P37 when used as serial I/O, are programmed as serial in and serial out, respectively (Figure 10 and Table 5).

Figure 10. Port 3 Configuration

Table 5. Port 3 Pin Assignments

| Pin# | 1/0 | CTC1            | Int. | P0HS | P2HS   | UART       | Ext.                                  |

|------|-----|-----------------|------|------|--------|------------|---------------------------------------|

| P30  | In  |                 | IRQ3 |      |        | Serial In  | · · · · · · · · · · · · · · · · · · · |

| P31  | ln  | T <sub>IN</sub> | IRQ2 |      | D/R    |            |                                       |

| P32  | ln  |                 | IRQ0 | D/R  |        |            |                                       |

| P33  | In  |                 | IRQ1 |      |        |            |                                       |

| P34  | Out |                 |      |      |        |            | DM                                    |

| P35  | Out |                 |      | R/D  |        |            |                                       |

| P36  | Out | Tout            |      | , –  | R/D    |            |                                       |

| P37  | Out | 001             |      |      | . ,, & | Serial Out |                                       |

Port 3 is configured under software control to provide the following control functions: handshake for Ports 0 and 2 (/DAV and RDY); four external interrupt request signals (IRQ0-IRQ3); timer input and output signals ( $T_{IN}$  and  $T_{OUT}$ ), and Data Memory Select (/DM).

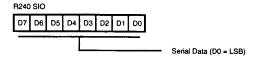

Port 3 lines P30 and P37 can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by the Counter/Timer 0.

The Z86C93 automatically adds a start bit and two stop bits to transmitted data (Figure 10). Odd parity is also available as an option. Eight data bits are always transmitted,

regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted characters.

Received data must have a start bit, eight data bits and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

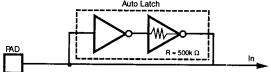

The Auto Latch on Port 3 puts a valid CMOS level on all CMOS inputs that are not externally driven. Whether this level is zero or one, cannot be determined. A valid CMOS level rather than a floating node reduces excessive supply current flow in the input buffer.

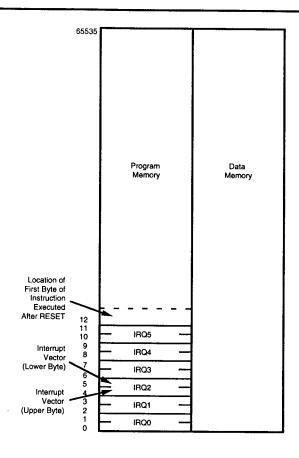

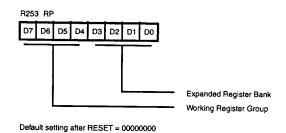

Figure 12. Program and Data Memory Configuration

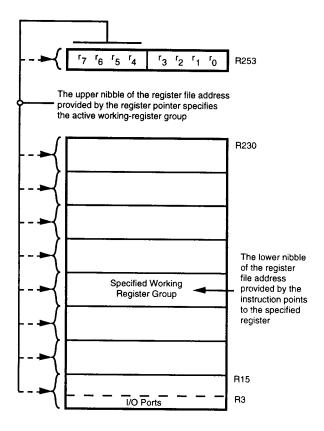

Expanded Register File. The register file has been expanded to allow for additional system control registers, and for mapping of additional peripheral devices along with I/O ports into the register address area (Figure 13). The Z8 register address space R0 through R15 has now been implemented as 16 groups of 16 registers per group. These register groups are known as the ERF (Expanded Register File). Bits 7-4 of register RP select the working register group. Bits 3-0 of register RP select the expanded register group (Figure 14). The registers that are used in the multiply/divide unit reside in the Expanded Register File at Bank E and those for the additional timer control words reside in Bank D. The rest of the Expanded Register is not physically implemented and is open for future expansion.

Register File. The Register File consists of four I/O port registers, 236 general-purpose registers and 16 control

and status registers. The instructions can access registers directly or indirectly via an 8-bit address field. The Z86C93 also allows short 4-bit register addressing using the Register Pointer (Figure 15). In the 4-bit mode, the Register File is divided into 16 working register groups, each occupying 16 continuous locations. The Register Pointer addresses the starting location of the active working-register group.

Note: Register Group E0-EF can only be accessed through working registers and indirect addressing modes.

Stack. The Z86C93 has a 16-bit Stack Pointer (R254-R255), used for external stack, that resides anywhere in the data memory. An 8-bit Stack Pointer (R255) is used for the internal stack that resides within the 236 general-purpose registers (R4-R239). The high byte of the Stack Pointer (SPH, Bits 8-15) can be used as a general-purpose register when using internal stack only.

Figure 14. Register Pointer Register

Figure 15. Register Pointer

# **FUNCTIONAL DESCRIPTION** (Continued)

DIVZR. Division by Zero (D0). When set to 1, this indicates an error of division by 0. This bit is read only.

### Example:

Upon reset, the status of the MDCON register is 100uuu00b (D7 to D0).

u = Undefined

x = Irrelevant

b = Binary

If multiplication operation is desired, the MDCON register is set to 010xxxxxb.

If the MDCON register is READ during multiplication, it would have a value of 000uuu00b.

Upon completion of multiplication, the result of the MDCON register is 100uuu00b.

If division operation is desired, the MDCON register is set to 001xxxxxb.

During division operation, the register would contain 000uu??b(?-value depends on the DIVIDEND, DIVISOR).

Upon completion of division operation, the MDCON register contains 100uuu??b.

Note that once the multiplication/division operation starts, all data registers (MREG5 through MREG0) are write-protected and so are the writable bits of the MDCON register. The write protection is released once the math unit operation is complete. However, the registers may be read at any time.

A multiplication sequence would look like:

- 1. Load multiplier and multiplicand.

- 2. Load MDCON register to start multiply operation.

- Wait for the DONE bit of the MDCON register to be set to 1 and then read results.

Note that while the multiply/divide operation is in progress, the programmer can use the Z8 to do other things. Also, since the multiplication/division takes a fixed number of cycles, he can start reading the results before the DONE bit is set.

During a division operation, the error flag bits are set at the beginning of the division operation which means the flag bits can be checked by the Z8 while the division operation is being done.

The two general purpose registers can be used as scratch pad registers or as external data memory address pointers during an LDE instruction. MREG0 through MREG5, if not used for multiplication or division, can be used as general purpose registers.

Performance of multiplication. The actual multiplication takes 17 internal clock cycles. It is expected that the chip would run at a 10 MHz internal clock frequency (external clock divided by two). This results in an actual multiplication time (16-bit x 16-bit) of 1.7  $\mu$ s. If the time to load operands and read results is included:

Number of internal clock cycles to load 5 registers: 30 Number of internal clock cycles to read 4 registers: 24

The total internal clock cycles to perform a multiplication is 71. This results in a net multiplication time of 7.1  $\mu$ s. Note that this would be the worst case. This assumes that all of the operands are loaded from the external world as opposed to some of the operands being already in place as a result of a previous operation whose destination register is one of the math unit registers.

Performance of division. The actual division needs 20 internal clock cycles. This translates to 2.0 µs for the actual division at 10 MHz (internal clock speed). If the time to load operands and read results is included:

Number of internal clock cycles to load operands: 42 Number of internal clock cycles to read results: 24

The total internal clock cycles to perform a division is 86. This translates to  $8.6~\mu s$  at 10~MHz.

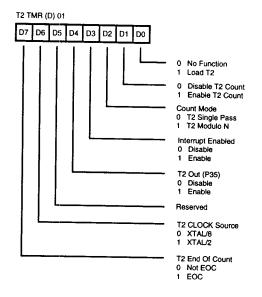

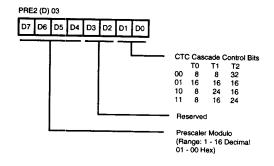

# Counter/Timers

This section describes the enhanced features of the counter/timers (CTC) on the Z86C93. It contains the register mapping of CTC registers and the bit functions of the newly added Timer2 control register.

In a standard Z8, there are two 8-bit programmable counter/timers (T0 and T1), each driven by its own 6-bit programmable prescaler. The T1 prescaler is driven by internal or external clock sources; however, the T0 prescaler is driven by the internal clock only.

The 6-bit prescalers divide the input frequency of the clock source by any integer number from 1 to 64. Each prescaler drives its counter, which decrements the value (1 to 256) that has been loaded into the counter. When the counter reaches the end of the count, a timer interrupt request IRQ4 (T0) or IRQ5 (T1), is generated.

# FUNCTIONAL DESCRIPTION (Continued)

# Operation

Except for the programmable down counter length and clock input, T2 is identical to T0.

T0 and T1 retain all their features except that now they are extendable interims of the down-counter length.

The output of T2, under program control, goes to an output pin (P35). Also, the interrupt generated by T2 is ORed with the interrupt request generated by P32. Note that the service routine then has to poll the T2 flag bit and also clear it (Bit 7 of T2 Timer Mode Register).

On power up, T0 and T1 are configured in the 8-bit down counter length mode (to be compatible with Z86C91) and T2 is in the 32-bit mode with its output disabled (no interrupt is generated and T2 output DOES NOT go to port pin P35).

The UART uses T0 for generating the bit clock. This means, while using UART, T0 should be in 8-bit mode. So, while using the UART there are only two independent timer/counters.

The counters are configured in the following manner:

| Timer | Mode   | Byte                                                                |

|-------|--------|---------------------------------------------------------------------|

| TO    | 8-bit  | Low Byte (T0)                                                       |

| TO    | 16-bit | High Byte (TO) + Low Byte (TO)                                      |

| T1    | 8-bit  | Low Byte (T1)                                                       |

| T1    | 16-bit | High Byte (T1)+ Low Byte (T1)                                       |

| T1    | 24-bit | High Byte (T0) + High Byte (T1) +<br>Low Byte (T1)                  |

| T2    | 16-bit | High Byte (T2) + Low Byte (T2)                                      |

| T2    | 24-bit | High Byte (T0) + High Byte (T2) +<br>Low Byte (T2)                  |

| T2    | 32-bit | High Byte (T0) + High Byte (T1) +<br>High Byte (T2) + Low Byte (T2) |

Note that the T2 interrupt is logically 0Red with P32 to generate IRQ0.

The T2 Timer Mode register is shown in Figure 19. Upon reaching end of count, bit 7 of this register is set to one. This bit IS NOT reset in hardware and it has to be cleared by the interrupt service routine.

T2 interrogates the state of the Count Mode Bit (D2) once it has counted down to it's zero value. T2 then makes the decision to continue counting (Module N Mode) or stop (Single Pass Mode). Observe this functionality if attempting to modify the count mode prior to the end of count bit (D7) being set.

The register map of the new CTC registers is shown in Figure 13. To high byte and T1 high byte are at the same relative locations as their respective low bytes, but in a different register bank.

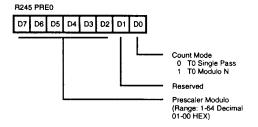

The T2 prescaler register is shown in Figure 19. Bits 1 and 0 of this register control the various cascade modes of the counters.

Figure 19. T2 Timer Mode Register (T2)

Figure 20. T2 Prescaler Register (PRE2)

| Name   | Source                       | Vector Location | Comments                                                                                                                                              |

|--------|------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ 0  | /DAV 0, P32, T2              | 0, 1            | External (P32), Programmable Rise or Fall Edge Triggered External (P33), Fall Edge Triggered External (P31), Programmable Rise or Fall Edge Triggered |

| IRQ 1, | P33                          | 2, 3            |                                                                                                                                                       |

| IRQ 2  | /DAV 2, P31, T <sub>IN</sub> | 4, 5            |                                                                                                                                                       |

| IRQ 3  | P30, Serial In               | 6, 7            | External (P30), Fall Edge Triggered                                                                                                                   |

| IRQ 4  | T0, Serial Out               | 8, 9            | Internal                                                                                                                                              |

| IRQ 5  | TI                           | 10, 11          | Internal                                                                                                                                              |

# Clock

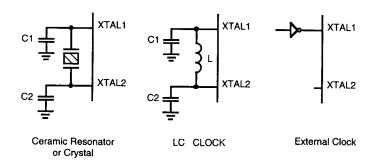

The Z86C93 on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal, LC, ceramic resonator, or any suitable external clock source (XTAL1=Input, XTAL2=Output). The external clock levels

are not TTL. The crystal should be AT cut, 1 MHz to 25 MHz max, and series resistance (RS) is less than or equal to 100 Ohms. The crystal should be connected across XTAL1 and XTAL2 using the recommended capacitors (10 pF<CL<100 pF) from each pin to ground (Figure 20).

Figure 22. Oscillator Configuration

## Power Down Modes

HALT. Turns off the internal CPU clock but not the XTAL oscillation. The counter/timers and the external interrupts IRQ0, IRQ1, IRQ2 and IRQ3 remain active. The devices are recovered by interrupts, either externally or internally generated. During HALT mode, /DS, /AS and R//W are HIGH. The outputs retain their preview value, and the inputs are floating.

STOP. This instruction turns off the internal clock and external crystal oscillation and reduces the standby current to 10  $\mu$ A or less. The STOP mode is terminated by a /RESET, which causes the processor to restart the application program at address 000CH.

In order to enter STOP (or HALT) mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user executes a NOP (opcode=OFFH) immediately before the appropriate sleep instruction, i.e.:

FF NOP ; clear the pipeline 6F STOP ; enter STOP mode

. . . . .

FF NOP ; clear the pipeline 7F HALT ; enter HALT mode

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Description       | Min  | Max  | Units |

|------------------|-------------------|------|------|-------|

| V <sub>CC</sub>  | Supply Voltage*   | -0.3 | +7.0 | v     |

| T <sub>STG</sub> | Storage Temp      | -65  | +150 | C     |

| T <sub>A</sub>   | Oper Ambient Temp | †    | †    | C     |

- Voltages on all pins with respect to GND.

- † See Ordering Information

Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

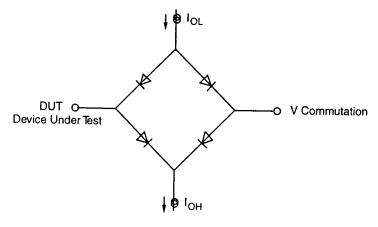

# STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin Test Load Diagram (Figure 23).

Figure 23. Test Load Diagram

# DC ELECTRICAL CHARACTERISTICS $V_{\text{CC}} = 3.3 V \pm 10\%$

| Sym | Parameter                    | T <sub>A</sub> = 0°C t<br>Min | o +70°C<br>Max      | Typical<br>at 25℃ | Units | Conditions                                                  |

|-----|------------------------------|-------------------------------|---------------------|-------------------|-------|-------------------------------------------------------------|

|     | Max Input Voltage            |                               | 7                   |                   | V     | I <sub>IN</sub> 250 μA                                      |

| н   | Clock Input High Voltage     | 0.8 V <sub>cc</sub>           | V <sub>cc</sub>     |                   | ٧     | Driven by External Clock Generator                          |

| L   | Clock Input Low Voltage      | -0.03                         | 0.1xV <sub>cc</sub> |                   | ٧     | Driven by External Clock Generator                          |

|     | Input High Voltage           | $0.7xV_{cc}$                  | V <sub>cc</sub>     |                   | V     | ,                                                           |

|     | Input Low Voltage            | -0.3                          | 0.1xV <sub>cc</sub> |                   | ٧     |                                                             |

| н   | Output High Voltge           | 1.8                           |                     |                   | ٧     | I <sub>DH</sub> = -1.0 mA                                   |

| i   | Output High Voltge           | V <sub>cc</sub> - 100mV       |                     |                   | V     | $I_{0H}^{(H)} = -100  \mu A$                                |

|     | Output Low Voltage           | 00                            | 0.4                 |                   | V     | $I_{01} = +1.0 \text{ mA}$                                  |

| 1   | Reset Input High Voltage     | $0.8xV_{cc}$                  | V <sub>cc</sub>     |                   | ٧     | o.                                                          |

|     | Reset Input Low Voltage      | -0.03                         | 0.1xV <sub>cc</sub> |                   | V     |                                                             |

|     | Input Leakage                | -2                            | 2                   |                   | μA    | Test at OV, V <sub>cc</sub>                                 |

|     | Output Leakage               | -2                            | 2                   |                   | μA    | Test at OV, V <sub>cc</sub>                                 |

|     | Reset Input Current          |                               | -80                 |                   | μA    | $V_{RI} = 0V$                                               |

|     | Supply Current               |                               | 30                  | 20                | mA    | @ 25 MHz [1]                                                |

| ,   | Stand By Current (HALT Mode) |                               | 12                  | 8                 | mA    | HALT Mode V <sub>IN</sub> =0V, V <sub>CC</sub> @ 25 MHz [1] |

| 2   | Stand By Current (HALT Mode) |                               | 8                   | 1                 | μA    | STOP Mode V <sub>N</sub> =0V, V <sub>CC</sub> [1]           |

|     | Auto Latch Low Current       | -10                           | 10                  | 5                 | μA    | 00                                                          |

Note: [1] All inputs driven to 0V,  $V_{\rm cc}$  and outputs floating.

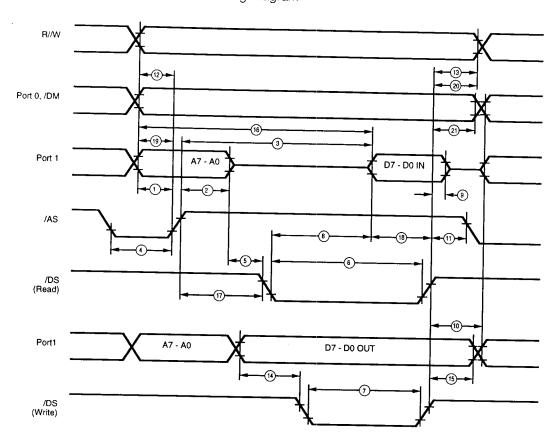

**AC CHARACTERISTICS**External I/O or Memory Read/Write Timing Diagram

Figure 24. External I/O or Memory Read/Write Timing

AC CHARACTERISTICS External I/O or Memory Read and Write; DSR/DSW; WAIT Timing Table

|              |                         |                                              |             |            |     | _ = 0°C    |           |            |                                               |       |

|--------------|-------------------------|----------------------------------------------|-------------|------------|-----|------------|-----------|------------|-----------------------------------------------|-------|

| No           | Sym                     | Parameter                                    | 33 I<br>Min | MHz<br>Max |     | MHz<br>Max | 20<br>Min | MHz<br>Max | Typical<br>V <sub>cc</sub> =5.0V <b>ଡ</b> 25℃ | Units |

| 1            | TdA(AS)                 | Address Valid To /AS Rise Delay              | 13          |            | 22  |            | 26        |            |                                               | ns    |

| 2            | TdAS(A)                 | /AS Rise To Address Hold Time                | 20          |            | 25  |            | 28        |            |                                               | ns    |

| 3<br>4       | TdAS(DI)<br>TwAS        | /AS Rise Data in Req'd Valid Delay           |             | 90         |     | 130        |           | 160        |                                               | ns    |

| <del>-</del> | TWAS                    | /AS Low Width                                | 20          |            | 28  |            | 36        |            |                                               | ns    |

| 5            | TdAZ(DSR)               | Address Float To /DS (Read)                  | 0           |            | 0   |            | 0         |            |                                               | ns    |

| 6            | TwDSR                   | /DS (Read) Low Width                         | 65          |            | 100 |            | 130       |            |                                               | ns    |

| 7            | TwDSW                   | /DS (Write) Low Width                        | 40          |            | 65  |            | 75        |            |                                               | ns    |

| 8            | TdDSR(DI)               | /DS (Read) To Data in Req'd Valid Delay      |             | 30         |     | 78         |           | 100        |                                               | ns    |

| 9            | ThDSR(DI)               | /DS Rise (Read) to Data In Hold Time         | 0           |            | 0   |            | 0         |            |                                               | ns    |

| 10           | TdDS(A)                 | /DS Rise To Address Active Delay             | 25          |            | 34  |            | 40        |            |                                               | ns    |

| 11<br>12     | TdDS(AS)                | /DS Rise To /AS Delay                        | 16          |            | 30  |            | 36        |            |                                               | ns    |

| 12           | TdR/W(AS)               | R/W To /AS Rise Delay                        | 12          |            | 26  |            | 32        |            |                                               | ns    |

| 13           | TdDS(R/W)               | /DS Rise To R/W Valid Delay                  | 12          | -          | 30  |            | 36        |            |                                               | ns    |

| 14<br>15     | TdDO(DSW)               | Data Out To /DS (Write) Delay                | 12          |            | 34  |            | 40        |            |                                               | ns    |

| 16           | ThDSW(DO)<br>TdA(DI)    | /DS Rise (Write) To Data Out Hold Time       | 12          |            | 34  |            | 40        |            |                                               | ns    |

|              |                         | Address To Data In Req'd Valid Delay         |             | 110        |     | 160        |           | 200        |                                               | ns    |

| 17           | TdAS(DSR)               | /AS Rise To /DS (Read) Delay                 | 20          |            | 40  |            | 48        |            |                                               | ns    |

| 18           | TaDI(DSR)               | Data In Set-up Time To /DS Rise Read         | 16          |            | 30  |            | 36        |            |                                               | ns    |

| 19<br>20     | TdDM(AS)<br>TdDS(DM)    | /DM To /AS Rise Delay                        | 10          |            | 22  |            | 26        |            |                                               | ns    |

|              |                         | /DS Rise To /DM Valid Delay                  |             |            |     |            |           |            | 34*                                           | ns    |

| 21           | ThDS(A)                 | /DS Rise To Address Valid Hold Time          |             |            |     |            |           |            | 34*                                           | ns    |

| 22<br>23     | TdXT(SCR)               | XTAL Falling to SCLK Rising                  |             |            |     |            |           |            | 20*                                           | ns    |

| 24           | TdXT(SCF)<br>TdXT(DSRF) | XTAL Falling to SCLK Falling                 |             |            |     |            |           |            | 23*                                           | ns    |

|              |                         | XTAL Falling to/DS Read Falling              |             |            |     |            |           |            | 29*                                           | ns    |

| 25           | TdXT(DSRR)              | XTAL Falling to /DS Read Rising              |             |            |     |            |           |            | 29*                                           | ns    |

| 26<br>27     | TdXT(DSWF)              | XTAL Falling to /DS Write Falling            |             |            |     |            |           |            | 29*                                           | ns    |

| 28           | TdXT(DSWF)<br>TsW(XT)   | XTAL Falling to /DS Write Rising             |             |            |     |            |           |            | 29*                                           | ns    |

| 29           | ThW(XT)                 | Wait Set-up Time<br>Wait Hold Time           |             |            |     |            |           |            | 10*                                           | ns    |

| 30           | TwW                     | Wait Hold Time<br>Wait Width (One Wait Time) |             |            |     |            |           |            | 15*                                           | ns    |

|              |                         | THE THEIR (ONE WAR TIME)                     |             |            |     |            |           |            | 25*                                           | ns    |

When using extended memory timing add 2 TpC.

Timing numbers given are for minimum TpC.

\* Preliminary value to be characterized.

# AC CHARACTERISTICS Handshake Timing Table

| No | Symbol                                | mbol Parameter             |     | C to +70°C |       |                   |

|----|---------------------------------------|----------------------------|-----|------------|-------|-------------------|

| 1  | T-DVD 410                             |                            | Min | Max        | Units | Data<br>Direction |

| 2  | TsDI(DAV)<br>ThDI(DAV)                | Data In Setup Time to /DAV | 0   |            |       |                   |

| 5  | ` '                                   | RDY to Data In Hold Time   | ñ   |            | ns    | ln                |

|    | TwDAV                                 | /DAV Width                 | 40  |            | ns    | In                |

|    | TdDAVIf(RDYf)                         | /DAV to RDY Delay          | 40  |            | ns    | In                |

|    | T ID NIII (DD)                        |                            |     | 70         | ns    | In                |

|    | TdDAVIr(RDYr)                         | DAV Rise to RDY Wait Time  |     |            |       |                   |

|    | TdRDYOr(DAVII)                        | RDY Rise to DAV Delay      | 0   | 40         | ns    | ln                |

|    | TdD0(DAV)                             | Data Out to DAV Delay      | 0   | _          | ns    | In                |

|    | TdDAV0f(RDYIf)                        | /DAV to RDY Delay          | _   | TpC        | ns    | Out               |

|    | <u> </u>                              |                            | 0   |            | ns    | Out               |

|    | TdRDYIf(DAVOr)                        | RDY to /DAV Rise Delay     |     |            |       | - Out             |

| 0  | TwRDY                                 | RDY Width                  | 40  | 70         | ns    | Out               |

|    | TdRDYIr(DAVOf)                        | RDY Rise to DAV Wait Time  | 40  |            | ns    | Out               |

|    | · · · · · · · · · · · · · · · · · · · | THE THIS TO DAY WAIT TIME  |     | 40         | ns    | Out               |

# **Z8 CONTROL REGISTERS**

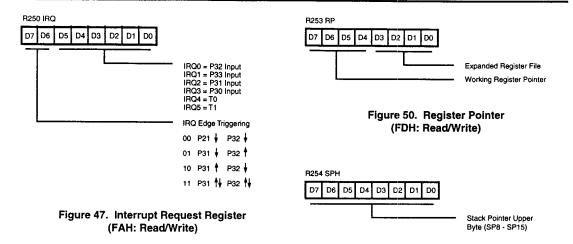

Figure 37. Serial I/O Register (F0H: Read/Write)

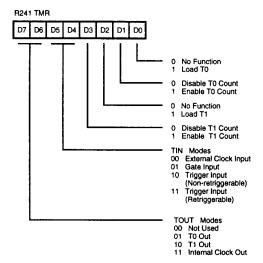

Figure 38. Timer Mode Register (F1H: Read/Write)

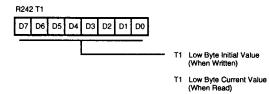

Figure 39. Counter/Timer 1 Register (F2H: Read/Write)

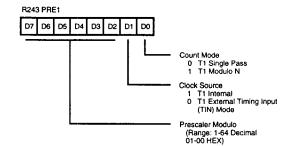

Figure 40. Prescaler 1 Register (F3H: Write Only)

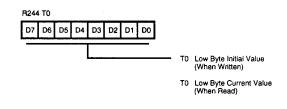

Figure 41. Counter/Timer 0 Register (F4H: Read/Write)

Figure 42. Prescaler 0 Register (F5H: Write Only)

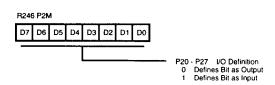

Figure 43. Port 2 Mode Register (F6H: Write Only)

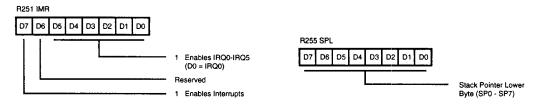

Figure 51. Stack Pointer High (FEH: Read/Write)

Figure 48. Interrupt Mask Register (FBH: Read/Write)

Figure 52. Stack Pointer Low (FFH: Read/Write)

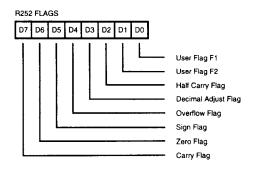

Figure 49. Flag Register (FCH: Read/Write)

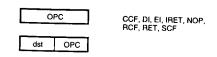

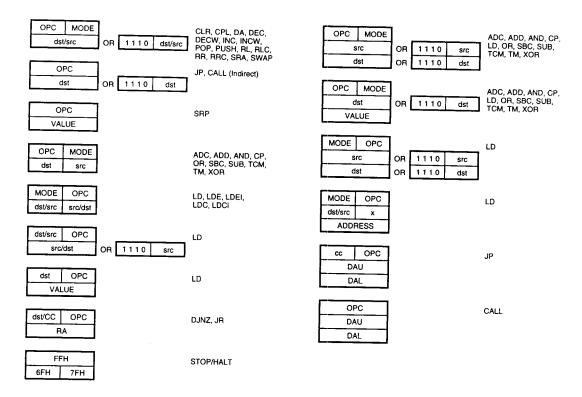

# **INSTRUCTION FORMATS**

# One-Byte Instructions

## **Two-Byte Instructions**

Three-Byte Instructions

# **INSTRUCTION SUMMARY**

Note: Assignment of a value is indicated by the symbol "  $\leftarrow$  ". For example:

notation "addr (n)" is used to refer to bit (n) of a given operand location. For example:

dst ← dst + src

dst (7)

indicates that the source data is added to the destination data and the result is stored in the destination location. The

refers to bit 7 of the destination operand.

# ORDERING INFORMATION

# Z86C93

20 MHz

44-pin PLCC

44-pin QFP

40-pin DIP

48-pin VQFP

Z86C9320VSC

Z86C9320FSC

Z86C9320PSC

Z80C9320ASC

25 MHz

44-pin PLCC

44-pin QFP

40-pin DIP

48-pin VQFP

Z86C9325VSC

Z86C9325FSC

Z86C9325PSC

Z80C9325ASC

33 MHz

44-pin PLCC

44-pin QFP

40-pin DIP

48-pin VQFP

Z86C9333VSC

Z86C9333FSC

Z86C9333PSC

Z80C9333ASC

For fast results, contact your local Zilog sales office for assistance in ordering the part desired.

### Package

V = Plastic Leaded Chip Carrier P = Plastic Dual In Line Package

# Longer Lead Time

F = Plastic Quad Flat Pack A = Very Small Quad Flat Pack

## Temperature

$S = 0^{\circ}C$  to  $+70^{\circ}C$

## Speed

20 = 20 MHz

25 = 25 MHz

33 = 33 MHz

## Environmental

C = Standard Flow

Example: