Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>Details</b> Product Status |                                                        |

|-------------------------------|--------------------------------------------------------|

| Draduct Ctatus                |                                                        |

| Product Status                | Obsolete                                               |

| Core Processor                | Z8                                                     |

| Core Size                     | 8-Bit                                                  |

| Speed                         | 25MHz                                                  |

| Connectivity                  | EBI/EMI, UART/USART                                    |

| Peripherals                   | -                                                      |

| Number of I/O                 | 24                                                     |

| Program Memory Size           | -                                                      |

| Program Memory Type           | ROMIess                                                |

| EEPROM Size                   | -                                                      |

| RAM Size                      | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd)    | 3V ~ 5.5V                                              |

| Data Converters               | -                                                      |

| Oscillator Type               | Internal                                               |

| Operating Temperature         | 0°C ~ 70°C (TA)                                        |

| Mounting Type                 | Surface Mount                                          |

| Package / Case                | 44-LQFP                                                |

| Supplier Device Package       | 44-LQFP (10x10)                                        |

| Purchase URL                  | https://www.e-xfl.com/product-detail/zilog/z86c9325fsc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### PRODUCT SPECIFICATION

# Z86C93

# CMOS Z8® MULTIPLY/DIVIDE MICROCONTROLLER

#### **FEATURES**

- Complete microcontroller, up to 24 I/O lines, and up to 64 Kbytes of addressable external space each for program and data memory.

- 16-bit x 16-bit hardwired multiplier with 32-bit product in 17 clock cycles.

- 32-bit x 16-bit hardwired divider with 16-bit quotient and 16-bit remainder in 20 clock cycles.

- 256-byte register file, including 236 general-purpose registers, up to three I/O port registers and 16 status and control registers.

- 17-byte Expanded Register File, including two generalpurpose registers and 15 status and control registers.

- Vectored, priority interrupts for I/O, counter/timers and UART.

- On-chip oscillator that accepts crystal or external clock drive.

- Two 16-bit counter timers with 6-bit prescalers.

- Third 16-bit counter/timer with 4-bit prescaler, one capture register and a fast decrement mode.

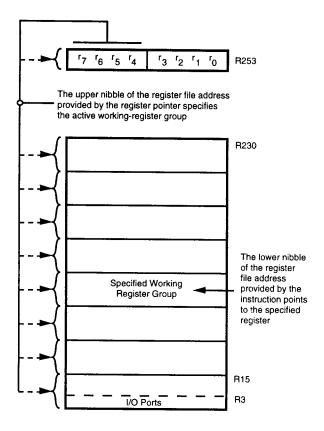

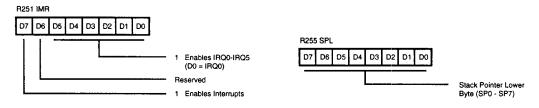

- Register Pointer for short, fast instructions that can access any one of the sixteen working register groups.

- Additional emulation signals SCLK, IACK, and /SYNC are made available.

- Two low power standby modes, STOP and HALT

- Full-duplex UART

- 3.3 ± 10% volt operation at 25 MHz

- $\blacksquare$  5.0  $\pm$  10% volt operation at 20, 25 and 33 MHz

#### **GENERAL DESCRIPTION**

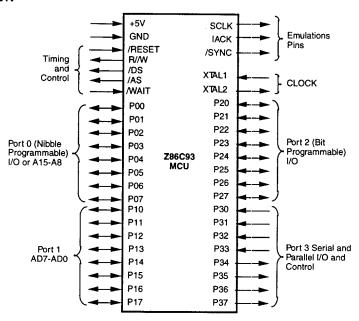

The Z86C93 is a CMOS ROMless Z8 microcontroller enhanced with a hardwired 16-bit x 16-bit multiplier and 32-bit/16-bit divider and three 16-bit counter timers (Figure 1). A capture register and a fast decrement mode is also provided. It is offered in 40-pin PDIP, 44-pin PLCC, 44-pin QFP and 48-pin VQFP (Figures 2, 3, 4, 5 and 6). Besides the four additional signals (SCLK, IACK, /SYNC and /WAIT), the Z86C93 is compatible with the Z86C91, yet it offers a much more powerful mathematical capability.

The Z86C93 provides up to 16 output address lines permitting an address space of up to 64 Kbytes of data and program memory each. Eight address outputs (AD7-AD0) are provided by a multiplexed, 8-bit, Address/Data bus. The remaining 8 bits can be provided by the software configuration of Port 0 to output address bits A15-A8.

#### PIN DESCRIPTION

Figure 2. Pin Functions

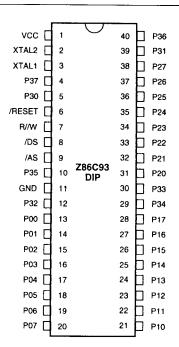

Pin# Symbol **Function** Direction V<sub>cc</sub> XTAL1 1 **Power Supply** Input 2 Crystal, Oscillator Clock Input 3 XTAL2 Crystal, Oscillator Clock Output 4 P37 Port 3 pin 7 Output 5 P30 Port 3 pin 0 Input 6 /RESET Reset Input 7 R//W Read/Write Output 8 /DS Data Strobe Output 9 /AS Address Strobe Output 10 P35 Port 3 pin 5 Output 11 GND Ground, GND Input 12 P32 Port 3 pin 2 Input 13-20 P00-P07 Port 0 pin 0,1,2,3,4,5,6,7 In/Output 21-28 P10-P17 Port 1 pin 0,1,2,3,4,5,6,7 In/Output 29 P34 Port 3 pin 4 Output 30 P33 Port 3 pin 3 Input 31-38 P20-P27 Port 2 pin 0,1,2,3,4,5,6,7 In/Output 39 P31 Port 3 pin 1 Input 40 P36 Port 3 pin 6 Output

Table 1. 40-Pin DIP Pin Identification

Figure 3. 40-Pin DIP

# PIN DESCRIPTION (Continued)

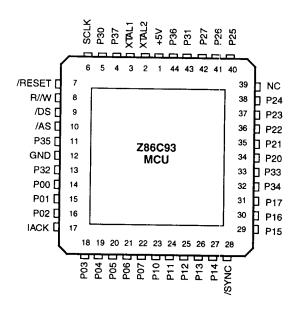

Figure 4. 44-Pin PLCC

Table 2. 44-Pin PLCC Pin Identification

| No | Symbol          | Function            | Direction | No    | Symbol  | Function             | Direction |

|----|-----------------|---------------------|-----------|-------|---------|----------------------|-----------|

| 1  | V <sub>cc</sub> | Power Supply        | Input     | 14-16 | P00-P02 | Port 0 pin 0,1,2     | In/Output |

| 2  | XTĂĽ2           | Crystal, Osc. Clock | Output    | 17    | IACK    | Int. Acknowledge     | Output    |

| 3  | XTAL1           | Crystal, Osc. Clock | Input     | 18-22 | P03-P07 | Port 0 pin 3,4,5,6,7 | In/Output |

| 4  | P37             | Port 3 pin 7        | Output    | 23-27 | P10-P14 | Port 1 pin 0,1,2,3,4 | In/Output |

| 5  | P30             | Port 3 pin 0        | Input     | 28    | /SYNC   | Synchronize Pin      | Output    |

| 6  | SCLK            | System Clock        | Output    | 29-31 | P15-P17 | Port 1 pin 5,6,7     | In/Output |

| 7  | /RESET          | Reset               | Input     | 32    | P34     | Port 3 pin 4         | Output    |

| 8  | R//W            | Read/Write          | Output    | 33    | P33     | Port 3 pin 3         | Input     |

| 9  | /DS             | Data Strobe         | Output    | 34-38 | P20-P24 | Port 2 pin 0,1,2,3,4 | In/Output |

| 10 | /AS             | Address Strobe      | Output    | 39    | N/C     | Not Connected (20 MH |           |

| 11 | P35             | Port 3 pin 5        | Output    |       | M/AIT   | WAIT (25 or 33 MHz)  | Input     |

| 12 | GND             | Ground GND          | Input     | 40-42 | P25-P27 | Port 2 pin 5,6,7     | In/Output |

| 13 | P32             | Port 3 pin 2        | Input     | 43    | P31     | Port 3 pin 1         | Input     |

|    |                 | <del></del>         |           | 44    | P36     | Port 3 pin 6         | Output    |

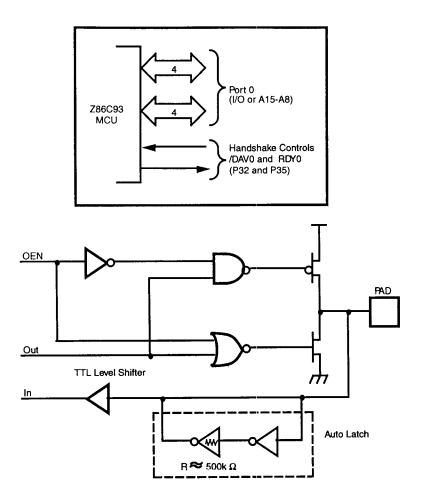

Figure 7. Port 0 Configuration

### PIN FUNCTIONS (Continued)

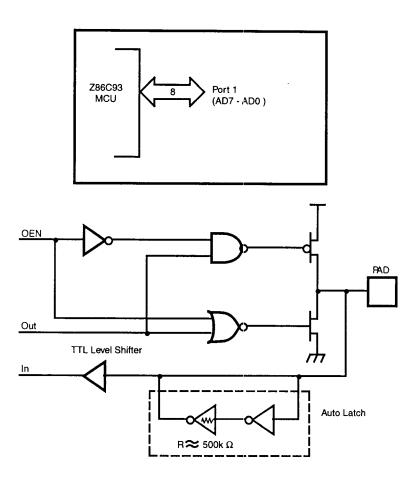

Port 1. (P10-P17). Port 1 is an 8-bit, TTL compatible port. It has multiplexed Address (A7-A0) and Data (D7-D0) ports for interfacing external memory (Figure 8).

If more than 256 external locations are required, Port 0 must output the additional lines.

Figure 8. Port 1 Configuration

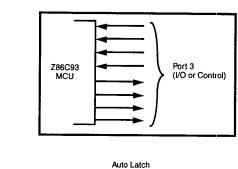

Port 3 P30-P37. Port 3 is an 8-bit, TTL compatible four fixed input and four fixed output ports. These eight I/O lines have four fixed (P30-P33) input and four fixed (P34-P37) output

ports. Port 3 pins P30 and P37 when used as serial I/O, are programmed as serial in and serial out, respectively (Figure 10 and Table 5).

Figure 10. Port 3 Configuration

Table 5. Port 3 Pin Assignments

| Pin# | 1/0 | CTC1            | Int. | P0HS | P2HS   | UART       | Ext. |

|------|-----|-----------------|------|------|--------|------------|------|

| P30  | ln  |                 | IRQ3 |      |        | Serial In  |      |

| P31  | In  | T <sub>IN</sub> | IRQ2 |      | D/R    |            |      |

| P32  | ln  |                 | IRQ0 | D/R  |        |            |      |

| P33  | In  |                 | IRQ1 |      |        |            |      |

| P34  | Out |                 |      |      |        |            | DM   |

| P35  | Out |                 |      | R/D  |        |            |      |

| P36  | Out | $T_out$         |      | , –  | R/D    |            |      |

| P37  | Out | 001             |      |      | . ,, & | Serial Out |      |

Port 3 is configured under software control to provide the following control functions: handshake for Ports 0 and 2 (/DAV and RDY); four external interrupt request signals (IRQ0-IRQ3); timer input and output signals ( $T_{\text{IN}}$  and  $T_{\text{OUT}}$ ), and Data Memory Select (/DM).

Port 3 lines P30 and P37 can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by the Counter/Timer 0.

The Z86C93 automatically adds a start bit and two stop bits to transmitted data (Figure 10). Odd parity is also available as an option. Eight data bits are always transmitted,

regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted characters.

Received data must have a start bit, eight data bits and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

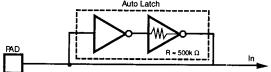

The Auto Latch on Port 3 puts a valid CMOS level on all CMOS inputs that are not externally driven. Whether this level is zero or one, cannot be determined. A valid CMOS level rather than a floating node reduces excessive supply current flow in the input buffer.

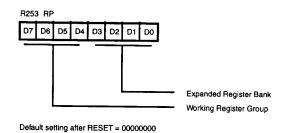

Figure 14. Register Pointer Register

Figure 15. Register Pointer

#### **FUNCTIONAL DESCRIPTION**

This section breaks down the Z86C93 into its main functional parts.

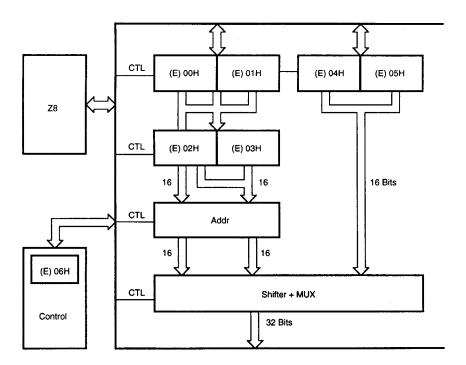

#### Multiply/Divide Unit

The Multiply/Divide unit describes the basic features, implementation details of the interface between the Z8 and the multiply/divide unit.

#### Basic features:

- 16-bit by 16-bit multiply with 32-bit product

- 32-bit by 16-bit divide with 16-bit quotient and 16-bit remainder

- Unsigned integer data format

- Simple interface to Z8

Interface to Z8. The following is a brief description of the register mapping in the multiply/divide unit and its interface to the Z8 (Figure 16).

The multiply/divide unit is interfaced like a peripheral. The only addressing mode available with the peripheral interface is register addressing. In other words, all of the operands are in the respective registers before a multiplication/division can start.

Register mapping. The registers used in the multiply/divide unit are mapped onto the expanded register file in Bank E. The exact register locations used are shown below.

| REGISTER | ADDRESS |

|----------|---------|

| MREG0    | (E) 00  |

| MREG1    | (E) 01  |

| MREG2    | (E) 02  |

| MREG3    | (E) 03  |

| MREG4    | (E) 04  |

| MREG5    | (E) 05  |

| MDCON    | (E) 06  |

| GPR      | (E) 14  |

| GPR      | (E) 15  |

Figure 16. Multiply/Divide Unit Block Diagram

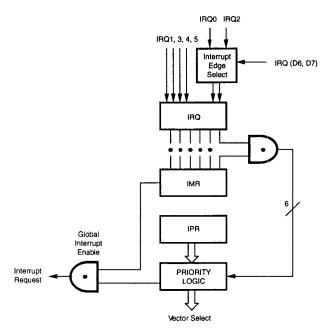

#### Interrupts

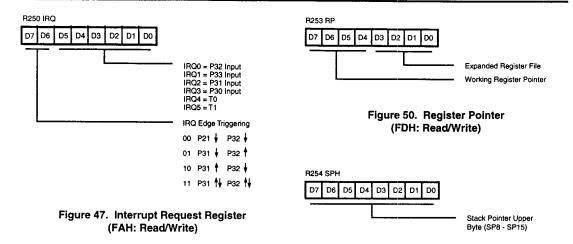

The Z86C93 has six different interrupts from nine different sources. The interrupts are maskable and prioritized. The nine sources are divided as follow: four sources are claimed by Port 3 lines P30-P33, one in Serial Out, one in Serial In, and three in the counter/timers. The Interrupt Mask Register globally or individually enables or disables the six interrupt requests. When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register. All Z86C93 interrupts are vectored through locations in the program memory. When an interrupt machine cycle is activated an interrupt request is granted. Thus, this disables all of the subsequent interrupts, save the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the Interrupt Request register is polled to determine which of the interrupt requests need service. Software initiated interrupts are supported by setting the appropriate bit in the Interrupt Request Register (IRQ).

Internal interrupt requests are sampled on the falling edge of the last cycle of every instruction. The interrupt request must be valid 5TpC before the falling edge of the last clock cycle of the currently executing instruction:

When the device samples a valid interrupt request, the next 48 (external) clock cycles are used to prioritize the interrupt, and push the two PC bytes and the FLAG register on the stack. The following nine cycles are used to fetch the interrupt vector from external memory. The first byte of the interrupt service routine is fetched beginning on the 58th TpC cycle following the internal sample point, which corresponds to the 63th TpC cycle following the external interrupt sample point.

Figure 21. Interrupt Block Diagram

| Name   | Source                       | Vector Location | Comments                                                                                                                                              |

|--------|------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ 0  | /DAV 0, P32, T2              | 0, 1            | External (P32), Programmable Rise or Fall Edge Triggered External (P33), Fall Edge Triggered External (P31), Programmable Rise or Fall Edge Triggered |

| IRQ 1, | P33                          | 2, 3            |                                                                                                                                                       |

| IRQ 2  | /DAV 2, P31, T <sub>IN</sub> | 4, 5            |                                                                                                                                                       |

| IRQ 3  | P30, Serial In               | 6, 7            | External (P30), Fall Edge Triggered                                                                                                                   |

| IRQ 4  | T0, Serial Out               | 8, 9            | Internal                                                                                                                                              |

| IRQ 5  | TI                           | 10, 11          | Internal                                                                                                                                              |

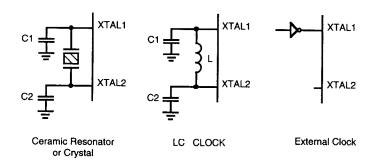

#### Clock

The Z86C93 on-chip oscillator has a high-gain, parallel-resonant amplifier for connection to a crystal, LC, ceramic resonator, or any suitable external clock source (XTAL1=Input, XTAL2=Output). The external clock levels

are not TTL. The crystal should be AT cut, 1 MHz to 25 MHz max, and series resistance (RS) is less than or equal to 100 Ohms. The crystal should be connected across XTAL1 and XTAL2 using the recommended capacitors (10 pF<CL<100 pF) from each pin to ground (Figure 20).

Figure 22. Oscillator Configuration

#### Power Down Modes

HALT. Turns off the internal CPU clock but not the XTAL oscillation. The counter/timers and the external interrupts IRQ0, IRQ1, IRQ2 and IRQ3 remain active. The devices are recovered by interrupts, either externally or internally generated. During HALT mode, /DS, /AS and R/W are HIGH. The outputs retain their preview value, and the inputs are floating.

STOP. This instruction turns off the internal clock and external crystal oscillation and reduces the standby current to 10  $\mu$ A or less. The STOP mode is terminated by a /RESET, which causes the processor to restart the application program at address 000CH.

In order to enter STOP (or HALT) mode, it is necessary to first flush the instruction pipeline to avoid suspending execution in mid-instruction. To do this, the user executes a NOP (opcode=OFFH) immediately before the appropriate sleep instruction, i.e.:

FF NOP ; clear the pipeline 6F STOP ; enter STOP mode

FF NOP ; clear the pipeline 7F HALT ; enter HALT mode

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                | Description                                    | Min              | Max               | Units |

|-------------------------------------------------------|------------------------------------------------|------------------|-------------------|-------|

| V <sub>cc</sub><br>T <sub>stg</sub><br>T <sub>4</sub> | Supply Voltage* Storage Temp Oper Ambient Temp | -0.3<br>-65<br>+ | +7.0<br>+150<br>+ | V C C |

- Voltages on all pins with respect to GND.

- † See Ordering Information

Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

### STANDARD TEST CONDITIONS

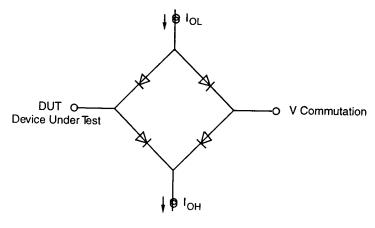

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to GND. Positive current flows into the referenced pin Test Load Diagram (Figure 23).

Figure 23. Test Load Diagram

# DC ELECTRICAL CHARACTERISTICS $V_{cc} = 5.0V \pm 10\%$

| Sym             | Parameter                 | T <sub>A</sub> ≃ 0°C to<br>Min | +70°C<br>Max           | Typical<br>at 25°C | Units | Conditions                                                   |

|-----------------|---------------------------|--------------------------------|------------------------|--------------------|-------|--------------------------------------------------------------|

|                 | Max Input Voltage         |                                | 7                      |                    |       | l <sub>,ν</sub> 250 μA                                       |

| $V_{ch}$        | Clock Input High Voltage  | 3.8                            | Vcc                    |                    | ٧     | Driven by External Clock Generator                           |

| V <sub>ci</sub> | Clock Input Low Voltage   | -0.03                          | V <sub>cc</sub><br>0.8 |                    | V     | Driven by External Clock Generator                           |

| V <sub>iH</sub> | Input High Voltage        | 2.0                            | V <sub>cc</sub>        |                    | ٧     |                                                              |

| V <sub>iL</sub> | Input Low Voltage         | -0.3                           | 0.8                    |                    | ٧     |                                                              |

| V <sub>OH</sub> | Output High Voltge        | 2.4                            |                        |                    | V     | I <sub>a</sub> =-2.0 mA                                      |

| OH<br>OL<br>BH  | Output High Voltage \     | √ <sub>cc</sub> -100mV         |                        |                    | ٧     | I <sub>он</sub> =-2.0 mA<br>I <sub>он</sub> = -100 µA        |

| OL              | Output Low Voltage        | •                              | 0.4                    |                    | ٧     | $I_{01}^{on} = +5 \text{ mA}$                                |

| / <sub>RH</sub> | Reset Input High Voltage  | 3.8                            | V <sub>cc</sub>        |                    | ٧     | OL                                                           |

| V <sub>RI</sub> | Reset Input Low Voltage   | -0.03                          | 0.8                    |                    | ٧     |                                                              |

| IL.             | Input Leakage             | -2                             | 2                      |                    | μA    | Test at OV, V <sub>cc</sub>                                  |

| OL.             | Output Leakage            | -2                             | 2                      |                    | μA    | Test at 0V, V <sub>CC</sub>                                  |

| iŘ.             | Reset Input Current       |                                | -80                    |                    | μA    | $V_{p_i} = 0V$                                               |

| CC              | Supply Current            |                                | 55                     | 35                 | mΑ    | @ 33 MHz [1]                                                 |

|                 |                           |                                | 40                     | 25                 | mA    | @ 25 MHz [1]                                                 |

|                 |                           |                                | 30                     | 20                 | mA    | @ 20 MHz [1]                                                 |

| CC1             | Standby Current (HALT Mod | e)                             | 15                     | 9                  | mA    | HALT Mode V <sub>IN</sub> = OV, V <sub>CC</sub> @ 25 MHz [1] |

|                 |                           |                                | 20                     | 15                 |       | HALT Mode $V_{in}^{in} = 0V$ , $V_{cc}^{ic}$ @ 33 MHz [1]    |

|                 |                           |                                | 12                     | 7                  | mΑ    | HALT Mode V <sub>IN</sub> = 0V, V <sub>CC</sub> @ 20 MHz [1] |

| CC2             | Standby Current (STOP Mod | le)                            | 10                     | 1                  | μA    | STOP Mode $V_{IN} = OV$ , $V_{CC}$ [1]                       |

| AL.             | Auto Latch Current        | -16                            | 16                     | 5                  | μA    | IN CC 1.1                                                    |

Note: [1] All inputs driven to 0V, or  $\rm \,V_{cc}$  and outputs floating.

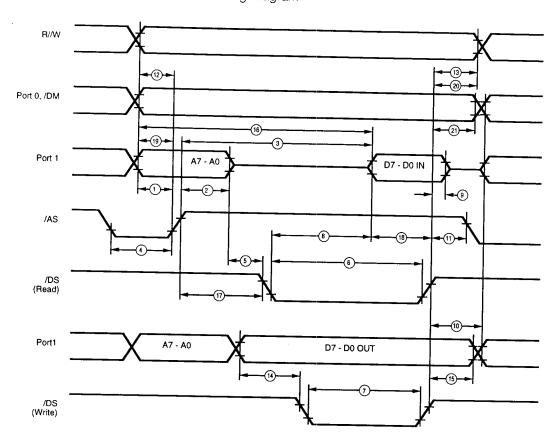

**AC CHARACTERISTICS**External I/O or Memory Read/Write Timing Diagram

Figure 24. External I/O or Memory Read/Write Timing

# **EXPANDED REGISTER FILE CONTROL REGISTERS**

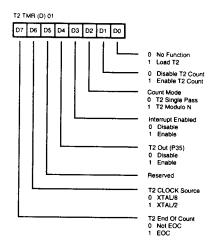

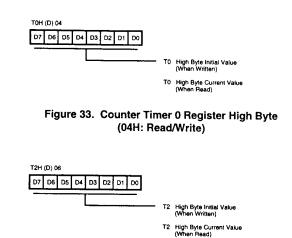

Figure 30. Timer 2 Mode Register (01H: Read/Write)

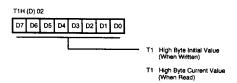

Figure 31. Counter Timer 1 Register High Byte (02H: Read/Write)

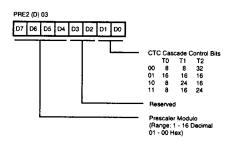

Figure 32. Prescaler 2 Register High Byte (03H: Write Only)

Figure 34. Counter Timer 2 Register High Byte (06H: Read/Write)

Figure 35. Counter Timer 2 Register Low Byte (07H: Read/Write)

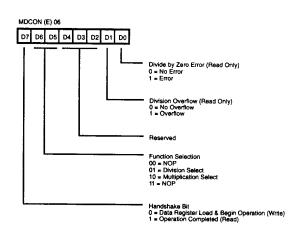

Figure 36. Multiply/Divide Control Register (MDCON)

#### **Z8 CONTROL REGISTERS**

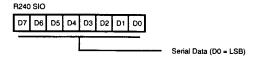

Figure 37. Serial I/O Register (F0H: Read/Write)

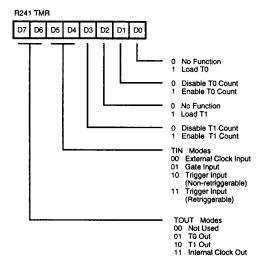

Figure 38. Timer Mode Register (F1H: Read/Write)

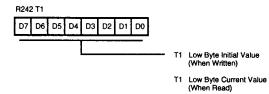

Figure 39. Counter/Timer 1 Register (F2H: Read/Write)

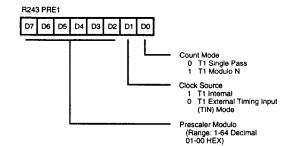

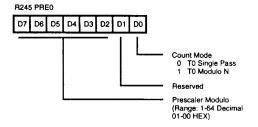

Figure 40. Prescaler 1 Register (F3H: Write Only)

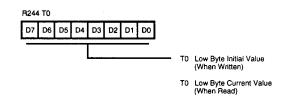

Figure 41. Counter/Timer 0 Register (F4H: Read/Write)

Figure 42. Prescaler 0 Register (F5H: Write Only)

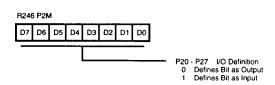

Figure 43. Port 2 Mode Register (F6H: Write Only)

Figure 51. Stack Pointer High (FEH: Read/Write)

Figure 48. Interrupt Mask Register (FBH: Read/Write)

Figure 52. Stack Pointer Low (FFH: Read/Write)

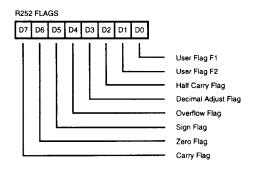

Figure 49. Flag Register (FCH: Read/Write)

# **CONDITION CODES**

| Value | Mnemonic | Meaning                        | Flags Set               |

|-------|----------|--------------------------------|-------------------------|

| 1000  |          | Always True                    |                         |

| 0111  | С        | Carry                          | C = 1                   |

| 1111  | NC       | No Carry                       | C = 0                   |

| 0110  | Z        | Zero                           | Z = 1                   |

| 1110  | NZ       | Not Zero                       | Z = 0                   |

| 1101  | PL       | Plus                           | S = 0                   |

| 0101  | MI       | Minus                          | S = 1                   |

| 0100  | OV       | Overflow                       | V = 1                   |

| 1100  | NOV      | No Overflow                    | V = 0                   |

| 0110  | EQ       | Equal                          | Z = 1                   |

| 1110  | NE       | Not Equal                      | Z = 0                   |

| 1001  | GE       | Greater Than or Equal          | (S XOR V) = 0           |

| 0001  | LT       | Less than                      | (S XOR V) = 1           |

| 1010  | GT       | Greater Than                   | [Z OR (S XOR V)] = 0    |

| 0010  | LE       | Less Than or Equal             | [Z OR (S XOR V)] = 1    |

| 1111  | UGE      | Unsigned Greater Than or Equal | C = 0                   |

| 0111  | ULT      | Unsigned Less Than             | C = 1                   |

| 1011  | UGT      | Unsigned Greater Than          | (C = 0  AND  Z = 0) = 1 |

| 0011  | ULE      | Unsigned Less Than or Equal    | (C OR Z) = 1            |

| 0000  |          | Never True                     | (, -,                   |

| INSTRUC <sup>*</sup> | TION SI | IMMARY | (Continue) | ed) |

|----------------------|---------|--------|------------|-----|

|                      |         |        |            |     |

| Instruction and Operation                                                | Address<br>Mode | Opcode<br>Byte (Hex) |   | Flags<br>Affected |   |   |   |   |  |  |

|--------------------------------------------------------------------------|-----------------|----------------------|---|-------------------|---|---|---|---|--|--|

|                                                                          | dst src         | _,,                  | С | Z                 | s | ٧ | D | Н |  |  |

| ADC dst, src<br>dst←dst + src +C                                         | †               | 1[]                  | * | *                 | * | * | 0 | * |  |  |

| ADD dst, src<br>dst←dst + src                                            | †               | 0[]                  | * | *                 | * | * | 0 | * |  |  |

| AND dst, src<br>dst←dst AND src                                          | t               | 5[]                  | - | *                 | * | 0 | - | - |  |  |

| CALL dst<br>SP←SP - 2<br>@SP←PC,<br>PC←dst                               | DA<br>IRR       | D6<br>D4             | - | -                 | - | - | - | - |  |  |

| CCF<br>C←NOT C                                                           |                 | EF                   | * | •                 | • | - | - | - |  |  |

| CLR dst<br>dst←0                                                         | R<br>IR         | B0<br>B1             | - | -                 | - | - | • | - |  |  |

| COM dst<br>dst←NOT dst                                                   | R<br>IR         | 60<br>61             | - | *                 | * | 0 | - | • |  |  |

| CP dst, src<br>dst - src                                                 | t               | A[ ]                 | * | *                 | * | * | - | - |  |  |

| <b>DA</b> dst<br>dst←DA dst                                              | R<br>IR         | 40<br>41             | * | *                 | * | X | - | - |  |  |

| DEC dst<br>dst←dst - 1                                                   | R<br>IR         | 00<br>01             | - | *                 | * | * | • | • |  |  |

| DECW dst<br>dst←dst - 1                                                  | RR<br>IR        | 80<br>81             | - | *                 | * | * | - | - |  |  |

| <b>DI</b><br>IMR(7)←0                                                    |                 | 8F                   | - | -                 | - | - | - | - |  |  |

| DJNZr, dst<br>r←r - 1<br>if r ≠ 0<br>PC←PC + dst<br>Range: +127,<br>-128 | RA              | rA<br>r = 0 - F      | - | -                 | • | - | - | - |  |  |

| <b>EI</b><br>1MR(7)←1                                                    |                 | 9F                   | - | -                 | - | • | - | - |  |  |

| HALT                                                                     |                 | 7F                   | - | -                 | - | - | - | - |  |  |

| Instruction and Operation | Mod | iress<br>de<br>src | Opcode<br>Byte (Hex) |   | ags<br>fec<br>Z |   | v | D | н |

|---------------------------|-----|--------------------|----------------------|---|-----------------|---|---|---|---|

|                           | ası | SIC                |                      | _ | _               |   | _ | _ | n |

| INC dst                   | r   |                    | rE                   | - | *               | * | * | - | - |

| dst←dst + 1               |     |                    | r = 0 - F            |   |                 |   |   |   |   |

|                           | R   |                    | 20                   |   |                 |   |   |   |   |

|                           | IR  |                    | 21                   |   |                 |   |   |   |   |

| INCW dst                  | RR  |                    | A0                   | _ | *               | * | * | - | - |

| dst←dst + 1               | IR  |                    | A1                   |   |                 |   |   |   |   |

| IRET                      |     |                    | BF                   | * | *               | * | * | * | * |

| FLAGS←@SP;                |     |                    |                      |   |                 |   |   |   |   |

| SP←SP + 1                 |     |                    |                      |   |                 |   |   |   |   |

| PC←@SP;                   |     |                    |                      |   |                 |   |   |   |   |

| SP←-SP + 2;               |     |                    |                      |   |                 |   |   |   |   |

| IMR(7)←1                  |     |                    |                      |   |                 |   |   |   |   |

| JP cc, dst                | DA  |                    | cD                   |   | -               | - | - | - | - |

| if cc is true             |     |                    | c = 0 - F            |   |                 |   |   |   |   |

| PC←dst                    | IRR |                    | 30                   |   |                 |   |   |   |   |

| JR cc, dst                | RA  |                    | сВ                   | - | -               | _ | _ | _ |   |

| if cc is true,            |     |                    | c = 0 - F            |   |                 |   |   |   |   |

| PC←PC + dst               |     |                    |                      |   |                 |   |   |   |   |

| Range: +127,              |     |                    |                      |   |                 |   |   |   |   |

| -128                      |     |                    |                      |   |                 |   |   |   |   |

| LD dst, src               | r   | lm                 | rC                   | - | -               | - | _ | _ | - |

| dst←src                   | r   | R                  | r8                   |   |                 |   |   |   |   |

|                           | R   | r                  | r9                   |   |                 |   |   |   |   |

|                           |     |                    | r = 0 - F            |   |                 |   |   |   |   |

|                           | r   | Χ                  | C7                   |   |                 |   |   |   |   |

|                           | X   | r                  | D7                   |   |                 |   |   |   |   |

|                           | r   | lr                 | E3                   |   |                 |   |   |   |   |

|                           | lr  | r                  | F3                   |   |                 |   |   |   |   |

|                           | R   | R                  | E4                   |   |                 |   |   |   |   |

|                           | R   | IR                 | E5                   |   |                 |   |   |   |   |

|                           | R   | IM                 | E6                   |   |                 |   |   |   |   |

|                           | IR  | IM                 | E7                   |   |                 |   |   |   |   |

|                           | IR  | R                  | F5                   |   |                 |   |   |   |   |

| LDC dst, src              | r   | lrr                | C2                   | - | -               | - | • | - | - |

| LDCI dst, src             | lr  | Irr                | СЗ                   | - | -               | - | - | - | - |

| dst←src                   |     |                    |                      |   |                 |   |   |   |   |

| r←r +1;                   |     |                    |                      |   |                 |   |   |   |   |

| rr←rr + 1                 |     |                    |                      |   |                 |   |   |   |   |

|                           |     |                    |                      |   |                 |   |   |   |   |

|                           |     |                    |                      |   |                 |   |   |   |   |

### **OPCODE MAP**

|                    | Lower Nibble (Hex) |                          |                           |                                |                                  |                              |                               |                             |                                   |                     |                            |                           |                         |             |                      |             |                    |

|--------------------|--------------------|--------------------------|---------------------------|--------------------------------|----------------------------------|------------------------------|-------------------------------|-----------------------------|-----------------------------------|---------------------|----------------------------|---------------------------|-------------------------|-------------|----------------------|-------------|--------------------|

|                    |                    | 0                        | 1                         | 2                              | 3                                | 4                            | 5                             | 6                           | 7                                 | 8                   | 9                          | A                         | В                       | С           | D                    | Ε           | F                  |

|                    | 0                  | 6.5<br><b>DEC</b><br>R1  | 6.5<br>DEC<br>IR1         | 6.5<br>ADD<br>r1, r2           | 6.5<br>ADD<br>r1, lr2            | 10.5<br>ADD<br>R2, R1        | 10.5<br>ADD<br>IR2, R1        | 10.5<br>ADD<br>R1, IM       | 10.5<br>ADD<br>IR1, IM            | 6.5<br>LD<br>r1, R2 | 6.5<br><b>LD</b><br>r2, R1 | 12/10.5<br>DJNZ<br>r1, RA | 12/10.0<br>JR<br>cc, RA | 6.5<br>LD   | 12.10.0<br><b>JP</b> | 6.5<br>INC  |                    |

|                    | 1                  | 6.5<br>RLC<br>R1         | 6.5<br>RLC<br>IR1         | 6.5<br>ADC<br>r1, r2           | 6.5<br>ADC<br>r1, Ir2            | 10.5<br>ADC<br>R2, R1        | 10.5<br>ADC<br>IR2, R1        | 10.5<br>ADC<br>R1, IM       | 10.5<br>ADC<br>IR1, IM            |                     |                            |                           | ١                       | r1, IM      | ∞, DA                |             | -                  |

|                    | 2                  | 6.5<br>INC<br>R1         | 6.5<br>INC<br>IR1         | 6.5<br>SUB<br>r1, r2           | 6.5<br>SUB<br>r1, Ir2            | 10.5<br>SUB<br>R2, R1        | 10.5<br>SUB<br>IR2, R1        | 10.5<br>SUB<br>R1, IM       | 10.5<br>SUB<br>IR1, IM            |                     |                            |                           |                         |             |                      |             |                    |

|                    | 3                  | 8.0<br><b>JP</b><br>IRR1 | 6.1<br>SRP                | 6.5<br>SBC<br>r1, r2           | 6.5<br>SBC<br>r1, lr2            | 10.5<br>SBC<br>R2, R1        | 10.5<br>SBC<br>IR2, R1        | 10.5<br>SBC<br>R1, IM       | 10.5<br>SBC                       |                     |                            |                           |                         |             |                      |             |                    |

|                    | 4                  | 8.5<br><b>DA</b><br>R1   | 8.5<br><b>DA</b><br>IR1   | 6.5<br>OR<br>r1, r2            | 6.5<br>OR<br>r1, lr2             | 10.5<br>OR<br>R2, R1         | 10.5<br>OR<br>IR2, R1         | 10.5<br>OR<br>R1, IM        | 10.5<br>OR                        |                     |                            |                           |                         |             |                      |             |                    |

|                    | 5                  | 10.5<br>POP<br>R1        | 10.5<br>POP<br>IR1        | 6.5<br>AND<br>r1, r2           | 6.5<br>AND<br>r1, lr2            | 10.5<br>AND<br>R2, R1        | 10.5<br>AND<br>IR2, R1        | 10.5<br>AND<br>R1, IM       | IR1, IM<br>10.5<br>AND<br>IR1, IM |                     |                            |                           |                         |             |                      |             |                    |

| (xe                | 6                  | 6.5<br><b>COM</b><br>R1  | 6.5<br>COM<br>IR1         | 6.5<br><b>TCM</b><br>r1, r2    | 6.5<br>TCM<br>r1, ir2            | 10.5<br>TCM<br>R2, R1        | 10.5<br>TCM<br>IR2, R1        | 10.5<br>TCM<br>R1, IM       | 10.5<br>TCM<br>IR1, IM            |                     |                            |                           |                         |             |                      |             | 6.0<br>STOP        |

| Upper Nibble (Hex) | 7                  | 10/12.1<br>PUSH<br>R2    | 12/14.1<br>PUSH<br>IR2    | 6.5<br><b>TM</b><br>r1, r2     | 6.5<br>TM<br>r1, Ir2             | 10.5<br><b>TM</b><br>R2, R1  | 10.5<br>TM                    | 10.5<br><b>TM</b><br>F1, IM | 10.5<br>TM<br>IR1, IM             |                     |                            |                           |                         |             |                      |             | 7.0<br><b>HALT</b> |

| pper Ni            | 8                  | 10.5<br>DECW<br>RR1      | 10.5<br>DECW<br>IR1       | 12.0<br>LDE<br>r1, lrr2        | 18.0<br><b>LDEI</b><br>Ir1, Irr2 |                              |                               | ,                           |                                   |                     |                            |                           |                         |             |                      |             | 6.1<br>Dt          |

| _                  | 9                  | 6.5<br>RL<br>R1          | 6.5<br><b>RL</b><br>IR1   | 12.0<br><b>LDE</b><br>r2, irr1 | 18.0<br><b>LDEI</b><br>Ir2, Irr1 |                              |                               |                             |                                   |                     |                            |                           |                         |             |                      |             | 6.1<br>EI          |

|                    | A                  | 10.5<br>INCW<br>RR1      | 10.5<br>INCW<br>IR1       | 6.5<br><b>CP</b><br>r1, r2     | 6.5<br><b>CP</b><br>r1, lr2      | 10.5<br><b>CP</b><br>R2, R1  | 10.5<br><b>CP</b><br>IR2, R1  | 10.5<br><b>CP</b><br>R1, IM | 10.5<br>CP<br>IR1, IM             |                     |                            |                           |                         |             |                      |             | 14.0<br>RET        |

|                    | В                  | 6.5<br><b>CLR</b><br>R1  | 6.5<br>CLR<br>IR1         | 6.5<br><b>XOR</b><br>r1, r2    | 6.5<br><b>XOR</b><br>r1, lr2     | 10.5<br><b>XOR</b><br>R2, R1 | 10.5<br><b>XOR</b><br>IR2, R1 | 10.5<br>XOR                 | 10.5<br>XOR<br>IR1, IM            |                     |                            |                           |                         |             |                      |             | 16.0<br>IRET       |

| 1                  | С                  | 6.5<br>RAC<br>R1         | 6.5<br>RRC<br>IR1         | 12.0<br>LDC<br>r1, lrr2        | 18.0<br><b>LDCI</b><br>lr1, lrr2 |                              |                               |                             | 10.5<br>LD<br>r1,x,R2             |                     |                            |                           |                         |             |                      |             | 6.5<br>RCF         |

| 1                  | D                  | 6.5<br><b>SRA</b><br>R1  | 6.5<br><b>SRA</b><br>IR1  | 12.0<br>LDC<br>r2, lrr1        | 18.0<br><b>LDCI</b><br>lr2, lrr1 | 20.0<br>CALL*<br>IRR1        |                               | 20.0<br>CALL                | 10.5<br>LD<br>r2,x,R1             |                     |                            |                           |                         |             |                      |             | 6.5<br>SCF         |

| ı                  | Ē                  | 6.5<br>RR<br>R1          | 6.5<br>RR<br>IR1          |                                | 6.5<br><b>LD</b><br>r1, IR2      | 10.5<br><b>LD</b><br>R2, R1  | 10.5<br>LD<br>R2, R1          | 10.5<br>LD                  | 10.5<br>LD                        |                     |                            |                           |                         |             |                      |             | 6.5<br><b>CCF</b>  |

| ı                  | F                  | 8.5<br>SWAP<br>R1        | 8.5<br><b>SWAP</b><br>IR1 |                                | 6.5<br><b>LD</b><br>lr1, r2      |                              | 10.5<br>LD<br>R2, IR1         |                             |                                   |                     |                            |                           |                         |             |                      |             | 6.0<br><b>NOP</b>  |

|                    | •                  |                          |                           |                                |                                  |                              | <del></del>                   |                             |                                   |                     |                            | $\Rightarrow$             |                         | <del></del> | $\Rightarrow$        | <del></del> |                    |

|                    |                    |                          | 2                         |                                |                                  |                              | 3                             | Byt                         | es per In                         | structio            | on                         | 2                         |                         |             | 3                    | 1           |                    |

Legend: R = 8-bit address r = 4-bit address  $R_1$  or  $r_2 = D$ st address  $R_1$  or  $r_2 = S$ rc address

Sequence: Opcode, First Operand, Second Operand

Note: The blank areas are not defined.

\* 2-byte instruction appears as a 3-byte instruction

# ZILOG DOMESTIC SALES OFFICES AND TECHNICAL CENTERS

## **CALIFORNIA** Agoura ...... 818-707-2160 Irvine ......714-453-9701 COLORADO **FLORIDA** Largo .......813-585-2533 **GEORGIA** ILLINOIS Schaumburg ......708-517-8080 **MINNESOTA** NEW HAMPSHIRE OHIO OREGON Portland ......503-274-6250 **PENNSYLVANIA** Ambler.....215-653-0230 **TEXAS** WASHINGTON

#### **INTERNATIONAL SALES OFFICES**

CANIADA

| Toronto                       | 416-673-0634                  |

|-------------------------------|-------------------------------|

| GERMANY<br>Munich<br>Sömmerda | 49-8967-2045<br>49-3634-23906 |

| JAPAN<br>Tokyo                | 81-3-3587-0528                |

| HONG KONG<br>Kowloon          | 852-7238979                   |

| KOREA<br>Seoul                | 82-2-577-3272                 |

| SINGAPORE<br>Singapore        | 65-2357155                    |

| TAIWAN<br>Taipei              | 886-2-741-3125                |

| UNITED KINGDOM<br>Maidenhead  | 44-628-392-00                 |

© 1992 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of mer-

chantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 Telex 910-338-7621 FAX 408 370-8056