Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | Z8                                                         |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 33MHz                                                      |

| Connectivity               | EBI/EMI, UART/USART                                        |

| Peripherals                | -                                                          |

| Number of I/O              | 24                                                         |

| Program Memory Size        | -                                                          |

| Program Memory Type        | ROMIess                                                    |

| EEPROM Size                | -                                                          |

| RAM Size                   | 236 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                            |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 44-LQFP                                                    |

| Supplier Device Package    | 44-LQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86c9333fsc00tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### PRODUCT SPECIFICATION

## Z86C93

# CMOS Z8® MULTIPLY/DIVIDE MICROCONTROLLER

### **FEATURES**

- Complete microcontroller, up to 24 I/O lines, and up to 64 Kbytes of addressable external space each for program and data memory.

- 16-bit x 16-bit hardwired multiplier with 32-bit product in 17 clock cycles.

- 32-bit x 16-bit hardwired divider with 16-bit quotient and 16-bit remainder in 20 clock cycles.

- 256-byte register file, including 236 general-purpose registers, up to three I/O port registers and 16 status and control registers.

- 17-byte Expanded Register File, including two generalpurpose registers and 15 status and control registers.

- Vectored, priority interrupts for I/O, counter/timers and UART.

- On-chip oscillator that accepts crystal or external clock drive.

- Two 16-bit counter timers with 6-bit prescalers.

- Third 16-bit counter/timer with 4-bit prescaler, one capture register and a fast decrement mode.

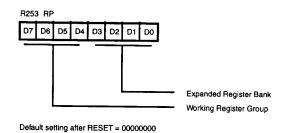

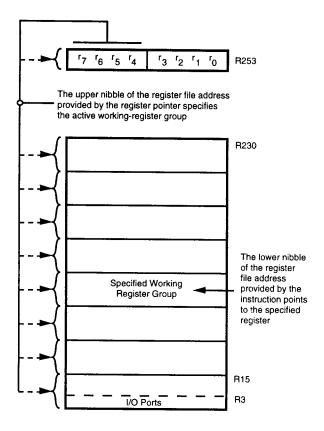

- Register Pointer for short, fast instructions that can access any one of the sixteen working register groups.

- Additional emulation signals SCLK, IACK, and /SYNC are made available.

- Two low power standby modes, STOP and HALT

- Full-duplex UART

- 3.3 ± 10% volt operation at 25 MHz

- $\blacksquare$  5.0  $\pm$  10% volt operation at 20, 25 and 33 MHz

### **GENERAL DESCRIPTION**

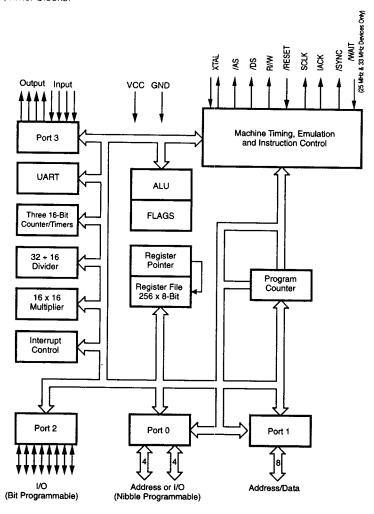

The Z86C93 is a CMOS ROMless Z8 microcontroller enhanced with a hardwired 16-bit x 16-bit multiplier and 32-bit/16-bit divider and three 16-bit counter timers (Figure 1). A capture register and a fast decrement mode is also provided. It is offered in 40-pin PDIP, 44-pin PLCC, 44-pin QFP and 48-pin VQFP (Figures 2, 3, 4, 5 and 6). Besides the four additional signals (SCLK, IACK, /SYNC and /WAIT), the Z86C93 is compatible with the Z86C91, yet it offers a much more powerful mathematical capability.

The Z86C93 provides up to 16 output address lines permitting an address space of up to 64 Kbytes of data and program memory each. Eight address outputs (AD7-AD0) are provided by a multiplexed, 8-bit, Address/Data bus. The remaining 8 bits can be provided by the software configuration of Port 0 to output address bits A15-A8.

### **GENERAL DESCRIPTION** (Continued)

There are 256 registers located on-chip and organized as 236 general-purpose registers, 16 control and status registers, and four I/O port registers. The register file can be divided into sixteen groups of 16 working registers each. Configuration of the registers in this manner allows the use of short format instructions; in addition, any of the individual registers can be accessed directly. There are an additional 17 registers implemented in the Expanded Register File in Banks D and E. Two of the registers may be used as general-purpose registers, while 15 registers supply the data and control functions for the Multiply/ Divide Unit and Counter/Timer blocks.

### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit                | Device          |

|------------|------------------------|-----------------|

| Power      | V <sub>cc</sub><br>GND | V <sub>DO</sub> |

| Ground     | GND                    | V <sub>ss</sub> |

Figure 1. Functional Block Diagram

### PIN DESCRIPTION

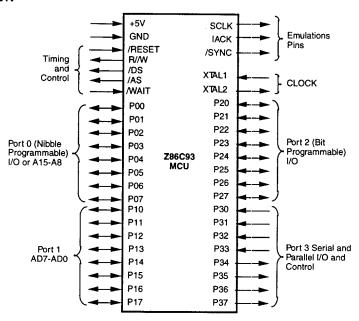

Figure 2. Pin Functions

Pin# Symbol **Function** Direction V<sub>cc</sub> XTAL1 1 **Power Supply** Input 2 Crystal, Oscillator Clock Input 3 XTAL2 Crystal, Oscillator Clock Output 4 P37 Port 3 pin 7 Output 5 P30 Port 3 pin 0 Input 6 /RESET Reset Input 7 R//W Read/Write Output 8 /DS Data Strobe Output 9 /AS Address Strobe Output 10 P35 Port 3 pin 5 Output 11 GND Ground, GND Input 12 P32 Port 3 pin 2 Input 13-20 P00-P07 Port 0 pin 0,1,2,3,4,5,6,7 In/Output 21-28 P10-P17 Port 1 pin 0,1,2,3,4,5,6,7 In/Output 29 P34 Port 3 pin 4 Output 30 P33 Port 3 pin 3 Input 31-38 P20-P27 Port 2 pin 0,1,2,3,4,5,6,7 In/Output 39 P31 Port 3 pin 1 Input 40 P36 Port 3 pin 6 Output

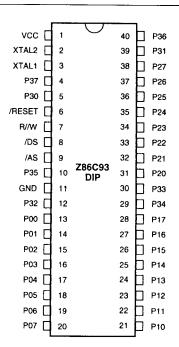

Table 1. 40-Pin DIP Pin Identification

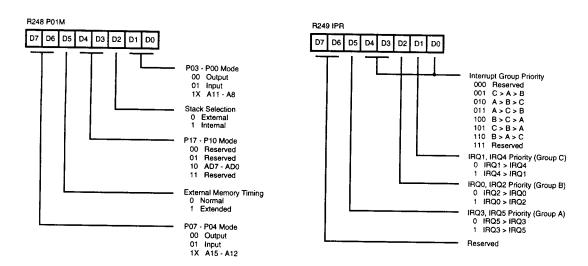

Figure 3. 40-Pin DIP

## PIN DESCRIPTION (Continued)

Figure 4. 44-Pin PLCC

Table 2. 44-Pin PLCC Pin Identification

| No | Symbol          | Function            | Direction | No    | Symbol  | Function             | Direction |

|----|-----------------|---------------------|-----------|-------|---------|----------------------|-----------|

| 1  | V <sub>cc</sub> | Power Supply        | Input     | 14-16 | P00-P02 | Port 0 pin 0,1,2     | In/Output |

| 2  | XTĂĽ2           | Crystal, Osc. Clock | Output    | 17    | IACK    | Int. Acknowledge     | Output    |

| 3  | XTAL1           | Crystal, Osc. Clock | Input     | 18-22 | P03-P07 | Port 0 pin 3,4,5,6,7 | In/Output |

| 4  | P37             | Port 3 pin 7        | Output    | 23-27 | P10-P14 | Port 1 pin 0,1,2,3,4 | In/Output |

| 5  | P30             | Port 3 pin 0        | Input     | 28    | /SYNC   | Synchronize Pin      | Output    |

| 6  | SCLK            | System Clock        | Output    | 29-31 | P15-P17 | Port 1 pin 5,6,7     | In/Output |

| 7  | /RESET          | Reset               | Input     | 32    | P34     | Port 3 pin 4         | Output    |

| 8  | R//W            | Read/Write          | Output    | 33    | P33     | Port 3 pin 3         | Input     |

| 9  | /DS             | Data Strobe         | Output    | 34-38 | P20-P24 | Port 2 pin 0,1,2,3,4 | In/Output |

| 10 | /AS             | Address Strobe      | Output    | 39    | N/C     | Not Connected (20 MH |           |

| 11 | P35             | Port 3 pin 5        | Output    |       | M/AIT   | WAIT (25 or 33 MHz)  | Input     |

| 12 | GND             | Ground GND          | Input     | 40-42 | P25-P27 | Port 2 pin 5,6,7     | In/Output |

| 13 | P32             | Port 3 pin 2        | Input     | 43    | P31     | Port 3 pin 1         | Input     |

|    |                 | <del></del>         |           | 44    | P36     | Port 3 pin 6         | Output    |

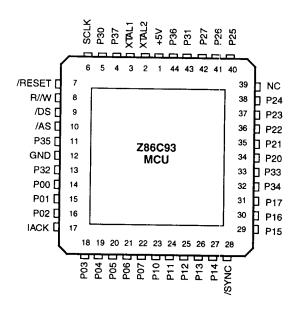

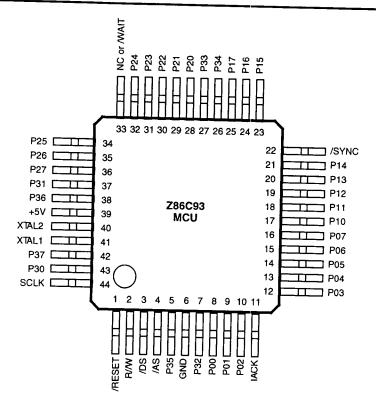

Figure 5. 44-Pin QFP

Table 3. 44-Pin QFP Pin Identification

| No    | Symbol  | Function             | Direction |

|-------|---------|----------------------|-----------|

| 1     | /RESET  | Reset                | Input     |

| 2     | R//W    | Read/Write           | Output    |

| 3     | /DS     | Data Strobe          | Output    |

| 4     | /AS     | Address Strobe       | Output    |

| 5     | P35     | Port 3 pin 5         | Input     |

| 6     | GND     | Ground GND           | Input     |

| 7     | P32     | Port 3 pin 2         | Input     |

| 8-10  | P00-P02 | Port 0 pin 0,1,2     | In/Output |

| 11    | IACK    | Int. Acknowledge     | Output    |

| 12-16 | P03-P07 | Port 0 pin 3,4,5,6,7 | In/Output |

| 17-21 | P10-P14 | Port 1 pin 0,1,2,3,4 | In/Output |

| 22    | /SYNC   | Synchronize Pin      | Output    |

| 23-25 | P15-P17 | Port 1 pin 5,6,7     | In/Output |

| No                      | Symbol                                | Function                                                                                             | Direction                                      |

|-------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 26<br>27<br>28-32<br>33 | P34<br>P33<br>P20-P24<br>N/C<br>/WAIT | Port 3 pin 4<br>Port 3 pin 3<br>Port 2 pin 0,1,2,3,4<br>Not Connected (20 MHz<br>WAIT (25 or 33 MHz) | Output<br>Input<br>In/Output<br>Input<br>Input |

| 34-36                   | P25-P27                               | Port 2 pin 5,6,7                                                                                     | In/Output                                      |

| 37                      | P31                                   | Port 3 pin 1                                                                                         | Input                                          |

| 38                      | P36                                   | Port 3 pin 6                                                                                         | Output                                         |

| 39                      | V <sub>30</sub>                       | Power Supply                                                                                         | Input                                          |

| 40                      | XTAL2                                 | Crystal, Osc. Clock                                                                                  | Output                                         |

| 41                      | XTAL1                                 | Crystal, Osc. Clock                                                                                  | Input                                          |

| 42                      | P37                                   | Port 3 pin 7                                                                                         | Output                                         |

| 43                      | P30                                   | Port 3 pin 0                                                                                         | Input                                          |

| 44                      | SCLK                                  | System Clock                                                                                         | Output                                         |

### **PIN FUNCTIONS**

/DS. (output, active Low). Data Strobe is activated once for each external memory transfer. For a READ operation, data must be available prior to the trailing edge of /DS. For WRITE operations, the falling edge of /DS indicates that output data is valid.

/AS. (output, active Low). Address Strobe is pulsed once at the beginning of each machine cycle. Address output is via Port 1 for all external programs. When /RESET is asserted, /AS toggles. Memory address transfers are valid at the trailing edge of /AS.

XTAL1, XTAL2. Crystal 1, Crystal 2(time-based input and output, respectively). These pins connect a parallel-resonant crystal, ceramic resonator, LC, or any external single-phase clock to the on-chip oscillator and buffer.

R/W. (output, read High/write Low). The Read/Write signal is Low when the MCU is writing to the external program or data memory. It is High when the MCU is reading from the external program or data memory.

/RESET. (input, active Low). To avoid asynchronous and noisy reset problems, the Z86C93 is equipped with a reset filter of four external clocks (4TpC). If the external /RESET signal is less than 4TpC in duration, no reset occurs.

On the 5th clock after the /RESET is detected, an internal RST signal is latched and held for an internal register count of 18 external clocks, or for the duration of the external /RESET, whichever is longer. During the reset cycle, /DS is held active Low while /AS cycles at a rate of 2TpC. When /RESET is deactivated, program execution begins at location 000CH. Reset time must be held Low for 50 ms or until  $\rm V_{cc}$  is stable, whichever is longer.

SCLK. System Clock (output). The internal system clock is available at this pin. Available in the PLCC, QFP and VQFP packages only.

IACK. Interrupt Acknowledge (output, active High). This output, when High, indicates that the Z86C93 is in an interrupt cycle. Available in the PLCC, QFP and VQFP packages only.

/SYNC. (output, active Low). This signal indicates the last clock cycle of the currently executing instruction. Available in the PLCC, QFP and VQFP packages only.

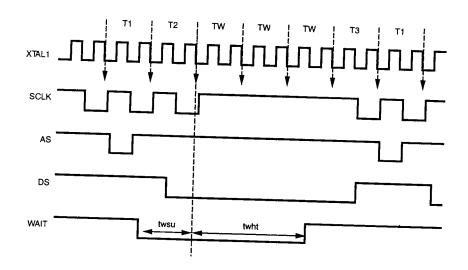

WAIT. (input, active Low). Introduces asynchronous wait states into the external memory fetch cycle. When this inut goes Low during an external memory access, the Z86C93 freezes the fetch cycle until tis pin goes High. This pin is sampled after /DS goes Low; should be pulled up if not used. Available in the 25 MHz and 33 MHz devices only.

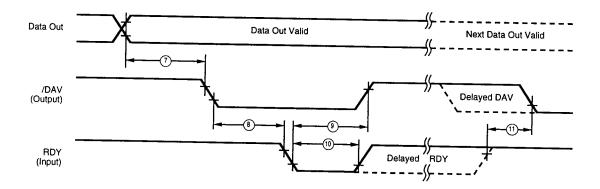

Port 0 P00-P07. Port 0 is an 8-bit, nibble programmable, bidirectional, TTL compatible port. These eight I/O lines can be configured under software control as a nibble I/O port, or as an address port for interfacing external memory. When used as an I/O port, Port 0 may be placed under handshake control. In this configuration, Port 3, lines P32 and P35 are used as the handshake control /DAV0 and RDY0 (Data Available and Ready). Handshake signal assignment is dictated by the I/O direction of the upper nibble P04-P07. The lower nibble must have the same direction as the upper nibble to be under handshake control. Port 0 comes up as A15-A8 Address lines after /RESET.

For external memory references, Port 0 can provide address bits A11-A8 (lower nibble) or A15-A8 (lower and upper nibble) depending on the required address space. If the address range requires 12 bits or less, the upper nibble of Port 0 can be programmed independently as I/O while the lower nibble is used for addressing. If one or both nibbles are needed for I/O operation, they must be configured by writing to the Port 0 Mode register. After a hardware reset, Port 0 lines are defined as address lines A15-A8, and extended timing is set to accommodate slow memory access. The initialization routine can include reconfiguration to eliminate this extended timing mode (Figure 7). The /OEN (Output Enable) signal in Figure 7 is an internal signal.

The Auto Latch on Port 0 puts valid CMOS levels on all CMOS inputs which are not externally driven. Whether this level is 0 or 1, cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

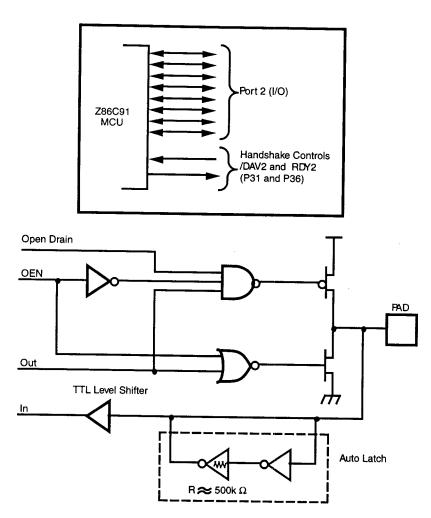

Port 2. (P20-P27). Port 2 is an 8-bit, bit programmable, bidirectional, TTL compatible port. Each of these eight I/O lines can be independently programmed as an input or output or globally as an open-drain output. Port 2 is always available for I/O operation. When used as an I/O port, Port 2 is placed under handshake control. In this configuration, Port 3 lines P31 and P36 are used as the handshake control lines /DAV2 and RDY2. The handshake signal

assignment for Port 3 lines P31 and P36 is dictated by the direction (input or output) assigned to P27 (Figure 9).

The Auto Latch on Port 2 puts valid CMOS levels on all CMOS inputs which are not externally driven. Whether this level is 0 or 1, cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

Figure 9. Port 2 Configuration

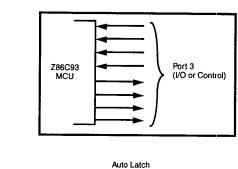

Port 3 P30-P37. Port 3 is an 8-bit, TTL compatible four fixed input and four fixed output ports. These eight I/O lines have four fixed (P30-P33) input and four fixed (P34-P37) output

ports. Port 3 pins P30 and P37 when used as serial I/O, are programmed as serial in and serial out, respectively (Figure 10 and Table 5).

Figure 10. Port 3 Configuration

Table 5. Port 3 Pin Assignments

| Pin# | 1/0 | CTC1            | Int. | P0HS | P2HS   | UART       | Ext. |

|------|-----|-----------------|------|------|--------|------------|------|

| P30  | ln  |                 | IRQ3 |      |        | Serial In  |      |

| P31  | In  | T <sub>IN</sub> | IRQ2 |      | D/R    |            |      |

| P32  | ln  |                 | IRQ0 | D/R  |        |            |      |

| P33  | In  |                 | IRQ1 |      |        |            |      |

| P34  | Out |                 |      |      |        |            | DM   |

| P35  | Out |                 |      | R/D  |        |            |      |

| P36  | Out | Tout            |      | , –  | R/D    |            |      |

| P37  | Out | 001             |      |      | . ,, & | Serial Out |      |

Port 3 is configured under software control to provide the following control functions: handshake for Ports 0 and 2 (/DAV and RDY); four external interrupt request signals (IRQ0-IRQ3); timer input and output signals ( $T_{\text{IN}}$  and  $T_{\text{OUT}}$ ), and Data Memory Select (/DM).

Port 3 lines P30 and P37 can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by the Counter/Timer 0.

The Z86C93 automatically adds a start bit and two stop bits to transmitted data (Figure 10). Odd parity is also available as an option. Eight data bits are always transmitted,

regardless of parity selection. If parity is enabled, the eighth bit is the odd parity bit. An interrupt request (IRQ4) is generated on all transmitted characters.

Received data must have a start bit, eight data bits and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ3 interrupt request.

The Auto Latch on Port 3 puts a valid CMOS level on all CMOS inputs that are not externally driven. Whether this level is zero or one, cannot be determined. A valid CMOS level rather than a floating node reduces excessive supply current flow in the input buffer.

Figure 14. Register Pointer Register

Figure 15. Register Pointer

### **FUNCTIONAL DESCRIPTION**

This section breaks down the Z86C93 into its main functional parts.

### Multiply/Divide Unit

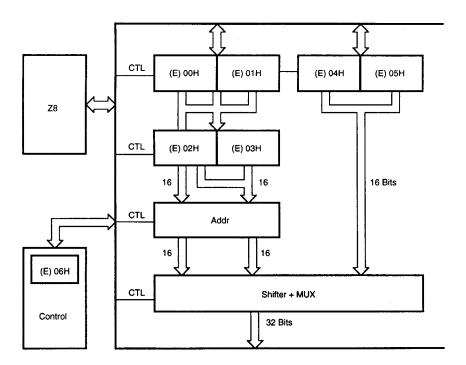

The Multiply/Divide unit describes the basic features, implementation details of the interface between the Z8 and the multiply/divide unit.

### Basic features:

- 16-bit by 16-bit multiply with 32-bit product

- 32-bit by 16-bit divide with 16-bit quotient and 16-bit remainder

- Unsigned integer data format

- Simple interface to Z8

Interface to Z8. The following is a brief description of the register mapping in the multiply/divide unit and its interface to the Z8 (Figure 16).

The multiply/divide unit is interfaced like a peripheral. The only addressing mode available with the peripheral interface is register addressing. In other words, all of the operands are in the respective registers before a multiplication/division can start.

Register mapping. The registers used in the multiply/divide unit are mapped onto the expanded register file in Bank E. The exact register locations used are shown below.

| REGISTER | ADDRESS |

|----------|---------|

| MREG0    | (E) 00  |

| MREG1    | (E) 01  |

| MREG2    | (E) 02  |

| MREG3    | (E) 03  |

| MREG4    | (E) 04  |

| MREG5    | (E) 05  |

| MDCON    | (E) 06  |

| GPR      | (E) 14  |

| GPR      | (E) 15  |

Figure 16. Multiply/Divide Unit Block Diagram

### Interrupts

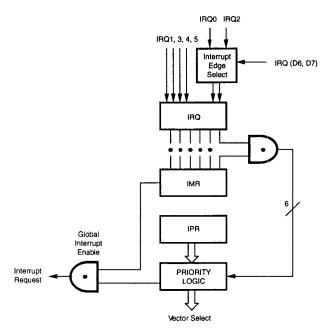

The Z86C93 has six different interrupts from nine different sources. The interrupts are maskable and prioritized. The nine sources are divided as follow: four sources are claimed by Port 3 lines P30-P33, one in Serial Out, one in Serial In, and three in the counter/timers. The Interrupt Mask Register globally or individually enables or disables the six interrupt requests. When more than one interrupt is pending, priorities are resolved by a programmable priority encoder that is controlled by the Interrupt Priority register. All Z86C93 interrupts are vectored through locations in the program memory. When an interrupt machine cycle is activated an interrupt request is granted. Thus, this disables all of the subsequent interrupts, save the Program Counter and Status Flags, and then branches to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular interrupt request.

To accommodate polled interrupt systems, interrupt inputs are masked and the Interrupt Request register is polled to determine which of the interrupt requests need service. Software initiated interrupts are supported by setting the appropriate bit in the Interrupt Request Register (IRQ).

Internal interrupt requests are sampled on the falling edge of the last cycle of every instruction. The interrupt request must be valid 5TpC before the falling edge of the last clock cycle of the currently executing instruction:

When the device samples a valid interrupt request, the next 48 (external) clock cycles are used to prioritize the interrupt, and push the two PC bytes and the FLAG register on the stack. The following nine cycles are used to fetch the interrupt vector from external memory. The first byte of the interrupt service routine is fetched beginning on the 58th TpC cycle following the internal sample point, which corresponds to the 63th TpC cycle following the external interrupt sample point.

Figure 21. Interrupt Block Diagram

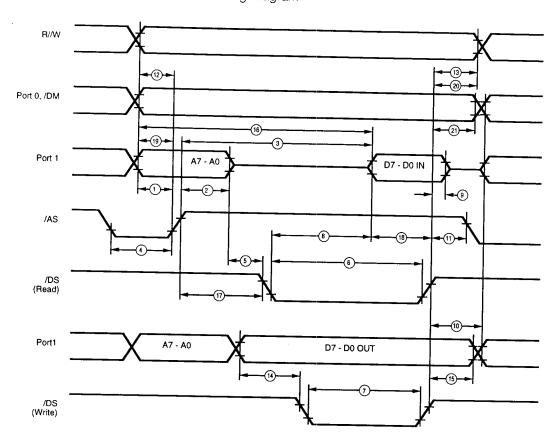

**AC CHARACTERISTICS**External I/O or Memory Read/Write Timing Diagram

Figure 24. External I/O or Memory Read/Write Timing

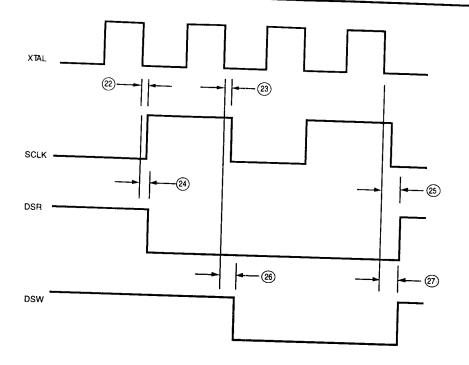

Figure 25. XTAL/SCLK To DSR and DSW Timing

Figure 26. XTAL/SCLK To WAIT Timing (25 MHz Device Only)

**AC CHARACTERISTICS** Handshake Timing Diagrams

Figure 28. Input Handshake Timing

Figure 29. Output Handshake Timing

## Z8 CONTROL REGISTERS (Continued)

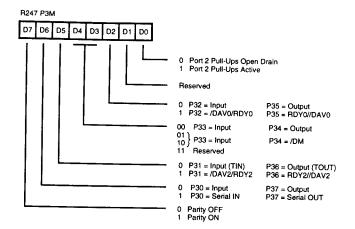

Figure 44. Port 3 Mode Register (F7H: Write Only)

Figure 45. Ports 0 and 1 Mode Registers (F8H: Write Only)

Figure 46. Interrupt Priority Register (F9H: Write Only)

| INSTRUC <sup>*</sup> | TION SI | IMMARY | (Continue) | ed) |

|----------------------|---------|--------|------------|-----|

|                      |         |        |            |     |

| Instruction and Operation                                                | Address<br>Mode | Opcode<br>Byte (Hex) |   | ags<br>fect |   |   |   |   |

|--------------------------------------------------------------------------|-----------------|----------------------|---|-------------|---|---|---|---|

|                                                                          | dst src         | _,,                  | С | Z           | s | ٧ | D | Н |

| ADC dst, src<br>dst←dst + src +C                                         | †               | 1[]                  | * | *           | * | * | 0 | * |

| ADD dst, src<br>dst←dst + src                                            | †               | 0[]                  | * | *           | * | * | 0 | * |

| AND dst, src<br>dst←dst AND src                                          | t               | 5[]                  | - | *           | * | 0 | - | - |

| CALL dst<br>SP←SP - 2<br>@SP←PC,<br>PC←dst                               | DA<br>IRR       | D6<br>D4             | - | -           |   | - | - | - |

| CCF<br>C←NOT C                                                           |                 | EF                   | * | •           | • | - | - | - |

| CLR dst<br>dst←0                                                         | R<br>IR         | B0<br>B1             | - | -           | - | - | • | - |

| COM dst<br>dst←NOT dst                                                   | R<br>IR         | 60<br>61             | - | *           | * | 0 | - | • |

| CP dst, src<br>dst - src                                                 | t               | A[ ]                 | * | *           | * | * | - | - |

| <b>DA</b> dst<br>dst←DA dst                                              | R<br>IR         | 40<br>41             | * | *           | * | X | - | - |

| DEC dst<br>dst←dst - 1                                                   | R<br>IR         | 00<br>01             | - | *           | * | * | • | • |

| DECW dst<br>dst←dst - 1                                                  | RR<br>IR        | 80<br>81             | - | *           | * | * | - | - |

| <b>DI</b><br>IMR(7)←0                                                    |                 | 8F                   | - | -           | - | - | - | - |

| DJNZr, dst<br>r←r - 1<br>if r ≠ 0<br>PC←PC + dst<br>Range: +127,<br>-128 | RA              | rA<br>r = 0 - F      | - | -           | • | - | - | - |

| <b>EI</b><br>1MR(7)←1                                                    |                 | 9F                   | - | -           | - | • | - | - |

| HALT                                                                     |                 | 7F                   | - | -           | - | - | - | - |

| Instruction and Operation | Address<br>Mode<br>dst src |     | Opcode<br>Byte (Hex) |   | ags<br>fec<br>Z | v        | D | н |   |

|---------------------------|----------------------------|-----|----------------------|---|-----------------|----------|---|---|---|

|                           | ası                        | SIC |                      | _ | _               | <u>s</u> | _ | _ | n |

| INC dst                   | r                          |     | rE                   | - | *               | *        | * | - | - |

| dst←dst + 1               |                            |     | r = 0 - F            |   |                 |          |   |   |   |

|                           | R                          |     | 20                   |   |                 |          |   |   |   |

|                           | IR                         |     | 21                   |   |                 |          |   |   |   |

| INCW dst                  | RR                         |     | A0                   | _ | *               | *        | * | - | - |

| dst←dst + 1               | IR                         |     | A1                   |   |                 |          |   |   |   |

| IRET                      |                            |     | BF                   | * | *               | *        | * | * | * |

| FLAGS←@SP;                |                            |     |                      |   |                 |          |   |   |   |

| SP←SP + 1                 |                            |     |                      |   |                 |          |   |   |   |

| PC←@SP;                   |                            |     |                      |   |                 |          |   |   |   |

| SP←-SP + 2;               |                            |     |                      |   |                 |          |   |   |   |

| IMR(7)←1                  |                            |     |                      |   |                 |          |   |   |   |

| JP cc, dst                | DA                         |     | cD                   |   | -               | -        | - | - | - |

| if cc is true             |                            |     | c = 0 - F            |   |                 |          |   |   |   |

| PC←dst                    | IRR                        |     | 30                   |   |                 |          |   |   |   |

| JR cc, dst                | RA                         |     | сВ                   | - | -               | _        |   | _ |   |

| if cc is true,            |                            |     | c = 0 - F            |   |                 |          |   |   |   |

| PC←PC + dst               |                            |     |                      |   |                 |          |   |   |   |

| Range: +127,              |                            |     |                      |   |                 |          |   |   |   |

| -128                      |                            |     |                      |   |                 |          |   |   |   |

| LD dst, src               | r                          | lm  | rC                   | - | -               | -        | _ | _ | - |

| dst←src                   | r                          | R   | r8                   |   |                 |          |   |   |   |

|                           | R                          | r   | r9                   |   |                 |          |   |   |   |

|                           |                            |     | r = 0 - F            |   |                 |          |   |   |   |

|                           | r                          | Χ   | C7                   |   |                 |          |   |   |   |

|                           | X                          | r   | D7                   |   |                 |          |   |   |   |

|                           | r                          | lr  | E3                   |   |                 |          |   |   |   |

|                           | lr                         | r   | F3                   |   |                 |          |   |   |   |

|                           | R                          | R   | E4                   |   |                 |          |   |   |   |

|                           | R                          | IR  | E5                   |   |                 |          |   |   |   |

|                           | R                          | IM  | E6                   |   |                 |          |   |   |   |

|                           | IR                         | IM  | E7                   |   |                 |          |   |   |   |

|                           | IR                         | R   | F5                   |   |                 |          |   |   |   |

| LDC dst, src              | r                          | lrr | C2                   | - | -               | -        | • | - | - |

| LDCI dst, src             | lr                         | Irr | СЗ                   | - | -               | -        | - | - | - |

| dst←src                   |                            |     |                      |   |                 |          |   |   |   |

| r←r +1;                   |                            |     |                      |   |                 |          |   |   |   |

| rr←rr + 1                 |                            |     |                      |   |                 |          |   |   |   |

|                           |                            |     |                      |   |                 |          |   |   |   |

|                           |                            |     |                      |   |                 |          |   |   |   |

## INSTRUCTION SUMMARY (Continued)

| Instruction and Operation         | M       | ddress<br>ode<br>st src |          | ode<br>(Hex) | F | Flag<br>Affe | cte |     |     | D | Н              |

|-----------------------------------|---------|-------------------------|----------|--------------|---|--------------|-----|-----|-----|---|----------------|

| NOP                               |         |                         | FF       |              | - | -            | -   | -   |     | • | -              |

| OR dst, src<br>dst←dst OR src     | †       | · · · · · ·             | 4[ ]     |              | - | *            |     | : ( | ) . |   | _              |

| POP dst<br>dst←@SP;<br>SP←SP + 1  | R       |                         | 50<br>51 | <u> </u>     | - | -            | -   | -   |     |   | -              |

| PUSH src<br>SP←SP - 1;<br>@SP←src |         | R<br>IR                 | 70<br>71 | <u> </u>     | - | -            | -   | -   | -   |   | _              |

| RCF<br>C←0                        |         |                         | CF       | ·            | 0 | -            | -   | -   | -   |   | -              |

| <b>RET</b> PC←@SP; SP←SP + 2      |         | .,                      | AF       | <u>.</u>     | - | -            | -   | -   | -   |   | _              |

| RL dst                            | R<br>IR |                         | 90<br>91 |              | * | *            | *   | *   | -   | • | -              |

| RLC dst                           | R<br>IR |                         | 10<br>11 |              | * | *            | *   | *   | -   | - | <del>-</del> - |

| RR dst                            | R<br>IR |                         | E0<br>E1 | :            | * | *            | *   | *   | -   | - | _              |

| RRC dst                           | R<br>IR |                         | C0<br>C1 | :            | * | *            | *   | *   | -   | - | -              |

| SBC dst, src<br>dst←dst←src←C     | †       |                         | 3[]      |              | k | *            | *   | *   | 1   | k | <              |

| SCF<br>C←1                        |         |                         | DF       | 1            | l | -            | -   | •   | -   | - | _              |

| SRA dst                           | R<br>IR |                         | D0<br>D1 | k            | k | *            | *   | 0   | -   | - | _              |

| SRP src<br>RP←src                 |         | lm .                    | 31       | -            |   | -            | -   | -   | •   | - | -              |

| Instruction<br>and Operation         | Address<br>Mode | Opcode<br>Byte (Hex) |   | ag: |   | _ |   |   |

|--------------------------------------|-----------------|----------------------|---|-----|---|---|---|---|

|                                      | dst src         |                      | С | Z   | S | ٧ | D | Н |

| STOP                                 |                 | 6F                   | - | -   |   | - | - | - |

| SUB dst, src<br>dst←dst←src          | †               | 2[ ]                 | * | *   | * | * | 1 | * |

| <b>SWAP</b> dst                      | R<br>IR         | F0<br>F1             | X | *   | * | X | - | - |

| TCM dst, src<br>(NOT dst)<br>AND src | †               | 6[]                  | - | *   | * | 0 | - | - |

| TM dst, src<br>dst AND src           | †               | 7[]                  | - | *   | * | 0 | - | - |

| XOR dst, src<br>dst←dst<br>XOR src   | t               | B[ ]                 | - | *   | * | 0 | - | • |

† These instructions have an identical set of addressing modes, which are encoded for brevity. The first opcode nibble is found in the instruction set table above. The second nibble is expressed symbolically by a '[ ]' in this table, and its value is found in the following table to the left of the applicable addressing mode pair.

For example, the opcode of an ADC instruction using the addressing modes  ${\bf r}$  (destination) and  ${\bf lr}$  (source) is 13.

| Address Mode<br>dst src |    | Lower<br>Opcode Nibble |  |  |

|-------------------------|----|------------------------|--|--|

| r                       | r  | [2]                    |  |  |

| r                       | Ir | [3]                    |  |  |

| R                       | R  | [4]                    |  |  |

| R                       | IR | [5]                    |  |  |

| R                       | IM | [6]                    |  |  |

| IR                      | IM | [7]                    |  |  |

|                         |    |                        |  |  |

### PACKAGE INFORMATION

| ZAMBOT | HILLINETER |       | INCH    |       |

|--------|------------|-------|---------|-------|

|        | MEN        | MAX   | MIN     | MAX   |

| Al     | 0.51       | 0.81  | 050     | .032  |

| 42     | 3.25       | 3.43  | 128     | 135   |

| В      | 0.38       | 0.53  | .015    | 150   |

| Bi     | 1.02       | 1.52  | .040    | .060  |

| C      | 0.63       | 0.38  | .009    | 015   |

| D      | 52.07      | 52.58 | 2.050   | 2.070 |

| ε      | 15.24      | 15.75 | .600    | .620  |

| £1     | 13.59      | 14.22 | .535    | .560  |

|        | 2.54 TYP   |       | 100 TYP |       |

| eA.    | 15.49      | 16.51 | .610    | .650  |

| L      | 3.18       | 3.81  | 125     | 150   |

| . D1   | 1.52       | 1.91  | .060    | .075  |

| 2      | 1.52       | 2 2 9 | .060    | 090   |

CONTROLLING DIMENSIONS : INCH

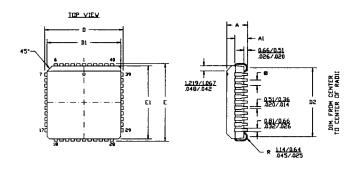

### 40-Pin DIP Package Diagram

| JOBMYZ | HILLIMETER |       | INCH |      |

|--------|------------|-------|------|------|

|        | MIN        | MAX   | MIN  | MAX  |

| A      | 4.27       | 4.57  | .168 | .180 |

| Al     | 2.67       | 2.92  | .105 | .115 |

| B/E    | 17.40      | 17.65 | .685 | .695 |

| DI/EI  | 16.51      | 16.66 | .650 | .656 |

| D2     | 15.24      | 16.00 | .600 | .630 |

| 8      | . 1.27     | TYP   | .050 | TYP  |

44-Pin PLCC Package Diagram

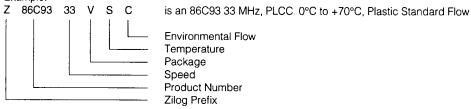

### ORDERING INFORMATION

### Z86C93

20 MHz

44-pin PLCC

44-pin QFP

40-pin DIP

48-pin VQFP

Z86C9320VSC

Z86C9320FSC

Z86C9320PSC

Z80C9320ASC

25 MHz

44-pin PLCC

44-pin QFP

40-pin DIP

48-pin VQFP

Z86C9325VSC

Z86C9325FSC

Z86C9325PSC

Z80C9325ASC

33 MHz

44-pin PLCC

44-pin QFP

40-pin DIP

48-pin VQFP

Z86C9333VSC

Z86C9333FSC

Z86C9333PSC

Z80C9333ASC

For fast results, contact your local Zilog sales office for assistance in ordering the part desired.

### Package

V = Plastic Leaded Chip Carrier P = Plastic Dual In Line Package

### Longer Lead Time

F = Plastic Quad Flat Pack A = Very Small Quad Flat Pack

### Temperature

$S = 0^{\circ}C$  to  $+70^{\circ}C$

### Speed

20 = 20 MHz

25 = 25 MHz

33 = 33 MHz

### Environmental

C = Standard Flow

Example:

| Notes: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |