Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 100MHz                                                                 |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (1)                                                             |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | 0°C ~ 95°C (TA)                                                        |

| Security Features               | -                                                                      |

| Package / Case                  | 256-BBGA                                                               |

| Supplier Device Package         | 256-PBGA (23x23)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc852tvr100a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Power Dissipation**

# 5 Power Dissipation

Table 4 provides power dissipation information. The modes are 1:1, where CPU and bus speeds are equal, and 2:1 mode, where CPU frequency is twice bus speed.

Table 4. Power Dissipation (P<sub>D</sub>)

| Die Revision | Bus Mode | Frequency<br>(MHz) | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|--------------|----------|--------------------|----------------------|----------------------|------|

|              |          |                    |                      |                      |      |

|              |          | 50                 | 110                  | 140                  | mW   |

|              | 1:1      | 66                 | 150                  | 180                  | mW   |

| 0            |          | 66                 | 140                  | 160                  | mW   |

|              | 2:1      | 80                 | 170                  | 200                  | mW   |

|              |          | 100                | 210                  | 250                  | mW   |

<sup>&</sup>lt;sup>1</sup> Typical power dissipation is measured at 1.9 V.

#### NOTE

Values in Table 4 represent  $V_{DDL}$ -based power dissipation, and do not include I/O power dissipation over  $V_{DDH}$ . I/O power dissipation varies widely by application that buffer current can cause, depending on external circuitry.

The V<sub>DDSYN</sub> power dissipation is negligible.

## 6 DC Characteristics

Table 5 provides the DC electrical characteristics for the MPC852T.

**Table 5. DC Electrical Specifications**

| Characteristic                                                                                                                                                                      | Symbol                                                    | Min                  | Max              | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------|------------------|------|

| Operating voltage                                                                                                                                                                   | V <sub>DDH</sub>                                          | 3.135                | 3.465            | V    |

|                                                                                                                                                                                     | V <sub>DDL</sub>                                          | 1.7                  | 1.9              | V    |

|                                                                                                                                                                                     | $V_{DDSYN}$                                               | 1.7                  | 1.9              | V    |

|                                                                                                                                                                                     | Difference between V <sub>DDL</sub> to V <sub>DDSYN</sub> | _                    | 100              | mV   |

| Input high voltage (all inputs except PA[0:3], PA[8:11], PB15, PB[24:25]; PB[28:31], PC[4:7], PC[12:13], PC15, PD[3:15], TDI, TDO, TCK, TRST, TMS, MII_TXEN, MII_MDIO) <sup>1</sup> | V <sub>IH</sub>                                           | 2.0                  | 3.465            | V    |

| Input low voltage                                                                                                                                                                   | V <sub>IL</sub>                                           | GND                  | 0.8              | V    |

| EXTAL, EXTCLK input high voltage                                                                                                                                                    | V <sub>IHC</sub>                                          | $0.7 \times V_{DDH}$ | V <sub>DDH</sub> | V    |

$<sup>^2</sup>$  Maximum power dissipation at  $\rm V_{DDL}$  and  $\rm V_{DDSYN}$  is at 1.9 V. and  $\rm V_{DDH}$  is at 3.465 V.

If the board temperature is known and the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made. For this method to work, the board and board mounting must be similar to the test board used to determine the junction-to-board thermal resistance, namely a 2s2p (board with a power and a ground plane) and vias attaching the thermal balls to the ground plane.

### 7.4 Estimation Using Simulation

When the board temperature is not known, a thermal simulation of the application is needed. The simple two-resistor model can be used with the thermal simulation of the application [2], or a more accurate and complex model of the package can be used in the thermal simulation.

### 7.5 Experimental Determination

To determine the junction temperature of the device in the application after prototypes are available, the thermal characterization parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_I = T_T + (\Psi_{IT} \times P_D)$$

where:

$\Psi_{JT}$  = thermal characterization parameter

$T_T$  = thermocouple temperature on top of package

$P_D$  = power dissipation in package

The thermal characterization parameter is measured per JESD51-2 specification published by JEDEC using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors that cooling effects of the thermocouple wire cause.

# 8 References

Semiconductor Equipment and Materials International (415) 964-5111

805 East Middlefield Rd

Mountain View, CA 94043

MIL-SPEC and EIA/JESD (JEDEC) specifications 800-854-7179 or (Available from Global Engineering documents) 303-397-7956

JEDEC Specifications http://www.jedec.org

- 1. C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 9 Power Supply and Power Sequencing

This section provides design considerations for the MPC852T power supply. The MPC852T has a core voltage ( $V_{DDL}$ ) and PLL voltage ( $V_{DDSYN}$ ) that operates at a lower voltage than the I/O voltage  $V_{DDH}$ . The I/O section of the MPC852T is supplied with 3.3 V across  $V_{DDH}$  and  $V_{SS}$  (GND).

The signals PA[0:3], PA[8:11], PB15, PB[24:25]; PB[28:31], PC[4:7], PC[12:13], PC15] PD[3:15], TDI, TDO, TCK, TRST, TMS, MII\_TXEN, MII\_MDIO are 5-V tolerant. All inputs cannot be more than 2.5 V greater than V<sub>DDH</sub>. In addition, 5-V tolerant pins can not exceed 5.5 V, and the remaining input pins cannot exceed 3.465 V. This restriction applies to power-on reset or power down and normal operation.

One consequence of multiple power supplies is that when power is initially applied, the voltage rails ramp up at different rates. The rates depend on the nature of the power supply, the type of load on each power supply, and the manner in which different voltages are derived. The following restrictions apply:

- ullet  $V_{DDL}$  must not exceed  $V_{DDH}$  during power-on reset or power down.

- V<sub>DDL</sub> must not exceed 1.9 V, and V<sub>DDH</sub> must not exceed 3.465.

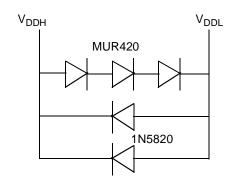

These cautions are necessary for the long-term reliability of the part. If they are violated, the electrostatic discharge (ESD) protection diodes are forward-biased, and excessive current can flow through these diodes. If the system power supply design does not control the voltage sequencing, the circuit shown in Figure 3 can be added to meet these requirements. The MUR420 Schottky diodes control the maximum potential difference between the external bus and core power supplies on power-on reset, and the 1N5820 diodes regulate the maximum potential difference on power-down.

Figure 3. Example Voltage Sequencing Circuit

# 10 Mandatory Reset Configurations

The MPC852T requires a mandatory configuration during reset.

If hardware reset configuration word (HRCW) is enabled, by asserting the  $\overline{RSTCONF}$  during  $\overline{HRESET}$  assertion, the HRCW[DBGC] value that is needed to be set to binary X1 in the hardware reset configuration word (HRCW) and the SIUMCR[DBGC] should be programmed with the same value in the boot code after reset.

If hardware reset configuration word (HRCW) is disabled, by negating the  $\overline{RSTCONF}$  during the  $\overline{HRESET}$  assertion, the SIUMCR[DBGC] should be programmed with binary X1 in the boot code after reset.

The MBMR[GPLB4DIS], PAPAR, PADIR, PBPAR, PBDIR, PCPAR, and PCDIR should be configured with the mandatory value in Table 6 in the boot code after the reset deasserts.

| Register/Configuration                     | Field                                     | Value<br>(Binary) |

|--------------------------------------------|-------------------------------------------|-------------------|

| HRCW (Hardware reset configuration word)   | HRCW[DBGC]                                | X1                |

| SIUMCR (SIU module configuration register) | SIUMCR[DBGC]                              | X1                |

| MBMR (Machine B mode register)             | MBMR[GPLB4DIS}                            | 0                 |

| PAPAR (Port A pin assignment register)     | PAPAR[4-7]<br>PAPAR[12-15]                | 0                 |

| PADIR (Port A data direction register)     | PADIR[4–7]<br>PADIR[12–15]                | 1                 |

| PBPAR (Port B pin assignment register)     | PBPAR[14]<br>PBPAR[16–23]<br>PBPAR[26–27] | 0                 |

| PBDIR (Port B data direction register)     | PBDIR[14]<br>PBDIR[16–23]<br>PBDIR[26–27] | 1                 |

| PCPAR (Port C pin assignment register)     | PCPAR[8-11]<br>PCDIR[14]                  | 0                 |

| PCDIR (Port C data direction register)     | PCDIR[8-11]<br>PCDIR[14]                  | 1                 |

Table 6. Mandatory Reset Configuration of MPC852T

# 11 Layout Practices

Each  $V_{DD}$  pin on the MPC852T should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1  $\mu$ F bypass capacitors located as close as possible to the four sides of the package. Each board designed should be characterized and additional appropriate decoupling capacitors should be used if required. The capacitor leads and associated printed-circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than half an inch per capacitor lead. At a minimum, a four-layer board employing two inner layers as  $V_{DD}$  and GND planes should be used.

All output pins on the MPC852T have fast rise and fall times. Printed-circuit (PC) trace interconnection length should be minimized to minimize undershoot and reflections that these fast output switching times cause. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances that the PC traces cause. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads, because these loads create higher transient currents in the V<sub>DD</sub> and GND circuits. Pull up all unused inputs or signals that are inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins. For more information, please refer to the *MPC866 PowerQUICC*<sup>TM</sup> *Family Reference Manual*, Section 14.4.3, "Clock Synthesizer Power (V<sub>DDSYN</sub>, V<sub>SSSYN</sub>, V<sub>SSSYN</sub>)."

### **Table 9. Bus Operation Timings (continued)**

| <b>N</b> I | Characteristic                                                                                                                                                           | 33   | MHz   | 40 I | ИНz   | 50 MHz |       | 66 MHz |       | Unit |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|--------|-------|--------|-------|------|--|

| Num        | Gilaracteristic                                                                                                                                                          |      | Max   | Min  | Max   | Min    | Max   | Min    | Max   | Unit |  |

| В3         | CLKOUT pulse width high (MIN = $0.4 \times B1$ , MAX = $0.6 \times B1$ )                                                                                                 | 12.1 | 18.2  | 10.0 | 15.0  | 8.0    | 12.0  | 6.1    | 9.1   | ns   |  |

| B4         | CLKOUT rise time                                                                                                                                                         | _    | 4.00  | _    | 4.00  | _      | 4.00  | _      | 4.00  | ns   |  |

| B5         | CLKOUT fall time                                                                                                                                                         | _    | 4.00  | _    | 4.00  | _      | 4.00  | _      | 4.00  | ns   |  |

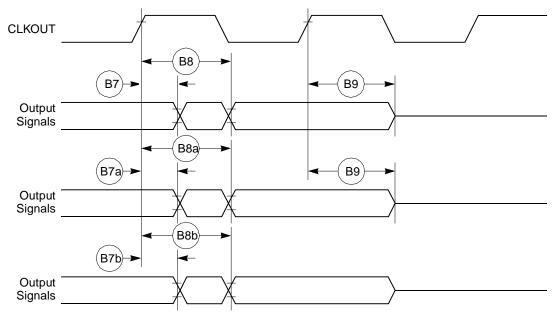

| В7         | CLKOUT to A(0:31), BADDR(28:30), RD/WR, BURST, D(0:31), DP(0:3) output hold (MIN = $0.25 \times B1$ )                                                                    | 7.60 | _     | 6.30 | _     | 5.00   | _     | 3.80   | _     | ns   |  |

| В7а        | CLKOUT to TSIZ(0:1), REG, RSV, BDIP, PTR output hold (MIN = 0.25 × B1)                                                                                                   | 7.60 | _     | 6.30 | _     | 5.00   | _     | 3.80   | _     | ns   |  |

| B7b        | CLKOUT to $\overline{\text{BR}}$ , $\overline{\text{BG}}$ , FRZ, VFLS(0:1), VF(0:2) IWP(0:2), LWP(0:1), $\overline{\text{STS}}$ output hold (MIN = 0.25 × B1)            | 7.60 | _     | 6.30 | _     | 5.00   | _     | 3.80   |       | ns   |  |

| B8         | CLKOUT to A(0:31), BADDR(28:30)<br>RD/WR, BURST, D(0:31), DP(0:3) valid<br>(MAX = 0.25 × B1 + 6.3)                                                                       |      | 13.80 |      | 12.50 | _      | 11.30 | _      | 10.00 | ns   |  |

| B8a        | CLKOUT to TSIZ(0:1), REG, RSV, BDIP, PTR valid (MAX = 0.25 × B1 + 6.3)                                                                                                   | _    | 13.80 | _    | 12.50 | _      | 11.30 | _      | 10.00 | ns   |  |

| B8b        | CLKOUT to $\overline{BR}$ , $\overline{BG}$ , VFLS(0:1), VF(0:2), IWP(0:2), FRZ, LWP(0:1), $\overline{STS}$ Valid <sup>3</sup> (MAX = 0.25 × B1 + 6.3)                   | _    | 13.80 | _    | 12.50 | _      | 11.30 | _      | 10.00 | ns   |  |

| В9         | CLKOUT to A(0:31), BADDR(28:30),<br>RD/WR, BURST, D(0:31), DP(0:3),<br>TSIZ(0:1), REG, RSV, PTR High-Z<br>(MAX = 0.25 × B1 + 6.3)                                        | 7.60 | 13.80 | 6.30 | 12.50 | 5.00   | 11.30 | 3.80   | 10.00 | ns   |  |

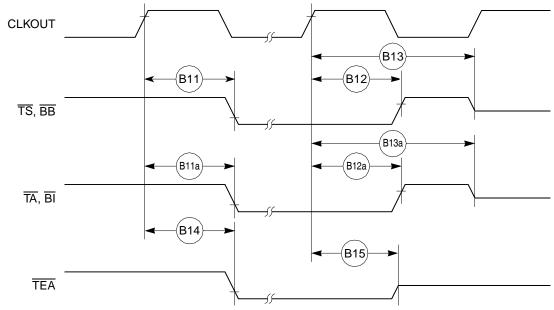

| B11        | CLKOUT to TS, BB assertion (MAX = 0.25 × B1 + 6.0)                                                                                                                       | 7.60 | 13.60 | 6.30 | 12.30 | 5.00   | 11.00 | 3.80   | 9.80  | ns   |  |

| B11a       | CLKOUT to $\overline{\text{TA}}$ , $\overline{\text{BI}}$ assertion (when driven by the memory controller or PCMCIA interface) (MAX = $0.00 \times \text{B1} + 9.30^2$ ) | 2.50 | 9.30  | 2.50 | 9.30  | 2.50   | 9.30  | 2.50   | 9.80  | ns   |  |

| B12        | CLKOUT to TS, BB negation (MAX = 0.25 × B1 + 4.8)                                                                                                                        | 7.60 | 12.30 | 6.30 | 11.00 | 5.00   | 9.80  | 3.80   | 8.50  | ns   |  |

| B12a       | CLKOUT to $\overline{\text{TA}}$ , $\overline{\text{BI}}$ negation (when driven by the memory controller or PCMCIA interface) (MAX = $0.00 \times \text{B1} + 9.00$ )    | 2.50 | 9.00  | 2.50 | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | ns   |  |

| B13        | CLKOUT to $\overline{TS}$ , $\overline{BB}$ High-Z (MIN = $0.25 \times B1$ )                                                                                             | 7.60 | 21.60 | 6.30 | 20.30 | 5.00   | 19.00 | 3.80   | 14.00 | ns   |  |

| B13a       | CLKOUT to $\overline{\text{TA}}$ , $\overline{\text{BI}}$ High-Z (when driven by the memory controller or PCMCIA interface) (MIN = $0.00 \times \text{B1} + 2.5$ )       | 2.50 | 15.00 | 2.50 | 15.00 | 2.50   | 15.00 | 2.50   | 15.00 | ns   |  |

| B14        | CLKOUT to TEA assertion<br>(MAX = 0.00 × B1 + 9.00)                                                                                                                      | 2.50 | 9.00  | 2.50 | 9.00  | 2.50   | 9.00  | 2.50   | 9.00  | ns   |  |

Figure 6 provides the timing for the synchronous output signals.

Figure 6. Synchronous Output Signals Timing

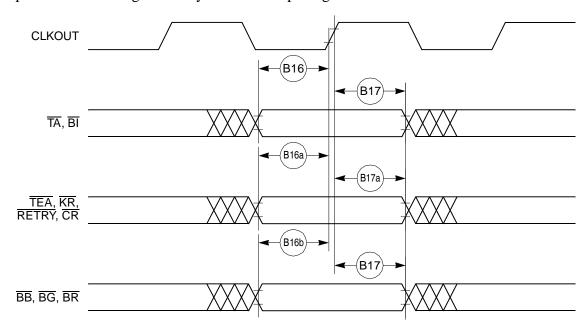

Figure 7 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 7. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

#### **Bus Signal Timing**

Figure 8 provides the timing for the synchronous input signals.

Figure 8. Synchronous Input Signals Timing

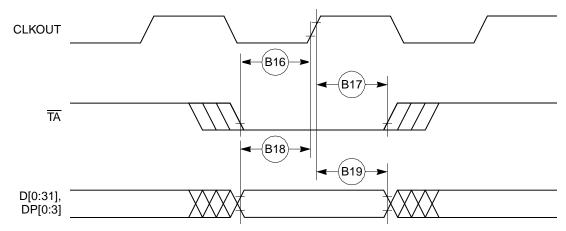

Figure 9 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 9. Input Data Timing in Normal Case

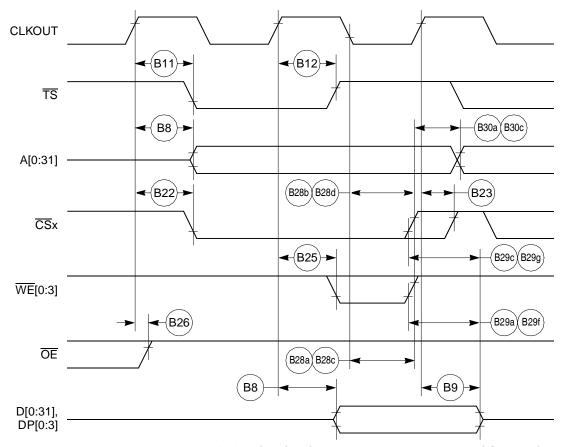

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

#### **Bus Signal Timing**

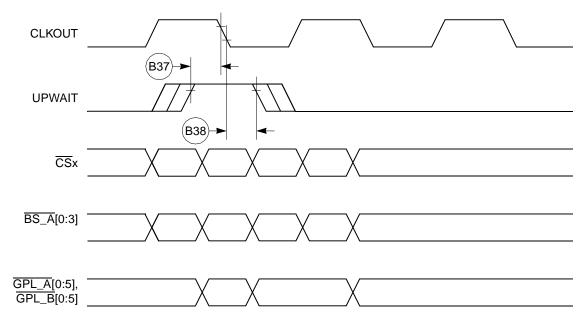

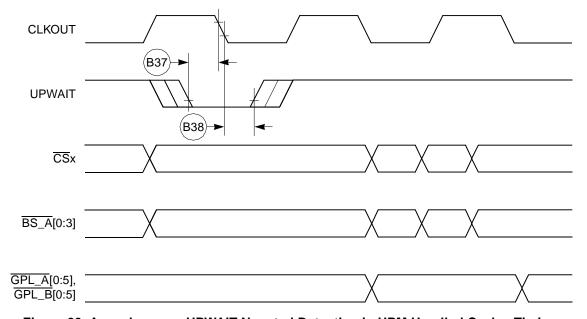

Figure 19 provides the timing for the asynchronous asserted UPWAIT signal that the UPM controls.

Figure 19. Asynchronous UPWAIT Asserted Detection in UPM Handled Cycles Timing

Figure 20 provides the timing for the asynchronous negated UPWAIT signal that the UPM controls.

Figure 20. Asynchronous UPWAIT Negated Detection in UPM Handled Cycles Timing

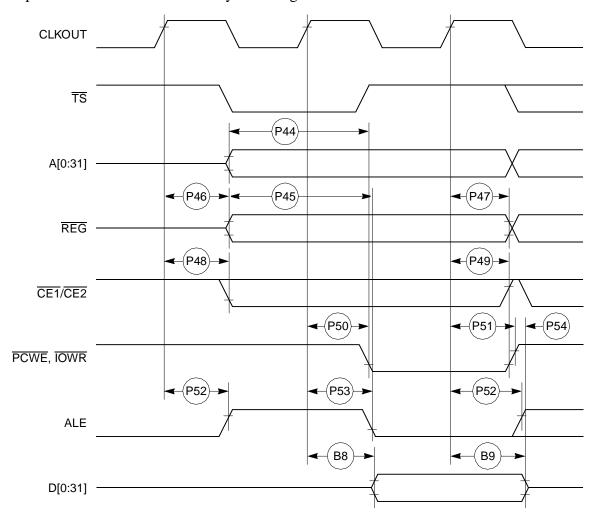

Figure 27 provides the PCMCIA access cycle timing for the external bus write.

Figure 27. PCMCIA Access Cycles Timing External Bus Write

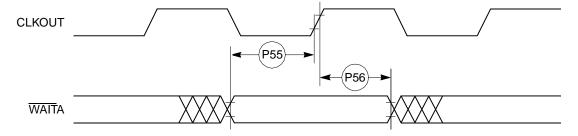

Figure 28 provides the PCMCIA WAIT signals detection timing.

Figure 28. PCMCIA WAIT Signals Detection Timing

Table 13 shows the debug port timing for the MPC852T.

**Table 13. Debug Port Timing**

| Num | Characteristic              | All Freque                   | Unit  |       |

|-----|-----------------------------|------------------------------|-------|-------|

| Num |                             | Min                          | Max   | Ollit |

| J82 | DSCK cycle time             | 3 × T <sub>CLOCKOUT</sub>    | _     | _     |

| J83 | DSCK clock pulse width      | 1.25 × T <sub>CLOCKOUT</sub> | _     | _     |

| J84 | DSCK rise and fall times    | 0.00                         | 3.00  | ns    |

| J85 | DSDI input data setup time  | 8.00                         | _     | ns    |

| J86 | DSDI data hold time         | 5.00                         | _     | ns    |

| J87 | DSCK low to DSDO data valid | 0.00                         | 15.00 | ns    |

| J88 | DSCK low to DSDO invalid    | 0.00                         | 2.00  | ns    |

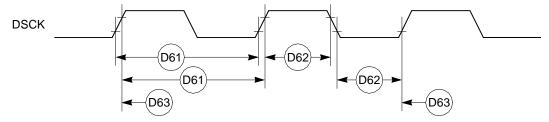

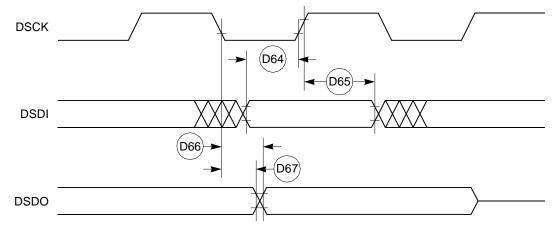

Figure 31 provides the input timing for the debug port clock.

Figure 31. Debug Port Clock Input Timing

Figure 32 provides the timing for the debug port.

Figure 32. Debug Port Timings

#### **CPM Electrical Characteristics**

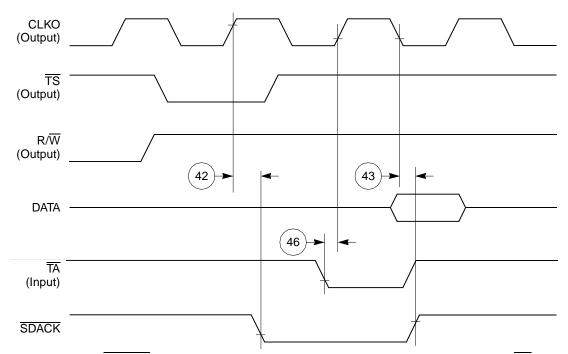

Figure 42. SDACK Timing Diagram—Peripheral Write, Externally-Generated TA

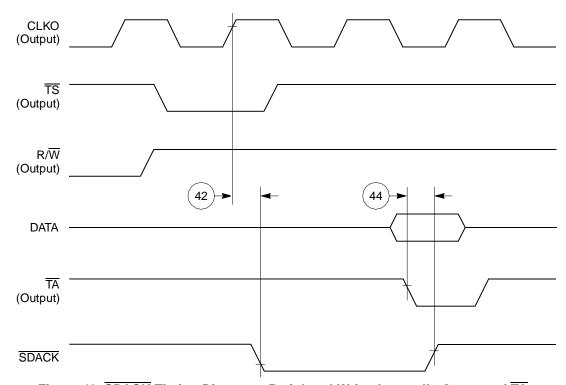

Figure 43. SDACK Timing Diagram—Peripheral Write, Internally-Generated TA

**CPM Electrical Characteristics**

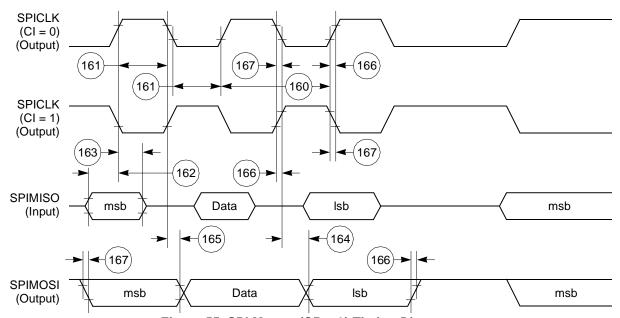

### 14.7 SPI Master AC Electrical Specifications

Table 23 provides the SPI master timings as shown in Figure 55 and Figure 56.

**Table 23. SPI Master Timing**

| Num | Observatoristis                     | All Freq |      |                  |

|-----|-------------------------------------|----------|------|------------------|

|     | Characteristic                      | Min      | Max  | Unit             |

| 160 | MASTER cycle time                   | 4        | 1024 | t <sub>cyc</sub> |

| 161 | MASTER clock (SCK) high or low time | 2        | 512  | t <sub>cyc</sub> |

| 162 | MASTER data setup time (inputs)     | 15       | _    | ns               |

| 163 | Master data hold time (inputs)      | 0        | _    | ns               |

| 164 | Master data valid (after SCK edge)  | _        | 10   | ns               |

| 165 | Master data hold time (outputs)     | 0        | _    | ns               |

| 166 | Rise time output                    | _        | 15   | ns               |

| 167 | Fall time output                    | _        | 15   | ns               |

Figure 55. SPI Master (CP = 0) Timing Diagram

Table 30. Pin Assignments—JEDEC Standard (continued)

| Name                                | Pin Number             | Туре                       |

|-------------------------------------|------------------------|----------------------------|

| FRZ<br>IRQ6                         | H4                     | Bidirectional (3.3 V only) |

| ĪRQ0                                | P13                    | Input (3.3 V only)         |

| ĪRQ1                                | M11                    | Input (3.3 V only)         |

| M_TX_CLK<br>IRQ7                    | N12                    | Input (3.3 V only)         |

| CS[0:5]                             | B2, A2, D3, C3, E6, C4 | Output                     |

| CS6                                 | D4                     | Output                     |

| CS7                                 | A3                     | Output                     |

| WE0<br>BS_B0<br>IORD                | D6                     | Output                     |

| WE1<br>BS_B1<br>IOWR                | C6                     | Output                     |

| WE2<br>BS_B2<br>PCOE                | A5                     | Output                     |

| WE3<br>BS_B3<br>PCWE                | B5                     | Output                     |

| BS_A[0:3]                           | A6, D7, C7, B7         | Output                     |

| GPL_A0<br>GPL_B0                    | C5                     | Output                     |

| OE<br>GPL_A1<br>GPL_B1              | D5                     | Output                     |

| GPL_A[2:3]<br>GPL_B[2:3]<br>CS[2-3] | A4, B4                 | Output                     |

| UPWAITA<br>GPL_A4                   | C2                     | Bidirectional (3.3 V only) |

| GPL_A5                              | E4                     | Output                     |

| PORESET                             | P1                     | Input (3.3 V only)         |

| RSTCONF                             | K4                     | Input (3.3 V only)         |

| HRESET                              | J4                     | Open-drain                 |

| SRESET                              | M3                     | Open-drain                 |

| XTAL                                | N1                     | Analog Output              |

### Table 30. Pin Assignments—JEDEC Standard (continued)

| Name                | Pin Number                                                                                               | Туре                            |

|---------------------|----------------------------------------------------------------------------------------------------------|---------------------------------|

| MII_MDIO            | G16                                                                                                      | Bidirectional<br>(5-V tolerant) |

| MII_TXEN            | T14                                                                                                      | Output<br>(5-V tolerant)        |

| MII_COL             | F2                                                                                                       | Input                           |

| V <sub>SSSYN</sub>  | N4                                                                                                       | PLL analog GND                  |

| V <sub>SSSYN1</sub> | P3                                                                                                       | PLL analog GND                  |

| V <sub>DDSYN</sub>  | P2                                                                                                       | PLL analog V <sub>DD</sub>      |

| GND                 | G6, G7, G8, G9, G10, G11, H6, H7, H8, H9, H10, H11, J6, J7, J8, J9, J10, J11, K6, K7, K8, K9, K10, K11   | Power                           |

| $V_{DDL}$           | A7, C1, D16, G15, L4, M2, R1, M15, T8                                                                    | Power                           |

| V <sub>DDH</sub>    | F5, F6, F7, F8, F9, F10, F11, F12, G5, G12, H5, H12, J5, J12, K5, K12, L5, L6, L7, L8, L9, L10, L11, L12 | Power                           |

| N/C                 | A1, A16, B16, C15, D14, E12, L13, M4, P15, R16, T1, T16                                                  | No connect                      |

Table 31. Pin Assignments—Non-JEDEC (continued)

| Name                   | Pin Number | Туре                                                      |

|------------------------|------------|-----------------------------------------------------------|

| IP_A1                  | N7         | Input (3.3 V only)                                        |

| IP_A2, IOIS16_A        | Т4         | Input (3.3 V only)                                        |

| IP_A3                  | N6         | Input (3.3 V only)                                        |

| IP_A4                  | U4         | Input (3.3 V only)                                        |

| IP_A5                  | P6         | Input (3.3 V only)                                        |

| IP_A6                  | N8         | Input (3.3 V only)                                        |

| IP_A7                  | Т3         | Input (3.3 V only)                                        |

| DSCK                   | J3         | Bidirectional<br>Three-state (3.3 V only)                 |

| IWP[0:1], VFLS[0:1]    | J4, H2     | Bidirectional (3.3 V only)                                |

| OP0                    | L2         | Bidirectional (3.3 V only)                                |

| OP1                    | L3         | Output                                                    |

| OP2, MODCK1, STS       | L4         | Bidirectional (3.3 V only)                                |

| OP3, MODCK2, DSDO      | M2         | Bidirectional (3.3 V only)                                |

| BADDR[28:29]           | M4, M3     | Output                                                    |

| BADDR30, REG           | K4         | Output                                                    |

| ĀS                     | К3         | Input (3.3 V only)                                        |

| PA11, RXD3             | F17        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA10, TXD3             | J16        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA9, RXD4              | K17        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA8, TXD4              | K16        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA3, CLK5, BRGO3, TIN3 | L17        | Bidirectional (5-V tolerant)                              |

| PA2, CLK6, TOUT3       | L15        | Bidirectional (5-V tolerant)                              |

| PA1, CLK7, BRGO4, TIN4 | M16        | Bidirectional (5-V tolerant)                              |

| PA0, CLK8, TOUT4       | N17        | Bidirectional (5-V tolerant)                              |

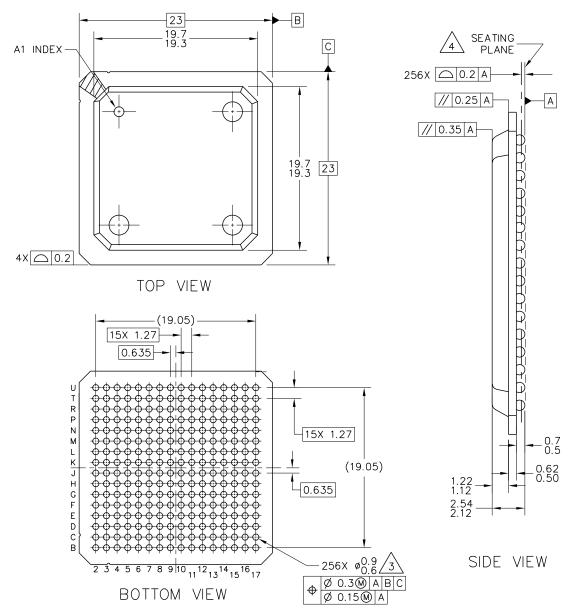

### 16.2 Mechanical Dimensions of the PBGA Package

For more information on the printed-circuit board layout of the PBGA package, including thermal via design and suggested pad layout, refer to Plastic Ball Grid Array Application Note (order number: AN1231) that is available from your local Freescale sales office. Figure 65 shows the mechanical dimensions of the PBGA package.

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Interpret dimensions and tolerances per ASME Y14.5M—1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is defined by the spherical crowns of the solder balls.

Note: Solder sphere composition is 95.5%Sn 45%Ag 0.5%Cu for MPC852TVRXXX. Solder sphere composition is 62%Sn 36%Pb 2%Ag for MPC852TZTXXX.

Figure 65. Mechanical Dimensions and Bottom Surface Nomenclature of the PBGA Package

MPC852T PowerQUICC™ Hardware Specifications, Rev. 4

**Document Revision History**

# 17 Document Revision History

Table 32 lists significant changes between revisions of this document.

**Table 32. Document Revision History**

| Revision | Date      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        |           | <ul> <li>Updated template.</li> <li>On page 1, updated first paragraph and added a second paragraph.</li> <li>After Table 2, inserted a new figure showing the undershoot/overshoot voltage (Figure 2) and renumbered the rest of the figures.</li> <li>In Table 9, for reset timings B29f and B29g added footnote indicating that the formula only applies to bus operation up to 50 MHz.</li> <li>In Figure 4, changed all reference voltage measurement points from 0.2 and 0.8 V to 50% level.</li> <li>In Table 17, changed num 46 description to read, "TA assertion to rising edge"</li> <li>In Figure 42, changed TA to reflect the rising edge of the clock.</li> </ul> |

| 3.1      | 1/18/2005 | Document template update.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.0      | 11/2004   | <ul> <li>Added sentence to Spec B1A about EXTCLK and CLKOUT being in Alignment for Integer Values</li> <li>Added a footnote to Spec 41 specifying that EDM = 1</li> <li>Broke the Section 16.1, "Pin Assignments," into 2 smaller sections for the JEDEC and non-JEDEC pinouts.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.0      | 12/2003   | Put 852T on the 1st page in place of 8245.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |           | Figure 62 on page 59 had overbars added on signals CR (pin G2) and WAIT_A (pin P4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.8      | 7/2003    | Changed the pinout to be JEDEC Compliant, changed timing parameters B28a through B28d, and B29d to show that TRLX can be 0 or 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.7      | 5/2003    | Changed the SPI Master Timing Specs. 162 and 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.6      | 4/2003    | Changed the package drawing in Figure 15-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.5      | 4/2003    | Changed 5 Port C pins with interrupt capability to 7 Port C pins. Added the Note: solder sphere composition for MPC852TVR and MPC852TCVR devices is 95.5%Sn 45%Ag 0.5%Cu to Figure 15-63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.4      | 2/2003    | Changed Table 15-30 Pin Assignments for the PLL Pins V <sub>SSSYN1</sub> , V <sub>SSSYN</sub> , V <sub>DDSYN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3      | 1/2003    | Added subscripts to timing diagrams for B1-B35, to specify memory controller settings for the specific edges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.2      | 1/2003    | In Table 15-30, specified EXTCLK as 3.3 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1      | 12/2002   | Added fast Ethernet controller to the features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1        | 11/2002   | Added values for 80 and 100 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0        | 10/2002   | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

**Document Revision History**

### THIS PAGE INTENTIONALLY LEFT BLANK

### THIS PAGE INTENTIONALLY LEFT BLANK