# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | MPC8xx                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 100MHz                                                                 |

| Co-Processors/DSP               | Communications; CPM                                                    |

| RAM Controllers                 | DRAM                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10Mbps (1)                                                             |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 3.3V                                                                   |

| Operating Temperature           | -40°C ~ 100°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 256-BBGA                                                               |

| Supplier Device Package         | 256-PBGA (23x23)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc852tcvr100a |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features

- Two baud rate generators

- Independent (can be connected to any SCC3/4 or SMC1)

- Allows changes during operation

- Autobaud support option

- Two SCCs (serial communication controllers)

- Ethernet/IEEE 802.3<sup>®</sup> standard optional on SCC3 and SCC4, supporting full 10-Mbps operation

- HDLC/SDLC

- HDLC bus (implements an HDLC-based local area network (LAN))

- Universal asynchronous receiver transmitter (UART)

- Totally transparent (bit streams)

- Totally transparent (frame-based with optional cyclic redundancy check (CRC))

- One SMC (serial management channel)

- UART

- One SPI (serial peripheral interface)

- Supports master and slave modes

- Supports multimaster operation on the same bus

- PCMCIA interface

- Master (socket) interface, release 2.1 compliant

- Supports one independent PCMCIA socket; 8-memory or I/O windows supported

- Debug interface

- Eight comparators: four operate on instruction address, two operate on data address, and two

operate on data

- Supports conditions:  $= \neq < >$

- Each watchpoint can generate a break point internally

- Normal high and normal low power modes to conserve power

- 1.8 V core and 3.3-V I/O operation with 5-V TTL compatibility. Refer to Table 5 for a listing of the 5-V tolerant pins.

Figure 1 shows the MPC852T block diagram.

**Power Dissipation**

# 5 **Power Dissipation**

Table 4 provides power dissipation information. The modes are 1:1, where CPU and bus speeds are equal, and 2:1 mode, where CPU frequency is twice bus speed.

| Die Revision | Bus Mode | Frequency<br>(MHz) | Typical <sup>1</sup> | Maximum <sup>2</sup> | Unit |

|--------------|----------|--------------------|----------------------|----------------------|------|

|              |          |                    |                      |                      |      |

|              |          | 50                 | 110                  | 140                  | mW   |

|              | 1:1      | 66                 | 150                  | 180                  | mW   |

| 0            |          | 66                 | 140                  | 160                  | mW   |

|              | 2:1      | 80                 | 170                  | 200                  | mW   |

|              | 2.1      | 100                | 210                  | 250                  | mW   |

Table 4. Power Dissipation (P<sub>D</sub>)

<sup>1</sup> Typical power dissipation is measured at 1.9 V.

$^2$   $\,$  Maximum power dissipation at V\_{DDL} and V\_{DDSYN} is at 1.9 V. and V\_{DDH} is at 3.465 V.

NOTE

Values in Table 4 represent  $V_{DDL}$ -based power dissipation, and do not include I/O power dissipation over  $V_{DDH}$ . I/O power dissipation varies widely by application that buffer current can cause, depending on external circuitry.

The V<sub>DDSYN</sub> power dissipation is negligible.

# 6 DC Characteristics

Table 5 provides the DC electrical characteristics for the MPC852T.

Table 5. DC Electrical Specifications

| Characteristic                                                                                                                                                                               | Symbol                                                       | Min                 | Мах              | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------|------------------|------|

| Operating voltage                                                                                                                                                                            | V <sub>DDH</sub>                                             | 3.135               | 3.465            | V    |

|                                                                                                                                                                                              | V <sub>DDL</sub>                                             | 1.7                 | 1.9              | V    |

|                                                                                                                                                                                              | V <sub>DDSYN</sub>                                           | 1.7                 | 1.9              | V    |

|                                                                                                                                                                                              | Difference between<br>V <sub>DDL</sub> to V <sub>DDSYN</sub> | —                   | 100              | mV   |

| Input high voltage (all inputs except PA[0:3], PA[8:11],<br>PB15, PB[24:25]; PB[28:31], PC[4:7], PC[12:13], PC15,<br>PD[3:15], TDI, TDO, TCK, TRST, TMS, MII_TXEN,<br>MII_MDIO) <sup>1</sup> | V <sub>IH</sub>                                              | 2.0                 | 3.465            | V    |

| Input low voltage                                                                                                                                                                            | V <sub>IL</sub>                                              | GND                 | 0.8              | V    |

| EXTAL, EXTCLK input high voltage                                                                                                                                                             | V <sub>IHC</sub>                                             | $0.7 	imes V_{DDH}$ | V <sub>DDH</sub> | V    |

NP

The MBMR[GPLB4DIS], PAPAR, PADIR, PBPAR, PBDIR, PCPAR, and PCDIR should be configured with the mandatory value in Table 6 in the boot code after the reset deasserts.

| Register/Configuration                     | Field                                     | Value<br>(Binary) |

|--------------------------------------------|-------------------------------------------|-------------------|

| HRCW (Hardware reset configuration word)   | HRCW[DBGC]                                | X1                |

| SIUMCR (SIU module configuration register) | SIUMCR[DBGC]                              | X1                |

| MBMR (Machine B mode register)             | MBMR[GPLB4DIS}                            | 0                 |

| PAPAR (Port A pin assignment register)     | PAPAR[4-7]<br>PAPAR[12-15]                | 0                 |

| PADIR (Port A data direction register)     | PADIR[4–7]<br>PADIR[12–15]                | 1                 |

| PBPAR (Port B pin assignment register)     | PBPAR[14]<br>PBPAR[16–23]<br>PBPAR[26–27] | 0                 |

| PBDIR (Port B data direction register)     | PBDIR[14]<br>PBDIR[16–23]<br>PBDIR[26–27] | 1                 |

| PCPAR (Port C pin assignment register)     | PCPAR[8–11]<br>PCDIR[14]                  | 0                 |

| PCDIR (Port C data direction register)     | PCDIR[8–11]<br>PCDIR[14]                  | 1                 |

| Table 6. Mandatory | v Reset | Configuration | of MPC852T   |

|--------------------|---------|---------------|--------------|

|                    | y neset | ooninguration | 01 101 00321 |

# **11 Layout Practices**

Each  $V_{DD}$  pin on the MPC852T should be provided with a low-impedance path to the board's supply. Each GND pin should likewise be provided with a low-impedance path to ground. The power supply pins drive distinct groups of logic on chip. The  $V_{DD}$  power supply should be bypassed to ground using at least four 0.1 µF bypass capacitors located as close as possible to the four sides of the package. Each board designed should be characterized and additional appropriate decoupling capacitors should be used if required. The capacitor leads and associated printed-circuit traces connecting to chip  $V_{DD}$  and GND should be kept to less than half an inch per capacitor lead. At a minimum, a four-layer board employing two inner layers as  $V_{DD}$  and GND planes should be used.

All output pins on the MPC852T have fast rise and fall times. Printed-circuit (PC) trace interconnection length should be minimized to minimize undershoot and reflections that these fast output switching times cause. This recommendation particularly applies to the address and data buses. Maximum PC trace lengths of six inches are recommended. Capacitance calculations should consider all device loads as well as parasitic capacitances that the PC traces cause. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads, because these loads create higher transient currents in the  $V_{DD}$  and GND circuits. Pull up all unused inputs or signals that are inputs during reset. Special care should be taken to minimize the noise levels on the PLL supply pins. For more information, please refer to the *MPC866 PowerQUICC*<sup>TM</sup> *Family Reference Manual*, Section 14.4.3, "Clock Synthesizer Power ( $V_{DDSYN}$ ,  $V_{SSSYN}$ ,  $V_{SSSYN1}$ )."

| Num  | Characteristic                                                                                                                                                            | 33    | MHz   | 40 1  | MHz   | 50   | MHz   | 66 MHz |       | Unit |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                                            | Min   | Max   | Min   | Max   | Min  | Max   | Min    | Max   | Onit |

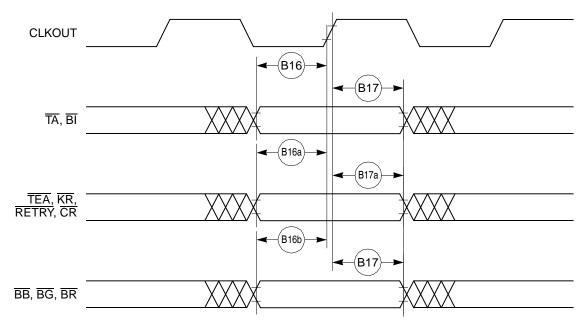

| B15  | CLKOUT to $\overline{\text{TEA}}$ High-Z<br>(MIN = 0.00 × B1 + 2.50)                                                                                                      | 2.50  | 15.00 | 2.50  | 15.00 | 2.50 | 15.00 | 2.50   | 15.00 | ns   |

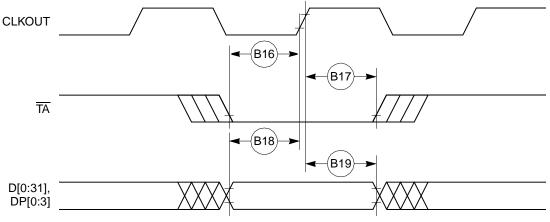

| B16  | $\overline{\text{TA}}$ , $\overline{\text{BI}}$ valid to CLKOUT (setup time)<br>(MIN = 0.00 × B1 + 6.00)                                                                  | 6.00  | _     | 6.00  | _     | 6.00 | —     | 6.00   | —     | ns   |

| B16a | TEA, $\overline{\text{KR}}$ , $\overline{\text{RETRY}}$ , $\overline{\text{CR}}$ valid to CLKOUT (setup time) (MIN = 0.00 × B1 + 4.5)                                     | 4.50  | _     | 4.50  | _     | 4.50 | _     | 4.50   | _     | ns   |

| B16b | $\overline{BB}, \overline{BG}, \overline{BR}, \text{ valid to CLKOUT (setup time)}$<br><sup>3</sup> (4MIN = 0.00 × B1 +.000)                                              | 4.00  | _     | 4.00  | —     | 4.00 | —     | 4.00   | —     | ns   |

| B17  | CLKOUT to $\overline{TA}$ , $\overline{TEA}$ , $\overline{BI}$ , $\overline{BB}$ , $\overline{BG}$ , $\overline{BR}$ valid (hold time) (MIN = $0.00 \times B1 + 1.00^4$ ) | 1.00  | _     | 1.00  | _     | 1.00 | _     | 2.00   | _     | ns   |

| B17a | CLKOUT to $\overline{KR}$ , $\overline{RETRY}$ , $\overline{CR}$ valid (hold time) (MIN = 0.00 × B1 + 2.00)                                                               | 2.00  | _     | 2.00  |       | 2.00 | —     | 2.00   | _     | ns   |

| B18  | D(0:31), DP(0:3) valid to CLKOUT rising edge (setup time) <sup>5</sup><br>(MIN = $0.00 \times B1 + 6.00$ )                                                                | 6.00  | _     | 6.00  |       | 6.00 | —     | 6.00   | —     | ns   |

| B19  | CLKOUT rising edge to D(0:31), DP(0:3) valid (hold time) <sup>5</sup> (MIN = $0.00 \times B1 + 1.00^{6}$ )                                                                | 1.00  | _     | 1.00  | _     | 1.00 | —     | 2.00   | _     | ns   |

| B20  | D(0:31), DP(0:3) valid to CLKOUT falling<br>edge (setup time) <sup>7</sup><br>(MIN = $0.00 \times B1 + 4.00$ )                                                            | 4.00  | _     | 4.00  | _     | 4.00 | —     | 4.00   | —     | ns   |

| B21  | CLKOUT falling edge to D(0:31), DP(0:3) valid (hold Time) <sup>7</sup> (MIN = $0.00 \times B1 + 2.00$ )                                                                   | 2.00  | _     | 2.00  | —     | 2.00 | —     | 2.00   | —     | ns   |

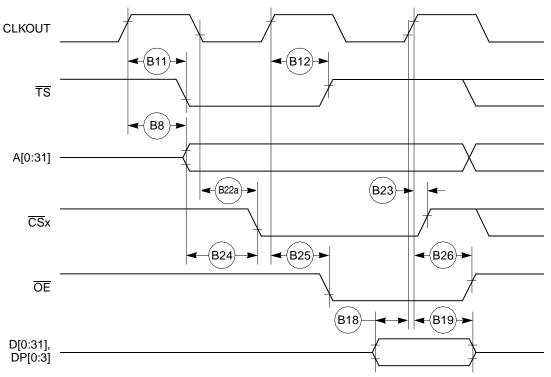

| B22  | CLKOUT rising edge to $\overline{CS}$ asserted<br>GPCM ACS = 00 (MAX = 0.25 × B1 + 6.3)                                                                                   | 7.60  | 13.80 | 6.30  | 12.50 | 5.00 | 11.30 | 3.80   | 10.00 | ns   |

| B22a | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 10, TRLX = 0<br>(MAX = 0.00 × B1 + 8.00)                                                                    | —     | 8.00  | _     | 8.00  | _    | 8.00  | _      | 8.00  | ns   |

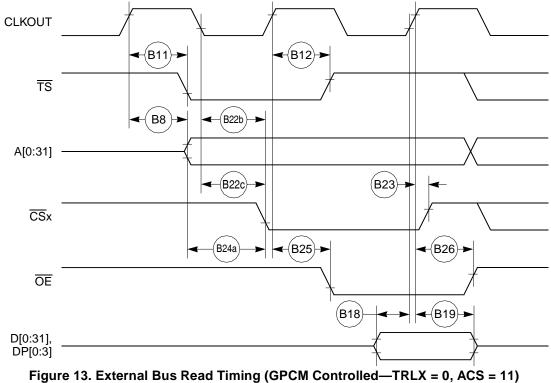

| B22b | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 11, TRLX = 0, EBDF = 0<br>(MAX = 0.25 × B1 + 6.3)                                                           | 7.60  | 13.80 | 6.30  | 12.50 | 5.00 | 11.30 | 3.80   | 10.00 | ns   |

| B22c | CLKOUT falling edge to $\overline{CS}$ asserted<br>GPCM ACS = 11, TRLX = 0, EBDF = 1<br>(MAX = 0.375 × B1 + 6.6)                                                          | 10.90 | 18.00 | 10.90 | 16.00 | 7.00 | 14.10 | 5.20   | 12.30 | ns   |

| B23  | CLKOUT rising edge to $\overline{CS}$ negated<br>GPCM read access, GPCM write access<br>ACS = 00, TRLX = 0 & CSNT = 0<br>(MAX = 0.00 × B1 + 8.00)                         | 2.00  | 8.00  | 2.00  | 8.00  | 2.00 | 8.00  | 2.00   | 8.00  | ns   |

| B24  | A(0:31) and BADDR(28:30) to $\overline{CS}$<br>asserted GPCM ACS = 10, TRLX = 0<br>(MIN = $0.25 \times B1 - 2.00$ )                                                       | 5.60  |       | 4.30  |       | 3.00 |       | 1.80   | _     | ns   |

#### Table 9. Bus Operation Timings (continued)

| Nivues | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 I  | ИНz | 40 M  | MHz 50 MHz |       |     | 66 I  | l lm:t |      |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------------|-------|-----|-------|--------|------|

| Num    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Min   | Мах | Min   | Мах        | Min   | Max | Min   | Max    | Unit |

| B29b   | $\overline{\text{CS}}$ negated to D(0:31), DP(0:3), High Z<br>GPCM write access, ACS = 00,<br>TRLX = 0,1 and CSNT = 0<br>(MIN = 0.25 × B1 - 2.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.60  | _   | 4.30  | _          | 3.00  | _   | 1.80  | _      | ns   |

| B29c   | $\label{eq:constraint} \hline \hline \hline CS \ negated to \ D(0:31), \ DP(0:3) \ High-Z \\ GPCM \ write \ access, \ TRLX = 0, \ CSNT = 1, \\ ACS = 10, \ or \ ACS = 11 \ EBDF = 0 \\ (MIN = 0.50 \times B1 - 2.00) \\ \hline \hline$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13.20 | _   | 10.50 | _          | 8.00  | _   | 5.60  | _      | ns   |

| B29d   | $ \frac{\overline{WE}(0:3)/BS_B[0:3] \text{ negated to } D(0:31), \\ DP(0:3) \text{ High-Z GPCM write access, TRLX} \\ = 1, CSNT = 1, EBDF = 0 \\ (MIN = 1.50 \times B1 - 2.00) $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43.50 | _   | 35.50 | _          | 28.00 | _   | 20.70 | _      | ns   |

| B29e   | $\overline{CS}$ negated to D(0:31), DP(0:3) High-Z<br>GPCM write access, TRLX = 1, CSNT = 1,<br>ACS = 10, or ACS = 11 EBDF = 0<br>(MIN = 1.50 × B1 - 2.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43.50 | _   | 35.50 | _          | 28.00 | _   | 20.70 | _      | ns   |

| B29f   | $\label{eq:weighted} \hline \hline WE(0:3/BS_B[0:3]) \ \text{negated to } D(0:31), \\ DP(0:3) \ \text{High Z GPCM write access}, \\ TRLX = 0, \ CSNT = 1, \ EBDF = 1 \\ (MIN = 0.375 \times B1 - 6.30)^8 \\ \hline \hline \hline \\ \hline \end{matrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.00  | _   | 3.00  | _          | 1.10  | _   | 0.00  | _      | ns   |

| B29g   | $\frac{\overline{\text{CS}} \text{ negated to D}(0:31), \text{ DP}(0:3) \text{ High-Z}}{\text{GPCM write access, TRLX = 0, CSNT = 1}}$ $\text{ACS = 10 \text{ or ACS = 11, EBDF = 1}}$ $(\text{MIN = 0.375 \times \text{B1} - 6.30)^8}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.00  | _   | 3.00  | _          | 1.10  | —   | 0.00  | _      | ns   |

| B29h   | $\label{eq:weighted} \hline \hline WE(0:3)/BS_B[0:3] \mbox{ negated to } D(0:31), \\ DP(0:3) \mbox{ High Z GPCM write access,} \\ TRLX = 1, \mbox{ CSNT } = 1, \mbox{ EBDF } = 1 \\ (MIN = 0.375 \times B1 - 3.30) \\ \hline \hline \hline \end{tabular}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38.40 | _   | 31.10 | _          | 24.20 | _   | 17.50 | _      | ns   |

| B29i   | $\label{eq:cs} \hline \frac{\overline{\text{CS}}}{\text{Regated to D}(0:31), \text{DP}(0:3) \text{ High-Z}} \\ \text{GPCM write access, TRLX = 1, CSNT = 1,} \\ \text{ACS = 10 or ACS = 11, EBDF = 1} \\ (\text{MIN = } 0.375 \times \text{B1} - 3.30) \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38.40 | _   | 31.10 | _          | 24.20 | _   | 17.50 | _      | ns   |

| B30    | $\overline{CS}$ , $\overline{WE}$ (0:3)/BS_B[0:3] negated to<br>A(0:31), BADDR(28:30) Invalid GPCM<br>write access <sup>9</sup> (MIN = 0.25 × B1 – 2.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.60  | _   | 4.30  | _          | 3.00  | _   | 1.80  | _      | ns   |

| B30a   | $eq:weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_weighted_$ | 13.20 |     | 10.50 |            | 8.00  |     | 5.60  |        | ns   |

#### Table 9. Bus Operation Timings (continued)

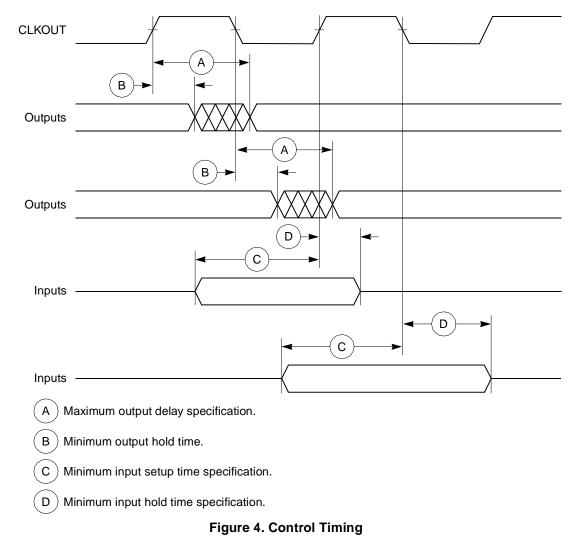

Figure 4 is the control timing diagram.

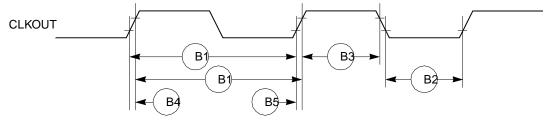

Figure 5 provides the timing for the external clock.

Figure 5. External Clock Timing

Figure 8 provides the timing for the synchronous input signals.

Figure 8. Synchronous Input Signals Timing

Figure 9 provides normal case timing for input data. It also applies to normal read accesses under the control of the UPM in the memory controller.

Figure 9. Input Data Timing in Normal Case

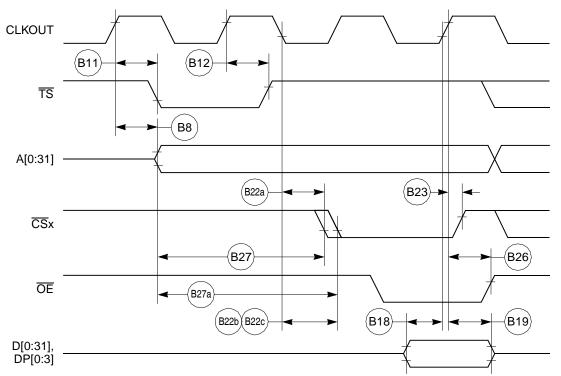

Figure 14. External Bus Read Timing (GPCM Controlled—TRLX = 0 or 1, ACS = 10, ACS = 11)

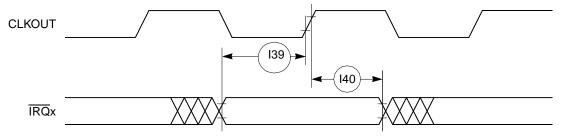

Table 10 provides interrupt timing for the MPC852T.

Table 10. Interrupt Timing

| Num   | Characteristic <sup>1</sup>                    | All Freq                | Unit |      |

|-------|------------------------------------------------|-------------------------|------|------|

| Nulli | Gharacteristic                                 | Min                     | Мах  | Unit |

| 139   | IRQx valid to CLKOUT rising edge (set up time) | 6.00                    |      | ns   |

| 140   | IRQx hold time after CLKOUT                    | 2.00                    |      | ns   |

| 141   | IRQx pulse width low                           | 3.00                    |      | ns   |

| 142   | IRQx pulse width high                          | 3.00                    |      | ns   |

| 143   | IRQx edge-to-edge time                         | $4 \times T_{CLOCKOUT}$ |      | _    |

<sup>1</sup> The timings I39 and I40 describe the testing conditions under which the IRQ lines are tested when being defined as level-sensitive. The IRQ lines are synchronized internally and need not be asserted or negated with reference to the CLKOUT. The timings I41, I42, and I43 are specified to allow the correct function of the IRQ lines detection circuitry, and have no direct relation with the total system interrupt latency that the MPC852T is able to support.

Figure 24 provides the interrupt detection timing for the external level-sensitive lines.

Figure 24. Interrupt Detection Timing for External Level Sensitive Lines

Figure 25 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 25. Interrupt Detection Timing for External Edge Sensitive Lines

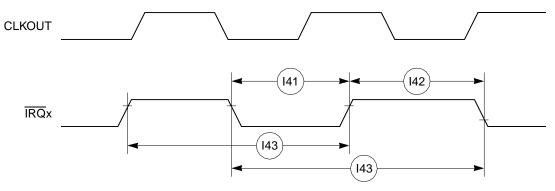

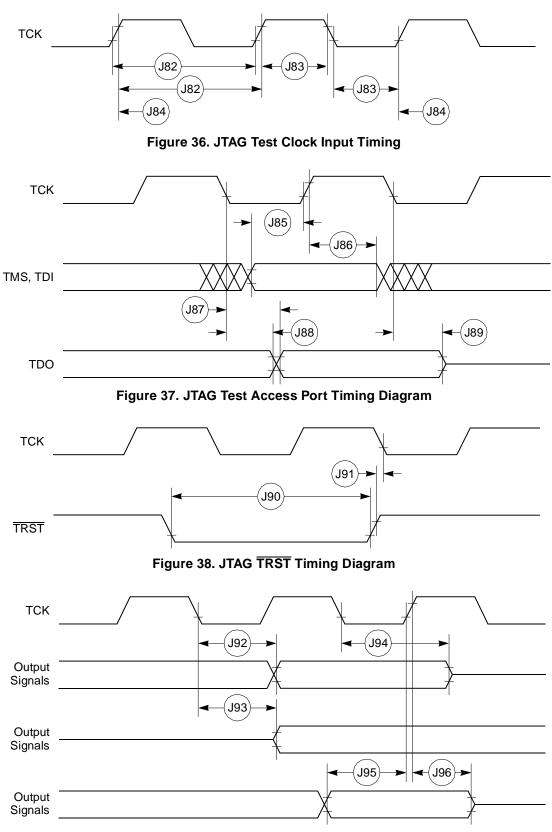

Table 14 shows the reset timing for the MPC852T.

Table 14. Reset Timing

| Num | Characteristic                                                                                                                              | 33     | MHz   | 40 M   | ИНz   | 50 N   | MHz   | 66 MHz |       | Unit |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

| NUM | Characteristic                                                                                                                              | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | Unit |

| J82 | CLKOUT to $\overline{\text{HRESET}}$ high impedance<br>(MAX = 0.00 × B1 + 20.00)                                                            | _      | 20.00 | —      | 20.00 | —      | 20.00 | —      | 20.00 | ns   |

| J83 | CLKOUT to $\overline{\text{SRESET}}$ high impedance<br>(MAX = 0.00 × B1 + 20.00)                                                            | _      | 20.00 | —      | 20.00 | —      | 20.00 | _      | 20.00 | ns   |

| J84 | $\overrightarrow{RSTCONF} \text{ pulse width (MIN = 17.00 \times B1)}$                                                                      | 515.20 |       | 425.00 | _     | 340.00 | _     | 257.60 | _     | ns   |

| J85 | _                                                                                                                                           | —      |       | —      | _     | —      | _     | —      | _     | —    |

| J86 | Configuration data to HRESET rising edge set up time (MIN = $15.00 \times B1 + 50.00$ )                                                     | 504.50 | —     | 425.00 | _     | 350.00 | _     | 277.30 | _     | ns   |

| J87 | Configuration data to $\overrightarrow{\text{RSTCONF}}$ rising<br>edge set up time<br>(MIN = 0.00 × B1 + 350.00)                            | 350.00 | —     | 350.00 | _     | 350.00 | —     | 350.00 | _     | ns   |

| J88 | Configuration data hold time after<br>$\overrightarrow{\text{RSTCONF}}$ negation<br>(MIN = 0.00 × B1 + 0.00)                                | 0.00   | —     | 0.00   | _     | 0.00   | _     | 0.00   | —     | ns   |

| J89 | Configuration data hold time after<br>HRESET negation<br>(MIN = $0.00 \times B1 + 0.00$ )                                                   | 0.00   | —     | 0.00   | _     | 0.00   | —     | 0.00   | _     | ns   |

| J90 | HRESET and RSTCONF asserted to data out drive (MAX = $0.00 \times B1 + 25.00$ )                                                             | _      | 25.00 | -      | 25.00 | -      | 25.00 | —      | 25.00 | ns   |

| J91 | <b>RSTCONF</b> negated to data out high impedance. (MAX = $0.00 \times B1 + 25.00$ )                                                        | _      | 25.00 | —      | 25.00 | —      | 25.00 | _      | 25.00 | ns   |

| J92 | CLKOUT of last rising edge before chip three-states $\overline{\text{HRESET}}$ to data out high impedance. (MAX = 0.00 × B1 + 25.00)        | —      | 25.00 | —      | 25.00 | _      | 25.00 | _      | 25.00 | ns   |

| J93 | DSDI, DSCK set up (MIN = $3.00 \times B1$ )                                                                                                 | 90.90  |       | 75.00  | _     | 60.00  | _     | 45.50  | _     | ns   |

| J94 | DSDI, DSCK hold time<br>(MIN = $0.00 \times B1 + 0.00$ )                                                                                    | 0.00   | —     | 0.00   | _     | 0.00   | _     | 0.00   | _     | ns   |

| J95 | $\begin{tabular}{l} \hline \hline SRESET negated to CLKOUT rising edge \\ for DSDI and DSCK sample \\ (MIN = 8.00 \times B1) \end{tabular}$ | 242.40 | _     | 200.00 |       | 160.00 | _     | 121.20 |       | ns   |

Figure 39. Boundary Scan (JTAG) Timing Diagram

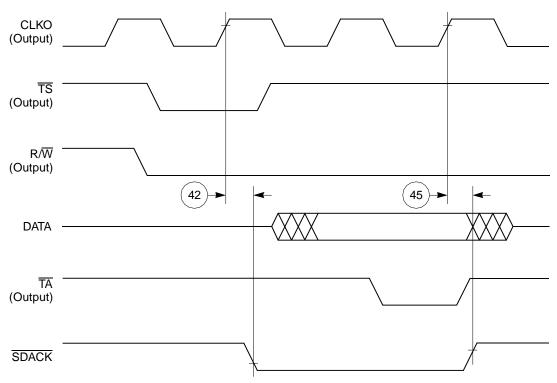

Figure 44. SDACK Timing Diagram—Peripheral Read, Internally-Generated TA

### **14.3 Baud Rate Generator AC Electrical Specifications**

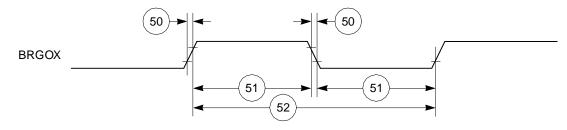

Table 18 provides the baud rate generator timings as shown in Figure 45.

| Table 18 | . Baud | Rate | Generator | Timing |

|----------|--------|------|-----------|--------|

|----------|--------|------|-----------|--------|

| Num | Characteristic          | All Freq | Unit |    |

|-----|-------------------------|----------|------|----|

| Num | Unardetensite           | Min      | Мах  | Om |

| 50  | BRGO rise and fall time | —        | 10   | ns |

| 51  | BRGO duty cycle         | 40       | 60   | %  |

| 52  | BRGO cycle              | 40       | _    | ns |

Figure 45. Baud Rate Generator Timing Diagram

**CPM Electrical Characteristics**

### 14.4 Timer AC Electrical Specifications

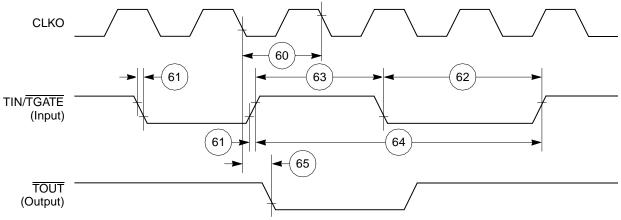

Table 19 provides the general-purpose timer timings as shown in Figure 46.

#### Table 19. Timer Timing

| Num | Characteristic               | All Freq | Unit |      |

|-----|------------------------------|----------|------|------|

|     | Cildiacteristic              | Min      | Мах  | Unit |

| 61  | TIN/TGATE rise and fall time | 10       | _    | ns   |

| 62  | TIN/TGATE low time           | 1        | _    | clk  |

| 63  | TIN/TGATE high time          | 2        | _    | clk  |

| 64  | TIN/TGATE cycle time         | 3        | _    | clk  |

| 65  | CLKO low to TOUT valid       | 3        | 25   | ns   |

Figure 46. CPM General-Purpose Timers Timing Diagram

### 14.5 SCC in NMSI Mode Electrical Specifications

Table 20 provides the NMSI external clock timing.

| Table 20 | . NMSI | External | Clock | Timing |

|----------|--------|----------|-------|--------|

|----------|--------|----------|-------|--------|

| Num | Characteristic                                       | All Frequencies |       | Unit |

|-----|------------------------------------------------------|-----------------|-------|------|

| Num | Characteristic                                       | Min             | Мах   | Onit |

| 100 | RCLK3 and TCLK3 width high <sup>1</sup>              | 1/SYNCCLK       | _     | ns   |

| 101 | RCLK3 and TCLK3 width low                            | 1/SYNCCLK + 5   | _     | ns   |

| 102 | RCLK3 and TCLK3 rise/fall time                       | —               | 15.00 | ns   |

| 103 | TXD3 active delay (from TCLK3 falling edge)          | 0.00            | 50.00 | ns   |

| 104 | RTS3 active/inactive delay (from TCLK3 falling edge) | 0.00            | 50.00 | ns   |

| 105 | CTS3 setup time to TCLK3 rising edge                 | 5.00            | —     | ns   |

| 106 | RXD3 setup time to RCLK3 rising edge                 | 5.00            | _     | ns   |

#### Table 20. NMSI External Clock Timing (continued)

| Num | Characteristic                                     | All Frequencies |     | Unit |

|-----|----------------------------------------------------|-----------------|-----|------|

| Num | Characteristic                                     | Min             | Мах | onit |

| 107 | RXD3 hold time from RCLK3 rising edge <sup>2</sup> | 5.00            | _   | ns   |

| 108 | CD3 setup Time to RCLK3 rising edge                | 5.00            | _   | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK3 and SyncCLK/TCLK3 must be greater than or equal to 2.25/1.

<sup>2</sup> Also applies to  $\overline{CD}$  and  $\overline{CTS}$  hold time when they are used as an external sync signal.

Table 21 provides the NMSI internal clock timing.

Table 21. NMSI Internal Clock Timing

| Num   | Characteristic                                       | All Frequencies |           | Unit |

|-------|------------------------------------------------------|-----------------|-----------|------|

| Nulli |                                                      | Min             | Мах       | onit |

| 100   | RCLK3 and TCLK3 frequency <sup>1</sup>               | 0.00            | SYNCCLK/3 | MHz  |

| 102   | RCLK3 and TCLK3 rise/fall time                       | _               | —         | ns   |

| 103   | TXD3 active delay (from TCLK3 falling edge)          | 0.00            | 30.00     | ns   |

| 104   | RTS3 active/inactive delay (from TCLK3 falling edge) | 0.00            | 30.00     | ns   |

| 105   | CTS3 setup time to TCLK3 rising edge                 | 40.00           | —         | ns   |

| 106   | RXD3 setup time to RCLK3 rising edge                 | 40.00           | —         | ns   |

| 107   | RXD3 hold time from RCLK3 rising edge <sup>2</sup>   | 0.00            | —         | ns   |

| 108   | CD3 setup time to RCLK3 rising edge                  | 40.00           | —         | ns   |

<sup>1</sup> The ratios SyncCLK/RCLK3 and SyncCLK/TCLK3 must be greater or equal to 3/1.

<sup>2</sup> Also applies to  $\overline{\text{CD}}$  and  $\overline{\text{CTS}}$  hold time when they are used as an external sync signals.

**CPM Electrical Characteristics**

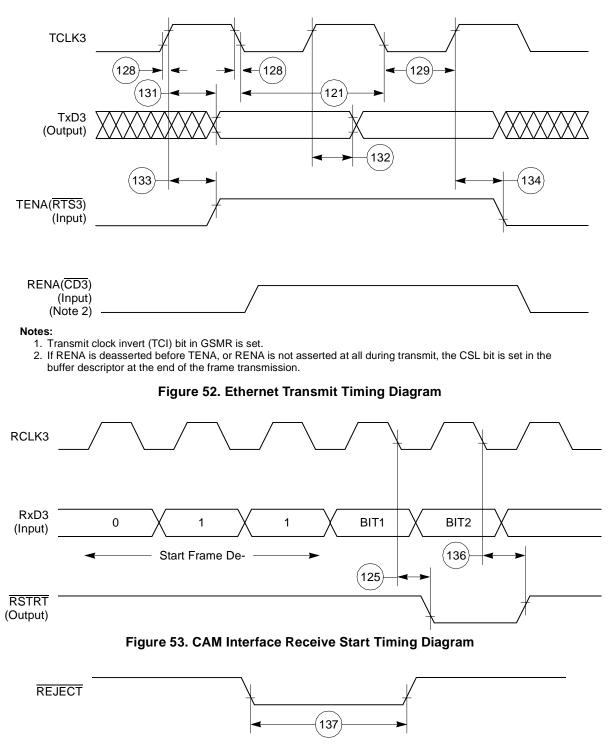

Figure 54. CAM Interface REJECT Timing Diagram

Table 31 contains a list of the MPC852T input and output signals and shows multiplexing and pin assignments.

| Name                       | Pin Number                                                                                                                                                       | Туре                                         |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| A[0:31]                    | C16, B16, B15, D15, E14, F12, C15, B14, D14, C14, E13, F11, D13,<br>C13, B13, E12, F10, D12, B10, B12, E11, D11, C9, B11, E10, D10,<br>D9, C12, B9, C11, C10, E9 | Bidirectional<br>Three-state (3.3 V only)    |

| TSIZ0, REG                 | F9                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| TSIZ1                      | F8                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| RD/WR                      | C2                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| BURST                      | H4                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| BDIP, GPL_B5               | E2                                                                                                                                                               | Output                                       |

| TS                         | F3                                                                                                                                                               | Bidirectional<br>Active pull-up (3.3 V only) |

| TA                         | G5                                                                                                                                                               | Bidirectional<br>Active pull-up (3.3 V only) |

| TEA                        | F4                                                                                                                                                               | Open-drain                                   |

| BI                         | E3                                                                                                                                                               | Bidirectional<br>Active pull-up (3.3 V only) |

| IRQ2, RSV                  | НЗ                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| IRQ4, KR<br>RETRY, SPKROUT | К2                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| CR, IRQ3                   | G2                                                                                                                                                               | Input (3.3 V only)                           |

| D[0:31]                    | T14, U12, T11, U11, U13, T10, T8, U7, U14, N11, P11, R11, R13, T13, N10, P10, R10, P12, U10, T9, R9, P9, U8, R12, R8, P8, N9, T12, T7, R7, U6, T6                | Bidirectional<br>Three-state (3.3 V only)    |

| DP0, IRQ3                  | R5                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| DP1, IRQ4                  | R6                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| DP2, IRQ5                  | U5                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| DP3, IRQ6                  | T5                                                                                                                                                               | Bidirectional<br>Three-state (3.3 V only)    |

| BR                         | F2                                                                                                                                                               | Bidirectional (3.3 V only)                   |

| BG                         | H5                                                                                                                                                               | Bidirectional (3.3 V only)                   |

| Name                   | Pin Number | Туре                                                      |

|------------------------|------------|-----------------------------------------------------------|

| IP_A1                  | N7         | Input (3.3 V only)                                        |

| IP_A2, IOIS16_A        | Т4         | Input (3.3 V only)                                        |

| IP_A3                  | N6         | Input (3.3 V only)                                        |

| IP_A4                  | U4         | Input (3.3 V only)                                        |

| IP_A5                  | P6         | Input (3.3 V only)                                        |

| IP_A6                  | N8         | Input (3.3 V only)                                        |

| IP_A7                  | тз         | Input (3.3 V only)                                        |

| DSCK                   | J3         | Bidirectional<br>Three-state (3.3 V only)                 |

| IWP[0:1], VFLS[0:1]    | J4, H2     | Bidirectional (3.3 V only)                                |

| OP0                    | L2         | Bidirectional (3.3 V only)                                |

| OP1                    | L3         | Output                                                    |

| OP2, MODCK1, STS       | L4         | Bidirectional (3.3 V only)                                |

| OP3, MODCK2, DSDO      | M2         | Bidirectional (3.3 V only)                                |

| BADDR[28:29]           | M4, M3     | Output                                                    |

| BADDR30, REG           | К4         | Output                                                    |

| ĀS                     | КЗ         | Input (3.3 V only)                                        |

| PA11, RXD3             | F17        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA10, TXD3             | J16        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA9, RXD4              | K17        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA8, TXD4              | K16        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA3, CLK5, BRGO3, TIN3 | L17        | Bidirectional<br>(5-V tolerant)                           |

| PA2, CLK6, TOUT3       | L15        | Bidirectional<br>(5-V tolerant)                           |

| PA1, CLK7, BRGO4, TIN4 | M16        | Bidirectional<br>(5-V tolerant)                           |

| PA0, CLK8, TOUT4       | N17        | Bidirectional<br>(5-V tolerant)                           |

#### Table 31. Pin Assignments—Non-JEDEC (continued)

| Name                 | Pin Number | Туре                                                      |

|----------------------|------------|-----------------------------------------------------------|

| PB31, SPISEL         | F14        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PB30, SPICLK         | G14        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PB29, SPIMOSI        | E16        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PB28, SPIMISO, BRGO4 | H14        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PB25, SMTXD1         | J15        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PB24, SMRXD1         | J17        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PB15, BRGO3          | M17        | Bidirectional<br>(5-V tolerant)                           |

| PC15, DREQ0          | D17        | Bidirectional<br>(5-V tolerant)                           |

| PC13, RTS3           | F15        | Bidirectional<br>(5-V tolerant)                           |

| PC12, RTS4           | F16        | Bidirectional<br>(5-V tolerant)                           |

| PC7, <u>CTS3</u>     | К15        | Bidirectional<br>(5-V tolerant)                           |

| PC6, CD3             | L16        | Bidirectional<br>(5-V tolerant)                           |

| PC5, CTS4, SDACK1    | К14        | Bidirectional<br>(5-V tolerant)                           |

| PC4, <u>CD4</u>      | M15        | Bidirectional<br>(5-V tolerant)                           |

| PD15, MII_RXD3       | N15        | Bidirectional<br>(5-V tolerant)                           |

| PD14, MII_RXD2       | P17        | Bidirectional<br>(5-V tolerant)                           |

| PD13, MII_RXD1       | L14        | Bidirectional<br>(5-V tolerant)                           |

#### Table 31. Pin Assignments—Non-JEDEC (continued)

#### Mechanical Data and Ordering Information

| Name                | Pin Number                                                                                                    | Туре                       |

|---------------------|---------------------------------------------------------------------------------------------------------------|----------------------------|

| V <sub>SSSYN1</sub> | R4                                                                                                            | PLL analog GND             |

| V <sub>DDSYN</sub>  | R3                                                                                                            | PLL analog V <sub>DD</sub> |

| GND                 | H7, H8, H9, H10, H11, H12, J7, J8, J9, J10, J11, J12, K7, K8, K9,<br>K10, K11, K12, L7, L8, L9, L10, L11, L12 | Power                      |

| V <sub>DDL</sub>    | B8, D2, E17, H16, M5, N3, T2, N16, U9                                                                         | Power                      |

| V <sub>DDH</sub>    | G6, G7, G8, G9, G10, G11, G12, G13, H6, H13, J6, J13, K6, K13,<br>L6, L13, M6, M7, M8, M9, M10, M11, M12, M13 | Power                      |

| N/C                 | B2, B17, C17, D16, E15, F13, M14, N5, R16, T17, U2, U17                                                       | No connect                 |

#### Table 31. Pin Assignments—Non-JEDEC (continued)