E·XF

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                            |

|---------------------------------|------------------------------------------------------------|

| Product Status                  | Active                                                     |

| Core Processor                  | -                                                          |

| Number of Cores/Bus Width       | -                                                          |

| Speed                           | -                                                          |

| Co-Processors/DSP               | -                                                          |

| RAM Controllers                 | -                                                          |

| Graphics Acceleration           | -                                                          |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | -                                                          |

| SATA                            | -                                                          |

| USB                             | -                                                          |

| Voltage - I/O                   | -                                                          |

| Operating Temperature           | -                                                          |

| Security Features               | -                                                          |

| Package / Case                  | -                                                          |

| Supplier Device Package         | -                                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc852tczt50a |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

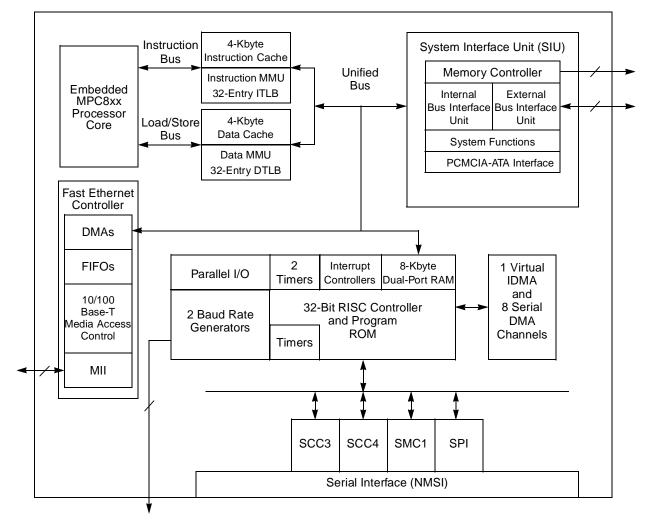

Figure 1. MPC852T Block Diagram

Power Supply and Power Sequencing

# 9 Power Supply and Power Sequencing

This section provides design considerations for the MPC852T power supply. The MPC852T has a core voltage ( $V_{DDL}$ ) and PLL voltage ( $V_{DDSYN}$ ) that operates at a lower voltage than the I/O voltage  $V_{DDH}$ . The I/O section of the MPC852T is supplied with 3.3 V across  $V_{DDH}$  and  $V_{SS}$  (GND).

The signals PA[0:3], PA[8:11], PB15, PB[24:25]; PB[28:31], PC[4:7], PC[12:13], PC15] PD[3:15], TDI, TDO, TCK, TRST, TMS, MII\_TXEN, MII\_MDIO are 5-V tolerant. All inputs cannot be more than 2.5 V greater than V<sub>DDH</sub>. In addition, 5-V tolerant pins can not exceed 5.5 V, and the remaining input pins cannot exceed 3.465 V. This restriction applies to power-on reset or power down and normal operation.

One consequence of multiple power supplies is that when power is initially applied, the voltage rails ramp up at different rates. The rates depend on the nature of the power supply, the type of load on each power supply, and the manner in which different voltages are derived. The following restrictions apply:

- $V_{DDL}$  must not exceed  $V_{DDH}$  during power-on reset or power down.

- V<sub>DDL</sub> must not exceed 1.9 V, and V<sub>DDH</sub> must not exceed 3.465.

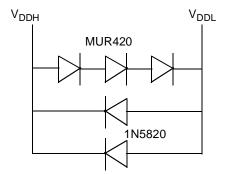

These cautions are necessary for the long-term reliability of the part. If they are violated, the electrostatic discharge (ESD) protection diodes are forward-biased, and excessive current can flow through these diodes. If the system power supply design does not control the voltage sequencing, the circuit shown in Figure 3 can be added to meet these requirements. The MUR420 Schottky diodes control the maximum potential difference between the external bus and core power supplies on power-on reset, and the 1N5820 diodes regulate the maximum potential difference on power-down.

Figure 3. Example Voltage Sequencing Circuit

# **10 Mandatory Reset Configurations**

The MPC852T requires a mandatory configuration during reset.

If hardware reset configuration word (HRCW) is enabled, by asserting the RSTCONF during HRESET assertion, the HRCW[DBGC] value that is needed to be set to binary X1 in the hardware reset configuration word (HRCW) and the SIUMCR[DBGC] should be programmed with the same value in the boot code after reset.

If hardware reset configuration word (HRCW) is disabled, by negating the  $\overline{\text{RSTCONF}}$  during the HRESET assertion, the SIUMCR[DBGC] should be programmed with binary X1 in the boot code after reset.

**Bus Signal Timing**

| Num  | Characteristic                                                                                                                                                                | 33    | MHz   | 40 1  | MHz   | 50 MHz |       | 66 MHz |       | 11:4 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--------|-------|--------|-------|------|

| Num  | Characteristic                                                                                                                                                                | Min   | Max   | Min   | Max   | Min    | Max   | Min    | Max   | Unit |

| B32a | CLKOUT falling edge to $\overline{\text{BS}}$ valid - as<br>requested by control bit BST1 in the<br>corresponding word in the UPM, EBDF = 0<br>(MAX = 0.25 × B1 + 6.80)       | 7.60  | 14.30 | 6.30  | 13.00 | 5.00   | 11.80 | 3.80   | 10.50 | ns   |

| B32b | CLKOUT rising edge to $\overline{\text{BS}}$ valid - as<br>requested by control bit BST2 in the<br>corresponding word in the UPM<br>(MAX = 0.00 × B1 + 8.00)                  | 1.50  | 8.00  | 1.50  | 8.00  | 1.50   | 8.00  | 1.50   | 8.00  | ns   |

| B32c | CLKOUT rising edge to $\overline{\text{BS}}$ valid - as<br>requested by control bit BST3 in the<br>corresponding word in the UPM<br>(MAX = 0.25 × B1 + 6.80)                  | 7.60  | 14.30 | 6.30  | 13.00 | 5.00   | 11.80 | 3.80   | 10.50 | ns   |

| B32d | CLKOUT falling edge to $\overline{\text{BS}}$ valid- as<br>requested by control bit BST1 in the<br>corresponding word in the UPM, EBDF = 1<br>(MAX = 0.375 × B1 + 6.60)       | 13.30 | 18.00 | 11.30 | 16.00 | 9.40   | 14.10 | 7.60   | 12.30 | ns   |

| B33  | CLKOUT falling edge to $\overline{\text{GPL}}$ valid - as<br>requested by control bit GxT4 in the<br>corresponding word in the UPM<br>(MAX = $0.00 \times \text{B1} + 6.00$ ) | 1.50  | 6.00  | 1.50  | 6.00  | 1.50   | 6.00  | 1.50   | 6.00  | ns   |

| B33a | CLKOUT rising edge to $\overline{\text{GPL}}$ Valid - as<br>requested by control bit GxT3 in the<br>corresponding word in the UPM<br>(MAX = $0.25 \times B1 + 6.80$ )         | 7.60  | 14.30 | 6.30  | 13.00 | 5.00   | 11.80 | 3.80   | 10.50 | ns   |

| B34  | A(0:31), BADDR(28:30), and D(0:31) to<br>$\overline{CS}$ valid - as requested by control bit<br>CST4 in the corresponding word in the<br>UPM (MIN = $0.25 \times B1 - 2.00$ ) | 5.60  | _     | 4.30  | _     | 3.00   | _     | 1.80   | _     | ns   |

| B34a | A(0:31), BADDR(28:30), and D(0:31) to<br>$\overline{CS}$ valid - as requested by control bit<br>CST1 in the corresponding word in the<br>UPM (MIN = $0.50 \times B1 - 2.00$ ) | 13.20 | _     | 10.50 | _     | 8.00   | _     | 5.60   | _     | ns   |

| B34b | A(0:31), BADDR(28:30), and D(0:31) to $\overline{CS}$ valid - as requested by CST2 in the corresponding word in UPM (MIN = $0.75 \times B1 - 2.00$ )                          | 20.70 | _     | 16.70 | _     | 13.00  | _     | 9.40   | _     | ns   |

| B35  | A(0:31), BADDR(28:30) to $\overline{CS}$ valid - as<br>requested by control bit BST4 in the<br>corresponding word in the UPM<br>(MIN = 0.25 × B1 - 2.00)                      | 5.60  | _     | 4.30  | _     | 3.00   | _     | 1.80   | _     | ns   |

| B35a | A(0:31), BADDR(28:30), and D(0:31) to<br>BS valid - As Requested by BST1 in the<br>corresponding word in the UPM<br>(MIN = $0.50 \times B1 - 2.00$ )                          | 13.20 | _     | 10.50 | —     | 8.00   | —     | 5.60   | _     | ns   |

## Table 9. Bus Operation Timings (continued)

| Num   | Characteristic                                                                                                                                                   | 33    | MHz | 40 M  | ИНz | 50 I  | MHz | 66 I | MHz | Unit |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----|-------|-----|------|-----|------|

| Nulli | Characteristic                                                                                                                                                   | Min   | Max | Min   | Max | Min   | Max | Min  | Max | Onit |

| B35b  | A(0:31), BADDR(28:30), and D(0:31) to<br>BS valid - as requested by control bit BST2<br>in the corresponding word in the UPM<br>(MIN = $0.75 \times B1 - 2.00$ ) | 20.70 | _   | 16.70 | _   | 13.00 | _   | 9.40 | _   | ns   |

| B36   | $A(0:31)$ , BADDR(28:30), and D(0:31) to GPL valid as requested by control bit GxT4 in the corresponding word in the UPM (MIN = $0.25 \times B1 - 2.00$ )        | 5.60  | _   | 4.30  | _   | 3.00  | _   | 1.80 | _   | ns   |

| B37   | UPWAIT valid to CLKOUT falling edge <sup>10</sup><br>(MIN = $0.00 \times B1 + 6.00$ )                                                                            | 6.00  |     | 6.00  |     | 6.00  | —   | 6.00 | —   | ns   |

| B38   | CLKOUT falling edge to UPWAIT valid <sup>10</sup><br>(MIN = $0.00 \times B1 + 1.00$ )                                                                            | 1.00  | _   | 1.00  | _   | 1.00  | —   | 1.00 | _   | ns   |

| B39   | $\overline{\text{AS}}$ valid to CLKOUT rising edge <sup>11</sup><br>(MIN = 0.00 × B1 + 7.00)                                                                     | 7.00  | _   | 7.00  | _   | 7.00  | —   | 7.00 | —   | ns   |

| B40   | A(0:31), TSIZ(0:1), RD/WR, BURST, valid<br>to CLKOUT rising edge<br>(MIN = $0.00 \times B1 + 7.00$ )                                                             | 7.00  | _   | 7.00  | _   | 7.00  | —   | 7.00 | —   | ns   |

| B41   | $\overline{\text{TS}}$ valid to CLKOUT rising edge (setup time) (MIN = 0.00 × B1 + 7.00)                                                                         | 7.00  | _   | 7.00  | _   | 7.00  | _   | 7.00 | _   | ns   |

| B42   | CLKOUT rising edge to $\overline{\text{TS}}$ valid (hold time) (MIN = 0.00 × B1 + 2.00)                                                                          | 2.00  | _   | 2.00  | _   | 2.00  | _   | 2.00 | —   | ns   |

| B43   | $\overline{\text{AS}}$ negation to memory controller signals negation (MAX = TBD)                                                                                | —     | TBD | _     | TBD | —     | TBD | —    | TBD | ns   |

#### Table 9. Bus Operation Timings (continued)

<sup>1</sup> If the rate of change of the frequency of EXTAL is slow (that is, it does not jump between the minimum and maximum values in one cycle) or the frequency of the jitter is fast (that is, it does not stay at an extreme value for a long time), then the maximum allowed jitter on EXTAL can be up to 2%.

<sup>2</sup> For part speeds above 50MHz, use 9.80ns for B11a.

<sup>3</sup> The timing required for BR input is relevant when the MPC852T is selected to work with internal bus arbiter. The timing for BG input is relevant when the MPC852T is selected to work with external bus arbiter.

<sup>4</sup> For part speeds above 50MHz, use 2ns for B17.

<sup>5</sup> The D(0:31) and DP(0:3) input timings B18 and B19 refer to the rising edge of the CLKOUT in which the TA input signal is asserted.

<sup>6</sup> For part speeds above 50MHz, use 2ns for B19.

- <sup>7</sup> The D(0:31) and DP(0:3) input timings B20 and B21 refer to the falling edge of the CLKOUT. This timing is valid only for read accesses controlled by chip-selects under control of the UPM in the memory controller, for data beats where DLT3 = 1 in the UPM RAM words. (This is only the case where data is latched on the falling edge of CLKOUT.)

- <sup>8</sup> This formula applies to bus operation up to 50 MHz.

- <sup>9</sup> The timing B30 refers to  $\overline{CS}$  when ACS = 00 and to  $\overline{WE}(0:3)$  when CSNT = 0.

- <sup>10</sup> The signal UPWAIT is considered asynchronous to the CLKOUT and synchronized internally. The timings specified in B37 and B38 are specified to enable the freeze of the UPM output signals as described in Figure 19.

- <sup>11</sup> The AS signal is considered asynchronous to the CLKOUT. The timing B39 is specified in order to allow the behavior specified in Figure 22.

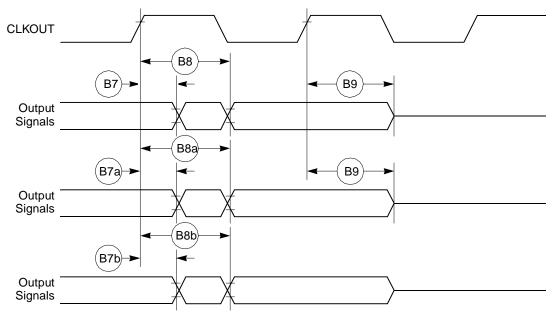

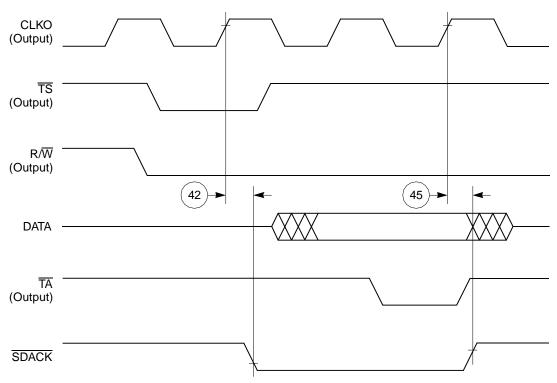

Figure 6 provides the timing for the synchronous output signals.

Figure 6. Synchronous Output Signals Timing

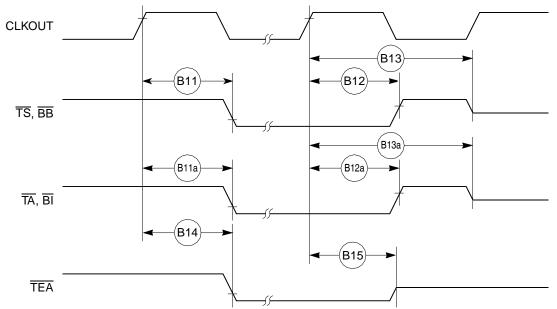

Figure 7 provides the timing for the synchronous active pull-up and open-drain output signals.

Figure 7. Synchronous Active Pull-Up Resistor and Open-Drain Outputs Signals Timing

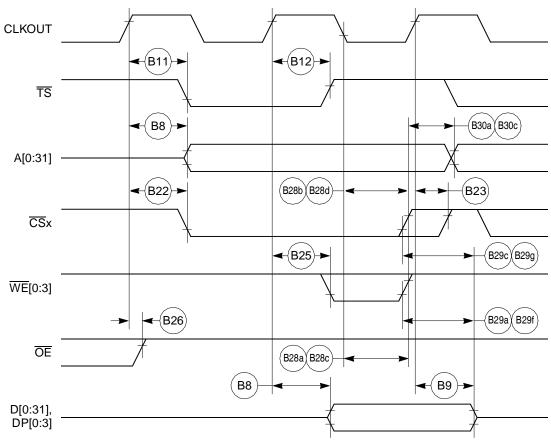

Figure 16. External Bus Write Timing (GPCM Controlled—TRLX = 0 or 1, CSNT = 1)

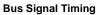

Bus Signal Timing

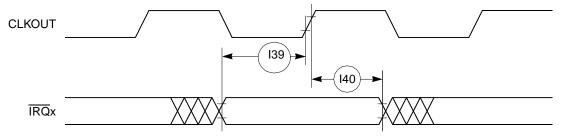

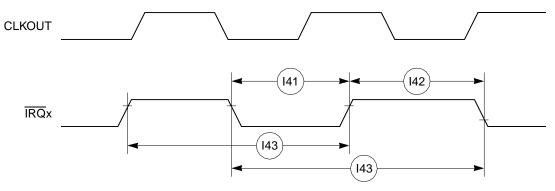

Table 10 provides interrupt timing for the MPC852T.

Table 10. Interrupt Timing

| Num   | Characteristic <sup>1</sup>                    | All Freq                | Unit |      |

|-------|------------------------------------------------|-------------------------|------|------|

| Nulli | Gharacteristic                                 | Min                     | Max  | Unit |

| 139   | IRQx valid to CLKOUT rising edge (set up time) | 6.00                    |      | ns   |

| 140   | IRQx hold time after CLKOUT                    | 2.00                    |      | ns   |

| 141   | IRQx pulse width low                           | 3.00                    |      | ns   |

| 142   | IRQx pulse width high                          | 3.00                    |      | ns   |

| 143   | IRQx edge-to-edge time                         | $4 \times T_{CLOCKOUT}$ |      | _    |

<sup>1</sup> The timings I39 and I40 describe the testing conditions under which the IRQ lines are tested when being defined as level-sensitive. The IRQ lines are synchronized internally and need not be asserted or negated with reference to the CLKOUT. The timings I41, I42, and I43 are specified to allow the correct function of the IRQ lines detection circuitry, and have no direct relation with the total system interrupt latency that the MPC852T is able to support.

Figure 24 provides the interrupt detection timing for the external level-sensitive lines.

Figure 24. Interrupt Detection Timing for External Level Sensitive Lines

Figure 25 provides the interrupt detection timing for the external edge-sensitive lines.

Figure 25. Interrupt Detection Timing for External Edge Sensitive Lines

Bus Signal Timing

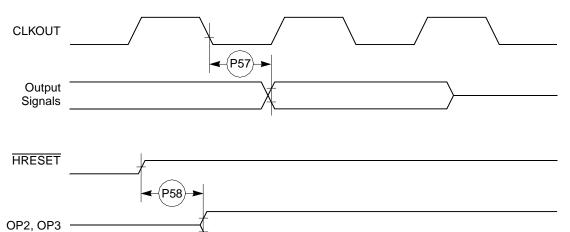

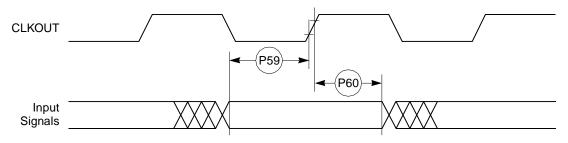

## Table 12 shows the PCMCIA port timing for the MPC852T.

Table 12. PCMCIA Port Timing

| Num | Characteristic                                                               | 33 MHz |       | 40 MHz |       | 50 MHz |       | 66 MHz |       | Unit |

|-----|------------------------------------------------------------------------------|--------|-------|--------|-------|--------|-------|--------|-------|------|

|     |                                                                              | Min    | Max   | Min    | Max   | Min    | Max   | Min    | Max   | onit |

| J95 | CLKOUT to OPx Valid<br>(MAX = 0.00 × B1 + 19.00)                             | _      | 19.00 | —      | 19.00 |        | 19.00 |        | 19.00 | ns   |

| J96 | HRESET negated to OPx drive <sup>1</sup><br>(MIN = $0.75 \times B1 + 3.00$ ) | 25.70  | _     | 21.70  | _     | 18.00  |       | 14.40  |       | ns   |

| J97 | IP_Xx valid to CLKOUT rising edge (MIN = $0.00 \times B1 + 5.00$ )           | 5.00   | —     | 5.00   | —     | 5.00   | _     | 5.00   | _     | ns   |

| J98 | CLKOUT rising edge to IP_Xx invalid<br>(MIN = $0.00 \times B1 + 1.00$ )      | 1.00   | _     | 1.00   | _     | 1.00   | _     | 1.00   | _     | ns   |

<sup>1</sup> OP2 and OP3 only.

## Figure 29 provides the PCMCIA output port timing for the MPC852T.

### Figure 29. PCMCIA Output Port Timing

Figure 30 provides the PCMCIA output port timing for the MPC852T.

Figure 30. PCMCIA Input Port Timing

#### **IEEE 1149.1 Electrical Specifications**

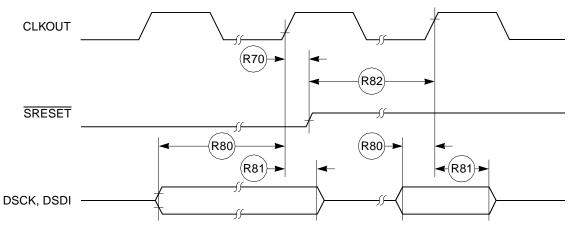

Figure 35 provides the reset timing for the debug port configuration.

Figure 35. Reset Timing—Debug Port Configuration

# 13 IEEE 1149.1 Electrical Specifications

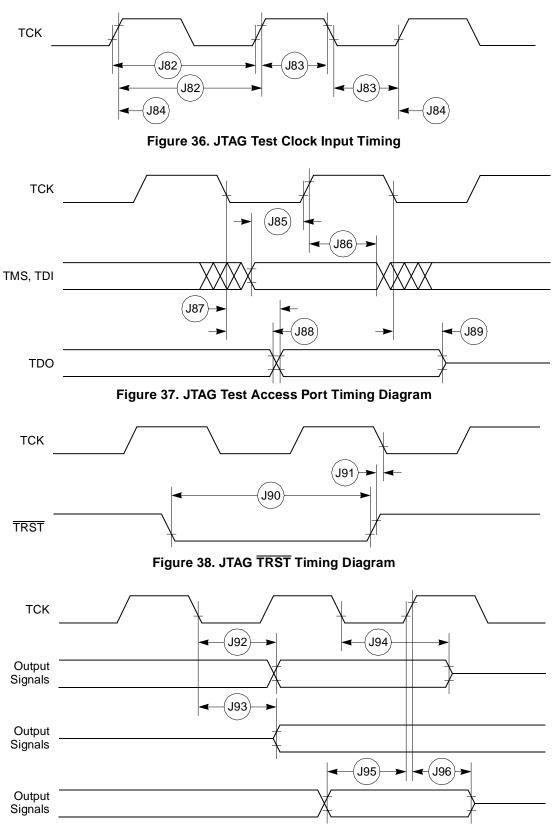

Table 15 provides the JTAG timings for the MPC852T shown in Figure 36 through Figure 39.

| Num | Characteristic                                         | All Freq | uencies | Unit |

|-----|--------------------------------------------------------|----------|---------|------|

| Num | Characteristic                                         | Min      | Мах     | Unit |

| J82 | TCK cycle time                                         | 100.00   |         | ns   |

| J83 | TCK clock pulse width measured at 1.5 V                | 40.00    | _       | ns   |

| J84 | TCK rise and fall times                                | 0.00     | 10.00   | ns   |

| J85 | TMS, TDI data setup time                               | 5.00     | _       | ns   |

| J86 | TMS, TDI data hold time                                | 25.00    | —       | ns   |

| J87 | TCK low to TDO data valid                              | —        | 27.00   | ns   |

| J88 | TCK low to TDO data invalid                            | 0.00     | —       | ns   |

| J89 | TCK low to TDO high impedance                          | _        | 20.00   | ns   |

| J90 | TRST assert time                                       | 100.00   | —       | ns   |

| J91 | TRST setup time to TCK low                             | 40.00    | —       | ns   |

| J92 | TCK falling edge to output valid                       | —        | 50.00   | ns   |

| J93 | TCK falling edge to output valid out of high impedance | —        | 50.00   | ns   |

| J94 | TCK falling edge to output high impedance              | —        | 50.00   | ns   |

| J95 | Boundary scan input valid to TCK rising edge           | 50.00    | —       | ns   |

| J96 | TCK rising edge to boundary scan input invalid         | 50.00    | —       | ns   |

| Table | 15. | <b>JTAG</b> | Timing |

|-------|-----|-------------|--------|

|-------|-----|-------------|--------|

Figure 39. Boundary Scan (JTAG) Timing Diagram

#### MPC852T PowerQUICC<sup>™</sup> Hardware Specifications, Rev. 4

**CPM Electrical Characteristics**

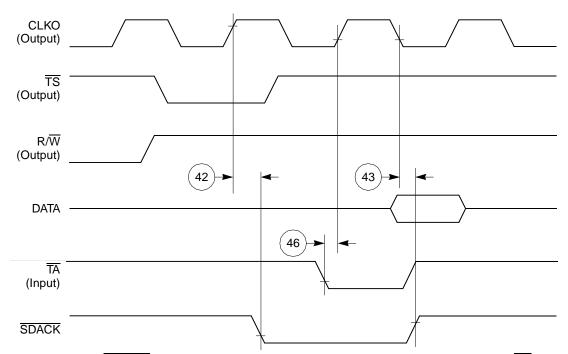

Figure 43. SDACK Timing Diagram—Peripheral Write, Internally-Generated TA

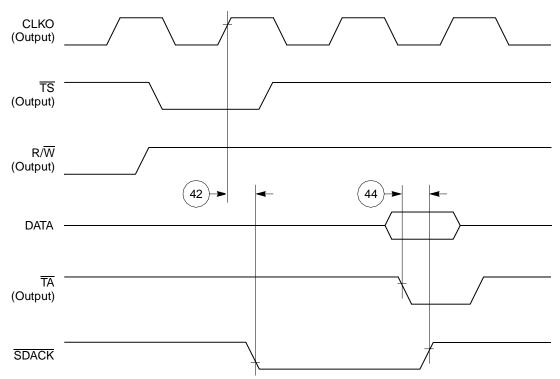

Figure 44. SDACK Timing Diagram—Peripheral Read, Internally-Generated TA

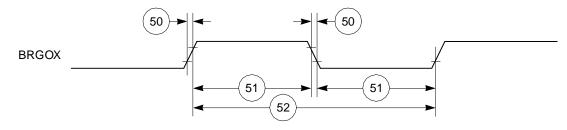

# **14.3 Baud Rate Generator AC Electrical Specifications**

Table 18 provides the baud rate generator timings as shown in Figure 45.

| Table 18 | . Baud | Rate | Generator | Timing |

|----------|--------|------|-----------|--------|

|----------|--------|------|-----------|--------|

| Num | Characteristic          | All Freq | Unit |    |

|-----|-------------------------|----------|------|----|

|     | Unardetensite           | Min      | Мах  | Om |

| 50  | BRGO rise and fall time | —        | 10   | ns |

| 51  | BRGO duty cycle         | 40       | 60   | %  |

| 52  | BRGO cycle              | 40       | _    | ns |

Figure 45. Baud Rate Generator Timing Diagram

MPC852T PowerQUICC<sup>™</sup> Hardware Specifications, Rev. 4

**CPM Electrical Characteristics**

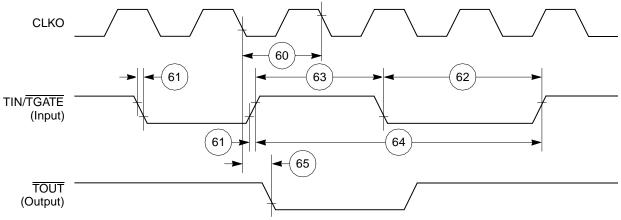

# 14.4 Timer AC Electrical Specifications

Table 19 provides the general-purpose timer timings as shown in Figure 46.

### Table 19. Timer Timing

| Num | Characteristic               | All Freq | Unit |      |

|-----|------------------------------|----------|------|------|

|     | Cildiacteristic              | Min      | Мах  | Unit |

| 61  | TIN/TGATE rise and fall time | 10       | _    | ns   |

| 62  | TIN/TGATE low time           | 1        | _    | clk  |

| 63  | TIN/TGATE high time          | 2        | _    | clk  |

| 64  | TIN/TGATE cycle time         | 3        | _    | clk  |

| 65  | CLKO low to TOUT valid       | 3        | 25   | ns   |

Figure 46. CPM General-Purpose Timers Timing Diagram

# 14.5 SCC in NMSI Mode Electrical Specifications

Table 20 provides the NMSI external clock timing.

| Table 20 | . NMSI | External | Clock | Timing |

|----------|--------|----------|-------|--------|

|----------|--------|----------|-------|--------|

| Num | Characteristic                                       | All Freque    | Unit  |      |

|-----|------------------------------------------------------|---------------|-------|------|

|     | Characteristic                                       | Min           | Мах   | Onit |

| 100 | RCLK3 and TCLK3 width high <sup>1</sup>              | 1/SYNCCLK     | _     | ns   |

| 101 | RCLK3 and TCLK3 width low                            | 1/SYNCCLK + 5 | _     | ns   |

| 102 | RCLK3 and TCLK3 rise/fall time                       | —             | 15.00 | ns   |

| 103 | TXD3 active delay (from TCLK3 falling edge)          | 0.00          | 50.00 | ns   |

| 104 | RTS3 active/inactive delay (from TCLK3 falling edge) | 0.00          | 50.00 | ns   |

| 105 | CTS3 setup time to TCLK3 rising edge                 | 5.00          | —     | ns   |

| 106 | RXD3 setup time to RCLK3 rising edge                 | 5.00          | _     | ns   |

MPC852T PowerQUICC<sup>™</sup> Hardware Specifications, Rev. 4

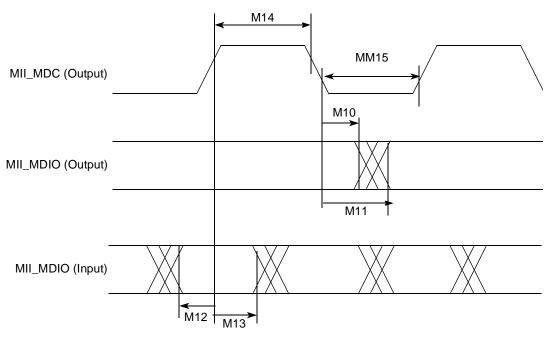

# 15.4 MII Serial Management Channel Timing (MII\_MDIO, MII\_MDC)

Table 28 provides information on the MII serial management channel signal timing. The FEC functions correctly with a maximum MDC frequency in excess of 2.5 MHz. The exact upper bound is under investigation.

| Num | Characteristic                                                              | Min | Мах | Unit           |

|-----|-----------------------------------------------------------------------------|-----|-----|----------------|

| M10 | MII_MDC falling edge to MII_MDIO output invalid (minimum propagation delay) | 0   | _   | ns             |

| M11 | MII_MDC falling edge to MII_MDIO output valid (max prop delay)              | _   | 25  | ns             |

| M12 | MII_MDIO (input) to MII_MDC rising edge setup                               | 10  | _   | ns             |

| M13 | MII_MDIO (input) to MII_MDC rising edge hold                                | 0   | _   | ns             |

| M14 | MII_MDC pulse width high                                                    | 40% | 60% | MII_MDC period |

| M15 | MII_MDC pulse width low                                                     | 40% | 60% | MII_MDC period |

Figure 62 shows the MII serial management channel timing diagram.

Figure 62. MII Serial Management Channel Timing Diagram

# 16.1.1 JEDEC Compliant Pinout

Figure 63 shows the JEDEC pinout of the PBGA package as viewed from the top surface. For additional information, see the *MPC866 PowerQUICC*<sup>TM</sup> *Family Reference Manual*.

$\bigcup_{\mathsf{CS7}} \ \bigcup_{\mathsf{GPL}\_\mathsf{A2}} \ \bigcup_{\mathsf{WE2}} \ \bigcup_{\mathsf{BS}\_\mathsf{A0}} \ \bigcup_{\mathsf{VDDL}}$ O A19 O A18 O A23 O A14 O A7 O A1 O N/C  $O_{CS1}$ O A28 O A2 А O N/C O A0 O A30 O A29 O A27 O A13 0 A9 O N/C  $\frac{O}{CS0}$ OCE2\_A OD WE3 MILCRS OD A3 O A22 O A6 В O A8 O A21  $O_{\overline{CS3}}$ O CS5 O A26 Ο Ο Ο Ο Ο Ο С A25 A17 A12 A3 N/C PC15 O PB29 O A20 O A4  $\frac{O}{CS6}$ O A31 OBI  $\frac{O}{CS2}$  $\bigcup_{WE0} \bigcup_{BS_A1}$ Ο Ο Ο Ο Ο OE D A24 A15 A10 N/C VDDL O TSIZ0 O PC12  $\bigcup_{TS}$ O GPL\_A5 CE\_1A O TSIZ1 O A16 O A11 O A5 O PB31 O PA11  $\bigcup_{BR}$  $O_{\text{TFA}}$  $O_{CS4}$ O N/C O PC13 Е O CR MIL\_COL О  $\bigcup_{BB}$  $O_{TA}$ Ο Ο Ο Ο Ο Ο Ο Ο  $\bigcirc$ O TDO Ο F PB30 TRST VFLS\_1 RSV OBURST O VDDL O O MDIO Ο Ο Ο Ο Ο Ο Ο Ο Ο G PB28 ALE\_A DSCK VFLS\_0 O FR7 Ο Ο Ο Ο О O PB25 O PA10 Ο Ο Ο Ο O PB24 н GND O BADDR30 O HRESET Ο Ο Ο Ο Ο Ο Ο Ο Ο Ο  $O_{\overline{KR}}$ Ο Ο J PC7 PC5 PA8 PA9 O OP1 Ο OP2 RSTCONF Ο Ο Ο Ο Ο Ο Ο Ο O PD13 O PA2 O PC6 О κ OP0 VDDH O PC4 O PA1 O PB15  $\bigcirc$ Ο Ο С Ο Ο Ο Ο Ο Ο Ο Ο O N/C L **OP3BADDR29 BADDR28** VDDL O D26 O D14 O D9 O IRQ1 O PD3 O PD8 O PD15 Ο Μ PÃ0 O D10 KTAL EXTCLK WAIT\_A VSSSYN IP\_A5 CLKOUT O D25 O D21 O D15 O D17 O IRQ7 O PD6 O PD9 O PD12 O PD14 Ν Ο Ο O D29 O D24 O D20 O D16 O D11 O D23 O D12 O PD4 O N/C O PD11 Ρ Ο Ο Ο Ο Ο Ο Ο Ο Ο Ο Ο Ο  $\bigcirc$ О  $\bigcirc$ С R IP\_A2 VDDL IP\_A7 D19 D13 D0 PD5 PD10 DP3 D31 D28 D6 D5 D2 D27 N/C O IP\_A0 O IP\_A4 O DP2  $O_{D30}$ Ω  $O_{D22}$  $O_{D18}$  $\sum_{3}$ P  $O_{N/C}$ B MILTXEN PD7 т UNC N/C  $\bigcup_{D4}$ 3 4 5 6 7 8 11 12 13 1 2 9 10 14 15 16 Figure 63. Pinout of PBGA Package—JEDEC Standard

NOTE: This is the top view of the device.

| Name                                | Pin Number             | Туре                       |  |

|-------------------------------------|------------------------|----------------------------|--|

| FRZ<br>IRQ6                         | H4                     | Bidirectional (3.3 V only) |  |

| IRQ0                                | P13                    | Input (3.3 V only)         |  |

| RQ1                                 | M11                    | Input (3.3 V only)         |  |

| M_TX_CLK<br>IRQ7                    | N12                    | Input (3.3 V only)         |  |

| CS[0:5]                             | B2, A2, D3, C3, E6, C4 | Output                     |  |

| CS6                                 | D4                     | Output                     |  |

| CS7                                 | A3                     | Output                     |  |

| WEO<br>BS_BO<br>IORD                | D6                     | Output                     |  |

| WE1<br>BS_B1<br>OWR                 | C6                     | Output                     |  |

| WE2<br>BS_B2<br>PCOE                | A5                     | Output                     |  |

| WE3<br>BS_B3<br>PCWE                | B5                     | Output                     |  |

| BS_A[0:3]                           | A6, D7, C7, B7         | Output                     |  |

| GPL_A0<br>GPL_B0                    | C5                     | Output                     |  |

| OE<br>GPL_A1<br>GPL_B1              | D5                     | Output                     |  |

| GPL_A[2:3]<br>GPL_B[2:3]<br>CS[2–3] | A4, B4                 | Output                     |  |

| JPWAITA<br>GPL_A4                   | C2                     | Bidirectional (3.3 V only) |  |

| GPL_A5                              | E4                     | Output                     |  |

| PORESET                             | P1                     | Input (3.3 V only)         |  |

| RSTCONF                             | К4                     | Input (3.3 V only)         |  |

| IRESET                              | J4                     | Open-drain                 |  |

| SRESET                              | M3                     | Open-drain                 |  |

| KTAL                                | N1                     | Analog Output              |  |

## Table 30. Pin Assignments—JEDEC Standard (continued)

| Name                | Pin Number | Туре                                                      |

|---------------------|------------|-----------------------------------------------------------|

| EXTAL               | M1         | Analog Input (1.8 V only)                                 |

| CLKOUT              | N6         | Output                                                    |

| EXTCLK              | N2         | Input (1.8 V only)                                        |

| ALE_A               | H1         | Output                                                    |

| CE1_A               | E5         | Output                                                    |

| CE2_A               | B3         | Output                                                    |

| WAIT_A              | N3         | Input (3.3 V only)                                        |

| IP_A0               | T2         | Input (3.3 V only)                                        |

| IP_A1               | M6         | Input (3.3 V only)                                        |

| IP_A2, IOIS16_A     | R3         | Input (3.3 V only)                                        |

| IP_A3               | M5         | Input (3.3 V only)                                        |

| IP_A4               | Т3         | Input (3.3 V only)                                        |

| IP_A5               | N5         | Input (3.3 V only)                                        |

| IP_A6               | M7         | Input (3.3 V only)                                        |

| IP_A7               | R2         | Input (3.3 V only)                                        |

| DSCK                | H2         | Bidirectional<br>Three-state (3.3 V only)                 |

| IWP[0:1], VFLS[0:1] | H3, G1     | Bidirectional (3.3 V only)                                |

| OP0                 | К1         | Bidirectional (3.3 V only)                                |

| OP1                 | К2         | Output                                                    |

| OP2, MODCK1, STS    | КЗ         | Bidirectional (3.3 V only)                                |

| OP3, MODCK2, DSDO   | L1         | Bidirectional (3.3 V only)                                |

| BADDR[28:29]        | L3, L2     | Output                                                    |

| BADDR30, REG        | J3         | Output                                                    |

| ĀS                  | J2         | Input (3.3 V only)                                        |

| PA11, RXD3          | E16        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA10, TXD3          | H15        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA9, RXD4 J16       |            | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

| PA8, TXD4           | J15        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |

## Table 30. Pin Assignments—JEDEC Standard (continued)

| Name                   | Pin Number | Type<br>Bidirectional<br>(5-V tolerant)                   |  |

|------------------------|------------|-----------------------------------------------------------|--|

| PA3, CLK5, BRGO3, TIN3 | K16        |                                                           |  |

| PA2, CLK6, TOUT3       | K14        | Bidirectional<br>(5-V tolerant)                           |  |

| PA1, CLK7, BRGO4, TIN4 | L15        | Bidirectional<br>(5-V tolerant)                           |  |

| PA0, CLK8, TOUT4       | M16        | Bidirectional<br>(5-V tolerant)                           |  |

| PB31, SPISEL           | E13        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |  |

| PB30, SPICLK           | F13        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |  |

| PB29, SPIMOSI          | D15        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |  |

| PB28, SPIMISO, BRGO4   | G13        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |  |

| PB25, SMTXD1           | H14        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |  |

| PB24, SMRXD1           | H16        | Bidirectional<br>(Optional: Open-drain)<br>(5-V tolerant) |  |

| PB15, BRGO3            | L16        | Bidirectional<br>(5-V tolerant)                           |  |

| PC15, DREQ0            | C16        | Bidirectional<br>(5-V tolerant)                           |  |

| PC13, RTS3             | E14        | Bidirectional<br>(5-V tolerant)                           |  |

| PC12, RTS4             | E15        | Bidirectional<br>(5-V tolerant)                           |  |

| PC7, <u>CTS3</u>       | J14        | Bidirectional<br>(5-V tolerant)                           |  |

| PC6, <u>CD3</u>        | K15        | Bidirectional<br>(5-V tolerant)                           |  |

| PC5, CTS4, SDACK1      | J13        | Bidirectional<br>(5-V tolerant)                           |  |

## Table 30. Pin Assignments—JEDEC Standard (continued)

**Mechanical Data and Ordering Information**

# 16.1.2 The non-JEDEC Pinout

Figure 64 shows the non-JEDEC pinout of the PBGA package as viewed from the top surface. For additional information, see the *PowerQUICC<sup>TM</sup> Family Reference Manual*.

$\bigcirc$  CS7  $\bigcirc$  GPL\_A2  $\bigcirc$  WE2  $\bigcirc$  BS\_A0  $\lor$  VDDL O A18 O A23 O A19 O A14 O A7 O A2 O A1 O N/C O N/C  $\frac{O}{CS1}$ O A28 в CE2\_A GPL\_A3 O O O BS\_A3 O A30 O A29 O A27 O A13 0 A9 O A6 O A0 O N/C  $\frac{O}{CS0}$ O A22 С  $O \over \text{GPL}_{A4}$  $\frac{O}{CS3}$  $\frac{O}{CS5}$ O GPL\_A0 Ο Ο O WE1 BS\_A2 Ο Ο Ο Ο Ο Ο Ο Ο D A21 A8 A3 N/C A26 A25 V<sub>DDL</sub> A17 A12 PC15 O A4 O N/C O PB29 OBI  $\frac{O}{CS2}$  $\frac{O}{CS6}$ O A31 O WE0 BS\_A1 Ο Ο Ο Ο O Ο Е A24 A20 A15 A10 VDDL O TS O = O = O = O = OO TSIZ0 O A16 O A11 O PB31 O PC13 O PC12 O TSIZ1  $\bigcup_{BR}$  $O_{\text{TEA}}$  $O_{CS4}$ O A5 O N/C O PA11 F O MII\_COL O BB O TMS Ο Ο Ο Ο  $O_{CR}$  $O_{TA}$ Ο Ο Ο Ο Ο Ο Ο G TDO PB30 TRST VFLS\_1 O BURST  $O_{BG}$ O Ο Ο Ο Ο Ο Ο Ο Ο  $\bigcirc$ Ο  $\bigcirc$ н PB28 VDDL MDIO ALE\_A DSCK VFLS\_0 O Ο Ο Ο Ο Ο O PA10 Ο Ο Ο О O PB25 O PB24 J GND O BADDR30 HRESET O PC5 O PC7 Ο O KR Ο Ο Ο Ο Ο Ο Ο  $\bigcirc$  $\bigcirc$ κ PA8 PA9 O OP1 OP2 RSTCONF Ο OP0 Ο Ο Ο Ο Ο Ο Ο O PD13 O PA2 O PC6 O PA3 L. V<sub>DDH</sub> OP3BADDR29 BADDR28 O PA1 O N/C O PC4 O PB15 Ο Ο Ο Ο Ο Ο Ο Ο Ο М V<sub>DDL</sub>  $\underset{V_{\text{DDL}}}{O}$ O PD8  $\underset{\mathsf{extal}}{\overset{}{\bigcup}} \; \underset{\mathsf{V}_{\mathsf{DDL}}}{\overset{}{\bigcup}} \; \underset{\overline{\mathsf{sreset}}}{\overset{}{\bigcup}} \; \underset{\mathsf{N/C}}{\overset{}{\bigcirc}}$ O O IP\_A3 IP\_A1 O D14 O D9 O IRQ1 O PD3 O PD15  $\bigcirc$ O IP\_A6 O D26 Ν PA0 O D21 O D15 O D10 O D17 KTAL EXTCLK WAIT\_A VSSSYN IP\_A5 CLKOUT O IRQ7 O PD6 O PD12 O D25 O PD9 O PD14 Р O D20 O D11 O D23 Ο O D16 O D12 О O D24 O D29 O PD4 O N/C O PD11 R PORST VDDSYN Ο Ο Ο Ο Ο Ο Ο Ο Ο Ο Ο Ο О Ο Ο Ο Т V<sub>DDL</sub> IP\_A7 IP\_A2 DP3 D31 D28 D19 D2 D27 D13 D0 PD5 PD10 N/C D6 D5 O O IP\_A0 ONC NC DP2 9 P  $Q_4$ U UNC NC  $O_{D30}$  $\bigcup_{D22}$  $O_{D18}$  $\bigcup_{3}$ D8 MIL\_TXEN PD7 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 Figure 64. Pinout of PBGA Package—Non-JEDEC

NOTE: This figure shows the top view of the device.

**Document Revision History**

## THIS PAGE INTENTIONALLY LEFT BLANK