Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Details                    |                                                                          |

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 6                                                                        |

| Program Memory Size        | 2KB (2K x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 8-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny202-ssnr |

# **Table of Contents**

| Int | roduct | tion                                                     | 1  |  |  |  |

|-----|--------|----------------------------------------------------------|----|--|--|--|

| Fe  | atures | S                                                        | 1  |  |  |  |

| 1.  | tinyA  | tinyAVR® 0-Series Overview                               |    |  |  |  |

|     | -      | Configuration Summary                                    |    |  |  |  |

| 2.  | Orde   | ering Information                                        | 11 |  |  |  |

|     | 2.1.   | ATtiny202                                                | 11 |  |  |  |

|     | 2.2.   | ATtiny402                                                |    |  |  |  |

| 3.  | Block  | k Diagram                                                | 12 |  |  |  |

| 4.  | Pino   | ut                                                       | 13 |  |  |  |

|     | 4.1.   | 8-Pin SOIC                                               | 13 |  |  |  |

| 5.  | I/O N  | //ultiplexing and Considerations                         | 14 |  |  |  |

|     | 5.1.   | Multiplexed Signals                                      |    |  |  |  |

| 6.  | Mem    | ories                                                    | 15 |  |  |  |

|     | 6.1.   | Overview                                                 |    |  |  |  |

|     | 6.2.   | Memory Map                                               |    |  |  |  |

|     | 6.3.   | In-System Reprogrammable Flash Program Memory            |    |  |  |  |

|     | 6.4.   | SRAM Data Memory                                         |    |  |  |  |

|     | 6.5.   | EEPROM Data Memory                                       |    |  |  |  |

|     | 6.6.   | User Row                                                 |    |  |  |  |

|     | 6.7.   | Signature Bytes                                          |    |  |  |  |

|     | 6.8.   | Memory Section Access from CPU and UPDI on Locked Device |    |  |  |  |

|     | 6.9.   | I/O Memory                                               | 19 |  |  |  |

|     | 6.10.  | Configuration and User Fuses (FUSE)                      | 22 |  |  |  |

| 7.  | Perip  | oherals and Architecture                                 | 41 |  |  |  |

|     | 7.1.   | Peripheral Module Address Map                            | 41 |  |  |  |

|     | 7.2.   | Interrupt Vector Mapping                                 | 42 |  |  |  |

|     | 7.3.   | System Configuration (SYSCFG)                            | 43 |  |  |  |

| 8.  | AVR    | CPU                                                      | 46 |  |  |  |

|     | 8.1.   | Features                                                 | 46 |  |  |  |

|     | 8.2.   | Overview                                                 |    |  |  |  |

|     | 8.3.   | Architecture                                             | 46 |  |  |  |

|     | 8.4.   | Arithmetic Logic Unit (ALU)                              | 48 |  |  |  |

|     | 8.5.   | Functional Description                                   | 49 |  |  |  |

|     | 8.6.   | Register Summary - CPU                                   | 54 |  |  |  |

|     | 8.7.   | Register Description                                     | 54 |  |  |  |

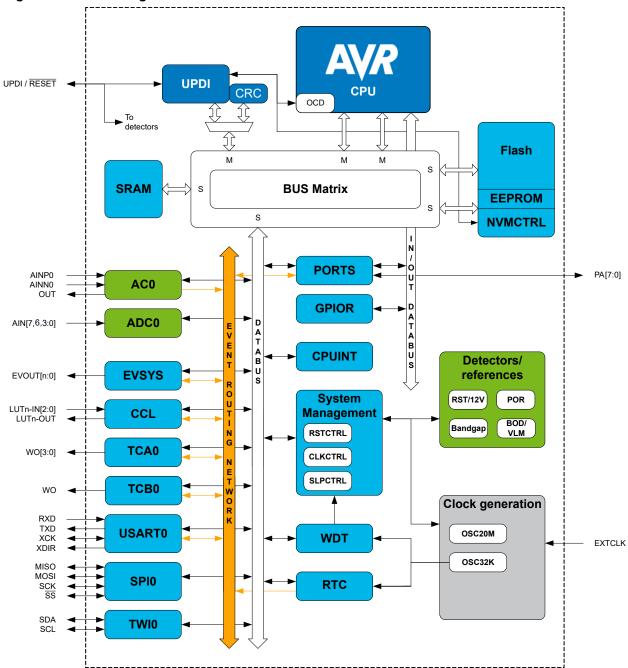

# 3. Block Diagram

Figure 3-1. Block Diagram

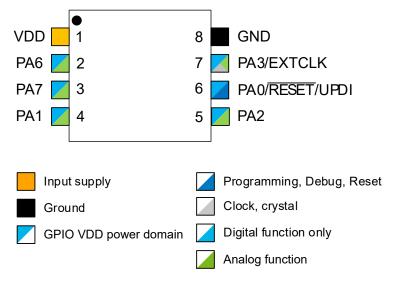

# 4. Pinout

## 4.1 8-Pin SOIC

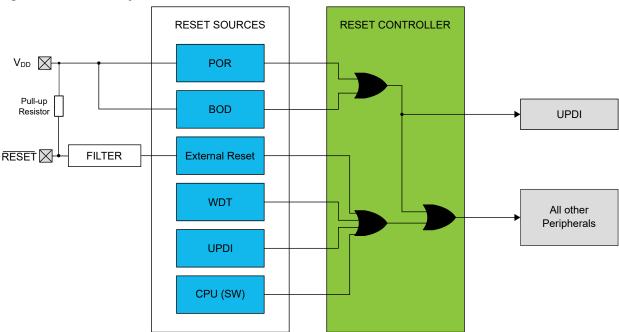

## 12. Reset Controller (RSTCTRL)

#### 12.1 Features

- Reset the device and set it to an initial state.

- Reset Flag register for identifying the Reset source in software.

- · Multiple Reset sources:

- Power supply Reset sources: Brown-out Detect (BOD), Power-on Reset (POR)

- User Reset sources: External Reset pin (RESET), Watchdog Reset (WDT), Software Reset (SW), and UPDI Reset.

## 12.2 Overview

The Reset Controller (RSTCTRL) manages the Reset of the device. It issues a device Reset, sets the device to its initial state, and allows the Reset source to be identified by software.

## 12.2.1 Block Diagram

Figure 12-1. Reset System Overview

#### 12.2.2 Signal Description

| Signal | Description                 | Туре          |

|--------|-----------------------------|---------------|

| RESET  | External Reset (active-low) | Digital input |

## Table 13-3. INTCTRL - Registers under Configuration Change Protection

| Register              | Key   |

|-----------------------|-------|

| IVSEL in CPUINT.CTRLA | IOREG |

| CVT in CPUINT.CTRLA   | IOREG |

## **Related Links**

Sequence for Write Operation to Configuration Change Protected I/O Registers

When an interrupt condition occurs, the corresponding interrupt flag is set in the Interrupt Flags register of the peripheral (peripheral.INTFLAGS).

An interrupt source is enabled or disabled by writing to the corresponding enable bit in the peripheral's Interrupt Control register (*peripheral*.INTCTRL).

An interrupt request is generated when the corresponding interrupt source is enabled and the interrupt flag is set. The interrupt request remains active until the interrupt flag is cleared. See the peripheral's INTFLAGS register for details on how to clear interrupt flags.

#### Related Links

**AVR CPU**

**SREG**

## 17.3.3 Sleep Mode Operation

There are two separate fuses defining the BOD configuration in different sleep modes; One fuse defines the mode used in Active mode and Idle Sleep mode (ACTIVE in FUSE.BODCFG), and is written to the ACTIVE bits in the Control A register (BOD.CTRLA). The second fuse (SLEEP in FUSE.BODCFG) selects the mode used in Standby Sleep mode and Power-Down Sleep mode, and is loaded into the SLEEP bits in the Control A register (BOD.CTRLA).

The operating mode in Active mode and Idle Sleep mode (i.e., ACTIVE in BOD.CTRLA) cannot be altered by software. The operating mode in Standby Sleep mode and Power-Down Sleep mode can be altered by writing to the SLEEP bits in the Control A register (BOD.CTRLA).

When the device is going into Standby Sleep mode or Power-Down Sleep mode, the BOD will change operation mode as defined by SLEEP in BOD.CTRLA. When the device is waking up from Standby or Power-Down Sleep mode, the BOD will operate in the mode defined by the ACTIVE bit field in BOD.CTRLA.

#### 17.3.4 Synchronization

Not applicable.

#### 17.3.5 Configuration Change Protection

This peripheral has registers that are under Configuration Change Protection (CCP). In order to write to these, a certain key must be written to the CPU.CCP register first, followed by a write access to the protected bits within four CPU instructions.

It is possible to try writing to these registers any time, but the values are not altered.

The following registers are under CCP:

Table 17-3. Registers Under Configuration Change Protection

| Register           | Key   |

|--------------------|-------|

| SLEEP in BOD.CTRLA | IOREG |

#### **Related Links**

Sequence for Write Operation to Configuration Change Protected I/O Registers

# ATtiny202/402 Voltage Reference (VREF)

respective Reference Select bit field (ADC0REFSEL, DAC0REFSEL) in the Control A register (VREF.CTRLA).

## 20.5.15 Period Register - Normal Mode

Name: PER

Offset: 0x26

Reset: 0xFFFF

Property: -

TCAn.PER contains the 16-bit TOP value in the timer/counter.

The TCAn.PERL and TCAn.PERH register pair represents the 16-bit value, TCAn.PER. The low byte [7:0] (suffix L) is accessible at the original offset. The high byte [15:8] (suffix H) can be accessed at offset + 0x01.

| Bit    | 15  | 14  | 13  | 12  | 11     | 10  | 9   | 8   |

|--------|-----|-----|-----|-----|--------|-----|-----|-----|

|        |     |     |     | PER | [15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 1   | 1   | 1   | 1   | 1      | 1   | 1   | 1   |

|        |     |     |     |     |        |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3      | 2   | 1   | 0   |

|        |     |     |     | PER | [7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 1   | 1   | 1   | 1   | 1      | 1   | 1   | 1   |

Bits 15:8 - PER[15:8] Periodic High Byte

These bits hold the MSB of the 16-bit period register.

## Bits 7:0 - PER[7:0] Periodic Low Byte

These bits hold the LSB of the 16-bit period register.

- Event 3: Clock period = 1024 RTC clock cycles

- Event 4: Clock period = 512 RTC clock cycles

- Event 5: Clock period = 256 RTC clock cycles

- Event 6: Clock period = 128 RTC clock cycles

- Event 7: Clock period = 64 RTC clock cycles

The event users are configured by the Event System (EVSYS).

#### Related Links

Event System (EVSYS)

## 22.6 Interrupts

#### Table 22-2. Available Interrupt Vectors and Sources

| Offset | Name | Vector Description                                     | Conditions                                                                                                                                                                       |  |

|--------|------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x00   | RTC  | Real-time counter overflow and compare match interrupt | <ul> <li>Overflow (OVF): The counter has reached its top value and wrapped to zero.</li> <li>Compare (CMP): Match between the counter value and the compare register.</li> </ul> |  |

| 0x02   | PIT  | Periodic Interrupt Timer interrupt                     | A time period has passed, as configured in RTC_PITCTRLA.PERIOD.                                                                                                                  |  |

When an interrupt condition occurs, the corresponding interrupt flag is set in the Interrupt Flags register of the peripheral (*peripheral*.INTFLAGS).

An interrupt source is enabled or disabled by writing to the corresponding enable bit in the peripheral's Interrupt Control register (*peripheral*.INTCTRL).

An interrupt request is generated when the corresponding interrupt source is enabled and the interrupt flag is set. The interrupt request remains active until the interrupt flag is cleared. See the peripheral's INTFLAGS register for details on how to clear interrupt flags.

#### **Related Links**

CPU Interrupt Controller (CPUINT)

**INTCTRL**

**PITINTCTRL**

## 22.7 Sleep Mode Operation

The RTC will continue to operate in Idle Sleep mode. It will run in Standby Sleep mode if the RUNSTDBY bit in RTC.CTRLA is set.

The PIT will continue to operate in any sleep mode.

#### **Related Links**

**CTRLA**

## 23.5.8 Control C - Async Mode

Name:

CTRLC

Offset:

0x07

Reset:

0x03

Property:

This register description is valid for all modes except Master SPI mode. When the USART Communication mode bits (CMODE) in this register are written to 'MSPI', see Control C - Master SPI Mode for the correct description.

| Bit    | 7   | 6       | 5    | 4       | 3      | 2   | 1           | 0   |

|--------|-----|---------|------|---------|--------|-----|-------------|-----|

|        | CMO | DE[1:0] | PMOD | DE[1:0] | SBMODE |     | CHSIZE[2:0] |     |

| Access | R/W | R/W     | R/W  | R/W     | R/W    | R/W | R/W         | R/W |

| Reset  | 0   | 0       | 0    | 0       | 0      | 0   | 1           | 1   |

#### Bits 7:6 - CMODE[1:0] USART Communication Mode

Writing these bits select the Communication mode of the USART.

Writing a 0x3 to these bits alters the available bit fields in this register, see Control C - Master SPI Mode.

| Value | Name         | Description            |

|-------|--------------|------------------------|

| 0x0   | ASYNCHRONOUS | Asynchronous USART     |

| 0x1   | SYNCHRONOUS  | Synchronous USART      |

| 0x2   | IRCOM        | Infrared Communication |

| 0x3   | MSPI         | Master SPI             |

## Bits 5:4 - PMODE[1:0] Parity Mode

Writing these bits enable and select the type of parity generation.

When enabled, the transmitter will automatically generate and send the parity of the transmitted data bits within each frame. The receiver will generate a parity value for the incoming data, compare it to the PMODE setting, and set the Parity Error flag (PERR) in the STATUS register (USARTn.STATUS) if a mismatch is detected.

| Value | Name     | Description          |

|-------|----------|----------------------|

| 0x0   | DISABLED | Disabled             |

| 0x1   | -        | Reserved             |

| 0x2   | EVEN     | Enabled, Even Parity |

| 0x3   | ODD      | Enabled, Odd Parity  |

#### Bit 3 - SBMODE Stop Bit Mode

Writing this bit selects the number of Stop bits to be inserted by the transmitter.

The receiver ignores this setting.

| Value | Description |

|-------|-------------|

| 0     | 1 Stop bit  |

| 1     | 2 Stop bits |

dedicated status flags for indicating ACK/NACK received, bus error, arbitration lost, clock hold, and bus state.

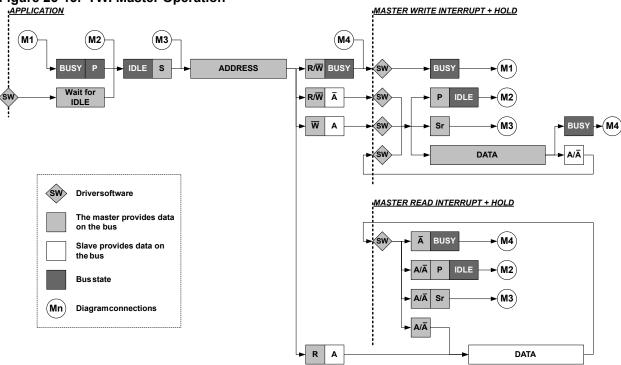

When an interrupt flag is set, the SCL line is forced low. This will give the master time to respond or handle any data, and will in most cases require software interaction. Figure 25-13 shows the TWI master operation. The diamond-shaped symbols (SW) indicate where software interaction is required. Clearing the interrupt flags releases the SCL line.

Figure 25-13. TWI Master Operation

The number of interrupts generated is kept to a minimum by an automatic handling of most conditions.

#### **Clock Generation**

The BAUD must be set to a value that results in a TWI bus clock frequency (f<sub>SCL</sub>) equal or less than 100 kHz/400 kHz/1 MHz, dependent on the mode used by the application (Standard mode Sm/Fast mode Fm/Fast mode plus Fm+).

The low ( $T_{LOW}$ ) and high ( $T_{HIGH}$ ) times are determined by the Baud Rate register (BAUD), while the rise ( $T_{RISE}$ ) and fall ( $T_{FALL}$ ) times are determined by the bus topology. Because of the wired-AND logic of the bus,  $T_{FALL}$  will be considered as part of  $T_{LOW}$ . Likewise,  $T_{RISE}$  will be in a state between  $T_{LOW}$  and  $T_{HIGH}$  until a high state has been detected.

#### Case S3: Collision

If the slave is not able to send a high level or NACK, the collision flag is set, and it will disable the data and acknowledge output from the slave logic. The clock hold is released. A Start or repeated Start condition will be accepted.

#### Case S4: STOP Condition Received

When the Stop condition is received, the slave address/stop flag will be set, indicating that a Stop condition, and not an address match, occurred.

#### **Receiving Data Packets**

The slave will know when an address packet with R/W direction bit cleared has been successfully received. After acknowledging this, the slave must be ready to receive data. When a data packet is received, the data interrupt flag is set and the slave must indicate ACK or NACK. After indicating a NACK, the slave must expect a Stop or repeated Start condition.

#### **Transmitting Data Packets**

The slave will know when an address packet with R/W direction bit set has been successfully received. It can then start sending data by writing to the slave data register. When a data packet transmission is completed, the data interrupt flag is set. If the master indicates NACK, the slave must stop transmitting data and expect a Stop or repeated Start condition.

#### 25.3.4.4 Smart Mode

The TWI interface has a Smart mode that simplifies application code and minimizes the user interaction needed to adhere to the I<sup>2</sup>C protocol. For TWI Master, Smart mode accomplishes this by automatically sending an ACK as soon as data register TWI.MDATA is read. This feature is only active when the ACKACT bit in TWIn.MCTRLA register is set to ACK. If ACKACT is set to NACK, the TWI Master will not generate a NACK bit followed by reading the Data register.

With Smart mode enabled for TWI Slave (SMEN bit in TWIn.SCTRLA), DIF (Data Interrupt Flag) will automatically be cleared if Data register (TWIn.SDATA) is read or written.

#### 25.3.5 Events

Not applicable.

#### 25.3.6 Interrupts

#### Table 25-2. Available Interrupt Vectors and Sources

| Offset | Name   | Vector Description   | Conditions                                                                                                               |  |

|--------|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| 0x00   | Slave  | TWI Slave interrupt  | <ul> <li>DIF: Data Interrupt Flag in SSTATUS set</li> <li>APIF: Address or Stop Interrupt Flag in SSTATUS set</li> </ul> |  |

| 0x02   | Master | TWI Master interrupt | <ul> <li>RIF: Read Interrupt Flag in MSTATUS set</li> <li>WIF: Write Interrupt Flag in MSTATUS set</li> </ul>            |  |

When an interrupt condition occurs, the corresponding interrupt flag is set in the Master register (TWI.MSTATUS) or Slave Status register (TWI.SSTATUS).

When several interrupt request conditions are supported by an interrupt vector, the interrupt requests are ORed together into one combined interrupt request to the interrupt controller. The user must read the peripheral's INTFLAGS register to determine which of the interrupt conditions are present.

#### **Related Links**

CPU Interrupt Controller (CPUINT)

**SREG**

#### 28.2.3.4 Events

The events of this peripheral are connected to the Event System.

#### 28.2.3.5 Debug Operation

This peripheral is unaffected by entering Debug mode.

If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during halted debugging.

## 28.3 Functional Description

#### 28.3.1 Initialization

For basic operation, follow these steps:

- Configure the desired input pins in the port peripheral

- Select the positive and negative input sources by writing the Positive and Negative Input MUX Selection bit fields (MUXPOS and MUXNEG) in the MUX Control A register (AC.MUXCTRLA)

- Optional: Enable the output to pin by writing a '1' to the Output Pad Enable bit (OUTEN) in the Control A register (AC.CTRLA)

- Enable the AC by writing a '1' to the ENABLE bit in AC.CTRLA

During the start-up time after enabling the AC, the output of the AC may be invalid.

The start-up time of the AC by itself is at most 2.5 µs. If an internal reference is used, the reference start-up time is normally longer than the AC start-up time. The VREF start-up time is 60 µs at most.

#### 28.3.2 Operation

#### 28.3.2.1 Input Hysteresis

Applying an input hysteresis helps to prevent constant toggling of the output when the noise-afflicted input signals are close to each other.

The input hysteresis can either be disabled or have one of three levels. The hysteresis is configured by writing to the Hysteresis Mode Select bit field (HYSMODE) in the Control A register (ACn.CTRLA).

## 28.3.2.2 Input Sources

The AC has one positive and one negative input. The inputs can be pins and internal sources, such as a voltage reference.

Each input is selected by writing to the Positive and Negative Input MUX Selection bit field (MUXPOS and MUXNEG) in the MUX Control A register (AC.MUXTRLA).

## **Pin Inputs**

The following Analog input pins on the port can be selected as input to the analog comparator

- AINN0

- AINP0

#### **Internal Inputs**

One internal input is available for the analog comparator:

· AC voltage reference

#### 28.3.2.3 Low-Power Mode

For power sensitive applications, the AC provides a Low-Power mode with reduced power consumption and increased propagation delay.

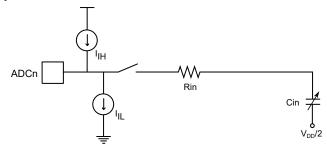

Figure 29-11. Analog Input Schematic

#### 29.3.2.5 ADC Conversion Result

After the conversion is complete (RESRDY is '1'), the conversion result RES is available in the ADC Result Register (ADCn.RES). The result for a 10-bit conversion is given as:

$$RES = \frac{1023 \times V_{IN}}{V_{REF}}$$

where  $V_{IN}$  is the voltage on the selected input pin and  $V_{REF}$  the selected voltage reference (see description for REFSEL in ADCn.CTRLC and ADCn.MUXPOS).

#### 29.3.2.6 Temperature Measurement

The temperature measurement is based on an on-chip temperature sensor. For a temperature measurement, follow these steps:

- 1. Configure the internal voltage reference to 1.1V by configuring the in VREF peripheral.

- 2. Select the internal voltage reference by writing the REFSEL bits in ADCn.CTRLC to 0x0.

- 3. Select the ADC temperature sensor channel by configuring the MUXPOS register (ADCn.MUXPOS). This enables the temperature sensor.

- 4. In ADCn.CTRLD Select INITDLY  $\geq$  32 µs  $\times f_{\text{CLK ADC}}$

- 5. In ADCn.SAMPCTRL Select SAMPLEN  $\geq$  32  $\mu$ s  $\times$   $f_{CLK}$  ADC

- 6. In ADCn.CTRLC Select SAMPCAP = 5 pF

- 7. Acquire the temperature sensor output voltage by starting a conversion.

- 8. Process the measurement result as described below.

The measured voltage has a linear relationship to the temperature. Due to process variations, the temperature sensor output voltage varies between individual devices at the same temperature. The individual compensation factors are determined during the production test and saved in the Signature Row:

- SIGROW.TEMPSENSE0 is a gain/slope correction

- SIGROW.TEMPSENSE1 is an offset correction

In order to achieve accurate results, the result of the temperature sensor measurement must be processed in the application software using factory calibration values. The temperature (in Kelvin) is calculated by this rule:

```

Temp = (((RESH << 8) | RESL) - TEMPSENSE1) * TEMPSENSE0) >> 8

```

RESH and RESL are the high and low byte of the Result register (ADCn.RES), and TEMPSENSEn are the respective values from the Signature row.

It is recommended to follow these steps in user code:

```

int8_t sigrow_offset = SIGROW.TEMPSENSE1; // Read signed value from signature row

uint8_t sigrow_gain = SIGROW.TEMPSENSE0; // Read unsigned value from signature row

```

#### 29.5.3 Control C

Name:

CTRLC

Offset:

0x02

Reset:

0x00

Property:

| Bit    | 7 | 6       | 5     | 4       | 3 | 2   | 1          | 0   |

|--------|---|---------|-------|---------|---|-----|------------|-----|

|        |   | SAMPCAP | REFSI | EL[1:0] |   |     | PRESC[2:0] |     |

| Access | R | R/W     | R/W   | R/W     | R | R/W | R/W        | R/W |

| Reset  | 0 | 0       | 0     | 0       | 0 | 0   | 0          | 0   |

## Bit 6 - SAMPCAP Sample Capacitance Selection

This bit selects the sample capacitance, and hence, the input impedance. The best value is dependent on the reference voltage and the application's electrical properties.

| Value | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| 0     | Recommended for reference voltage values below 1V.                               |

| 1     | Reduced size of sampling capacitance. Recommended for higher reference voltages. |

## Bits 5:4 - REFSEL[1:0] Reference Selection

These bits select the voltage reference for the ADC.

| Value | Name     | Description        |

|-------|----------|--------------------|

| 0x0   | INTERNAL | Internal reference |

| 0x1   | VDD      | $V_{DD}$           |

| Other | -        | Reserved.          |

## Bits 2:0 - PRESC[2:0] Prescaler

These bits define the division factor from the peripheral clock (CLK\_PER) to the ADC clock (CLK\_ADC).

| Value | Name   | Description            |

|-------|--------|------------------------|

| 0x0   | DIV2   | CLK_PER divided by 2   |

| 0x1   | DIV4   | CLK_PER divided by 4   |

| 0x2   | DIV8   | CLK_PER divided by 8   |

| 0x3   | DIV16  | CLK_PER divided by 16  |

| 0x4   | DIV32  | CLK_PER divided by 32  |

| 0x5   | DIV64  | CLK_PER divided by 64  |

| 0x6   | DIV128 | CLK_PER divided by 128 |

| 0x7   | DIV256 | CLK_PER divided by 256 |

## 29.5.6 Sample Control

Name: SAMPCTRL

Offset:

0x5

Reset:

0x00

Property:

| Bit    | / | 6 | 5 | 4            | 3   | 2   | 1   | 0   |  |

|--------|---|---|---|--------------|-----|-----|-----|-----|--|

|        |   |   |   | SAMPLEN[4:0] |     |     |     |     |  |

| Access |   |   |   | R/W          | R/W | R/W | R/W | R/W |  |

| Reset  |   |   |   | 0            | 0   | 0   | 0   | 0   |  |

## Bits 4:0 - SAMPLEN[4:0] Sample Length

These bits extend the ADC sampling length in a number of CLK\_ADC cycles. By default, the sampling time is two CLK\_ADC cycles. Increasing the sampling length allows sampling sources with higher impedance. The total conversion time increases with the selected sampling length.

Size A - Address size 0 0 Byte 0 1 Word (2 Bytes) 1 0 Reserved 1 Reserved Byte Word (2 Bytes) Reserved DATA SIZE Rх Adr\_0 Adr\_n Data\_0 Data\_n Τx ACK ACK ΔGT--ΔGT

Figure 30-10. STS Instruction Operation

The transfer protocol for an STS instruction is depicted in the figure as well, following this sequence:

- 1. The address is sent.

- 2. An Acknowledge (ACK) is sent back from the UPDI if the transfer was successful.

- 3. The number of bytes as specified in the STS instruction is sent.

- 4. A new ACK is received after the data has been successfully transferred.

## 30.3.3.3 LD - Load Data from Data Space Using Indirect Addressing

The LD instruction is used to load data from the bus matrix and into the serial shift register for serial readout. The LD instruction is based on indirect addressing, which means that the Address Pointer in the UPDI needs to be written prior to bus matrix access. Automatic pointer post-increment operation is supported and is useful when the LD instruction is used with REPEAT. It is also possible to do an LD of the UPDI Pointer register. The maximum supported size for address and data load is 16 bits.

## 30.5.5 ASI Key Status

Name: ASI\_KEY\_STATUS

Offset:

0x07

Reset:

0x00

Property:

| Bit    | 7 | 6 | 5         | 4       | 3         | 2 | 1 | 0 |

|--------|---|---|-----------|---------|-----------|---|---|---|

|        |   |   | UROWWRITE | NVMPROG | CHIPERASE |   |   |   |

| Access |   |   | R         | R       | R         |   |   |   |

| Reset  |   |   | 0         | 0       | 0         |   |   |   |

#### Bit 5 - UROWWRITE User Row Write Key Status

This bit is set to '1' if the UROWWRITE KEY is active. Otherwise, this bit reads as zero.

#### Bit 4 – NVMPROG NVM Programming

This bit is set to '1' if the NVMPROG KEY is active. This bit is automatically reset after the programming sequence is done. Otherwise, this bit reads as zero.

#### Bit 3 - CHIPERASE Chip Erase

This bit is set to '1' if the CHIPERASE KEY is active. This bit will automatically be reset when the Chip Erase sequence is completed. Otherwise, this bit reads as zero.

2. CPU in Standby mode.

## 31.7 BOD and POR Characteristics

## Table 31-8. Power Supply Characteristics

| Symbol | Description    | Condition | Min. | Тур. | Max. | Unit |

|--------|----------------|-----------|------|------|------|------|

| SRON   | Power-on Slope |           | -    | -    | 100  | V/ms |

## Table 31-9. Power-On Reset (POR) Characteristics

| Symbol | Description                                      | Condition                                        | Min. | Тур. | Max. | Unit |

|--------|--------------------------------------------------|--------------------------------------------------|------|------|------|------|

| VPOR   | POR threshold voltage on V <sub>DD</sub> falling | V <sub>DD</sub> falls/rises at 0.5V/ms or slower | 0.8  | -    | 1.6  | V    |

|        | POR threshold voltage on V <sub>DD</sub> rising  |                                                  | 1.4  | -    | 1.8  |      |

## Table 31-10. Brown-Out Detection (BOD) Characteristics

| Symbol             | Description                           | Condition                               | Min. | Тур. | Max.                                            | Unit |

|--------------------|---------------------------------------|-----------------------------------------|------|------|-------------------------------------------------|------|

| VBOD               | BOD triggering level (falling/rising) | BODLEVEL7                               | 3.9  | 4.2  | 4.5                                             | V    |

|                    |                                       | BODLEVEL2                               | 2.4  | 2.6  | 2.9                                             |      |

|                    | BODLEVEL0                             | BODLEVEL0                               | 1.7  | 1.8  | 2.0                                             |      |

| VINT               | Interrupt level 0                     | Percentage above the selected BOD level | -    | 4    | -                                               | %    |

|                    | Interrupt level 1                     |                                         | -    | 13   | -                                               |      |

|                    | Interrupt level 2                     |                                         | -    | 25   | 4.5<br>2.9<br>2.0                               |      |

| VHYS               | Hysteresis                            | BODLEVEL7                               | -    | 80   | 2.9<br>2.0<br>-<br>-<br>-<br>-<br>-<br>-        | mV   |

|                    |                                       | BODLEVEL2                               | -    | 40   | -                                               |      |

|                    |                                       | BODLEVEL0                               | -    | 25   | 4.5<br>2.9<br>2.0<br>-<br>-<br>-<br>-<br>-      |      |

| TBOD               | Detection time                        | Continuous                              | -    | 7    | -                                               | μs   |

|                    |                                       | Sampled, 1 kHz -                        |      | 1    | -                                               | ms   |

|                    |                                       | Sampled, 125 Hz                         | -    | 8    | 4.5<br>2.9<br>2.0<br>-<br>-<br>-<br>-<br>-<br>- |      |

| T <sub>start</sub> | Start-up time                         | Time from enable to ready               | -    | 40   | -                                               | μs   |

## 31.8 External Reset Characteristics

## **Table 31-11. External Reset Characteristics**

| Mode                 | Description                                | Condition | Min.                | Тур. | Max.                 | Unit |

|----------------------|--------------------------------------------|-----------|---------------------|------|----------------------|------|

| V <sub>HVRST</sub>   | RESET pin threshold for high-voltage Reset |           | 11.5                | -    | 12.5                 | V    |

| V <sub>RST_VIH</sub> | Input high-voltage for RESET               |           | 0.8×V <sub>DD</sub> | -    | V <sub>DD</sub> +0.2 |      |

| V <sub>RST_VIL</sub> | Input low-voltage for RESET                |           | -0.2                | -    | $0.2 \times V_{DD}$  |      |

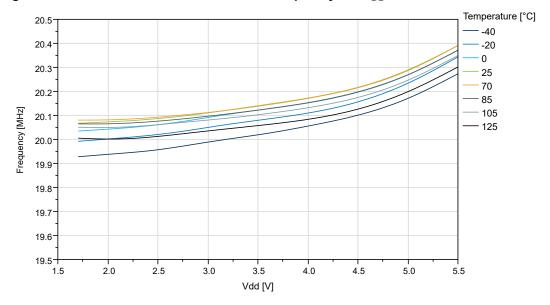

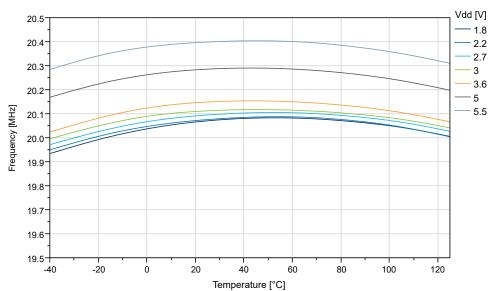

Figure 32-59. OSC20M Internal Oscillator: Frequency vs. Temperature

Figure 32-60. OSC20M Internal Oscillator: Frequency vs. V<sub>DD</sub>