Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

|                            |                                                                                 |

| Product Status             | Obsolete                                                                        |

| Core Processor             | F <sup>2</sup> MC-8FX                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, UART/USART                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 45                                                                              |

| Program Memory Size        | 60KB (60K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1.98K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                     |

| Data Converters            | A/D 12x8/10b                                                                    |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 52-LQFP                                                                         |

| Supplier Device Package    | 52-LQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f398kpmc1-g-sne2 |

### On-chip debug

- 1-wire serial control

- Serial writing supported (asynchronous mode)

#### Hardware/software watchdog timer

- Built-in hardware watchdog timer

- Built-in software watchdog timer

### Low-voltage detection reset circuit

■ Built-in low-voltage detector

#### **Clock supervisor counter**

■ Built-in clock supervisor counter function

#### Programmable port input voltage level

■ CMOS input level / hysteresis input level

#### **Dual operation Flash memory**

■ The erase/write operation and the read operation can be executed in different banks (upper bank/lower bank) simultaneously.

#### Flash memory security function

■ Protects the content of the Flash memory

| Part number                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------|--------------------|---------------------|--|--|--|--|

|                                                    | MB95F394H                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MB95F396H                                                   | MB95F398H                                                                                | MB95F394K           | MB95F396K          | MB95F398K           |  |  |  |  |

| Parameter                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

| Ì                                                  | 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

| UART/SIO                                           | <ul> <li>Data transfer with UART/SIO is enabled.</li> <li>It has a full duplex double buffer, variable data length (5/6/7/8 bits), a built-in baud rate generator and an error detection function.</li> <li>It uses the NRZ type transfer format.</li> <li>LSB-first data transfer and MSB-first data transfer are available to use.</li> <li>Clock-asynchronous (UART) serial data transfer and clock-synchronous (SIO) serial data transfer is enabled.</li> </ul> |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

|                                                    | 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

| l <sup>2</sup> C                                   | <ul> <li>It has the follow</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |                                                                                          |                     |                    | detection function, |  |  |  |  |

|                                                    | 3 channels                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

| 8/16-bit PPG                                       | <ul> <li>The counter ope</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  | rating clock can be                                         | as two 8-bit PPG ch<br>selected from eight                                               |                     | 16-bit PPG channel |                     |  |  |  |  |

| 16-bit PPG                                         | <ul><li>The counter ope</li><li>It supports exteri</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                         | nal trigger start.                                          | e available to use.<br>selected from eight<br>er with the multi-pul                      |                     |                    |                     |  |  |  |  |

| 16-bit reload timer                                | <ul><li>It can output squ</li><li>Count clock: it ca</li><li>Two counter ope</li></ul>                                                                                                                                                                                                                                                                                                                                                                               | are waveform.<br>an be selected from<br>rating modes: reloa | perating modes are<br>internal clocks (se<br>ad mode and one-sl<br>er with the multi-pul | ven types) and exte | ernal clocks.      |                     |  |  |  |  |

| Multi-pulse<br>generator (for DC<br>motor control) | <ul> <li>It can work independently or together with the multi-pulse generator.</li> <li>16-bit PPG timer: 1 channel</li> <li>16-bit reload timer operations: toggle output, one-shot output</li> <li>Event counter: 1 channel</li> <li>Waveform sequencer (including a 16-bit timer equipped with a buffer and a compare clear function)</li> </ul>                                                                                                                  |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

| Watch prescaler                                    | Eight different time                                                                                                                                                                                                                                                                                                                                                                                                                                                 | intervals can be se                                         | elected.                                                                                 |                     | -                  |                     |  |  |  |  |

| Flash memory                                       | <ul> <li>It supports automatic programming, Embedded Algorithm, and write/erase/erase-suspend/erase-resume commands.</li> <li>It has a flag indicating the completion of the operation of Embedded Algorithm.</li> <li>Number of write/erase cycles: 100000</li> <li>Data retention time: 20 years</li> <li>Flash security feature for protecting the content of the Flash memory</li> </ul>                                                                         |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

| Standby mode                                       | Sleep mode, stop r                                                                                                                                                                                                                                                                                                                                                                                                                                                   | node, watch mode,                                           | time-base timer mo                                                                       | ode                 |                    |                     |  |  |  |  |

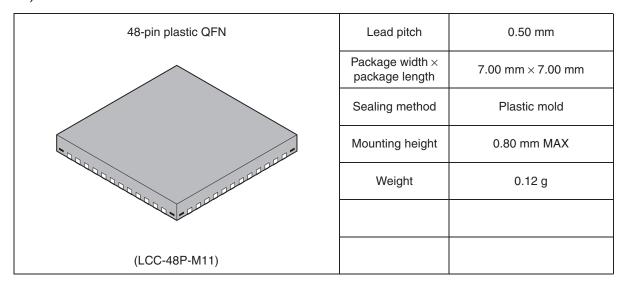

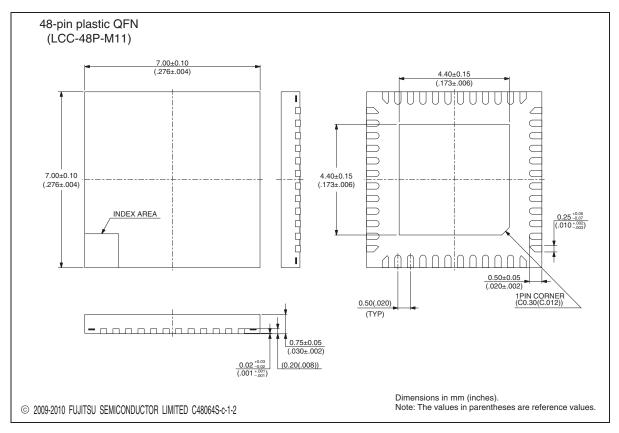

| Package                                            | FPT-48P-M49 FPT-52P-M02 LCC-48P-M11                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |                                                                                          |                     |                    |                     |  |  |  |  |

## 5. Pin Functions

|          | Pin no.             |          | Pin             | .1/0                          |                                                                                     |  |

|----------|---------------------|----------|-----------------|-------------------------------|-------------------------------------------------------------------------------------|--|

| LQFP48*1 | QFN48* <sup>2</sup> | LQFP52*3 | name            | circuit<br>type* <sup>4</sup> | Function                                                                            |  |

|          |                     |          | PG2             |                               | General-purpose I/O port                                                            |  |

| 1        | 1                   | 1        | X1A C           |                               | Subclock I/O oscillation pin                                                        |  |

|          | ·                   | ·        | SNI2            |                               | Trigger input pin for the position detection function of the MPG waveform sequencer |  |

|          |                     |          | PG1             |                               | General-purpose I/O port                                                            |  |

| 2        | 2                   | 2        | X0A             | С                             | Subclock input oscillation pin                                                      |  |

| _        | _                   | _        | SNI1            |                               | Trigger input pin for the position detection function of the MPG waveform sequencer |  |

| 3        | 3                   | 3        | V <sub>CC</sub> | _                             | Power supply pin                                                                    |  |

| 4        | 4                   | 4        | С               | _                             | Capacitor connection pin                                                            |  |

| 5        | 5                   | 5        | P40             | K                             | General-purpose I/O port                                                            |  |

| 5        | 5                   | 5        | AN08            |                               | A/D converter analog input pin                                                      |  |

| 6        | 6                   | 6        | P41             | K                             | General-purpose I/O port                                                            |  |

| 0        | 0                   | 0        | AN09            |                               | A/D converter analog input pin                                                      |  |

| _        | _                   | 7        | NC              | _                             | It is an internally connected pin. Always leave it unconnected.                     |  |

| 7        | 7                   | 0        | P42             | K                             | General-purpose I/O port                                                            |  |

| 7        | 7                   | 8        | AN10            |                               | A/D converter analog input pin                                                      |  |

| 8        | 8                   | 9        | P43             | V                             | General-purpose I/O port                                                            |  |

| 0        | 0                   | 9        | AN11            | K                             | A/D converter analog input pin                                                      |  |

| 9        | 9                   | 10       | P44             | G                             | General-purpose I/O port                                                            |  |

| 9        | 9                   | 10       | TO1             |                               | 16-bit reload timer ch. 0 output pin                                                |  |

| 10       | 10                  | 11       | P45             | G                             | General-purpose I/O port                                                            |  |

| 10       | 10                  | 11       | SCK             |                               | LIN-UART clock I/O pin                                                              |  |

| 11       | 11                  | 12       | P46             | G                             | General-purpose I/O port                                                            |  |

| 11       | 11                  | 12       | SOT             | 6                             | LIN-UART data output pin                                                            |  |

| 12       | 12                  | 13       | P47             | J                             | General-purpose I/O port                                                            |  |

| 12       | 12                  | 13       | SIN             |                               | LIN-UART data input pin                                                             |  |

| 13       | 13                  | 14       | P10             | G                             | General-purpose I/O port                                                            |  |

| 15       | 13                  | 14       | PPG10           |                               | 8/16-bit PPG ch. 1 output pin                                                       |  |

| 14       | 14                  | 15       | P11             | G                             | General-purpose I/O port                                                            |  |

| 14       | 14                  | 13       | PPG11           |                               | 8/16-bit PPG ch. 1 output pin                                                       |  |

| 15       | 15                  | 16       | P12             | Н                             | General-purpose I/O port                                                            |  |

| າວ       | 10                  | 10       | DBG             |                               | DBG input pin                                                                       |  |

| 16       | 16                  | 17       | P13             | G                             | General-purpose I/O port                                                            |  |

| 10       | 10                  | 17       | PPG00           | 9                             | 8/16-bit PPG ch. 0 output pin                                                       |  |

|          | Pin no.             |          | Pin   | I/O                           |                                                                                     |

|----------|---------------------|----------|-------|-------------------------------|-------------------------------------------------------------------------------------|

| LQFP48*1 | QFN48* <sup>2</sup> | LQFP52*3 | name  | circuit<br>type* <sup>4</sup> | Function                                                                            |

| 47       | 47                  | 40       | P14   | _                             | General-purpose I/O port                                                            |

| 17       | 17                  | 18       | PPG01 | G                             | 8/16-bit PPG ch. 0 output pin                                                       |

| 10       | 10                  | 10       | P15   | G                             | General-purpose I/O port                                                            |

| 18       | 18                  | 19       | PPG20 | G                             | 8/16-bit PPG ch. 2 output pin                                                       |

| _        | _                   | 20       | NC    | _                             | It is an internally connected pin. Always leave it unconnected.                     |

| 19       | 19                  | 21       | P16   | G                             | General-purpose I/O port                                                            |

| 19       | 19                  | 21       | PPG21 | ]                             | 8/16-bit PPG ch. 2 output pin                                                       |

|          |                     |          | P17   |                               | General-purpose I/O port                                                            |

| 20       | 20                  | 22       | SNI0  | G                             | Trigger input pin for the position detection function of the MPG waveform sequencer |

| 21       | 21                  | 23       | P70   | G                             | General-purpose I/O port                                                            |

| 21       | 21                  | 23       | TO00  | G                             | 8/16-bit composite timer ch. 0 output pin                                           |

| 22       | 22                  | 24       | P71   | G                             | General-purpose I/O port                                                            |

| 22       | 22                  | 24       | TO01  | J                             | 8/16-bit composite timer ch. 0 output pin                                           |

| 23       | 23                  | 25       | P72   |                               | General-purpose I/O port                                                            |

| 25       | 23                  | 23       | SCL   | '                             | I <sup>2</sup> C clock I/O pin                                                      |

| 24       | 24                  | 26       | P73   |                               | General-purpose I/O port                                                            |

| 24       | <u> </u>            | 20       | SDA   | '                             | I <sup>2</sup> C data I/O pin                                                       |

| 25       | 25                  | 27       | P74   | G                             | General-purpose I/O port                                                            |

| 20       |                     | 21       | EC0   | Ŭ                             | 8/16-bit composite timer ch. 0 clock input pin                                      |

| 26       | 26                  | 28       | P75   | G                             | General-purpose I/O port                                                            |

| 20       |                     | 20       | UCK0  | J                             | UART/SIO ch. 0 clock I/O pin                                                        |

| 27       | 27                  | 29       | P76   | G                             | General-purpose I/O port                                                            |

|          |                     |          | UO0   |                               | UART/SIO ch. 0 data output pin                                                      |

| 28       | 28                  | 30       | P77   | J                             | General-purpose I/O port                                                            |

|          |                     |          | UI0   |                               | UART/SIO ch. 0 data input pin                                                       |

| 29       | 29                  | 31       | P60   | G                             | General-purpose I/O port                                                            |

|          |                     |          | DTTI  |                               | MPG waveform sequencer input pin                                                    |

| 30       | 30                  | 32       | P61   | G                             | General-purpose I/O port                                                            |

|          |                     |          | TI1   |                               | 16-bit reload timer ch. 0 input pin                                                 |

| _        | _                   | 33       | NC    | _                             | It is an internally connected pin. Always leave it unconnected.                     |

|          |                     |          | P62   |                               | General-purpose I/O port<br>High-current pin                                        |

| 31       | 31                  | 34       | OPT0  | D                             | MPG waveform sequencer output pin                                                   |

|          |                     |          | PPG00 |                               | 8/16-bit PPG ch. 0 output pin                                                       |

|          |                     |          | TO10  |                               | 8/16-bit composite timer ch. 1 output pin                                           |

| Address           | Register abbreviation | Register name                                                               | R/W | Initial value         |

|-------------------|-----------------------|-----------------------------------------------------------------------------|-----|-----------------------|

| 0060 <sub>H</sub> | IBCR00                | I <sup>2</sup> C bus control register 0                                     | R/W | 00000000 <sub>B</sub> |

| 0061 <sub>H</sub> | IBCR10                | I <sup>2</sup> C bus control register 1                                     |     | 00000000 <sub>B</sub> |

| 0062 <sub>H</sub> | IBCR0                 | I <sup>2</sup> C bus status register                                        | R/W | 00000000 <sub>B</sub> |

| 0063 <sub>H</sub> | IDDR0                 | I <sup>2</sup> C data register                                              | R/W | 00000000 <sub>B</sub> |

| 0064 <sub>H</sub> | IAAR0                 | I <sup>2</sup> C address register                                           | R/W | 00000000 <sub>B</sub> |

| 0065 <sub>H</sub> | ICCR0                 | I <sup>2</sup> C clock control register                                     | R/W | 00000000 <sub>B</sub> |

| 0066 <sub>H</sub> | OPCUR                 | Output control register (upper)                                             | R/W | 00000000 <sub>B</sub> |

| 0067 <sub>H</sub> | OPCLR                 | Output control register (lower)                                             | R/W | 00000000 <sub>B</sub> |

| 0068 <sub>H</sub> | IPCUR                 | Input control register (upper)                                              | R/W | 00000000 <sub>B</sub> |

| 0069 <sub>H</sub> | IPCLR                 | Input control register (lower)                                              | R/W | 00000000 <sub>B</sub> |

| 006A <sub>H</sub> | NCCR                  | Noise cancellation control register                                         | R/W | 00000000 <sub>B</sub> |

| 006B <sub>H</sub> | TCSR                  | Timer control status register                                               | R/W | 00000000 <sub>B</sub> |

| 006C <sub>H</sub> | ADC1                  | 8/10-bit A/D converter control register 1                                   | R/W | 00000000 <sub>B</sub> |

| 006D <sub>H</sub> | ADC2                  | 8/10-bit A/D converter control register 2                                   | R/W | 00000000 <sub>B</sub> |

| 006E <sub>H</sub> | ADDH                  | 8/10-bit A/D converter data register (upper)                                | R/W | 00000000 <sub>B</sub> |

| 006F <sub>H</sub> | ADDL                  | 8/10-bit A/D converter data register (lower)                                | R/W | 00000000 <sub>B</sub> |

| 0070 <sub>H</sub> | _                     | (Disabled)                                                                  |     | _                     |

| 0071 <sub>H</sub> | FSR2                  | Flash memory status register 2                                              | R/W | 00000000 <sub>B</sub> |

| 0072 <sub>H</sub> | FSR                   | Flash memory status register                                                | R/W | 000X0000 <sub>B</sub> |

| 0073 <sub>H</sub> | SWRE0                 | Flash memory sector write control register 0                                | R/W | 00000000 <sub>B</sub> |

| 0074 <sub>H</sub> | FSR3                  | Flash memory status register 3                                              | R   | 00000000 <sub>B</sub> |

| 0075 <sub>H</sub> | _                     | (Disabled)                                                                  |     | _                     |

| 0076 <sub>H</sub> | WREN                  | Wild register address compare enable register                               | R/W | 00000000 <sub>B</sub> |

| 0077 <sub>H</sub> | WROR                  | Wild register data test setting register                                    | R/W | 00000000 <sub>B</sub> |

| 0078 <sub>H</sub> | _                     | Mirror of register bank pointer (RP) and mirror of direct bank pointer (DP) | _   | _                     |

| 0079 <sub>H</sub> | ILR0                  | Interrupt level setting register 0                                          | R/W | 11111111 <sub>B</sub> |

| 007A <sub>H</sub> | ILR1                  | Interrupt level setting register 1                                          | R/W | 11111111 <sub>B</sub> |

| 007B <sub>H</sub> | ILR2                  | Interrupt level setting register 2                                          | R/W | 11111111 <sub>B</sub> |

| 007C <sub>H</sub> | ILR3                  | Interrupt level setting register 3                                          |     | 11111111 <sub>B</sub> |

| 007D <sub>H</sub> | ILR4                  | Interrupt level setting register 4                                          |     | 11111111 <sub>B</sub> |

| 007E <sub>H</sub> | ILR5                  | Interrupt level setting register 5                                          |     | 11111111 <sub>B</sub> |

| 007F <sub>H</sub> | _                     | (Disabled)                                                                  | _   | _                     |

| 0F80 <sub>H</sub> | WRARH0                | Wild register address setting register (upper) ch. 0                        | R/W | 00000000 <sub>B</sub> |

| 0F81 <sub>H</sub> | WRARL0                | Wild register address setting register (lower) ch. 0                        | R/W | 00000000 <sub>B</sub> |

| 0F82 <sub>H</sub> | WRDR0                 | Wild register data setting register ch. 0                                   | R/W | 00000000 <sub>B</sub> |

# 13. Interrupt Source Table

|                                                                               |                                | Vector tab        | le address        |                                              | Priority order of                                                       |

|-------------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|----------------------------------------------|-------------------------------------------------------------------------|

| Interrupt source                                                              | Interrupt<br>request<br>number | Upper             | Lower             | Bit name of interrupt level setting register | interrupt sources<br>of the same level<br>(occurring<br>simultaneously) |

| External interrupt ch. 0, ch. 4                                               | IRQ00                          | FFFA <sub>H</sub> | FFFB <sub>H</sub> | L00 [1:0]                                    | High                                                                    |

| External interrupt ch. 1, ch. 5                                               | IRQ01                          | FFF8 <sub>H</sub> | FFF9 <sub>H</sub> | L01 [1:0]                                    | <b>A</b>                                                                |

| External interrupt ch. 2, ch. 6                                               | IRQ02                          | FFF6 <sub>H</sub> | FFF7 <sub>H</sub> | L02 [1:0]                                    |                                                                         |

| External interrupt ch. 3, ch. 7                                               | IRQ03                          | FFF4 <sub>H</sub> | FFF5 <sub>H</sub> | L03 [1:0]                                    |                                                                         |

| UART/SIO ch. 0, MPG (DTTI)                                                    | IRQ04                          | FFF2 <sub>H</sub> | FFF3 <sub>H</sub> | L04 [1:0]                                    |                                                                         |

| 8/16-bit composite timer ch. 0 (lower)                                        | IRQ05                          | FFF0 <sub>H</sub> | FFF1 <sub>H</sub> | L05 [1:0]                                    |                                                                         |

| 8/16-bit composite timer ch. 0 (upper)                                        | IRQ06                          | FFEE <sub>H</sub> | FFEF <sub>H</sub> | L06 [1:0]                                    |                                                                         |

| LIN-UART (reception)                                                          | IRQ07                          | FFEC <sub>H</sub> | FFED <sub>H</sub> | L07 [1:0]                                    |                                                                         |

| LIN-UART (transmission)                                                       | IRQ08                          | FFEA <sub>H</sub> | FFEB <sub>H</sub> | L08 [1:0]                                    |                                                                         |

| 8/16-bit PPG ch. 1 (lower)                                                    | IRQ09                          | FFE8 <sub>H</sub> | FFE9 <sub>H</sub> | L09 [1:0]                                    |                                                                         |

| 8/16-bit PPG ch. 1 (upper)                                                    | IRQ10                          | FFE6 <sub>H</sub> | FFE7 <sub>H</sub> | L10 [1:0]                                    |                                                                         |

| 8/16-bit PPG ch. 2 (upper)                                                    | IRQ11                          | FFE4 <sub>H</sub> | FFE5 <sub>H</sub> | L11 [1:0]                                    |                                                                         |

| 8/16-bit PPG ch. 0 (upper)                                                    | IRQ12                          | FFE2 <sub>H</sub> | FFE3 <sub>H</sub> | L12 [1:0]                                    |                                                                         |

| 8/16-bit PPG ch. 0 (lower)                                                    | IRQ13                          | FFE0 <sub>H</sub> | FFE1 <sub>H</sub> | L13 [1:0]                                    |                                                                         |

| 8/16-bit composite timer ch. 1 (upper)                                        | IRQ14                          | FFDE <sub>H</sub> | FFDF <sub>H</sub> | L14 [1:0]                                    |                                                                         |

| 8/16-bit PPG ch. 2 (lower)                                                    | IRQ15                          | FFDC <sub>H</sub> | FFDD <sub>H</sub> | L15 [1:0]                                    |                                                                         |

| 16-bit reload timer ch. 1, MPG (write timing/compare clear), I <sup>2</sup> C | IRQ16                          | FFDA <sub>H</sub> | FFDB <sub>H</sub> | L16 [1:0]                                    |                                                                         |

| 16-bit PPG timer ch. 1, MPG (position detection/compare match)                | IRQ17                          | FFD8 <sub>H</sub> | FFD9 <sub>H</sub> | L17 [1:0]                                    |                                                                         |

| 8/10-bit A/D converter                                                        | IRQ18                          | FFD6 <sub>H</sub> | FFD7 <sub>H</sub> | L18 [1:0]                                    |                                                                         |

| Time-base timer                                                               | IRQ19                          | FFD4 <sub>H</sub> | FFD5 <sub>H</sub> | L19 [1:0]                                    |                                                                         |

| Watch prescaler                                                               | IRQ20                          | FFD2 <sub>H</sub> | FFD3 <sub>H</sub> | L20 [1:0]                                    |                                                                         |

| _                                                                             | IRQ21                          | FFD0 <sub>H</sub> | FFD1 <sub>H</sub> | L21 [1:0]                                    |                                                                         |

| 8/16-bit composite timer ch. 1 (lower)                                        | IRQ22                          | FFCE <sub>H</sub> | FFCF <sub>H</sub> | L22 [1:0]                                    |                                                                         |

| Flash memory                                                                  | IRQ23                          | FFCC <sub>H</sub> | FFCD <sub>H</sub> | L23 [1:0]                                    | •                                                                       |

|                                                                               |                                |                   |                   |                                              | Low                                                                     |

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| D                                  | 0hl                                               | Di              | 0                                                                              |     | Value |      | 11!4 |         |

|------------------------------------|---------------------------------------------------|-----------------|--------------------------------------------------------------------------------|-----|-------|------|------|---------|

| Parameter                          | Symbol                                            | Pin name        | Condition                                                                      | Min | Typ*3 | Max  | Unit | Remarks |

|                                    | I <sub>CCTS</sub> V <sub>CC</sub> (External clock |                 | $V_{CC}$ = 5.5 V<br>$F_{CH}$ = 32 MHz<br>Time-base timer mode<br>$T_A$ = +25°C | _   | 0.9   | 3    | mA   |         |

|                                    | I <sub>CCH</sub>                                  | operation)      | $V_{CC}$ = 5.5 V<br>Substop mode<br>$T_A$ = +25°C                              | _   | 3.4   | 22.5 | μΑ   |         |

| Power supply current* <sup>2</sup> | I <sub>LVD</sub>                                  |                 | Current consumption for<br>low-voltage detection<br>circuit only               | _   | 31    | 54   | μΑ   |         |

|                                    | I <sub>CRH</sub>                                  | V <sub>CC</sub> | Current consumption for the main CR oscillator                                 | _   | 0.5   | 0.6  | mA   |         |

|                                    | I <sub>CRL</sub>                                  |                 | Current consumption for<br>the sub-CR oscillator<br>oscillating at 100 kHz     | _   | 20    | 72   | μА   |         |

<sup>\*1:</sup> The input levels of P47, P72, P73 and P77 can be switched between "CMOS input level" and "hysteresis input level". The input level selection register (ILSR) is used to switch between the two input levels.

- See "AC Characteristics: Clock Timing" for  $F_{CH}$  and  $F_{CL}$ .

- See "AC Characteristics: Source Clock/Machine Clock" for F<sub>MP</sub> and F<sub>MPI</sub> .

<sup>\*2: •</sup> The power supply current is determined by the external clock. When the low-voltage detection option is selected, the power-supply current will be the sum of adding the current consumption of the low-voltage detection circuit (I<sub>LVD</sub>) to one of the value from I<sub>CC</sub> to I<sub>CCH</sub>. In addition, when both the low-voltage detection option and the CR oscillator are selected, the power supply current will be the sum of adding up the current consumption of the low-voltage detection circuit, the current consumption of the CR oscillators (I<sub>CRH</sub>, I<sub>CRL</sub>) and a specified value. In on-chip debug mode, the CR oscillator (I<sub>CRH</sub>) and the low-voltage detection circuit are always enabled, and current consumption therefore increases accordingly.

<sup>\*3:</sup>  $V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}$

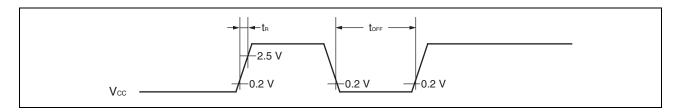

#### 14.4.4 Power-on Reset

$(V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                | Symbol           | Condition | Va  | lue | Unit  | Remarks                  |

|--------------------------|------------------|-----------|-----|-----|-------|--------------------------|

| Faranietei               | Symbol           | Condition | Min | Max | Oilit | Kemarks                  |

| Power supply rising time | t <sub>R</sub>   | _         | _   | 50  | ms    |                          |

| Power supply cutoff time | t <sub>OFF</sub> | _         | 1   | _   | ms    | Wait time until power-on |

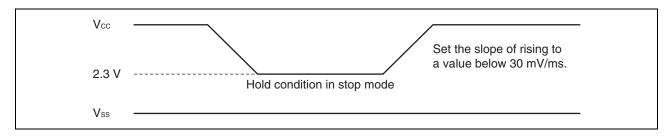

**Note:** A sudden change of power supply voltage may activate the power-on reset function. When changing the power supply voltage during the operation, set the slope of rising to a value below within 30 mV/ms as shown below.

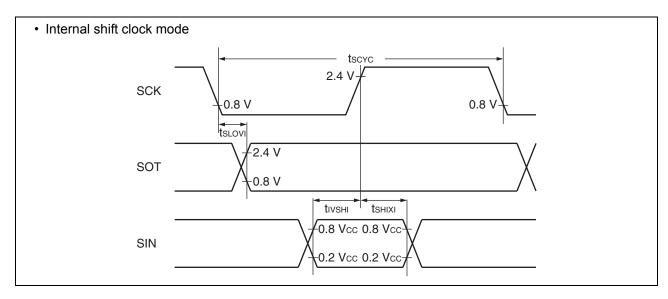

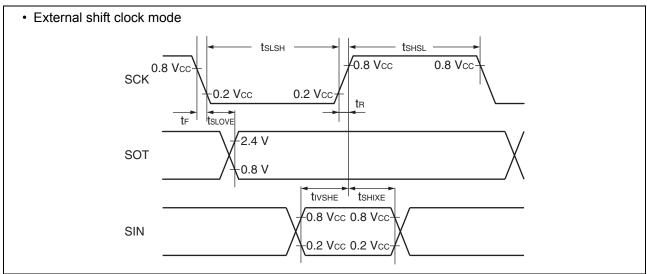

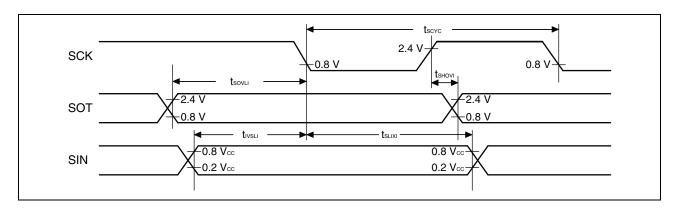

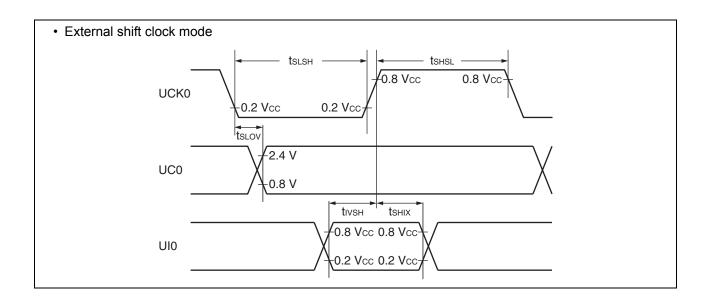

Sampling is executed at the rising edge of the sampling  $\operatorname{clock}^{*1}$ , and serial  $\operatorname{clock}$  delay is enabled\*2. (ESCR register: SCES bit = 0, ECCR register: SCDE bit = 1)

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                                         | Symbol             | Pin name   | Pin name Condition             |                            | Value                  |      |  |

|---------------------------------------------------|--------------------|------------|--------------------------------|----------------------------|------------------------|------|--|

| raiailletei                                       | Symbol             | Fill flame | Condition                      | Min                        | Max                    | Unit |  |

| Serial clock cycle time                           | t <sub>SCYC</sub>  | SCK        |                                | 5 t <sub>MCLK</sub> *3     | _                      | ns   |  |

| $SCK \uparrow \to SOT \ delay\ time$              | t <sub>SHOVI</sub> | SCK, SOT   | Internal clock                 | <b>-95</b>                 | +95                    | ns   |  |

| $Valid\;SIN\toSCK\;\!\downarrow$                  | t <sub>IVSLI</sub> | SCK, SIN   | operation output pin:          | t <sub>MCLK</sub> *3 + 190 | _                      | ns   |  |

| $SCK \downarrow \to valid \; SIN \; hold \; time$ | t <sub>SLIXI</sub> | SCK, SIN   | C <sub>L</sub> = 80 pF + 1 TTL | 0                          | _                      | ns   |  |

| $SOT \to SCK \downarrow delay \; time$            | t <sub>SOVLI</sub> | SCK, SOT   |                                | _                          | 4 t <sub>MCLK</sub> *3 | ns   |  |

- \*1: There is a function used to choose whether the sampling of reception data is performed at a rising edge or a falling edge of the serial clock.

- \*2: The serial clock delay function is a function that delays the output signal of the serial clock for half clock.

- \*3: See "Source Clock/Machine Clock" for t<sub>MCLK</sub>.

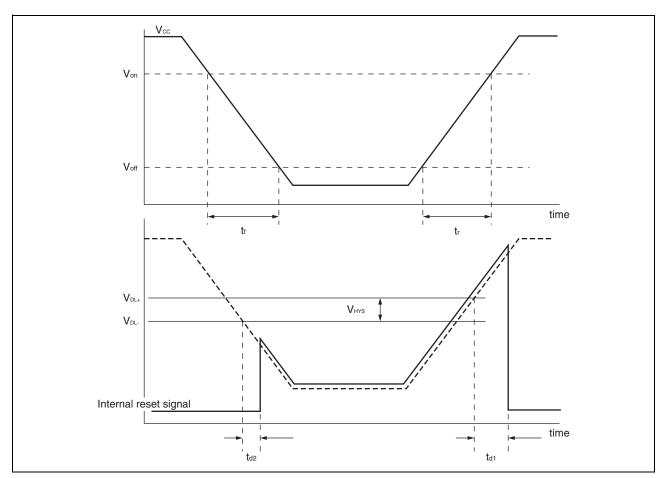

### 14.4.7 Low-voltage Detection

$(V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                                               | Cymbol           |      | Value |      | Unit  | Remarks                                                                                               |

|---------------------------------------------------------|------------------|------|-------|------|-------|-------------------------------------------------------------------------------------------------------|

| rarameter                                               | Symbol           | Min  | Тур   | Max  | Ullit | Remarks                                                                                               |

| Release voltage                                         | $V_{DL+}$        | 2.52 | 2.7   | 2.88 | V     | At power supply rise                                                                                  |

| Detection voltage                                       | $V_{DL}$         | 2.42 | 2.6   | 2.78 | V     | At power supply fall                                                                                  |

| Hysteresis width                                        | V <sub>HYS</sub> | 70   | 100   | _    | mV    |                                                                                                       |

| Power supply start voltage                              | V <sub>off</sub> | _    | _     | 2.3  | V     |                                                                                                       |

| Power supply end voltage                                | V <sub>on</sub>  | 4.9  | _     | _    | V     |                                                                                                       |

| Power supply voltage change time (at power supply rise) | t <sub>r</sub>   | 3000 | _     | _    | μs    | Slope of power supply that the reset release signal generates within the rating (V <sub>DL+</sub> )   |

| Power supply voltage change time (at power supply fall) | t <sub>f</sub>   | 300  | _     | _    | μs    | Slope of power supply that the reset detection signal generates within the rating (V <sub>DL</sub> .) |

| Reset release delay time                                | t <sub>d1</sub>  | _    | _     | 300  | μs    |                                                                                                       |

| Reset detection delay time                              | t <sub>d2</sub>  | _    | _     | 20   | μs    |                                                                                                       |

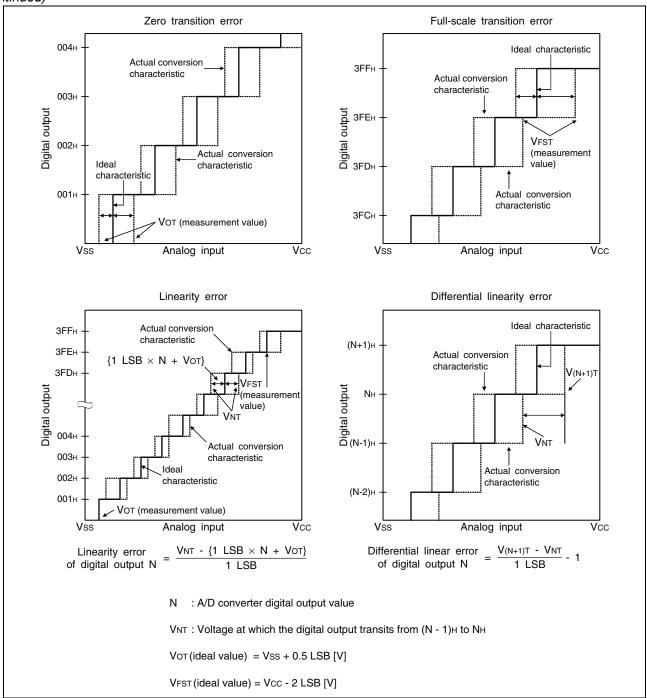

#### 14.5 A/D Converter

#### 14.5.1 A/D Converter Electrical Characteristics

(V<sub>CC</sub> = 4.0 V to 5.5 V, V<sub>SS</sub> = 0.0 V,  $T_A$  =  $-40^{\circ}$ C to  $+85^{\circ}$ C)

| Parameter                     | Symbol           |                           | Value                     |                           | Unit  | Remarks                                                                                              |

|-------------------------------|------------------|---------------------------|---------------------------|---------------------------|-------|------------------------------------------------------------------------------------------------------|

| Parameter                     | Symbol           | Min                       | Тур                       | Max                       | Ullit | Remarks                                                                                              |

| Resolution                    |                  | _                         | _                         | 10                        | bit   |                                                                                                      |

| Total error                   |                  | -3                        | _                         | +3                        | LSB   |                                                                                                      |

| Linearity error               | _                | -2.5                      | _                         | +2.5                      | LSB   |                                                                                                      |

| Differential linear error     |                  | -1.9                      | _                         | +1.9                      | LSB   |                                                                                                      |

| Zero transition voltage       | V <sub>OT</sub>  | V <sub>SS</sub> – 1.5 LSB | V <sub>SS</sub> + 0.5 LSB | V <sub>SS</sub> + 2.5 LSB | V     |                                                                                                      |

| Full-scale transition voltage | V <sub>FST</sub> | V <sub>CC</sub> – 4.5 LSB | V <sub>CC</sub> – 2 LSB   | V <sub>CC</sub> + 0.5 LSB | ٧     |                                                                                                      |

| Compare time                  |                  | 0.9                       | _                         | 16500                     | μs    | $4.5~\text{V} \leq \text{V}_{CC} \leq 5.5~\text{V}$                                                  |

| Compare time                  | _                | 1.8                       | _                         | 16500                     | μs    | $4.0 \text{ V} \le \text{V}_{CC} \le 4.5 \text{ V}$                                                  |

| Compling time                 |                  | 0.6                       | _                         | ∞                         | μs    | $4.5~\text{V} \leq \text{V}_{CC} \leq 5.5~\text{V}$ , with external impedance < $5.4~\text{k}\Omega$ |

| Sampling time                 |                  | 1.2                       | _                         | σ.                        | μs    | $4.0~\text{V} \leq \text{V}_{CC} < 4.5~\text{V}$ , with external impedance < 2.4 k $\Omega$          |

| Analog input current          | I <sub>AIN</sub> | -0.3                      | _                         | +0.3                      | μA    |                                                                                                      |

| Analog input voltage          | V <sub>AIN</sub> | V <sub>SS</sub>           | _                         | V <sub>CC</sub>           | V     |                                                                                                      |

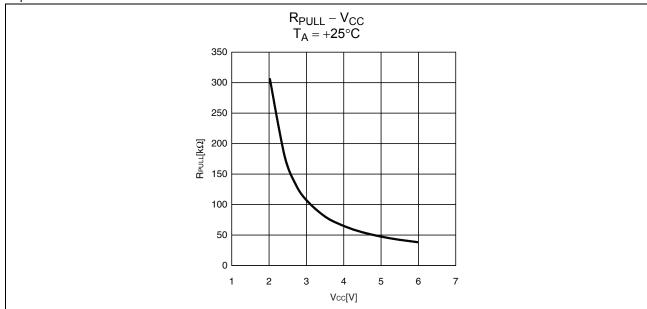

## ■ Pull-up characteristics

# 16. Mask Options

| No. | Part Number                 | MB95F394H<br>MB95F396H<br>MB95F398H                                  | MB95F394K<br>MB95F396K<br>MB95F398K |  |  |  |

|-----|-----------------------------|----------------------------------------------------------------------|-------------------------------------|--|--|--|

|     | Selectable/Fixed            | Fixed                                                                |                                     |  |  |  |

| 1   | Low-voltage detection reset | Without low-voltage detection reset With low-voltage detection reset |                                     |  |  |  |

| 2   | Reset                       | With dedicated reset input Without dedicated reset input             |                                     |  |  |  |

# 19. Major Changes

| Page     | Section                                                      | Details                                                                                                                                                                                                         |

|----------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Features                                                     | Changed the main CR clock oscillation accuracy. $\pm 2\% \rightarrow \pm 2\%$ or $\pm 2.5\%$                                                                                                                    |

|          |                                                              | Added a remark about the main CR clock accuracy.                                                                                                                                                                |

| 4        | Product Line-up                                              | Added FPT-52P-M02.                                                                                                                                                                                              |

| 5        | Packages And Corresponding Products                          | Added FPT-52P-M02.                                                                                                                                                                                              |

| 6        | Differences Among Products And Notes On<br>Product Selection | Added a reference for the connection method in "• On-chip debug function".                                                                                                                                      |

| 8        | Pin Assignment                                               | Added the pin assignment diagram of FPT-52P-M02.                                                                                                                                                                |

| 10 to 13 | Pin Functions                                                | Added the pin numbers of FPT-52P-M02.                                                                                                                                                                           |

| 34       | Electrical Characteristics AC Characteristics Clock Timing   | Changed the values of clock frequency (F <sub>CRH</sub> ).  Added conditions related to the LQFP package and the QFN package for the values of clock frequency (F <sub>CRH</sub> ).  Added footnotes *2 and *3. |

| 58 to 63 | Sample Characteristics                                       | Added "Sample Characteristics".                                                                                                                                                                                 |

| 65       | Ordering Information                                         | Added the part numbers of FPT-52P-M02.                                                                                                                                                                          |

| 67       | Package Dimension                                            | Added the package diagram of FPT-52P-M02.                                                                                                                                                                       |

NOTE: Please see "Document History" about later revised information.

# **Document History**

| Document Title: MB95F394H/F396K/F398H/F394K/F396H/F398K CMOS F2MC-8FX MB95390H Series 8-bit Microcontrollers Document Number: 002-07573 |         |                    |                    |                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------|

| Revision                                                                                                                                | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                  |

| **                                                                                                                                      | _       | AKIH               | 07/27/2010         | Migrated to Cypress and assigned document number 002-07573.  No change to document contents or format. |

| *A                                                                                                                                      | 5185613 | AKIH               | 3/31/2016          | Updated to Cypress template                                                                            |

Document Number: 002-07573 Rev. \*A Page 71 of 72

### Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

**USB Controllers**

Wireless/RF

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface Lighting & Power Control Memory **PSoC** Touch Sensing

cypress.com/interface cypress.com/powerpsoc cypress.com/memory cypress.com/psoc cypress.com/touch cypress.com/usb cypress.com/wireless

#### PSoC® Solutions

cypress.com/psoc PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

**Technical Support** cypress.com/support

© Cypress Semiconductor Corporation 2010-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners

Document Number: 002-07573 Rev. \*A Revised March 31, 2016 Page 72 of 72