Welcome to **E-XFL.COM**

<u>Embedded - Microcontrollers - Application</u>

<u>Specific</u>: Tailored Solutions for Precision and Performance

Embedded - Microcontrollers - Application Specific represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

What Are <u>Embedded - Microcontrollers - Application Specific?</u>

Application enecific microcontrollers are engineered to

| Details                 |                                                                          |

|-------------------------|--------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                 |

| Applications            | Automotive                                                               |

| Core Processor          | S12                                                                      |

| Program Memory Type     | FLASH (32KB)                                                             |

| Controller Series       | HCS12                                                                    |

| RAM Size                | 2K x 8                                                                   |

| Interface               | LIN, SCI                                                                 |

| Number of I/O           | 9                                                                        |

| Voltage - Supply        | 2.25V ~ 5.5V                                                             |

| Operating Temperature   | -40°C ~ 105°C                                                            |

| Mounting Type           | Surface Mount                                                            |

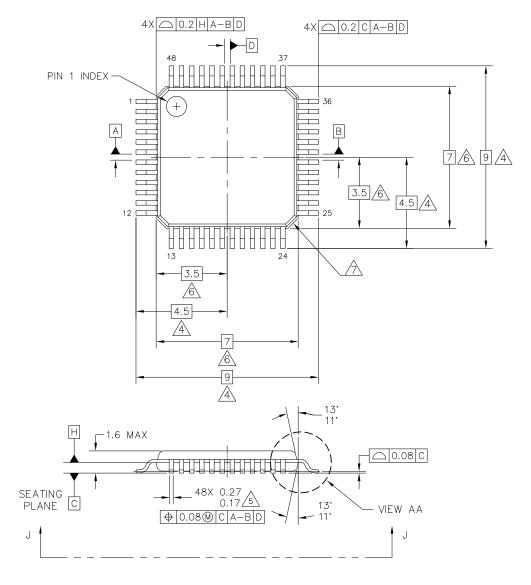

| Package / Case          | 48-LQFP Exposed Pad                                                      |

| Supplier Device Package | 48-HLQFP (7x7)                                                           |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/mm912f634bv1aer2 |

|                         |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 6. Maximum Electrical Ratings - MCU Die

| Ratings                                                                 | Symbol            | Value        | Unit |

|-------------------------------------------------------------------------|-------------------|--------------|------|

| 5.0 V Supply Voltage                                                    | V <sub>EDDX</sub> | -0.3 to 6.0  | V    |

| 2.5 V Supply Voltage                                                    | V <sub>EDD</sub>  | -0.3 to 2.75 | V    |

| Digital I/O input voltage (PA0PA7, PE0, PE1)                            | V <sub>IN</sub>   | -0.3 to 6.0  | V    |

| EXTAL, XTAL                                                             | V <sub>ILV</sub>  | -0.3 to 2.16 | V    |

| TEST input                                                              | V <sub>TEST</sub> | -0.3 to 10.0 | V    |

| Instantaneous maximum current Single pin limit for all digital I/O pins | I <sub>D</sub>    | -25 to 25    | mA   |

| Instantaneous maximum current Single pin limit for EXTAL, XTAL          | I <sub>DL</sub>   | -25 to 25    | mA   |

#### **Table 7. Maximum Thermal Ratings**

| Ratings                                                                                                                                                                                                            | Symbol                                                     | Value          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------|------|

| Storage Temperature                                                                                                                                                                                                | T <sub>STG</sub>                                           | -55 to 150     | °C   |

| Package Thermal Resistance - LQFP48-EP Four layer board (JEDEC 2s2p) Junction to Ambient Natural Convection (7) Junction to Board (9) Two layer board (JEDEC 1s) Junction to Ambient Natural Convection (7), (8)   | $egin{array}{c} R_{	heta JA} \ R_{	heta JB} \ \end{array}$ | 39<br>16<br>91 | °C/W |

| Package Thermal Resistance - LQFP48  Four layer board (JEDEC 2s2p)  Junction to Ambient Natural Convection (7)  Junction to Board (9)  Two layer board (JEDEC 1s)  Junction to Ambient Natural Convection (7), (8) | R <sub>θJA</sub><br>R <sub>θJB</sub><br>R <sub>θJA</sub>   | 59<br>31<br>96 | °C/W |

| Peak Package Reflow Temperature During Reflow (10),(11)                                                                                                                                                            | T <sub>PPRT</sub>                                          | 300            | °C   |

#### Notes

- 7. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 8. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 9. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 10. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 11. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC34xxxD enter 34xxx), and review parametrics.

# 3.3 Operating Conditions

This section describes the operating conditions of the device. Unless otherwise noted those conditions apply to all the following data.

## **Table 8. Operating Conditions**

| Ratings                                                                                           | Symbol            | Value      | Unit |

|---------------------------------------------------------------------------------------------------|-------------------|------------|------|

| Analog Die Nominal Operating Voltage                                                              | V <sub>SUP</sub>  | 5.5 to 18  | V    |

| Analog Die Functional Operating Voltage - Device is fully functional. All features are operating. | $V_{SUPOP}$       | 5.5 to 27  | V    |

| MCU I/O and supply voltage <sup>(12)</sup>                                                        | V <sub>EDDX</sub> | 4.5 to 5.5 | V    |

Table 22. Static Electrical Characteristics - Current Sense Module - ISENSE

| Symbol              | Min                   | Тур | Max                                                                           | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|-----------------------|-----|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G                   |                       |     |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -                     | 7.0 | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -                     | 9.0 | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -                     | 10  | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -                     | 12  | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -                     | 14  | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -                     | 18  | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -                     | 24  | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -                     | 36  | -                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | -3.0                  | -   | 3.0                                                                           | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     | -1.5                  | -   | 1.5                                                                           | %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RES                 | -                     | 51  | -                                                                             | mA/LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>IN</sub>     | -0.2                  | -   | 3.0                                                                           | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I <sub>ISENSE</sub> | -                     | 600 | -                                                                             | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                     | G RES V <sub>IN</sub> | G   | G - 7.0 - 9.0 - 10 - 12 - 14 - 18 - 24 - 36 - 3.0 1.5 - RES - 51 - VIN -0.2 - | G - 7.0 - 9.0 - 10 - 10 - 12 - 12 - 14 - 18 - 18 - 24 - 36 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 1.5 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - 3.0 - |

Note:

26. RES =  $2.44 \text{ mV/(GAIN*R}_{SHUNT})$

Table 23. Static Electrical Characteristics - Temperature Sensor - TSENSE

| Ratings                                                                           | Symbol              | Min  | Тур  | Max | Unit |

|-----------------------------------------------------------------------------------|---------------------|------|------|-----|------|

| Internal Chip Temperature Sense Gain <sup>(27)</sup>                              | TS <sub>G</sub>     | -    | 9.17 | -   | mV/k |

| Internal Chip Temperature Sense Error at the end of conversion <sup>(27)</sup>    | TS <sub>ERR</sub>   | -5.0 | -    | 5.0 | °C   |

| Temperature represented by a ADC <sub>IN</sub> Voltage of 0.150 V <sup>(27)</sup> | T <sub>0.15V</sub>  | -55  | -50  | -45 | °C   |

| Temperature represented by a ADC <sub>IN</sub> Voltage of 1.984 V <sup>(27)</sup> | T <sub>1.984V</sub> | 145  | 150  | 155 | °C   |

Note:

27. Guaranteed by design and characterization.

Table 24. Static Electrical Characteristics - Supply Voltage Sense - VSENSE and VS1SENSE

| Ratings                                                                                                    | Symbol                    | Min | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------------------------------|---------------------------|-----|------|------|------|

| VSENSE Input Divider Ratio (RATIO <sub>VSENSE</sub> = $V_{VSENSE}$ / ADCIN)<br>5.5 V < $V_{SUP}$ < 27 V    | RATIO <sub>VSENSE</sub>   |     | 10.8 |      |      |

| VSENSE error - whole path (VSENSE pin to Digital value)                                                    | ER <sub>VSENSE</sub>      | -   | -    | 5.0  | %    |

| VS1SENSE Input Divider Ratio (RATIO <sub>VS1SENSE</sub> = $V_{VS1SENSE}$ / ADCIN) 5.5 V < $V_{SUP}$ < 27 V | RATIO <sub>VS1SENSE</sub> |     | 10.8 |      |      |

| VS1SENSE error - whole path (VS1 pin to Digital value)                                                     | ER <sub>VS1SENSE</sub>    | -   | -    | 5.0  | %    |

| VSENSE Series Resistor                                                                                     | R <sub>VSENSE</sub>       | 9.5 | 10   | 10.5 | kΩ   |

| VSENSE Capacitor (optional) <sup>(28)</sup>                                                                | C <sub>VSENSE</sub>       | -   | 100  | -    | nF   |

Note:

28. The ESD behavior specified in Section 3.8, "ESD Protection and Latch-up Immunity" is guaranteed without the optional capacitor.

Table 36. Dynamic Electrical Characteristics - Analog Digital Converter - ADC

| Ratings                                                      | Symbol            | Min | Тур | Max | Unit |

|--------------------------------------------------------------|-------------------|-----|-----|-----|------|

| ADC Operating Frequency <sup>(39)</sup>                      | f <sub>ADC</sub>  | 1.6 | 2.0 | 2.4 | MHz  |

| Conversion Time (from ACCR write to CC Flag) <sup>(39)</sup> |                   |     | 26  |     | clk  |

| Sample Frequency Channel 14 (Bandgap) <sup>(39)</sup>        | f <sub>CH14</sub> | -   | -   | 2.5 | kHz  |

Note:

#### 3.6.2 Dynamic Electrical Characteristics MCU Die

#### 3.6.2.1 **NVM Timing**

The time base for all NVM program or erase operations is derived from the bus block. A minimum bus frequency f<sub>NVMBUS</sub> is required for performing program or erase operations. The NVM module do not has any means to monitor the frequency and does not prevent a program or erase operation at frequencies above or below the specified minimum. Attempting to program or erase the NVM modules at a lower frequency, a full program, or erase transition is not assured.

The Flash program and erase operations are timed using a clock derived from the bus clock using the FCLKDIV and register. The frequency of this clock must be set within the limits specified as f<sub>NVMOP</sub>.

The minimum program and erase times shown in Table 37 are calculated for maximum  $f_{NVMOP}$  and maximum  $f_{BUS}$ . The maximum times are calculated for minimum  $f_{NVMOP}$  and a  $f_{BUS}$  of 2.0 MHz.

## 3.6.2.1.1 Single Word Programming

The programming time for single word programming is dependant on the bus frequency as a well as on the frequency  $f_{NVMOP}$ , and can be calculated according to the following formula.

$$t_{\text{swpgm}} = 9 \cdot \frac{1}{f_{\text{NVMOP}}} + 25 \cdot \frac{1}{f_{\text{bus}}}$$

#### 3.6.2.1.2 Burst Programming

This applies only to the Flash, where up to 64 words in a row can be programmed consecutively, using burst programming by keeping the command pipeline filled. The time to program a consecutive word can be calculated as:

$$t_{\text{bwpgm}} = 4 \cdot \frac{1}{f_{\text{NVMOP}}} + 9 \cdot \frac{1}{f_{\text{bus}}}$$

The time to program a whole row is:

$$t_{brpgm} = t_{swpgm} + 63 \cdot t_{bwpgm}$$

Burst programming is more than 2 times faster than single word programming.

#### 3.6.2.1.3 Sector Erase

#### NOTE

The sector erase cycle is divided into 16 individual erase pulses to achieve faster system response during the erase flow. The given erase time (t<sub>ERA</sub>) specifies the time considering consecutive pulses.

<sup>39.</sup> Guaranteed by design.

#### 3.6.2.2 NVM Reliability

The reliability of the NVM blocks is guaranteed by stress tests during qualification, constant process monitors, and burn-in to screen early life failures. The program/erase cycle count on the sector is incremented every time a sector or mass erase event is executed.

**Table 38. NVM Reliability Characteristics**

| Rating                                                                                               | Symbol             | Min    | Тур                     | Max | Unit   |

|------------------------------------------------------------------------------------------------------|--------------------|--------|-------------------------|-----|--------|

| Data retention after 10,000 program/erase cycles for T <sub>JAVG</sub> ≤ 85 °C <sup>(45), (46)</sup> | t                  | 15     | 100 <sup>(47)</sup>     | -   | Years  |

| Data retention with <100 program/erase cycles for T <sub>JAVG</sub> ≤ 85 °C <sup>(45), (46)</sup>    | <sup>t</sup> FLRET | 20     | 100 <sup>(47)</sup>     | -   | icais  |

| Number of program/erase cycles (46) (-40 °C $\leq$ T <sub>J</sub> $\leq$ 0 °C)                       | n                  | 10,000 | -                       | -   | Cycles |

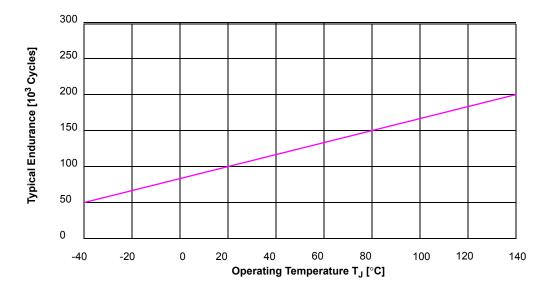

| Number of program/erase cycles $^{(46)}$ (0 °C $\leq$ T <sub>J</sub> $\leq$ 140 °C)                  | - n <sub>FL</sub>  | 10,000 | 100,000 <sup>(48)</sup> | -   | Cycles |

#### Note:

- 45. T<sub>JAVG</sub> is the Average Junction Temperature

- 46. T<sub>JAVG</sub> does not exceed 85 °C considering a typical temperature profile over the lifetime of a consumer, industrial, or automotive application.

- 47. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25 °C, using the Arrhenius equation. For additional information on how Freescale defines Typical Data Retention, refer to Engineering Bulletin EB618.

- 48. Spec table quotes typical endurance evaluated at 25 °C for this product family, typical endurance at various temperature can be estimated using the graph in Figure 10. For additional information on how Freescale defines Typical Endurance, refer to Engineering Bulletin EB619.

Figure 10. Typical Flash Cycling Endurance vs. Temperature

## Table 77. VSR - Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>VROVC | Voltage Regulator Overvoltage Condition - This status bit indicates an overvoltage warning is present for at least one of the main voltage regulators (VDD or VDDX). Reading the register clears the VROVI flag if present. See Section 4.6, "Interrupts" for details. Note: This feature requires the trimming of Section 4.25.2.3, "Trimming Register 2 (CTR2)" to be done to be effective. Untrimmed devices may issue the VROVC condition including the LS turn off at normal operation.  0 - No Voltage Regulator Overvoltage Condition present.  1 - Voltage Regulator Overvoltage Condition present. |

| 3<br>HTC   | High Temperature Condition - This status bit indicates a high temperature warning is present for the Voltage regulators (VDD/VDDX). Reading the register clears the HTI flag if present. See Section 4.6, "Interrupts" for details.  0 - No High Temperature Condition present.  1 - High Temperature Condition present.                                                                                                                                                                                                                                                                                    |

| 2<br>HVC   | High Voltage Condition - This status bit indicates a high voltage warning for VS2 is present. Reading the register clears the HVI flag if present. See Section 4.6, "Interrupts" for details.  0 - No High Voltage Condition present.  1 - High Voltage Condition present.                                                                                                                                                                                                                                                                                                                                  |

| 1<br>LVC   | Low Voltage Condition - This status bit indicates a low voltage warning for VS1 is present. Reading the register clears the LVI flag if present. See Section 4.6, "Interrupts" for details.  0 - No Low Voltage Condition present.  1 - Low Voltage Condition present.                                                                                                                                                                                                                                                                                                                                      |

| 0<br>LBC   | Low Battery Condition - This status bit indicates a low voltage warning for VSENSE is present. Reading the register clears the LBI flag if present. See Section 4.6, "Interrupts" for details.  0 - No Low Battery Condition present.  1 - Low Battery Condition present.                                                                                                                                                                                                                                                                                                                                   |

# 4.5 Die to Die Interface - Target

The D2D Interface is the bus interface to the Microcontroller. Access to the MM912F634 analog die is controlled by the D2D Interface module. This section describes the functionality of the die-to-die target block (D2D).

# 4.5.1 Overview

The D2D is the target for a data transfer from the target to the initiator (MCU). The initiator provides a set of configuration registers and two memory mapped 256 Byte address windows. When writing to a window, a transaction is initiated sending a write command, followed by an 8-bit address, and the data byte or word is received from the initiator. When reading from a window, a transaction is received with the read command, followed by an 8-bit address. The target then responds with the data. The basic idea is that a peripheral located on the MM912F634 analog die, can be addressed like an on-chip peripheral.

#### Features:

- · software transparent register access to peripherals on the MM912F634 analog die

- · 256 Byte address window

- · supports blocking read or write, as well as non-blocking write transactions

- · 4 bit physical bus width

- · automatic synchronization of the target when initiator starts driving the interface clock

- · generates transaction and error status as well as EOT acknowledge

- · providing single interrupt interface to D2D Initiator

#### 4.8.1 Wake-up Sources

#### 4.8.1.1 Lx - Wake-up (Cyclic Sense Disabled)

Any state digital change on a Wake-up Enabled Lx input issues a wake-up. In order to select and activate a Wake-up Input (Lx), the Wake-up Control Register (WCR) must be configured with appropriate LxWE inputs enabled or disabled before entering low power mode. The Lx - Wake-up may be combined with the Forced Wake-up.

Note: Selecting a Lx Input for wake-up disables a selected analog input once entering low power mode.

#### 4.8.1.2 Lx - Cyclic Sense Wake-up

#### NOTE

Once Cyclic Sense is configured (CSSEL!=0), the state change is only recognized from one cyclic sense event to the next.

The additional accuracy of the cyclic sense cycle by the WD clock trimming is only active during STOP mode. There is no trimmed clock available during SLEEP mode.

To reduce external power consumption during low power mode a cyclic wake-up has been implemented. Configuring the Timing Control Register (TCR) a specific cycle time can be selected to implement a periodic switching of the HS1 or HS2 output with the corresponding detection of an Lx state change. Any configuration of the HSx in the High-side Control Register (HSCR) is ignored when entering low power mode. The Lx - Cyclic Sense Wake-up may be combined with the Forced Wake-up. In case both (forced and Lx change) events are present at the same time, the Forced Wake-up is indicated as Wake-up source.

#### 4.8.1.3 Forced Wake-up

Configuring the Forced Wake-up Multiplier (FWM) in the Timing Control Register (TCR) enables the forced wake-up based on the selected Cyclic Sense Timing (CST). Forced Wake-up can be combined with all other wake-up sources considering the timing dependencies.

#### 4.8.1.4 LIN - Wake-up

While in Low-Power mode the MM912F634 analog die monitors the activity on the LIN bus. A dominant pulse longer than t<sub>PROPWL</sub> followed by a dominant to recessive transition causes a LIN Wake-up. This behavior protects the system from a short-to-ground bus condition.

## 4.8.1.5 D2D - Wake-up (Stop Mode Only)

Receiving a Normal mode request via the D2D interface (MODE=0, Mode Control Register (MCR)) results in a wake-up from stop mode. As this condition is controlled by the MCU, no wake-up status bit does indicate this wake-up source.

#### 4.8.1.6 Wake-up Due to Internal / External Reset (STOP Mode Only)

While in Stop mode, a Reset due to a VDD low voltage condition or an external Reset applied on the RESET\_A pin results in a Wake-up with immediate transition to Reset mode. In this case, the LVR or EXR bits in the Reset Status Register indicates the source of the event.

#### 4.8.1.7 Wake-up Due to Loss of Supply Voltage (SLEEP Mode Only)

While in Sleep mode, a supply voltage VS1 < V<sub>POR</sub> results in a transition to Power On mode.

#### 4.10.1 Register Definition

#### 4.10.1.1 Hall Supply Register (HSR)

#### Table 95. Hall Supply Register (HSR)

| Offset <sup>(81)</sup> | 0x38  |      |   |   |   |   | Access | : User read/write |

|------------------------|-------|------|---|---|---|---|--------|-------------------|

|                        | 7     | 6    | 5 | 4 | 3 | 2 | 1      | 0                 |

| R                      | HOTIE | НОТС | 0 | 0 | 0 | 0 | 0      | HSUPON            |

| W                      | HOTIL |      |   |   |   |   |        | 11001 014         |

| Reset                  | 0     | 0    | 0 | 0 | 0 | 0 | 0      | 0                 |

Note:

#### Table 96. HSR - Register Field Descriptions

| Field      | Description                                                                                                                                                                                    |  |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7 - HOTIE  | Hall Supply Overtemperature Interrupt Enable                                                                                                                                                   |  |  |  |  |  |

| 6 - HOTC   | Hall Supply Overtemperature Condition present. During the event, the Hall Supply is shut down. Reading the register clears the HOT flag if present. See Section 4.6, "Interrupts" for details. |  |  |  |  |  |

| 0 - HSUPON | Hall Supply On: 0 - Hall Supply Regulator disabled 1 - Hall Supply Regulator enabled                                                                                                           |  |  |  |  |  |

# 4.11 High-side Drivers - HS

These outputs are two High-side drivers, intended to drive small resistive loads or LEDs incorporating the following features:

- · PWM capability via the PWM Module

- · Open load detection

- · Current limitation

- · Overtemperature shutdown (with maskable interrupt)

- High voltage shutdown HVI (software maskable)

- Cyclic-Sense, See Section 4.8, "Wake-up / Cyclic Sense"

#### 4.11.1 Open Load Detection

Each high-side driver signals an Open Load condition if the current through the high-side is below the open load current threshold. The open load condition is indicated with the bits HS10L and HS20L in the High-side Status Register (HSSR).

When the High-side is in OFF state, the Open Load Detection function is not operating. When reading the HSSR register while the High-side is operating in PWM and is in the OFF state, the HS10L and HS20L bits does not indicate Open Load.

## 4.11.2 Current Limitation

Each high-side driver has an output current limitation. In combination with the overtemperature shutdown the high-side drivers are protected against overcurrent and short-circuit failures. The driver operating in the current limitation area is indicated with the bits HS1CL and HS2CL in the High-side Status Register (HSSR).

# 4.11.3 Overtemperature Protection (HS Interrupt)

Both high-side drivers are protected against overtemperature. In overtemperature conditions, both high-side drivers are shut down and the event is latched in the Interrupt Control Module. The shutdown is indicated as HS Interrupt in the Interrupt Source Register (ISR).

A thermal shutdown of the high-side drivers is indicated by setting the HSOT bit in the High-side Status Register (HSSR). A write to the High-side Control Register (HSCR), when the overtemperature condition is gone, re- enables the high-side drivers.

<sup>81.</sup> Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

## 4.11.7.2 High-side Status Register (HSSR)

#### Table 99. High-side Status Register (HSSR)

| Offset <sup>(83)</sup> 0x29 Access: User read |       |   |   |   |       |       |       |       |

|-----------------------------------------------|-------|---|---|---|-------|-------|-------|-------|

|                                               | 7     | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

| R                                             | HSOTC | 0 | 0 | 0 | HS2CL | HS1CL | HS2OL | HS10L |

| W                                             |       |   |   |   |       |       |       |       |

| Reset                                         | 0     | 0 | 0 | 0 | 0     | 0     | 0     | 0     |

Note:

#### Table 100. HSSR - Register Field Descriptions

| Field     | Description                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 - HSOTC | High-side Overtemperature Condition present. Both drivers are turned off. Reading the register clears the HSOT interrupt flag if present. See Section 4.6, "Interrupts" for details. |

| 3 - HS2CL | High-side 2 Current Limitation                                                                                                                                                       |

| 2 - HS1CL | High-side 1 Current Limitation                                                                                                                                                       |

| 1 - HS2OL | High-side 2 Open Load <sup>(84)</sup>                                                                                                                                                |

| 0 - HS1OL | High-side 1 Open Load <sup>(84)</sup>                                                                                                                                                |

Note:

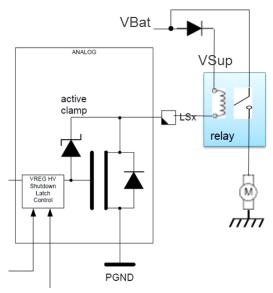

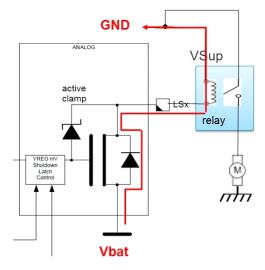

#### 4.12 Low-side Drivers - LSx

#### 4.12.1 Introduction / Features

These outputs are two Low-side drivers intended to drive relays (inductive loads) incorporating the following features:

- · PWM capability

- · Open load detection

- · Current limitation

- · Overtemperature shutdown (with maskable interrupt)

- · Active clamp

- · Independent VREG High Voltage Shutdown

<sup>83.</sup> Offset related to 0x0200 for blocking access and 0x300 for non blocking access within the global address space.

<sup>84.</sup> When the High-side is in OFF state, the Open Load Detection function is not operating. When reading the HSSR register while the High-side is operating in PWM and is in the OFF state, the HS10L and HS20L bits does not indicate Open Load.

#### 4.12.5 PWM Capability

See Section 4.13, "PWM Control Module (PWM8B2C)".

#### 4.12.6 Low-side Driver in Reverse Polarity

Freescale recommends the user implement their systems using an external diode to protect the low-side driver (LSx) from potential damage (see Figure 22) in the event of a reverse polarity condition. However, if the user chooses to implement their system without an external diode, and a reverse polarity condition were to occur, the current would flow through the body diode of the LSx driver and through the closing coil of the relay, as shown in Figure 23. The magnitude of current through this body diode is determined by the characteristics of this relay coil. Since this body diode is not specified to carry a sustained minimum amount of current, Freescale strongly recommends users implement their systems using an external reverse polarity protection diode.

Figure 22. Low-side Driver Implemented With External Reverse Polarity Diode

Figure 23. Current Flow in Low-side Driver Under Reverse Polarity Condition Without External Diode

- · Hardware parity generation and checking

- · Programmable 8-bit or 9-bit character length

- · Receiver wake-up by idle-line or address-mark

- Optional 13-bit break character generation / 11-bit break character detection

- · Selectable transmitter output polarity

## 4.15.1.2 Modes of Operation

See Section 4.15.3, "Functional Description"," For details concerning SCI operation in these modes:

- · 8- and 9-bit data modes

- Loop mode

- · Single-wire mode

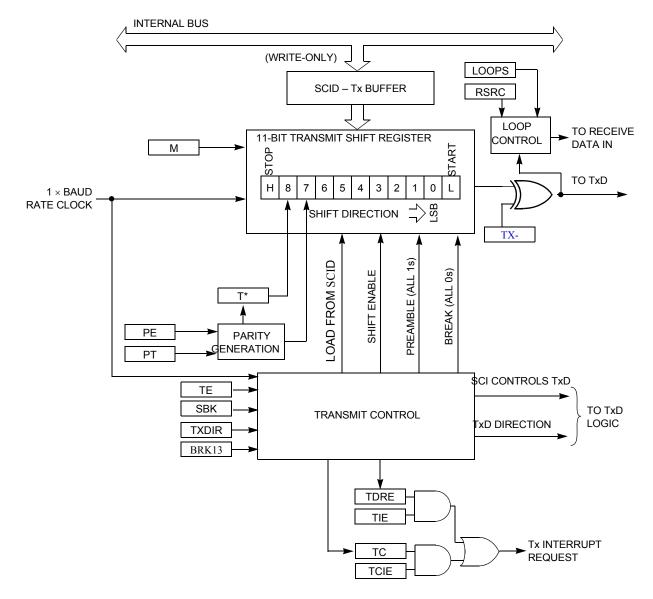

#### 4.15.1.3 Block Diagram

Figure 32 shows the transmitter portion of the SCI.

Figure 32. SCI Transmitter Block Diagram

Table 188. Analog Digital Converter Module - Memory Map (continued)

| Register /<br>Offset <sup>(135)</sup> |   | Bit 7  | 6    | 5 | 4    | 3                 | 2 | 1 | Bit 0 |

|---------------------------------------|---|--------|------|---|------|-------------------|---|---|-------|

| 0x90                                  | R |        |      |   | ADR  | 5[9:2]            |   |   |       |

| ADR5 (hi)                             | W |        |      |   |      |                   |   |   |       |

| 0x91                                  | R | ADR5[1 | 1:0] |   |      |                   |   |   |       |

| ADR5 (lo)                             | W |        |      |   |      |                   |   |   |       |

| 0x92                                  | R |        |      |   | ADR  | 6[9:2]            |   |   |       |

| ADR6 (hi)                             | w |        |      |   |      |                   |   |   |       |

| 0x93                                  | R | ADR6[1 | 1:0] |   |      |                   |   |   |       |

| ADR6 (lo)                             | w | Ī      | -    |   |      |                   |   |   |       |

| 0x94                                  | R |        |      |   | ADR7 | <u>[</u><br>[9:2] |   |   |       |

| ADR7 (hi)                             | w |        |      |   |      |                   |   |   |       |

| 0x95                                  | R |        | 1:0] |   |      |                   |   |   |       |

| ADR7 (lo)                             | W |        |      |   |      |                   |   |   |       |

| 0x96                                  | R |        |      |   | ADR8 | B[9:2]            |   |   |       |

| ADR8 (hi)                             | W |        |      |   |      |                   |   |   |       |

| 0x97                                  | R | ADR8[1 | 1:0] |   |      |                   |   |   |       |

| ADR8 (lo)                             | W | Ī      | •    |   |      |                   |   |   |       |

| 0x98                                  | R |        |      |   | ADRS | )[9:2]            |   |   |       |

| ADR9 (hi)                             | W |        |      |   |      |                   |   |   |       |

| 0x99                                  | R | ADR9[1 | 1:0] |   |      |                   |   |   |       |

| ADR9 (lo)                             | W |        | -    |   |      |                   |   |   |       |

| 0x9A                                  | R |        |      |   | ADR1 | 0[9:2]            |   |   |       |

| ADR10 (hi)                            | W |        |      |   |      |                   |   |   |       |

| 0x9B                                  | R | ADR10[ | 1:0] |   |      |                   |   |   |       |

| ADR10 (lo)                            | W |        |      |   |      |                   |   |   |       |

| 0x9C                                  | R |        |      |   | ADR1 | 1[9:2]            |   |   |       |

| ADR11 (hi)                            | W |        |      |   |      |                   |   |   |       |

| 0x9D                                  | R | ADR11[ | 1:0] |   |      |                   |   |   |       |

| ADR11 (lo)                            | W |        | -    |   |      |                   |   |   |       |

| 0x9E                                  | R |        |      |   | ADR1 |                   |   |   |       |

| ADR12 (hi)                            | W |        |      |   |      |                   |   |   |       |

| 0x9F                                  | R | ADR12[ | 1:0] |   |      |                   |   |   |       |

| ADR12 (lo)                            | W |        | -    |   |      |                   |   |   |       |

| 0xA0                                  | R |        |      |   |      |                   |   |   |       |

| Reserved                              | W |        |      |   |      |                   |   |   |       |

| 0xA1                                  | R |        |      |   |      |                   |   |   |       |

| Reserved                              | W |        |      |   |      |                   |   |   |       |

| 0xA2                                  | R |        |      |   | ADR1 | 4[9:2]            |   |   |       |

| ADR14 (hi)                            | W |        |      |   |      |                   |   |   |       |

| , ,                                   |   |        |      |   |      |                   |   |   |       |

## Table 218. Port A Data Register Description (continued)

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>PTA | Port A general purpose input/output data—Data Register Port A pin 2 is associated with the SCK signal of the SPI module. When not used with the alternative function, this pin can be used as general purpose I/O. If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the buffered and synchronized pin input state is read.  |

| 1<br>PTA | Port A general purpose input/output data—Data Register Port A pin 1 is associated with the MOSI signal of the SPI module. When not used with the alternative function, this pin can be used as general purpose I/O. If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the buffered and synchronized pin input state is read. |

| 0<br>PTA | Port A general purpose input/output data—Data Register Port A pin 0 is associated with the MISO signal of the SPI module. When not used with the alternative function, this pin can be used as general purpose I/O. If the associated data direction bit of this pin is set to 1, a read returns the value of the port register, otherwise the buffered and synchronized pin input state is read. |

## 4.27.3.2 PIM Reserved Register

#### Table 219. PIM Reserved Register

| Address 0x0001 Access: User read |   |   |   |   |   |   | ss: User read <sup>(159)</sup> |   |

|----------------------------------|---|---|---|---|---|---|--------------------------------|---|

|                                  | 7 | 6 | 5 | 4 | 3 | 2 | 1                              | 0 |

| R                                | 0 | 0 | 0 | 0 | 0 | 0 | 0                              | 0 |

| W                                |   |   |   |   |   |   |                                |   |

| Reset                            | 0 | 0 | 0 | 0 | 0 | 0 | 0                              | 0 |

Note:

159. Read: Anytime.

Write: Unimplemented. Writing to this register has no effect.

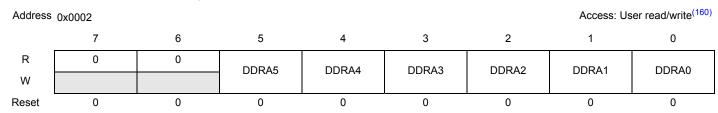

# 4.27.3.3 Port A Data Direction Register (DDRA)

#### Table 220. Port A Data Direction Register (DDRA)

Note:

160. Read: Anytime. Write: Anytime.

# Table 221. DDRA Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-0<br>DDRA | Port A Data Direction— This register controls the data direction of pins 5 through 0. The SPI function controls the data direction for the associated pins. In this case the data direction bits do not change. When operating a pin as a general purpose I/O, the associated data direction bit determines whether it is an input or output.  1 Associated pin is configured as output.  O Associated pin is configured as high-impedance input. |

The least significant word of line is read out first. This corresponds to the fields 1 and 0 of Table 315. The next word read returns field 2 in the least significant bits [3:0] and "0" for bits [15:4]. Reading the Trace Buffer while the DBG module is armed, returns invalid data, and no shifting of the RAM pointer occurs.

#### 4.31.4.5.6 Trace Buffer Reset State