Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                        |

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16/32-Bit                                                                       |

| Speed                      | 66MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI            |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                            |

| Number of I/O              | 75                                                                              |

| Program Memory Size        | 448KB (448K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 34K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-100-3                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc226456f66lackxuma1 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 Summary of Features

For a quick overview and easy reference, the features of the XC226x are summarized here.

- High-performance CPU with five-stage pipeline

- 12.5 ns instruction cycle at 80 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1024 Bytes on-chip special function register area (C166 Family compatible)

- Interrupt system with 16 priority levels for up to 87 sources

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 12.5 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- On-chip memory modules

- 1 Kbyte on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- 16 Kbytes on-chip data SRAM (DSRAM)

- Up to 64 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 768 Kbytes on-chip program memory (Flash memory)

- On-Chip Peripheral Modules

- Two Synchronizable A/D Converters with up to 16 channels, 10-bit resolution, conversion time below 1  $\mu$ s, optional data preprocessing (data reduction, range check)

- 16-channel general purpose capture/compare unit (CAPCOM2)

- Up to four capture/compare units for flexible PWM signal generation (CCU6x)

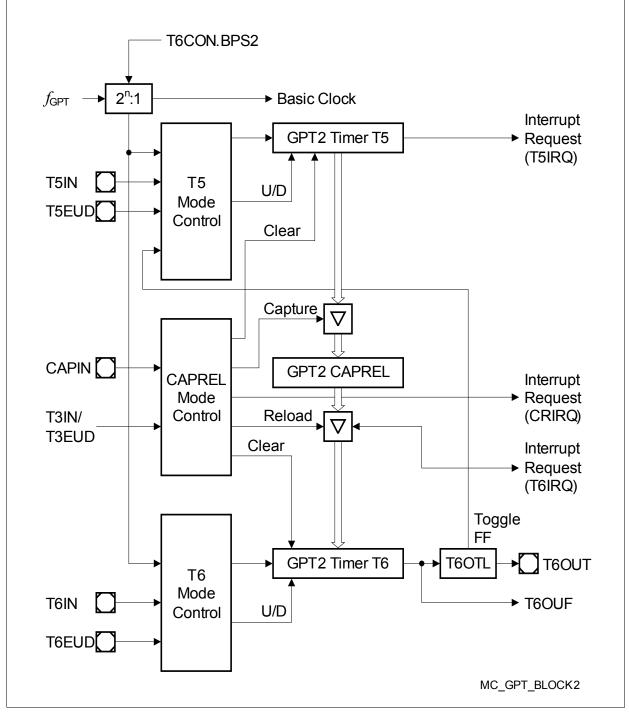

- Multi-functional general purpose timer unit with 5 timers

٠

#### **General Device Information**

#### **Notes to Pin Definitions**

Ctrl.: The output signal for a port pin is selected by bitfield PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bitfield PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc. Output signal OH is controlled by hardware.

2. **Type**: Indicates the pad type used (St=standard pad, Sp=special pad, DP=double pad, In=input pad, PS=power supply) and its power supply domain (A, B, M, 1).

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TESTM             | 1      | In/B | <b>Testmode Enable</b><br>Enables factory test modes, must be held HIGH for<br>normal operation (connect to $V_{\rm DDPB}$ ).<br>An internal pullup device will hold this pin high<br>when nothing is driving it.                                                                                                                                                |

| 4   | P7.2              | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                    |

|     | EMUX0             | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                                                      |

|     | TxDC4             | 02     | St/B | CAN Node 4 Transmit Data Output                                                                                                                                                                                                                                                                                                                                  |

|     | CCU62_<br>CCPOS0A | I      | St/B | CCU62 Position Input 0                                                                                                                                                                                                                                                                                                                                           |

|     | TDI_C             | I      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                             |

| 5   | TRST              | 1      | In/B | <b>Test-System Reset Input</b><br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XC226x's debug system.<br>In this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pulldown device will hold this pin low<br>when nothing is driving it. |

| 6   | P7.0              | O0 / I | St/B | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                    |

|     | T3OUT             | 01     | St/B | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                                                |

|     | T6OUT             | 02     | St/B | GPT2 Timer T6 Toggle Latch Output                                                                                                                                                                                                                                                                                                                                |

|     | TDO_A             | ОН     | St/B | JTAG Test Data Output                                                                                                                                                                                                                                                                                                                                            |

|     | ESR2_1            | 1      | St/B | ESR2 Trigger Input 1                                                                                                                                                                                                                                                                                                                                             |

|     | RxDC4B            | Ι      | St/B | CAN Node 4 Receive Data Input                                                                                                                                                                                                                                                                                                                                    |

#### Table 4 Pin Definitions and Functions

| Table | e 4 Pin De        | finitior | ns and | Functions (cont'd)                            |

|-------|-------------------|----------|--------|-----------------------------------------------|

| Pin   | Symbol            | Ctrl.    | Туре   | Function                                      |

| 7     | P7.3              | O0 / I   | St/B   | Bit 3 of Port 7, General Purpose Input/Output |

|       | EMUX1             | 01       | St/B   | External Analog MUX Control Output 1 (ADC1)   |

|       | U0C1_DOUT         | 02       | St/B   | USIC0 Channel 1 Shift Data Output             |

|       | U0C0_DOUT         | O3       | St/B   | USIC0 Channel 0 Shift Data Output             |

|       | CCU62_<br>CCPOS1A | 1        | St/B   | CCU62 Position Input 1                        |

|       | TMS_C             | I        | St/B   | JTAG Test Mode Selection Input                |

|       | U0C1_DX0F         | I        | St/B   | USIC0 Channel 1 Shift Data Input              |

| 8     | P7.1              | O0 / I   | St/B   | Bit 1 of Port 7, General Purpose Input/Output |

|       | EXTCLK            | 01       | St/B   | Programmable Clock Signal Output              |

|       | TxDC4             | 02       | St/B   | CAN Node 4 Transmit Data Output               |

|       | CCU62_<br>CTRAPA  | I        | St/B   | CCU62 Emergency Trap Input                    |

|       | BRKIN_C           | I        | St/B   | OCDS Break Signal Input                       |

| 9     | P7.4              | O0 / I   | St/B   | Bit 4 of Port 7, General Purpose Input/Output |

|       | EMUX2             | 01       | St/B   | External Analog MUX Control Output 2 (ADC1)   |

|       | U0C1_DOUT         | 02       | St/B   | USIC0 Channel 1 Shift Data Output             |

|       | U0C1_<br>SCLKOUT  | O3       | St/B   | USIC0 Channel 1 Shift Clock Output            |

|       | CCU62_<br>CCPOS2A | 1        | St/B   | CCU62 Position Input 2                        |

|       | TCK_C             | I        | St/B   | JTAG Clock Input                              |

|       | U0C0_DX0D         | I        | St/B   | USIC0 Channel 0 Shift Data Input              |

|       | U0C1_DX1E         | I        | St/B   | USIC0 Channel 1 Shift Clock Input             |

| 11    | P6.0              | O0 / I   | St/A   | Bit 0 of Port 6, General Purpose Input/Output |

|       | EMUX0             | 01       | St/A   | External Analog MUX Control Output 0 (ADC0)   |

|       | BRKOUT            | O3       | St/A   | OCDS Break Signal Output                      |

|       | ADCx_<br>REQGTyC  | I        | St/A   | External Request Gate Input for ADC0/1        |

|       | U1C1_DX0E         | I        | St/A   | USIC1 Channel 1 Shift Data Input              |

| Table | Table 4Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |  |  |

|-------|-----------------------------------------------|--------|------|------------------------------------------------|--|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                       |  |  |  |  |

| 60    | P10.1                                         | O0 / I | St/B | Bit 1 of Port 10, General Purpose Input/Output |  |  |  |  |

|       | U0C0_DOUT                                     | 01     | St/B | USIC0 Channel 0 Shift Data Output              |  |  |  |  |

|       | CCU60_<br>CC61                                | 02 / 1 | St/B | CCU60 Channel 1 Input/Output                   |  |  |  |  |

|       | AD1                                           | OH/I   | St/B | External Bus Interface Address/Data Line 1     |  |  |  |  |

|       | U0C0_DX0B                                     | I      | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |  |

|       | U0C0_DX1A                                     | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |  |  |

| 61    | P0.3                                          | O0 / I | St/B | Bit 3 of Port 0, General Purpose Input/Output  |  |  |  |  |

|       | U1C0_<br>SELO0                                | 01     | St/B | USIC1 Channel 0 Select/Control 0 Output        |  |  |  |  |

|       | U1C1_<br>SELO1                                | 02     | St/B | USIC1 Channel 1 Select/Control 1 Output        |  |  |  |  |

|       | CCU61_<br>COUT60                              | O3     | St/B | CCU61 Channel 0 Output                         |  |  |  |  |

|       | A3                                            | OH     | St/B | External Bus Interface Address Line 3          |  |  |  |  |

|       | U1C0_DX2A                                     | I      | St/B | USIC1 Channel 0 Shift Control Input            |  |  |  |  |

|       | RxDC0B                                        | I      | St/B | CAN Node 0 Receive Data Input                  |  |  |  |  |

| 62    | P10.2                                         | O0 / I | St/B | Bit 2 of Port 10, General Purpose Input/Output |  |  |  |  |

|       | U0C0_<br>SCLKOUT                              | 01     | St/B | USIC0 Channel 0 Shift Clock Output             |  |  |  |  |

|       | CCU60_<br>CC62                                | 02 / I | St/B | CCU60 Channel 2 Input/Output                   |  |  |  |  |

|       | AD2                                           | OH/I   | St/B | External Bus Interface Address/Data Line 2     |  |  |  |  |

|       | U0C0_DX1B                                     | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |  |  |

| PinSymbolCtrl.TypeFunction71P0.6O0 / ISt/BBit 6 of Port 0, General Purpose Input/Output11U1C1_DOUTO1St/BUSIC1 Channel 1 Shift Data OutputTxDC1O2St/BCAN Node 1 Transmit Data OutputCCU61_O3St/BCCU61 Channel 3 OutputCOUT63A6OHSt/BExternal Bus Interface Address Line 6U1C1_DX0AISt/BUSIC1 Channel 1 Shift Data InputCCU61_ISt/BCCU61 Emergency Trap InputCTRAPAISt/BUSIC1 Channel 1 Shift Clock Input72P10.6O0 / ISt/BUSIC0 Channel 0 Shift Data OutputU1C0_DOUTO1St/BUSIC0 Channel 0 Shift Data OutputTxDC4O2St/BUSIC1 Channel 1 Shift Clock Input72P10.6O0 / ISt/BUSIC0 Channel 0 Shift Data OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data InputU1C0_DDXC1ISt/BUSIC0 Channel 0 Shift Data InputU1C1_DDUTO1St/BUSIC1 Channel 0 Shift Control InputCCU60_ISt/BUSIC0 Channel 0 Shift Data OutputU0C1_DDUCISt/BUSIC0 Channel 0 Shift Data OutputTxDC4O2St/BCCU60 Emergency Trap InputCTRAPAISt/BUSIC0 Channel 0 Shift Data Output <th>Table</th> <th>e 4 Pin De</th> <th>finitior</th> <th>ns and</th> <th>Functions (cont'd)</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table | e 4 Pin De | finitior | ns and | Functions (cont'd)                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|----------|--------|------------------------------------------------|

| U1C1_DOUT         O1         St/B         USIC1 Channel 1 Shift Data Output           TxDC1         O2         St/B         CAN Node 1 Transmit Data Output           CCU61_<br>COUT63         O3         St/B         CCU61 Channel 3 Output           A6         OH         St/B         External Bus Interface Address Line 6           U1C1_DX0A         I         St/B         CCU61 Emergency Trap Input           CTRAPA         I         St/B         CCU61 Emergency Trap Input           TXDC4         O2         St/B         USIC1 Channel 1 Shift Data Input           T2         P10.6         O0 / I         St/B         Bit 6 of Port 10, General Purpose Input/Output           U0C0_DOUT         O1         St/B         USIC0 Channel 0 Shift Data Output           TXDC4         O2         St/B         CAN Node 4 Transmit Data Output           U1C0_         O3         St/B         USIC1 Channel 0 Shift Data Input           U1C0_         O3         St/B         USIC1 Channel 0 Shift Data Input           U1C0_DX0C         I         St/B         USIC1 Channel 0 Shift Data Input           U1C0_DX0ZD         I         St/B         USIC1 Channel 0 Shift Data Input           U1C0_DX0ZD         I         St/B         USIC1 Channel 0 Shift Control Inpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pin   | Symbol     | Ctrl.    | Туре   | Function                                       |

| TxDC1O2St/BCAN Node 1 Transmit Data OutputCCU61<br>COUT63O3St/BCCU61 Channel 3 OutputA6OHSt/BExternal Bus Interface Address Line 6U1C1_DX0AISt/BUSIC1 Channel 1 Shift Data InputCCU61_<br>CTRAPAISt/BCCU61 Emergency Trap Input72P10.6O0 / ISt/BUSIC1 Channel 1 Shift Clock Input72P10.6O0 / ISt/BUSIC0 Channel 0 Shift Data OutputTxDC4O2St/BUSIC1 Channel 0 Shift Data OutputTxDC4O2St/BUSIC1 Channel 0 Shift Data OutputTxDC4O2St/BUSIC1 Channel 0 Shift Data OutputU1C0_<br>SELO0O3St/BUSIC1 Channel 0 Shift Data OutputTxDC4O2St/BUSIC1 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71    | P0.6       | O0 / I   | St/B   | Bit 6 of Port 0, General Purpose Input/Output  |

| CCU61_<br>COUT63O3St/BCCU61 Channel 3 OutputA6OHSt/BExternal Bus Interface Address Line 6U1C1_DX0AISt/BUSIC1 Channel 1 Shift Data InputCCU61_<br>CTRAPAISt/BCCU61 Emergency Trap Input72P10.6O0 / ISt/BUSIC1 Channel 1 Shift Clock Input72P10.6O0 / ISt/BUSIC0 Channel 0 Shift Data Output74U0C0_DOUTO1St/BUSIC0 Channel 0 Shift Data Output75V1C0_<br>SELO0O3St/BUSIC1 Channel 0 Shift Data Output76V1C0_<br>SELO0O3St/BUSIC1 Channel 0 Shift Data Output77V1C0_<br>SELO0O3St/BUSIC1 Channel 0 Shift Data Output78V1C0_<br>SELO0O3St/BUSIC1 Channel 0 Shift Data Input73P10.7O0 / ISt/BUSIC1 Channel 0 Shift Data Input73P10.7O0 / ISt/BUSIC0 Channel 1 Shift Data Output73P10.7O1 / ISt/BUSIC0 Channel 3 Output74AD7OH / ISt/BUSIC0 Channel 3 Output75P10.7O1 / ISt/BUSIC0 Channel 3 Output76CU60_<br>COUT63O2St/BCCU60 Channel 3 Output77O4 / ISt/BUSIC0 Channel 3 Output78P10.7OH / ISt/BUSIC0 Channel 3 Output79CU60_<br>COUT63O2St/BCCU60 Channel 3 Output74O4 / ISt/BUSIC0 Channel 3 Outp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | U1C1_DOUT  | 01       | St/B   | USIC1 Channel 1 Shift Data Output              |

| COUT63         Image: String Stri        |       | TxDC1      | 02       | St/B   | CAN Node 1 Transmit Data Output                |

| U1C1_DX0AISt/BUSIC1 Channel 1 Shift Data InputCCU61_<br>CTRAPAISt/BCCU61 Emergency Trap Input72P10.6O0 / ISt/BBit 6 of Port 10, General Purpose Input/Output72P10.6O0 / ISt/BUSIC0 Channel 0 Shift Data Output72P10.6O2St/BCAN Node 4 Transmit Data Output73V1C0_<br>SELOOO3St/BUSIC1 Channel 0 Shift Data Input74O20_DXUCISt/BUSIC1 Channel 0 Shift Data Input73P10.7O0 / ISt/BUSIC1 Channel 1 Shift Data Output73P10.7O0 / ISt/BUSIC0 Channel 1 Shift Data Output74OC1_DOUTO1St/BUSIC1 Channel 0 Shift Data Input75P10.7O0 / ISt/BUSIC0 Channel 1 Shift Data Output74OC1_DOUTO1St/BUSIC0 Channel 1 Shift Data Output75P10.7O0 / ISt/BUSIC0 Channel 1 Shift Data Output76OC1_DOUTO1St/BUSIC0 Channel 1 Shift Data Output77OU1St/BUSIC0 Channel 1 Shift Data Output78P10.7OH / ISt/BUSIC0 Channel 3 Output79OU1_DOUTO1St/BUSIC0 Channel 3 Output70OH / ISt/BUSIC0 Channel 1 Shift Data Input71OC1_DX0BISt/BUSIC0 Channel 1 Shift Data Input72OUC1_DX0BISt/BUSIC0 Channel 1 Shift Data Input73OUC1_DX0B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | _          | O3       | St/B   | CCU61 Channel 3 Output                         |

| CCU61_<br>CTRAPAISt/BCCU61 Emergency Trap Input72P10.6O0 / ISt/BUSIC1 Channel 1 Shift Clock Input72P10.6O0 / ISt/BBit 6 of Port 10, General Purpose Input/Output74U0C0_DOUTO1St/BUSIC0 Channel 0 Shift Data Output75TxDC4O2St/BCAN Node 4 Transmit Data Output76U1C0_<br>SELOOO3St/BUSIC1 Channel 0 Select/Control 0 Output76AD6OH / ISt/BUSIC0 Channel 0 Shift Data Input77U1C0_DX0CISt/BUSIC0 Channel 0 Shift Data Input78U1C0_DX2DISt/BUSIC1 Channel 0 Shift Control Input73P10.7O0 / ISt/BCCU60 Emergency Trap Input73P10.7O0 / ISt/BUSIC0 Channel 1 Shift Data Output74U0C1_DOUTO1St/BUSIC0 Channel 3 Output75P10.7OH / ISt/BCCU60 Channel 3 Output76OH / ISt/BUSIC0 Channel 3 Output77OH / ISt/BUSIC0 Channel 3 Output78P10.7OH / ISt/BCCU60 Channel 3 Output79P10.7OI / St/BUSIC0 Channel 1 Shift Data Input70CU60_<br>COUT63ISt/BCCU60 Channel 3 Output79P10.7OH / ISt/BUSIC0 Channel 1 Shift Data Input70CU60_<br>COUT63ISt/BUSIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | A6         | OH       | St/B   | External Bus Interface Address Line 6          |

| CTRAPAISt/BUSIC1 Channel 1 Shift Clock Input72P10.6O0 / ISt/BBit 6 of Port 10, General Purpose Input/Output10C0_DOUTO1St/BUSIC0 Channel 0 Shift Data Output1xDC4O2St/BCAN Node 4 Transmit Data Output1xDC4O2St/BUSIC1 Channel 0 Select/Control 0 Output1C0_SELO0O3St/BUSIC1 Channel 0 Select/Control 0 OutputAD6OH / ISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Control InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputU1C1_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>CU163ISt/BCCU60 Emergency Trap Input73P10.7O0 / ISt/BUSIC0 Channel 1 Shift Data OutputU0C1_DOUTO1St/BUSIC0 Channel 3 OutputCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BUSIC0 Channel 1 Shift Data InputU0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCU60_<br>CCPOS0AISt/BUSIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | U1C1_DX0A  | 1        | St/B   | USIC1 Channel 1 Shift Data Input               |

| 72P10.6O0 / ISt/BBit 6 of Port 10, General Purpose Input/OutputU0C0_DOUTO1St/BUSIC0 Channel 0 Shift Data OutputTxDC4O2St/BCAN Node 4 Transmit Data OutputU1C0_<br>SELO0O3St/BUSIC1 Channel 0 Select/Control 0 OutputAD6OH / ISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>CTRAPAISt/BUSIC1 Channel 0 Shift Control Input73P10.7O0 / ISt/BUSIC0 Channel 1 Shift Data OutputU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 1 Shift Data OutputAD7OH / ISt/BUSIC0 Channel 3 OutputOC1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | _          | I        | St/B   | CCU61 Emergency Trap Input                     |

| U0C0_DOUTO1St/BUSIC0 Channel 0 Shift Data OutputTxDC4O2St/BCAN Node 4 Transmit Data OutputU1C0_<br>SELO0O3St/BUSIC1 Channel 0 Select/Control 0 OutputAD6OH / ISt/BUSIC1 Channel 0 Select/Control 0 OutputU0C0_DX0CISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>CTRAPAISt/BUSIC1 Channel 0 Shift Control Input73P10.7O0 / ISt/BBit 7 of Port 10, General Purpose Input/OutputU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BUSIC0 Channel 3 OutputOC1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | U1C1_DX1B  | I        | St/B   | USIC1 Channel 1 Shift Clock Input              |

| TxDC4O2St/BCAN Node 4 Transmit Data OutputU1C0_<br>SELO0O3St/BUSIC1 Channel 0 Select/Control 0 OutputAD6OH / ISt/BExternal Bus Interface Address/Data Line 6U0C0_DX0CISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>CTRAPAISt/BCCU60 Emergency Trap Input73P10.7O0 / ISt/BUSIC0 Channel 1 Shift Data OutputU0C1_DOUTO1St/BUSIC0 Channel 3 OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>COUT63OH / ISt/BCCU60 Channel 3 OutputAD7OH / ISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BUSIC0 Channel 1 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 72    | P10.6      | O0 / I   | St/B   | Bit 6 of Port 10, General Purpose Input/Output |

| U1C0_<br>SELO0O3St/BUSIC1 Channel 0 Select/Control 0 OutputAD6OH / ISt/BExternal Bus Interface Address/Data Line 6U0C0_DX0CISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>CTRAPAISt/BCCU60 Emergency Trap Input73P10.7O0 / ISt/BBit 7 of Port 10, General Purpose Input/OutputU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>COUT63ISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | U0C0_DOUT  | 01       | St/B   | USIC0 Channel 0 Shift Data Output              |

| SELOOImage: SELOOSELOOAD6OH/ISt/BExternal Bus Interface Address/Data Line 6U0C0_DX0CISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>CTRAPAISt/BCCU60 Emergency Trap Input73P10.7O0 / ISt/BBit 7 of Port 10, General Purpose Input/OutputU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | TxDC4      | 02       | St/B   | CAN Node 4 Transmit Data Output                |

| U0C0_DX0CISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>CTRAPAISt/BCCU60 Emergency Trap Input73P10.7O0 / ISt/BBit 7 of Port 10, General Purpose Input/OutputU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BCCU60 Position Input 0CCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | _          | O3       | St/B   | USIC1 Channel 0 Select/Control 0 Output        |

| U1C0_DX2DISt/BUSIC1 Channel 0 Shift Control InputCCU60_<br>CTRAPAISt/BCCU60 Emergency Trap Input73P10.7O0 / ISt/BBit 7 of Port 10, General Purpose Input/OutputU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | AD6        | OH/I     | St/B   | External Bus Interface Address/Data Line 6     |

| CCU60_<br>CTRAPAISt/BCCU60 Emergency Trap Input73P10.7O0 / ISt/BBit 7 of Port 10, General Purpose Input/OutputU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       | U0C0_DX0C  | 1        | St/B   | USIC0 Channel 0 Shift Data Input               |

| CTRAPACTRAPA73P10.7O0 / ISt/BBit 7 of Port 10, General Purpose Input/OutputU0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | U1C0_DX2D  | 1        | St/B   | USIC1 Channel 0 Shift Control Input            |

| U0C1_DOUTO1St/BUSIC0 Channel 1 Shift Data OutputCCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | _          | I        | St/B   | CCU60 Emergency Trap Input                     |

| CCU60_<br>COUT63O2St/BCCU60 Channel 3 OutputAD7OH / ISt/BExternal Bus Interface Address/Data Line 7U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73    | P10.7      | O0 / I   | St/B   | Bit 7 of Port 10, General Purpose Input/Output |

| COUT63Image: Courtest of the second seco |       | U0C1_DOUT  | 01       | St/B   | USIC0 Channel 1 Shift Data Output              |

| U0C1_DX0BISt/BUSIC0 Channel 1 Shift Data InputCCU60_<br>CCPOS0AISt/BCCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | _          | O2       | St/B   | CCU60 Channel 3 Output                         |

| CCU60_     I     St/B     CCU60 Position Input 0       CCPOS0A     I     St/B     CCU60 Position Input 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | AD7        | OH/I     | St/B   | External Bus Interface Address/Data Line 7     |

| CCPOSOA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | U0C1_DX0B  | I        | St/B   | USIC0 Channel 1 Shift Data Input               |

| RxDC4C   I   St/B   CAN Node 4 Receive Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | _          | I        | St/B   | CCU60 Position Input 0                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | RxDC4C     | I        | St/B   | CAN Node 4 Receive Data Input                  |

| Table | e 4 Pin De       | finition | is and | Functions (cont'd)                              |

|-------|------------------|----------|--------|-------------------------------------------------|

| Pin   | Symbol           | Ctrl.    | Туре   | Function                                        |

| 83    | P10.11           | O0 / I   | St/B   | Bit 11 of Port 10, General Purpose Input/Output |

|       | U1C0_<br>SCLKOUT | 01       | St/B   | USIC1 Channel 0 Shift Clock Output              |

|       | BRKOUT           | O2       | St/B   | OCDS Break Signal Output                        |

|       | AD11             | OH/I     | St/B   | External Bus Interface Address/Data Line 11     |

|       | U1C0_DX1D        | I        | St/B   | USIC1 Channel 0 Shift Clock Input               |

|       | RxDC2B           | I        | St/B   | CAN Node 2 Receive Data Input                   |

|       | TMS_B            | I        | St/B   | JTAG Test Mode Selection Input                  |

| 84    | P1.2             | O0 / I   | St/B   | Bit 2 of Port 1, General Purpose Input/Output   |

|       | CCU62_<br>CC62   | 01 / I   | St/B   | CCU62 Channel 2 Input/Output                    |

|       | U1C0_<br>SELO6   | O2       | St/B   | USIC1 Channel 0 Select/Control 6 Output         |

|       | U2C1_<br>SCLKOUT | O3       | St/B   | USIC2 Channel 1 Shift Clock Output              |

|       | A10              | OH       | St/B   | External Bus Interface Address Line 10          |

|       | ESR1_4           | I        | St/B   | ESR1 Trigger Input 4                            |

|       | CCU61_<br>T12HRB | 1        | St/B   | External Run Control Input for T12 of CCU61     |

|       | EX2AINA          | I        | St/B   | External Interrupt Trigger Input                |

|       | U2C1_DX0D        | I        | St/B   | USIC2 Channel 1 Shift Data Input                |

|       | U2C1_DX1C        | I        | St/B   | USIC2 Channel 1 Shift Clock Input               |

| 85    | P10.12           | O0 / I   | St/B   | Bit 12 of Port 10, General Purpose Input/Output |

|       | U1C0_DOUT        | 01       | St/B   | USIC1 Channel 0 Shift Data Output               |

|       | TxDC2            | 02       | St/B   | CAN Node 2 Transmit Data Output                 |

|       | TDO_B            | O3       | St/B   | JTAG Test Data Output                           |

|       | AD12             | OH/I     | St/B   | External Bus Interface Address/Data Line 12     |

|       | U1C0_DX0C        | I        | St/B   | USIC1 Channel 0 Shift Data Input                |

|       | U1C0_DX1E        | I        | St/B   | USIC1 Channel 0 Shift Clock Input               |

### **General Device Information**

2) Pin TRef was used to control the core voltage generation in step AA. For that step, pin TRef must be connected to *V*<sub>DDPB</sub>.

This connection is no more required from step AB on. For the current step, pin TRef is logically not connected. Future derivatives will feature an additional general purpose IO pin at this position.

## 3 Functional Description

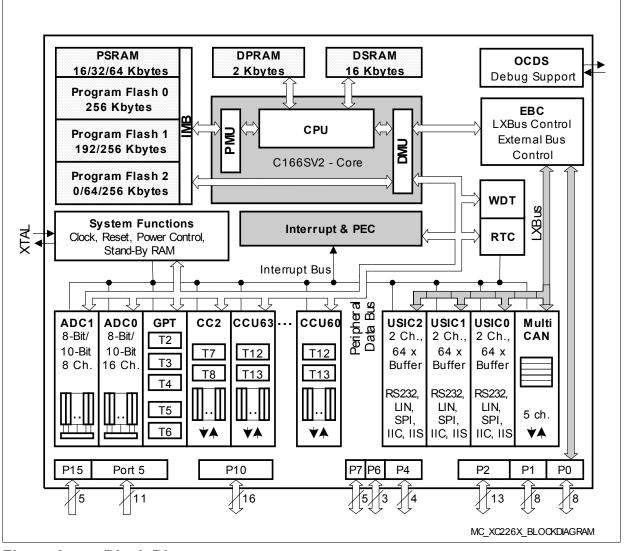

The architecture of the XC226x combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources (see **Figure 3**). This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC226x.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC226x.

Figure 3 Block Diagram

With this hardware most XC226x instructions can be executed in a single machine cycle of 12.5 ns with an 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 wordwide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XC226x instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

The XC226x includes an excellent mechanism to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate non-maskable system reaction similar to a standard interrupt service (branching to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

Table 7 shows all possible exceptions or error conditions that can arise during runtime:

| Exception Condition                                                                                                                                                                                            | Trap<br>Flag                              | Trap<br>Vector                            | Vector<br>Location <sup>1)</sup>                                                                                                             | Trap<br>Number                                                           | Trap<br>Priority           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------|

| Reset Functions                                                                                                                                                                                                | -                                         | RESET                                     | xx'0000 <sub>H</sub>                                                                                                                         | 00 <sub>H</sub>                                                          | 111                        |

| <ul> <li>Class A Hardware Traps:</li> <li>System Request 0</li> <li>Stack Overflow</li> <li>Stack Underflow</li> <li>Software Break</li> </ul>                                                                 | SR0<br>STKOF<br>STKUF<br>SOFTBRK          | SR0TRAP<br>STOTRAP<br>STUTRAP<br>SBRKTRAP | xx'0008 <sub>H</sub><br>xx'0010 <sub>H</sub><br>xx'0018 <sub>H</sub><br>xx'0020 <sub>H</sub>                                                 | 02 <sub>H</sub><br>04 <sub>H</sub><br>06 <sub>H</sub><br>08 <sub>H</sub> | <br>  <br>  <br>           |

| <ul> <li>Class B Hardware Traps:</li> <li>System Request 1</li> <li>Undefined Opcode</li> <li>Memory Access Error</li> <li>Protected Instruction<br/>Fault</li> <li>Illegal Word Operand<br/>Access</li> </ul> | SR1<br>UNDOPC<br>ACER<br>PRTFLT<br>ILLOPA | BTRAP<br>BTRAP<br>BTRAP<br>BTRAP<br>BTRAP | xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub><br>xx'0028 <sub>H</sub> | 0A <sub>H</sub><br>0A <sub>H</sub><br>0A <sub>H</sub><br>0A <sub>H</sub> | <br> <br> <br>             |

| Reserved                                                                                                                                                                                                       | -                                         | -                                         | [2C <sub>H</sub> - 3C <sub>H</sub> ]                                                                                                         | [0B <sub>H</sub> -<br>0F <sub>H</sub> ]                                  | _                          |