Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| ipplier Device Package   | PG-LQFP-100-3 https://www.e-xfl.com/product-detail/infineon-technologies/xc226756f66lackxuma |

|--------------------------|----------------------------------------------------------------------------------------------|

| kage / Case              | 100-LQFP Exposed Pad                                                                         |

| inting Type              | Surface Mount                                                                                |

| erating Temperature      | -40°C ~ 125°C (TA)                                                                           |

| cillator Type            | Internal                                                                                     |

| ata Converters           | A/D 16x8/10b                                                                                 |

| ltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                                    |

| 1 Size                   | 34K x 8                                                                                      |

| PROM Size                | -                                                                                            |

| gram Memory Type         | FLASH                                                                                        |

| ogram Memory Size        | 448KB (448K x 8)                                                                             |

| ber of I/O               | 75                                                                                           |

| ipherals                 | DMA, I²S, POR, PWM, WDT                                                                      |

| nnectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                         |

| eed                      | 66MHz                                                                                        |

| re Size                  | 16/32-Bit                                                                                    |

| re Processor             | C166SV2                                                                                      |

| oduct Status             | Discontinued at Digi-Key                                                                     |

## XC226x

16/32-Bit Single-Chip Microcontroller with 32-Bit Performance

Microcontrollers

| 1                                                                                                                         | Summary of Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1                                                                                                           | General Device Information       8         Pin Configuration and Definition       9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17 | Functional Description         33           Memory Subsystem and Organization         32           External Bus Controller         35           Central Processing Unit (CPU)         36           Interrupt System         38           On-Chip Debug Support (OCDS)         44           Capture/Compare Unit (CAPCOM2)         45           Capture/Compare Units CCU6x         48           General Purpose Timer (GPT12E) Unit         50           Real Time Clock         54           A/D Converters         56           Universal Serial Interface Channel Modules (USIC)         57           MultiCAN Module         59           Watchdog Timer         67           Clock Generation         67           Parallel Ports         62           Power Management         64           Instruction Set Summary         65 |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5<br>4.6.1<br>4.6.2<br>4.6.3<br>4.6.4<br>4.6.5<br>4.6.5<br>4.6.6 | Electrical Parameters68General Parameters68DC Parameters72DC Parameters for Upper Voltage Area74DC Parameters for Lower Voltage Area76Power Consumption78Analog/Digital Converter Parameters83System Parameters86Flash Memory Parameters86AC Parameters96Testing Waveforms96Definition of Internal Timing97External Clock Input Parameters96External Bus Timing98Synchronous Serial Interface Timing106JTAG Interface Timing106                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>5</b><br>5.1<br>5.2                                                                                                    | Package and Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Data Sheet 3 V2.1, 2008-08

## **General Device Information**

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                      |

|-----|-------------------|--------|------|-----------------------------------------------|

| 7   | P7.3              | O0 / I | St/B | Bit 3 of Port 7, General Purpose Input/Output |

|     | EMUX1             | 01     | St/B | External Analog MUX Control Output 1 (ADC1)   |

|     | U0C1_DOUT         | O2     | St/B | USIC0 Channel 1 Shift Data Output             |

|     | U0C0_DOUT         | О3     | St/B | USIC0 Channel 0 Shift Data Output             |

|     | CCU62_<br>CCPOS1A | I      | St/B | CCU62 Position Input 1                        |

|     | TMS_C             | I      | St/B | JTAG Test Mode Selection Input                |

|     | U0C1_DX0F         | I      | St/B | USIC0 Channel 1 Shift Data Input              |

| 8   | P7.1              | O0 / I | St/B | Bit 1 of Port 7, General Purpose Input/Output |

|     | EXTCLK            | 01     | St/B | Programmable Clock Signal Output              |

|     | TxDC4             | O2     | St/B | CAN Node 4 Transmit Data Output               |

|     | CCU62_<br>CTRAPA  | I      | St/B | CCU62 Emergency Trap Input                    |

|     | BRKIN_C           | I      | St/B | OCDS Break Signal Input                       |

| 9   | P7.4              | O0 / I | St/B | Bit 4 of Port 7, General Purpose Input/Output |

|     | EMUX2             | 01     | St/B | External Analog MUX Control Output 2 (ADC1)   |

|     | U0C1_DOUT         | O2     | St/B | USIC0 Channel 1 Shift Data Output             |

|     | U0C1_<br>SCLKOUT  | О3     | St/B | USIC0 Channel 1 Shift Clock Output            |

|     | CCU62_<br>CCPOS2A | I      | St/B | CCU62 Position Input 2                        |

|     | TCK_C             | I      | St/B | JTAG Clock Input                              |

|     | U0C0_DX0D         | I      | St/B | USIC0 Channel 0 Shift Data Input              |

|     | U0C1_DX1E         | I      | St/B | USIC0 Channel 1 Shift Clock Input             |

| 11  | P6.0              | O0 / I | St/A | Bit 0 of Port 6, General Purpose Input/Output |

|     | EMUX0             | 01     | St/A | External Analog MUX Control Output 0 (ADC0)   |

|     | BRKOUT            | О3     | St/A | OCDS Break Signal Output                      |

|     | ADCx_<br>REQGTyC  | I      | St/A | External Request Gate Input for ADC0/1        |

|     | U1C1_DX0E         | I      | St/A | USIC1 Channel 1 Shift Data Input              |

## **General Device Information**

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

| 68  | P0.5             | O0 / I | St/B | Bit 5 of Port 0, General Purpose Input/Output  |

|     | U1C1_<br>SCLKOUT | 01     | St/B | USIC1 Channel 1 Shift Clock Output             |

|     | U1C0_<br>SELO2   | O2     | St/B | USIC1 Channel 0 Select/Control 2 Output        |

|     | CCU61_<br>COUT62 | О3     | St/B | CCU61 Channel 2 Output                         |

|     | A5               | ОН     | St/B | External Bus Interface Address Line 5          |

|     | U1C1_DX1A        | I      | St/B | USIC1 Channel 1 Shift Clock Input              |

|     | U1C0_DX1C        | I      | St/B | USIC1 Channel 0 Shift Clock Input              |

| 69  | P10.4            | O0 / I | St/B | Bit 4 of Port 10, General Purpose Input/Output |

|     | U0C0_<br>SELO3   | 01     | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CCU60_<br>COUT61 | O2     | St/B | CCU60 Channel 1 Output                         |

|     | AD4              | OH/I   | St/B | External Bus Interface Address/Data Line 4     |

|     | U0C0_DX2B        | I      | St/B | USIC0 Channel 0 Shift Control Input            |

|     | U0C1_DX2B        | I      | St/B | USIC0 Channel 1 Shift Control Input            |

| 70  | P10.5            | O0 / I | St/B | Bit 5 of Port 10, General Purpose Input/Output |

|     | U0C1_<br>SCLKOUT | 01     | St/B | USIC0 Channel 1 Shift Clock Output             |

|     | CCU60_<br>COUT62 | O2     | St/B | CCU60 Channel 2 Output                         |

|     | AD5              | OH/I   | St/B | External Bus Interface Address/Data Line 5     |

|     | U0C1_DX1B        | I      | St/B | USIC0 Channel 1 Shift Clock Input              |

Data Sheet 21 V2.1, 2008-08

## **General Device Information**

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Type | Function                                       |

|-----|-------------------|--------|------|------------------------------------------------|

| 71  | P0.6              | O0 / I | St/B | Bit 6 of Port 0, General Purpose Input/Output  |

|     | U1C1_DOUT         | 01     | St/B | USIC1 Channel 1 Shift Data Output              |

|     | TxDC1             | 02     | St/B | CAN Node 1 Transmit Data Output                |

|     | CCU61_<br>COUT63  | О3     | St/B | CCU61 Channel 3 Output                         |

|     | A6                | ОН     | St/B | External Bus Interface Address Line 6          |

|     | U1C1_DX0A         | 1      | St/B | USIC1 Channel 1 Shift Data Input               |

|     | CCU61_<br>CTRAPA  | I      | St/B | CCU61 Emergency Trap Input                     |

|     | U1C1_DX1B         | I      | St/B | USIC1 Channel 1 Shift Clock Input              |

| 72  | P10.6             | O0 / I | St/B | Bit 6 of Port 10, General Purpose Input/Output |

|     | U0C0_DOUT         | 01     | St/B | USIC0 Channel 0 Shift Data Output              |

|     | TxDC4             | O2     | St/B | CAN Node 4 Transmit Data Output                |

|     | U1C0_<br>SELO0    | О3     | St/B | USIC1 Channel 0 Select/Control 0 Output        |

|     | AD6               | OH/I   | St/B | External Bus Interface Address/Data Line 6     |

|     | U0C0_DX0C         | I      | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U1C0_DX2D         | I      | St/B | USIC1 Channel 0 Shift Control Input            |

|     | CCU60_<br>CTRAPA  | I      | St/B | CCU60 Emergency Trap Input                     |

| 73  | P10.7             | O0 / I | St/B | Bit 7 of Port 10, General Purpose Input/Output |

|     | U0C1_DOUT         | 01     | St/B | USIC0 Channel 1 Shift Data Output              |

|     | CCU60_<br>COUT63  | O2     | St/B | CCU60 Channel 3 Output                         |

|     | AD7               | OH/I   | St/B | External Bus Interface Address/Data Line 7     |

|     | U0C1_DX0B         | I      | St/B | USIC0 Channel 1 Shift Data Input               |

|     | CCU60_<br>CCPOS0A | 1      | St/B | CCU60 Position Input 0                         |

|     | RxDC4C            | 1      | St/B | CAN Node 4 Receive Data Input                  |

## **General Device Information**

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                        |

|-----|------------------|--------|------|-------------------------------------------------|

| 83  | P10.11           | O0 / I | St/B | Bit 11 of Port 10, General Purpose Input/Output |

|     | U1C0_<br>SCLKOUT | 01     | St/B | USIC1 Channel 0 Shift Clock Output              |

|     | BRKOUT           | O2     | St/B | OCDS Break Signal Output                        |

|     | AD11             | OH/I   | St/B | External Bus Interface Address/Data Line 11     |

|     | U1C0_DX1D        | I      | St/B | USIC1 Channel 0 Shift Clock Input               |

|     | RxDC2B           | I      | St/B | CAN Node 2 Receive Data Input                   |

|     | TMS_B            | I      | St/B | JTAG Test Mode Selection Input                  |

| 84  | P1.2             | O0 / I | St/B | Bit 2 of Port 1, General Purpose Input/Output   |

|     | CCU62_<br>CC62   | O1 / I | St/B | CCU62 Channel 2 Input/Output                    |

|     | U1C0_<br>SELO6   | O2     | St/B | USIC1 Channel 0 Select/Control 6 Output         |

|     | U2C1_<br>SCLKOUT | O3     | St/B | USIC2 Channel 1 Shift Clock Output              |

|     | A10              | ОН     | St/B | External Bus Interface Address Line 10          |

|     | ESR1_4           | I      | St/B | ESR1 Trigger Input 4                            |

|     | CCU61_<br>T12HRB | I      | St/B | External Run Control Input for T12 of CCU61     |

|     | EX2AINA          | I      | St/B | External Interrupt Trigger Input                |

|     | U2C1_DX0D        | I      | St/B | USIC2 Channel 1 Shift Data Input                |

|     | U2C1_DX1C        | I      | St/B | USIC2 Channel 1 Shift Clock Input               |

| 85  | P10.12           | O0 / I | St/B | Bit 12 of Port 10, General Purpose Input/Output |

|     | U1C0_DOUT        | 01     | St/B | USIC1 Channel 0 Shift Data Output               |

|     | TxDC2            | O2     | St/B | CAN Node 2 Transmit Data Output                 |

|     | TDO_B            | О3     | St/B | JTAG Test Data Output                           |

|     | AD12             | OH/I   | St/B | External Bus Interface Address/Data Line 12     |

|     | U1C0_DX0C        | I      | St/B | USIC1 Channel 0 Shift Data Input                |

|     | U1C0_DX1E        | I      | St/B | USIC1 Channel 0 Shift Clock Input               |

#### **Functional Description**

With this hardware most XC226x instructions can be executed in a single machine cycle of 12.5 ns with an 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 word-wide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XC226x instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

Data Sheet 37 V2.1, 2008-08

## **Functional Description**

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the compare mode selected.

Data Sheet 46 V2.1, 2008-08

## **Functional Description**

#### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Up to five independent CAN nodes

- Up to 128 independent message objects (shared by the CAN nodes)

- · Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- · Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

## **Functional Description**

## 3.13 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz). The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

#### 3.14 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XC226x from a number of external or internal clock sources:

- External clock signals with pad or core voltage levels

- External crystal using the on-chip oscillator

- On-chip clock source for operation without crystal

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals or from the on-chip clock source. See also **Section 4.6.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

Data Sheet 61 V2.1, 2008-08

## **Functional Description**

#### 3.15 Parallel Ports

The XC226x provides up to 75 I/O lines which are organized into 7 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in **Table 9**.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

Table 9 Summary of the XC226x's Parallel Ports

| Port   | Width | Alternate Functions                                                                                                                                                                                     |

|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 0 | 8     | Address lines,<br>Serial interface lines of USIC1, CAN0, and CAN1,<br>Input/Output lines for CCU61                                                                                                      |

| Port 1 | 8     | Address lines, Serial interface lines of USIC1 and USIC2, Input/Output lines for CCU62, OCDS control, interrupts                                                                                        |

| Port 2 | 13    | Address and/or data lines, bus control, Serial interface lines of USIC0, CAN0, and CAN1, Input/Output lines for CCU60, CCU63, and CAPCOM2, Timer control signals, JTAG, interrupts, system clock output |

| Port 4 | 8     | Chip select signals, Serial interface lines of CAN2, Input/Output lines for CAPCOM2, Timer control signals                                                                                              |

| Port 5 | 16    | Analog input channels to ADC0, Input/Output lines for CCU6x, Timer control signals, JTAG, OCDS control, interrupts                                                                                      |

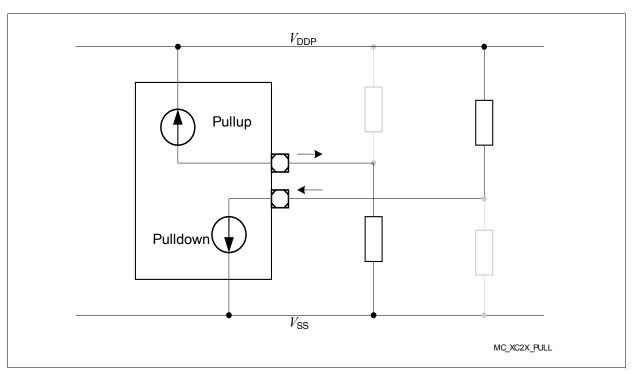

#### Pullup/Pulldown Device Behavior

Most pins of the XC226x feature pullup or pulldown devices. For some special pins these are fixed; for the port pins they can be selected by the application.

The specified current values indicate how to load the respective pin depending on the intended signal level. **Figure 12** shows the current paths.

The shaded resistors shown in the figure may be required to compensate system pull currents that do not match the given limit values.

Figure 12 Pullup/Pulldown Current Definition

Data Sheet 73 V2.1, 2008-08

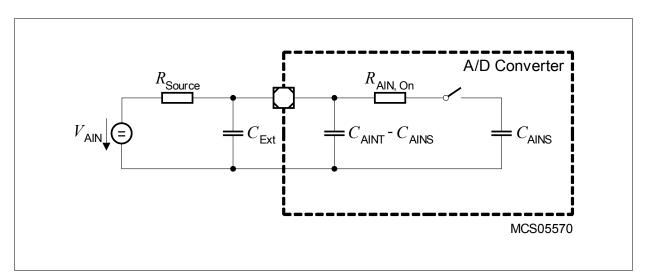

Table 18 A/D Converter Characteristics (cont'd) (Operating Conditions apply)

| Parameter                                   | Symbol      |    | Lim  | it Values | Unit | Test      |  |

|---------------------------------------------|-------------|----|------|-----------|------|-----------|--|

|                                             |             |    | Min. | Max.      |      | Condition |  |

| Switched capacitance of the reference input | $C_{AREFS}$ | CC | _    | 7         | pF   | 6)7)      |  |

| Resistance of the reference input path      | $R_{AREF}$  | CC | _    | 2         | kΩ   | 6)7)      |  |

- 1) TUE is tested at  $V_{\text{AREFx}} = V_{\text{DDPA}}$ ,  $V_{\text{AGND}} = 0 \text{ V}$ . It is verified by design for all other voltages within the defined voltage range.

- The specified TUE is valid only if the absolute sum of input overload currents on Port 5 or Port 15 pins (see  $I_{\rm OV}$  specification) does not exceed 10 mA, and if  $V_{\rm AREF}$  and  $V_{\rm AGND}$  remain stable during the measurement time.

- 2)  $V_{\text{AIN}}$  may exceed  $V_{\text{AGND}}$  or  $V_{\text{AREFx}}$  up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 3) The limit values for  $f_{ADCI}$  must not be exceeded when selecting the peripheral frequency and the prescaler setting.

- 4) This parameter includes the sample time (also the additional sample time specified by STC), the time to determine the digital result and the time to load the result register with the conversion result. Values for the basic clock t<sub>ADCI</sub> depend on programming and are found in Table 19.

- 5) The total unadjusted error TUE is the maximum deviation from the ideal ADC transfer curve, not the sum of individual errors.

- All error specifications are based on measurement methods standardized by IEEE 1241.2000.

- 6) Not subject to production test verified by design/characterization.

- 7) These parameter values cover the complete operating range. Under relaxed operating conditions (temperature, supply voltage) typical values can be used for calculation. At room temperature and nominal supply voltage the following typical values can be used:

$$C_{\mathsf{AINTtyp}}$$

= 12 pF,  $C_{\mathsf{AINStyp}}$  = 5 pF,  $R_{\mathsf{AINtyp}}$  = 1.0 k $\Omega$ ,  $C_{\mathsf{AREFTtyp}}$  = 15 pF,  $C_{\mathsf{AREFStyp}}$  = 10 pF,  $R_{\mathsf{AREFtyp}}$  = 1.0 k $\Omega$ .

Figure 15 Equivalent Circuitry for Analog Inputs

Data Sheet 84 V2.1, 2008-08

Sample time and conversion time of the XC226x's A/D converters are programmable. The timing above can be calculated using **Table 19**.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

Table 19 A/D Converter Computation Table

| GLOBCTR.5-0<br>(DIVA) | A/D Converter Analog Clock $f_{ADCI}$ | INPCRx.7-0<br>(STC) | Sample Time $t_{\rm S}$   |

|-----------------------|---------------------------------------|---------------------|---------------------------|

| 000000 <sub>B</sub>   | $f_{	exttt{SYS}}$                     | 00 <sub>H</sub>     | $t_{ADCI} \times 2$       |

| 000001 <sub>B</sub>   | $f_{SYS}$ / 2                         | 01 <sub>H</sub>     | $t_{ADCI} \times 3$       |

| 000010 <sub>B</sub>   | $f_{SYS}$ / 3                         | 02 <sub>H</sub>     | $t_{ADCI} \times 4$       |

| :                     | $f_{\rm SYS}$ / (DIVA+1)              | :                   | $t_{ADCI} \times (STC+2)$ |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                 | FE <sub>H</sub>     | $t_{ADCI} \times 256$     |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                 | FF <sub>H</sub>     | $t_{ADCI} 	imes 257$      |

## **Converter Timing Example A:**

Assumptions:  $f_{SYS}$  = 80 MHz (i.e.  $t_{SYS}$  = 12.5 ns), DIVA = 03<sub>H</sub>, STC = 00<sub>H</sub>

Analog clock  $f_{ADCI} = f_{SYS} / 4 = 20 \text{ MHz}$ , i.e.  $t_{ADCI} = 50 \text{ ns}$

Sample time  $t_S = t_{ADCI} \times 2 = 100 \text{ ns}$

Conversion 10-bit:

$t_{\text{C10}} = 13 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 13 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.675 \text{ }\mu\text{s}$

**Conversion 8-bit:**

$t_{\rm C8} = 11 \times t_{\rm ADCI} + 2 \times t_{\rm SYS} = 11 \times 50 \text{ ns} + 2 \times 12.5 \text{ ns} = 0.575 \text{ }\mu\text{s}$

## **Converter Timing Example B:**

Assumptions:  $f_{SYS}$  = 40 MHz (i.e.  $t_{SYS}$  = 25 ns), DIVA = 02<sub>H</sub>, STC = 03<sub>H</sub>

Analog clock  $f_{ADCI} = f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e.  $t_{ADCI} = 75 \text{ ns}$

Sample time  $t_{\rm S} = t_{\rm ADCI} \times 5 = 375 \text{ ns}$

Conversion 10-bit:

$t_{\text{C10}} = 16 \times t_{\text{ADCI}} + 2 \times t_{\text{SYS}} = 16 \times 75 \text{ ns} + 2 \times 25 \text{ ns} = 1.25 \text{ }\mu\text{s}$

**Conversion 8-bit:**

$t_{\text{C8}}$  = 14 ×  $t_{\text{ADCI}}$  + 2 ×  $t_{\text{SYS}}$  = 14 × 75 ns + 2 × 25 ns = 1.10  $\mu$ s

Data Sheet 85 V2.1, 2008-08

## 4.4 System Parameters

The following parameters specify several aspects which are important when integrating the XC226x into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Table 20 Various System Parameters

| Parameter                                                 | Symbol                 |                         | Values   | S                       | Unit | Note /                                                |  |

|-----------------------------------------------------------|------------------------|-------------------------|----------|-------------------------|------|-------------------------------------------------------|--|

|                                                           |                        | Min.                    | Тур.     | Max.                    |      | Test Condition                                        |  |

| Supply watchdog (SWD) supervision level (see Table 21)    | V <sub>SWD</sub><br>CC | V <sub>LV</sub> - 0.150 | $V_{LV}$ | V <sub>LV</sub> + 0.100 | V    | $V_{\rm LV}$ = selected voltage in upper voltage area |  |

|                                                           |                        | V <sub>LV</sub> - 0.125 | $V_{LV}$ | V <sub>LV</sub> + 0.050 | V    | $V_{\rm LV}$ = selected voltage in lower voltage area |  |

| Core voltage (PVC)<br>supervision level<br>(see Table 22) | $V_{PVC}CC$            | V <sub>LV</sub> - 0.070 | $V_{LV}$ | V <sub>LV</sub> + 0.030 | V    | $V_{\rm LV}$ = selected voltage                       |  |

| Current control limit                                     | $I_{\rm CC}$ CC        | 13                      | _        | 30                      | mA   | Power domain DMP_M                                    |  |

|                                                           |                        | 90                      | _        | 150                     | mA   | Power domain DMP_1                                    |  |

| Wakeup clock source frequency                             | $f_{WU}CC$             | 400                     | 500      | 600                     | kHz  | FREQSEL<br>= 00 <sub>B</sub>                          |  |

| Internal clock source frequency                           | $f_{INT}CC$            | 4.8                     | 5.0      | 5.2                     | MHz  |                                                       |  |

| Startup time from stopover mode                           | $t_{\rm SSO}$ CC       | 200                     | 260      | 320                     | μs   | User instruction from PSRAM                           |  |

| Startup time from standby mode                            | t <sub>SSB</sub> CC    | 2.5                     | 2.8      | 3.5                     | ms   | User instruction from Flash                           |  |

#### 4.6 AC Parameters

These parameters describe the dynamic behavior of the XC226x.

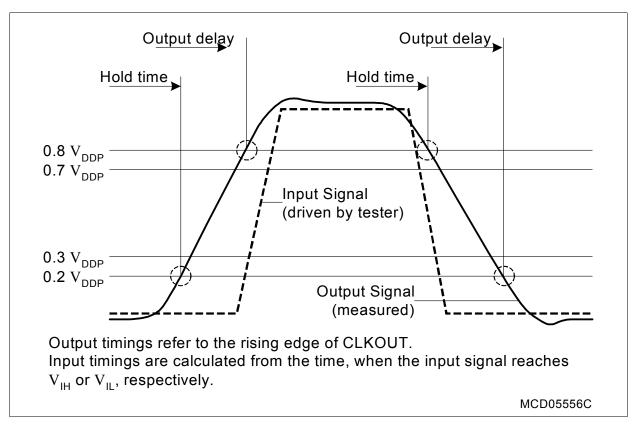

## 4.6.1 Testing Waveforms

These values are used for characterization and production testing (except pin XTAL1).

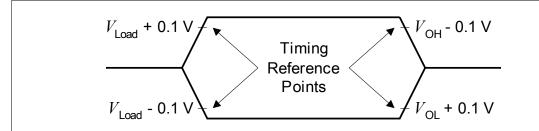

Figure 16 Input Output Waveforms

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs, but begins to float when a 100 mV change from the loaded  $V_{\rm OH}/V_{\rm OI}$  level occurs ( $I_{\rm OH}/I_{\rm OI}$  = 20 mA).

MCA05565

Figure 17 Floating Waveforms

### 4.6.2 Definition of Internal Timing

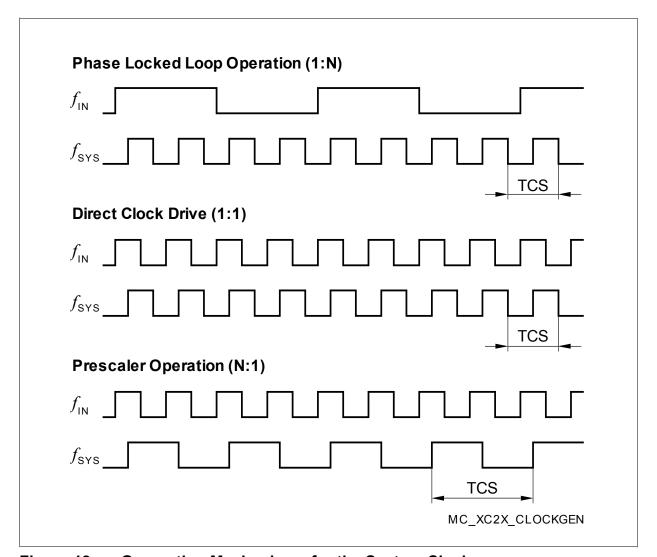

The internal operation of the XC226x is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XC226x.

Figure 18 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 18** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

### 4.6.3 External Clock Input Parameters

These parameters specify the external clock generation for the XC226x. The clock can be generated in two ways:

- By connecting a crystal or ceramic resonator to pins XTAL1/XTAL2.

- By supplying an external clock signal. This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain).

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . In connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

Table 26 External Clock Input Characteristics (Operating Conditions apply)

| Parameter                                      | Symbol               | L                             | imit Val | ues  | Unit | Note / Test                        |

|------------------------------------------------|----------------------|-------------------------------|----------|------|------|------------------------------------|

|                                                |                      | Min.                          | Тур.     | Max. |      | Condition                          |

| Input voltage range limits for signal on XTAL1 | $V_{\rm IX1}{ m SR}$ | -1.7 + V <sub>DDI</sub>       | _        | 1.7  | V    | 1)                                 |

| Input voltage (amplitude) on XTAL1             | $V_{AX1}SR$          | $0.3 \times V_{\mathrm{DDI}}$ | _        | _    | V    | Peak-to-peak voltage <sup>2)</sup> |

| XTAL1 input current                            | $I_{IL}$ CC          | _                             | _        | ±20  | μΑ   | $0 \ V < V_{IN} < V_{DD}$          |

| Oscillator frequency                           | $f_{\rm OSC}$ CC     | 4                             | _        | 40   | MHz  | Clock signal                       |

|                                                |                      | 4                             | _        | 16   | MHz  | Crystal or<br>Resonator            |

| High time                                      | t <sub>1</sub> SR    | 6                             | _        | _    | ns   |                                    |

| Low time                                       | t <sub>2</sub> SR    | 6                             | _        | _    | ns   |                                    |

| Rise time                                      | t <sub>3</sub> SR    | _                             | 8        | 8    | ns   |                                    |

| Fall time                                      | t <sub>4</sub> SR    | _                             | 8        | 8    | ns   |                                    |

<sup>1)</sup> Overload conditions must not occur on pin XTAL1.

Data Sheet 96 V2.1, 2008-08

<sup>2)</sup> The amplitude voltage  $V_{\text{AX1}}$  refers to the offset voltage  $V_{\text{OFF}}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{\text{IX1}}$ .

### 4.6.4 External Bus Timing

The following parameters specify the behavior of the XC226x bus interface.

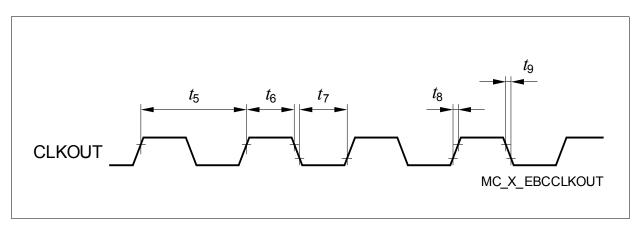

Table 27 CLKOUT Reference Signal

| Parameter         | Sym                   | Symbol |    | Limits                 | Unit | Note / Test<br>Condition |

|-------------------|-----------------------|--------|----|------------------------|------|--------------------------|

|                   |                       |        |    | Max.                   |      |                          |

| CLKOUT cycle time | $t_5$                 | CC     | 40 | /25/12.5 <sup>1)</sup> | ns   |                          |

| CLKOUT high time  | <i>t</i> <sub>6</sub> | CC     | 3  | _                      | ns   |                          |

| CLKOUT low time   | <i>t</i> <sub>7</sub> | CC     | 3  | _                      | ns   |                          |

| CLKOUT rise time  | <i>t</i> <sub>8</sub> | CC     | _  | 3                      | ns   |                          |

| CLKOUT fall time  | $t_9$                 | CC     | _  | 3                      | ns   |                          |

<sup>1)</sup> The CLKOUT cycle time is influenced by the PLL jitter (given values apply to  $f_{\rm SYS}$  = 25/40/80 MHz). For longer periods the relative deviation decreases (see PLL deviation formula).

Figure 21 CLKOUT Signal Timing

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

Data Sheet 98 V2.1, 2008-08

## 4.6.5 Synchronous Serial Interface Timing

The following parameters are applicable for a USIC channel operated in SSC mode.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Table 31 SSC Master/Slave Mode Timing for Upper Voltage Range (Operating Conditions apply),  $C_1 = 50 \text{ pF}$

| Parameter                                                         | Symbol                    | Values               |      |      | Unit | Note /          |

|-------------------------------------------------------------------|---------------------------|----------------------|------|------|------|-----------------|

|                                                                   |                           | Min.                 | Тур. | Max. |      | Test Co ndition |

| Master Mode Timing                                                |                           | 1                    |      | - "  |      |                 |

| Slave select output SELO active to first SCLKOUT transmit edge    | t <sub>1</sub> CC         | 0                    | _    | 1)   | ns   | 2)              |

| Slave select output SELO inactive after last SCLKOUT receive edge | t <sub>2</sub> CC         | $0.5 \times t_{BIT}$ | _    | 3)   | ns   |                 |

| Transmit data output valid time                                   | t <sub>3</sub> CC         | -6                   | _    | 13   | ns   |                 |

| Receive data input setup time to SCLKOUT receive edge             | t <sub>4</sub> SR         | 31                   | -    | _    | ns   |                 |

| Data input DX0 hold time from SCLKOUT receive edge                | t <sub>5</sub> SR         | -7                   | _    | _    | ns   |                 |

| Slave Mode Timing                                                 |                           |                      |      |      | - 1  |                 |

| Select input DX2 setup to first clock input DX1 transmit edge     | <i>t</i> <sub>10</sub> SR | 7                    | _    | _    | ns   | 4)              |

| Select input DX2 hold after last clock input DX1 receive edge     | <i>t</i> <sub>11</sub> SR | 5                    | _    | _    | ns   | 4)              |

| Data input DX0 setup time to clock input DX1 receive edge         | <i>t</i> <sub>12</sub> SR | 7                    | _    | _    | ns   | 4)              |

| Data input DX0 hold time from clock input DX1 receive edge        | <i>t</i> <sub>13</sub> SR | 5                    | _    | -    | ns   | 4)              |

| Data output DOUT valid time                                       | t <sub>14</sub> CC        | 8                    | _    | 29   | ns   | 4)              |

<sup>1)</sup> The maximum value further depends on the settings for the slave select output leading delay.

Data Sheet 106 V2.1, 2008-08

<sup>2)</sup>  $t_{SYS} = 1/f_{SYS}$  (= 12.5 ns @ 80 MHz)

<sup>3)</sup> The maximum value depends on the settings for the slave select output trailing delay and for the shift clock output delay.

<sup>4)</sup> These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).