Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                         |

| Core Size                  | 16/32-Bit                                                                       |

| Speed                      | 66MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI            |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                            |

| Number of I/O              | 75                                                                              |

| Program Memory Size        | 768KB (768K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 82K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 16x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP Exposed Pad                                                            |

| Supplier Device Package    | PG-LQFP-100-3                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc226796f66lackxuma1 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# XC226x 16/32-Bit Single-Chip Microcontroller with 32-Bit Performance

## Microcontrollers

Never stop thinking

#### **Summary of Features**

| Table 1                  | Table 1 XC226x Derivative Synopsis |                                 |                     |               |                            |                                |  |  |

|--------------------------|------------------------------------|---------------------------------|---------------------|---------------|----------------------------|--------------------------------|--|--|

| Derivative <sup>1)</sup> | Temp.<br>Range                     | Program<br>Memory <sup>2)</sup> | PSRAM <sup>3)</sup> | CCU6<br>Mod.  | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>       |  |  |

| SAK-XC2267-<br>96FxxL    | -40 °C to<br>125 °C                | 768 Kbytes<br>Flash             | 64 Kbytes           | 0, 1,<br>2, 3 | 11 + 5                     | 5 CAN Nodes,<br>6 Serial Chan. |  |  |

| SAF-XC2267-<br>96FxxL    | -40 °C to<br>85 °C                 | 768 Kbytes<br>Flash             | 64 Kbytes           | 0, 1,<br>2, 3 | 11 + 5                     | 5 CAN Nodes,<br>6 Serial Chan. |  |  |

| SAK-XC2267-<br>72FxxL    | -40 °C to<br>125 °C                | 576 Kbytes<br>Flash             | 32 Kbytes           | 0, 1,<br>2, 3 | 11 + 5                     | 5 CAN Nodes,<br>6 Serial Chan. |  |  |

| SAF-XC2267-<br>72FxxL    | -40 °C to<br>85 °C                 | 576 Kbytes<br>Flash             | 32 Kbytes           | 0, 1,<br>2, 3 | 11 + 5                     | 5 CAN Nodes,<br>6 Serial Chan. |  |  |

| SAK-XC2267-<br>56FxxL    | -40 °C to<br>125 °C                | 448 Kbytes<br>Flash             | 16 Kbytes           | 0, 1,<br>2, 3 | 11 + 5                     | 5 CAN Nodes,<br>6 Serial Chan. |  |  |

| SAF-XC2267-<br>56FxxL    | -40 °C to<br>85 °C                 | 448 Kbytes<br>Flash             | 16 Kbytes           | 0, 1,<br>2, 3 | 11 + 5                     | 5 CAN Nodes,<br>6 Serial Chan. |  |  |

| SAK-XC2264-<br>96FxxL    | -40 °C to<br>125 °C                | 768 Kbytes<br>Flash             | 64 Kbytes           | 0, 1          | 8                          | 2 CAN Nodes,<br>4 Serial Chan. |  |  |

| SAF-XC2264-<br>96FxxL    | -40 °C to<br>85 °C                 | 768 Kbytes<br>Flash             | 64 Kbytes           | 0, 1          | 8                          | 2 CAN Nodes,<br>4 Serial Chan. |  |  |

| SAK-XC2264-<br>72FxxL    | -40 °C to<br>125 °C                | 576 Kbytes<br>Flash             | 32 Kbytes           | 0, 1          | 8                          | 2 CAN Nodes,<br>4 Serial Chan. |  |  |

| SAF-XC2264-<br>72FxxL    | -40 °C to<br>85 °C                 | 576 Kbytes<br>Flash             | 32 Kbytes           | 0, 1          | 8                          | 2 CAN Nodes,<br>4 Serial Chan. |  |  |

| SAK-XC2264-<br>56FxxL    | -40 °C to<br>125 °C                | 448 Kbytes<br>Flash             | 16 Kbytes           | 0, 1          | 8                          | 2 CAN Nodes,<br>4 Serial Chan. |  |  |

| SAF-XC2264-<br>56FxxL    | -40 °C to<br>85 °C                 | 448 Kbytes<br>Flash             | 16 Kbytes           | 0, 1          | 8                          | 2 CAN Nodes,<br>4 Serial Chan. |  |  |

1) This Data Sheet is valid for devices starting with and including design step AC.

2) Specific inormation about the on-chip Flash memory in Table 2.

3) All derivatives additionally provide 1 Kbyte SBRAM, 2 Kbytes DPRAM, and 16 Kbytes DSRAM.

4) Specific information about the available channels in Table 3.

Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

#### **General Device Information**

## 2 General Device Information

The XC226x derivatives are high-performance members of the Infineon XC2000 Family of full-feature single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

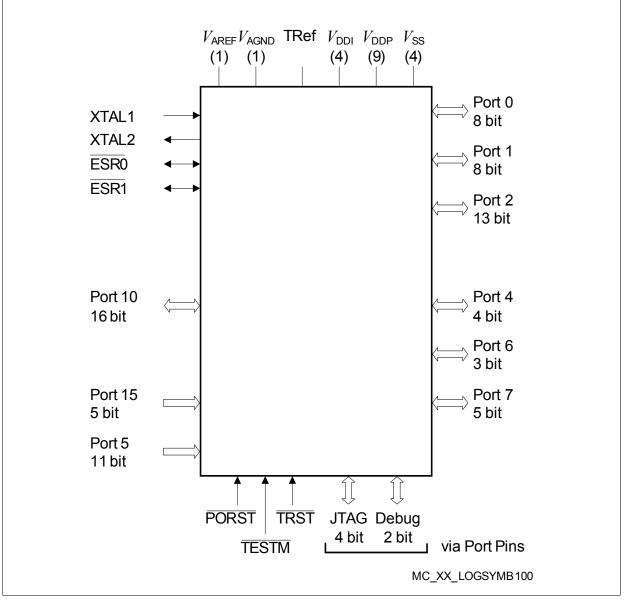

Figure 1 Logic Symbol

#### **General Device Information**

#### **Notes to Pin Definitions**

Ctrl.: The output signal for a port pin is selected by bitfield PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bitfield PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc. Output signal OH is controlled by hardware.

2. **Type**: Indicates the pad type used (St=standard pad, Sp=special pad, DP=double pad, In=input pad, PS=power supply) and its power supply domain (A, B, M, 1).

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                         |

|-----|-------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TESTM             | I      | In/B | Testmode EnableEnables factory test modes, must be held HIGH fornormal operation (connect to $V_{\text{DDPB}}$ ).An internal pullup device will hold this pin highwhen nothing is driving it.                                                                                                                                                                    |

| 4   | P7.2              | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                    |

|     | EMUX0             | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                                                      |

|     | TxDC4             | 02     | St/B | CAN Node 4 Transmit Data Output                                                                                                                                                                                                                                                                                                                                  |

|     | CCU62_<br>CCPOS0A | I      | St/B | CCU62 Position Input 0                                                                                                                                                                                                                                                                                                                                           |

|     | TDI_C             | I      | St/B | JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                             |

| 5   | TRST              | 1      | In/B | <b>Test-System Reset Input</b><br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XC226x's debug system.<br>In this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pulldown device will hold this pin low<br>when nothing is driving it. |

| 6   | P7.0              | O0 / I | St/B | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                                    |

|     | T3OUT             | 01     | St/B | GPT1 Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                                                |

|     | T6OUT             | 02     | St/B | GPT2 Timer T6 Toggle Latch Output                                                                                                                                                                                                                                                                                                                                |

|     | TDO_A             | ОН     | St/B | JTAG Test Data Output                                                                                                                                                                                                                                                                                                                                            |

|     | ESR2_1            | 1      | St/B | ESR2 Trigger Input 1                                                                                                                                                                                                                                                                                                                                             |

|     | RxDC4B            | Ι      | St/B | CAN Node 4 Receive Data Input                                                                                                                                                                                                                                                                                                                                    |

#### Table 4 Pin Definitions and Functions

#### Table 6XC226x Interrupt Nodes

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

| CAPCOM Register 16, or<br>ERU Request 0       | CC2_CC16IC          | xx'0040 <sub>H</sub>             | 10 <sub>H</sub> / 16 <sub>D</sub> |

| CAPCOM Register 17, or<br>ERU Request 1       | CC2_CC17IC          | xx'0044 <sub>H</sub>             | 11 <sub>H</sub> / 17 <sub>D</sub> |

| CAPCOM Register 18, or<br>ERU Request 2       | CC2_CC18IC          | xx'0048 <sub>H</sub>             | 12 <sub>H</sub> / 18 <sub>D</sub> |

| CAPCOM Register 19, or<br>ERU Request 3       | CC2_CC19IC          | xx'004C <sub>H</sub>             | 13 <sub>H</sub> / 19 <sub>D</sub> |

| CAPCOM Register 20, or<br>USIC0 Request 6     | CC2_CC20IC          | xx'0050 <sub>H</sub>             | 14 <sub>H</sub> / 20 <sub>D</sub> |

| CAPCOM Register 21, or<br>USIC0 Request 7     | CC2_CC21IC          | xx'0054 <sub>H</sub>             | 15 <sub>H</sub> / 21 <sub>D</sub> |

| CAPCOM Register 22, or<br>USIC1 Request 6     | CC2_CC22IC          | xx'0058 <sub>H</sub>             | 16 <sub>H</sub> / 22 <sub>D</sub> |

| CAPCOM Register 23, or<br>USIC1 Request 7     | CC2_CC23IC          | xx'005C <sub>H</sub>             | 17 <sub>H</sub> / 23 <sub>D</sub> |

| CAPCOM Register 24, or<br>ERU Request 0       | CC2_CC24IC          | xx'0060 <sub>H</sub>             | 18 <sub>H</sub> / 24 <sub>D</sub> |

| CAPCOM Register 25, or<br>ERU Request 1       | CC2_CC25IC          | xx'0064 <sub>H</sub>             | 19 <sub>H</sub> / 25 <sub>D</sub> |

| CAPCOM Register 26, or<br>ERU Request 2       | CC2_CC26IC          | xx'0068 <sub>H</sub>             | 1A <sub>H</sub> / 26 <sub>D</sub> |

| CAPCOM Register 27, or<br>ERU Request 3       | CC2_CC27IC          | xx'006C <sub>H</sub>             | 1B <sub>H</sub> / 27 <sub>D</sub> |

| CAPCOM Register 28, or<br>USIC2 Request 6     | CC2_CC28IC          | xx'0070 <sub>H</sub>             | 1C <sub>H</sub> / 28 <sub>D</sub> |

| CAPCOM Register 29, or<br>USIC2 Request 7     | CC2_CC29IC          | xx'0074 <sub>H</sub>             | 1D <sub>H</sub> / 29 <sub>D</sub> |

| CAPCOM Register 30                            | CC2_CC30IC          | xx'0078 <sub>H</sub>             | 1E <sub>H</sub> / 30 <sub>D</sub> |

| CAPCOM Register 31                            | CC2_CC31IC          | xx'007C <sub>H</sub>             | 1F <sub>H</sub> / 31 <sub>D</sub> |

| GPT1 Timer 2                                  | GPT12E_T2IC         | xx'0080 <sub>H</sub>             | 20 <sub>H</sub> / 32 <sub>D</sub> |

| GPT1 Timer 3                                  | GPT12E_T3IC         | xx'0084 <sub>H</sub>             | 21 <sub>H</sub> / 33 <sub>D</sub> |

| GPT1 Timer 4                                  | GPT12E_T4IC         | xx'0088 <sub>H</sub>             | 22 <sub>H</sub> / 34 <sub>D</sub> |

#### Table 6XC226x Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|

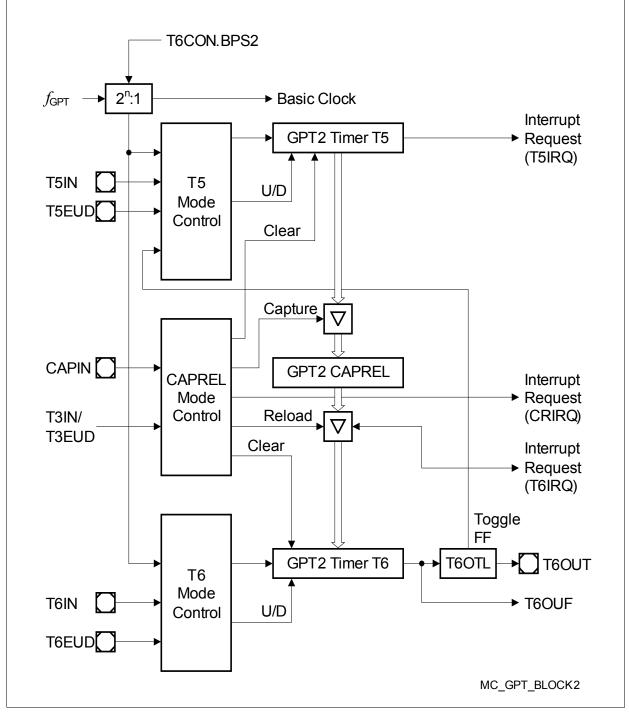

| GPT2 Timer 5                                  | GPT12E_T5IC         | xx'008C <sub>H</sub>             | 23 <sub>H</sub> / 35 <sub>D</sub> |

| GPT2 Timer 6                                  | GPT12E_T6IC         | xx'0090 <sub>H</sub>             | 24 <sub>H</sub> / 36 <sub>D</sub> |

| GPT2 CAPREL Register                          | GPT12E_CRIC         | xx'0094 <sub>H</sub>             | 25 <sub>H</sub> / 37 <sub>D</sub> |

| CAPCOM Timer 7                                | CC2_T7IC            | xx'0098 <sub>H</sub>             | 26 <sub>H</sub> / 38 <sub>D</sub> |

| CAPCOM Timer 8                                | CC2_T8IC            | xx'009C <sub>H</sub>             | 27 <sub>H</sub> / 39 <sub>D</sub> |

| A/D Converter Request 0                       | ADC_0IC             | xx'00A0 <sub>H</sub>             | 28 <sub>H</sub> / 40 <sub>D</sub> |

| A/D Converter Request 1                       | ADC_1IC             | xx'00A4 <sub>H</sub>             | 29 <sub>H</sub> / 41 <sub>D</sub> |

| A/D Converter Request 2                       | ADC_2IC             | xx'00A8 <sub>H</sub>             | 2A <sub>H</sub> / 42 <sub>D</sub> |

| A/D Converter Request 3                       | ADC_3IC             | xx'00AC <sub>H</sub>             | 2B <sub>H</sub> / 43 <sub>D</sub> |

| A/D Converter Request 4                       | ADC_4IC             | xx'00B0 <sub>H</sub>             | 2C <sub>H</sub> / 44 <sub>D</sub> |

| A/D Converter Request 5                       | ADC_5IC             | xx'00B4 <sub>H</sub>             | 2D <sub>H</sub> / 45 <sub>D</sub> |

| A/D Converter Request 6                       | ADC_6IC             | xx'00B8 <sub>H</sub>             | 2E <sub>H</sub> / 46 <sub>D</sub> |

| A/D Converter Request 7                       | ADC_7IC             | xx'00BC <sub>H</sub>             | 2F <sub>H</sub> / 47 <sub>D</sub> |

| CCU60 Request 0                               | CCU60_0IC           | xx'00C0 <sub>H</sub>             | 30 <sub>H</sub> / 48 <sub>D</sub> |

| CCU60 Request 1                               | CCU60_1IC           | xx'00C4 <sub>H</sub>             | 31 <sub>H</sub> / 49 <sub>D</sub> |

| CCU60 Request 2                               | CCU60_2IC           | xx'00C8 <sub>H</sub>             | 32 <sub>H</sub> / 50 <sub>D</sub> |

| CCU60 Request 3                               | CCU60_3IC           | xx'00CC <sub>H</sub>             | 33 <sub>H</sub> / 51 <sub>D</sub> |

| CCU61 Request 0                               | CCU61_0IC           | xx'00D0 <sub>H</sub>             | 34 <sub>H</sub> / 52 <sub>D</sub> |

| CCU61 Request 1                               | CCU61_1IC           | xx'00D4 <sub>H</sub>             | 35 <sub>H</sub> / 53 <sub>D</sub> |

| CCU61 Request 2                               | CCU61_2IC           | xx'00D8 <sub>H</sub>             | 36 <sub>H</sub> / 54 <sub>D</sub> |

| CCU61 Request 3                               | CCU61_3IC           | xx'00DC <sub>H</sub>             | 37 <sub>H</sub> / 55 <sub>D</sub> |

| CCU62 Request 0                               | CCU62_0IC           | xx'00E0 <sub>H</sub>             | 38 <sub>H</sub> / 56 <sub>D</sub> |

| CCU62 Request 1                               | CCU62_1IC           | xx'00E4 <sub>H</sub>             | 39 <sub>H</sub> / 57 <sub>D</sub> |

| CCU62 Request 2                               | CCU62_2IC           | xx'00E8 <sub>H</sub>             | 3A <sub>H</sub> / 58 <sub>D</sub> |

| CCU62 Request 3                               | CCU62_3IC           | xx'00EC <sub>H</sub>             | 3B <sub>H</sub> / 59 <sub>D</sub> |

| CCU63 Request 0                               | CCU63_0IC           | xx'00F0 <sub>H</sub>             | 3C <sub>H</sub> / 60 <sub>D</sub> |

| CCU63 Request 1                               | CCU63_1IC           | xx'00F4 <sub>H</sub>             | 3D <sub>H</sub> / 61 <sub>D</sub> |

| CCU63 Request 2                               | CCU63_2IC           | xx'00F8 <sub>H</sub>             | 3E <sub>H</sub> / 62 <sub>D</sub> |

| CCU63 Request 3                               | CCU63_3IC           | xx'00FC <sub>H</sub>             | 3F <sub>H</sub> / 63 <sub>D</sub> |

| CAN Request 0                                 | CAN_0IC             | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |

## 3.7 Capture/Compare Units CCU6x

The XC226x features up to four CCU6 units (CCU60, CCU61, CCU62, CCU63).

The CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

#### **Timer 12 Features**

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- · Many interrupt request sources

- Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

#### Timer 13 Features

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period match and compare match

- Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

#### Additional Features

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC drives

- Output levels can be selected and adapted to the power stage

## XC2267 / XC2264 XC2000 Family Derivatives

### **Functional Description**

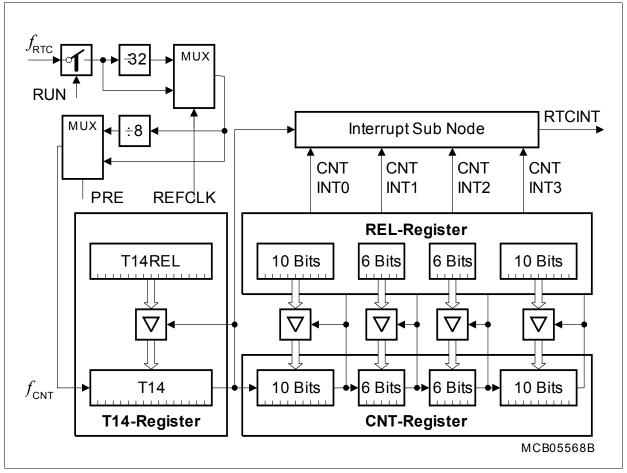

## 3.9 Real Time Clock

The Real Time Clock (RTC) module of the XC226x can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

#### Figure 9 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

### **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- **UART** (asynchronous serial channel)

- maximum baud rate:  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- maximum baud rate:  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI/QSPI (synchronous serial channel with or without data buffer)

- maximum baud rate in slave mode:  $f_{\rm SYS}$

- maximum baud rate in master mode:  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- **IIS** (Inter-IC Sound Bus)

- maximum baud rate:  $f_{SYS}$  / 2 for transmitter,  $f_{SYS}$  for receiver

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

#### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Up to five independent CAN nodes

- Up to 128 independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

### **Operating Conditions**

The following operating conditions must not be exceeded to ensure correct operation of the XC226x. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

### Table 12 Operating Condition Parameters

| Parameter                                                                               | Symbol                     | Values |                           |                           | Unit | Note /                                |  |

|-----------------------------------------------------------------------------------------|----------------------------|--------|---------------------------|---------------------------|------|---------------------------------------|--|

|                                                                                         |                            | Min.   | Тур.                      | Max.                      |      | Test Condition                        |  |

| Digital core supply voltage                                                             | V <sub>DDI</sub>           | 1.4    | _                         | 1.6                       | V    |                                       |  |

| Core Supply Voltage<br>Difference                                                       | ∆VDDI                      | -10    | -                         | +10                       | mV   | V <sub>DDIM</sub> - V <sub>DDI1</sub> |  |

| Digital supply voltage for<br>IO pads and voltage<br>regulators,<br>upper voltage range | $V_{ m DDPA}, V_{ m DDPB}$ | 4.5    | -                         | 5.5                       | V    | 2)                                    |  |

| Digital supply voltage for<br>IO pads and voltage<br>regulators,<br>lower voltage range | $V_{ m DDPA}, V_{ m DDPB}$ | 3.0    | -                         | 4.5                       | V    | 2)                                    |  |

| Digital ground voltage                                                                  | V <sub>SS</sub>            | 0      | -                         | 0                         | V    | Reference<br>voltage                  |  |

| Overload current                                                                        | I <sub>OV</sub>            | -5     | -                         | 5                         | mA   | Per IO pin <sup>3)4)</sup>            |  |

|                                                                                         |                            | -2     | -                         | 5                         | mA   | Per analog input pin <sup>3)4)</sup>  |  |

| Overload positive current coupling factor for analog inputs <sup>5)</sup>               | K <sub>ova</sub>           | -      | 1.0 ×<br>10 <sup>-6</sup> | 1.0 ×<br>10 <sup>-4</sup> | -    | <i>I</i> <sub>OV</sub> > 0            |  |

| Overload negative current coupling factor for analog inputs <sup>5)</sup>               | K <sub>ova</sub>           | -      | 2.5 ×<br>10 <sup>-4</sup> | 1.5 ×<br>10 <sup>-3</sup> | -    | <i>I</i> <sub>OV</sub> < 0            |  |

| Overload positive current<br>coupling factor for digital<br>I/O pins <sup>5)</sup>      | K <sub>OVD</sub>           | -      | 1.0 ×<br>10 <sup>-4</sup> | 5.0 ×<br>10 <sup>-3</sup> | -    | <i>I</i> <sub>OV</sub> > 0            |  |

| Overload negative current coupling factor for digital I/O pins <sup>5)</sup>            | K <sub>ovd</sub>           | -      | 1.0 ×<br>10 <sup>-2</sup> | 3.0 ×<br>10 <sup>-2</sup> | -    | <i>I</i> <sub>OV</sub> < 0            |  |

| Absolute sum of overload currents                                                       | ΣΙΙΟΥΙ                     | -      | -                         | 50                        | mA   | 4)                                    |  |

- Not subject to production test verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 13, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

- 4) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are verified.

- 5) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 6) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- 7) The given values are worst-case values. In production test, this leakage current is only tested at 125°C; other values are ensured by correlation. For derating, please refer to the following descriptions:

Leakage derating depending on temperature ( $T_J$  = junction temperature [°C]):

$I_{OZ}$  = 0.05 × e<sup>(1.5 + 0.028×TJ)</sup> [µA]. For example, at a temperature of 130°C the resulting leakage current is 8.54 µA.

Leakage derating depending on voltage level (DV =  $V_{\text{DDP}}$  -  $V_{\text{PIN}}$  [V]):

$I_{OZ} = I_{OZtempmax} - (1.6 \times DV) [\mu A]$

This voltage derating formula is an approximation which applies for maximum temperature.

Because pin P2.8 is connected to two pads (standard pad and high-speed clock pad), it has twice the normal leakage.

8) Keep current: Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level:  $V_{\text{PIN}} \ge V_{\text{IL}}$  for a pullup;  $V_{\text{PIN}} \le V_{\text{IL}}$  for a pulldown.

Force current: Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device:  $V_{\text{PIN}} \leq V_{\text{IL}}$  for a pullup;  $V_{\text{PIN}} \geq V_{\text{IH}}$  for a pulldown.

These values apply to the fixed pull-devices in dedicated pins and to the user-selectable pull-devices in general purpose IO pins.

Not subject to production test - verified by design/characterization. Because pin P2.8 is connected to two pads (standard pad and high-speed clock pad), it has twice the normal capacitance.

| Table 21          | Coding of Bitfields LEVXV | Coding of Bittleids LEVXV in Register SWDCONU |  |  |  |  |  |  |

|-------------------|---------------------------|-----------------------------------------------|--|--|--|--|--|--|

| Code              | Default Voltage Level     | Notes <sup>1)</sup>                           |  |  |  |  |  |  |

| 0000 <sub>B</sub> | 2.9 V                     |                                               |  |  |  |  |  |  |

| 0001 <sub>B</sub> | 3.0 V                     | LEV1V: reset request                          |  |  |  |  |  |  |

| 0010 <sub>B</sub> | 3.1 V                     |                                               |  |  |  |  |  |  |

| 0011 <sub>B</sub> | 3.2 V                     |                                               |  |  |  |  |  |  |

| 0100 <sub>B</sub> | 3.3 V                     |                                               |  |  |  |  |  |  |

| 0101 <sub>B</sub> | 3.4 V                     |                                               |  |  |  |  |  |  |

| 0110 <sub>B</sub> | 3.6 V                     |                                               |  |  |  |  |  |  |

| 0111 <sub>B</sub> | 4.0 V                     |                                               |  |  |  |  |  |  |

| 1000 <sub>B</sub> | 4.2 V                     |                                               |  |  |  |  |  |  |

| 1001 <sub>B</sub> | 4.5 V                     | LEV2V: no request                             |  |  |  |  |  |  |

| 1010 <sub>B</sub> | 4.6 V                     |                                               |  |  |  |  |  |  |

| 1011 <sub>B</sub> | 4.7 V                     |                                               |  |  |  |  |  |  |

| 1100 <sub>B</sub> | 4.8 V                     |                                               |  |  |  |  |  |  |

| 1101 <sub>B</sub> | 4.9 V                     |                                               |  |  |  |  |  |  |

| 1110 <sub>B</sub> | 5.0 V                     |                                               |  |  |  |  |  |  |

| 1111 <sub>B</sub> | 5.5 V                     |                                               |  |  |  |  |  |  |

|                   |                           |                                               |  |  |  |  |  |  |

## Table 21 Coding of Bitfields LEVxV in Register SWDCON0

1) The indicated default levels are selected automatically after a power reset.

#### Table 22 Coding of Bitfields LEVxV in Registers PVCyCONz

| Code             | Default Voltage Level | Notes <sup>1)</sup>      |

|------------------|-----------------------|--------------------------|

| 000 <sub>B</sub> | 0.9 V                 |                          |

| 001 <sub>B</sub> | 1.0 V                 |                          |

| 010 <sub>B</sub> | 1.1 V                 |                          |

| 011 <sub>B</sub> | 1.2 V                 |                          |

| 100 <sub>B</sub> | 1.3 V                 | LEV1V: reset request     |

| 101 <sub>B</sub> | 1.4 V                 | LEV2V: interrupt request |

| 110 <sub>B</sub> | 1.5 V                 |                          |

| 111 <sub>B</sub> | 1.6 V                 |                          |

1) The indicated default levels are selected automatically after a power reset.

#### 4.5 Flash Memory Parameters

The XC226x is delivered with all Flash sectors erased and with no protection installed.

The data retention time of the XC226x's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

| Parameter                                            | Symbol           | Limit Values |                 |      | Unit   | Note / Test                        |  |

|------------------------------------------------------|------------------|--------------|-----------------|------|--------|------------------------------------|--|

|                                                      |                  | Min.         | Тур.            | Max. |        | Condition                          |  |

| Programming time per<br>128-byte page                | t <sub>PR</sub>  | -            | 3 <sup>1)</sup> | 3.5  | ms     | ms                                 |  |

| Erase time per<br>sector/page                        | t <sub>ER</sub>  | -            | 4 <sup>1)</sup> | 5    | ms     | ms                                 |  |

| Data retention time                                  | t <sub>RET</sub> | 20           | -               | -    | years  | 1,000 erase /<br>program<br>cycles |  |

| Flash erase endurance for user sectors <sup>2)</sup> | $N_{ER}$         | 15,000       | -               | -    | cycles | Data retentior time 5 years        |  |

| Flash erase endurance for security pages             | N <sub>SEC</sub> | 10           | -               | -    | cycles | Data retentior time 20 years       |  |

| Drain disturb limit                                  | $N_{\rm DD}$     | 64           | -               | _    | cycles | 3)                                 |  |

## Table 23Flash Characteristics(Operating Conditions apply)

Programming and erase times depend on the internal Flash clock source. The control state machine needs a few system clock cycles. This requirement is only relevant for extremely low system frequencies. In the XC226x erased areas must be programmed completely (with actual code/data or dummy values) before that area is read.

2) A maximum of 64 Flash sectors can be cycled 15,000 times. For all other sectors the limit is 1,000 cycles.

3) This parameter limits the number of subsequent programming operations within a physical sector. The drain disturb limit is applicable if wordline erase is used repeatedly. For normal sector erase/program cycles this limit will not be violated.

Access to the XC226x Flash modules is controlled by the IMB. Built-in prefetch mechanisms optimize the performance for sequential access.

Flash access waitstates only affect non-sequential access. Due to prefetch mechanisms, the performance for sequential access (depending on the software structure) is only partially influenced by waitstates.

## 4.6.2 Definition of Internal Timing

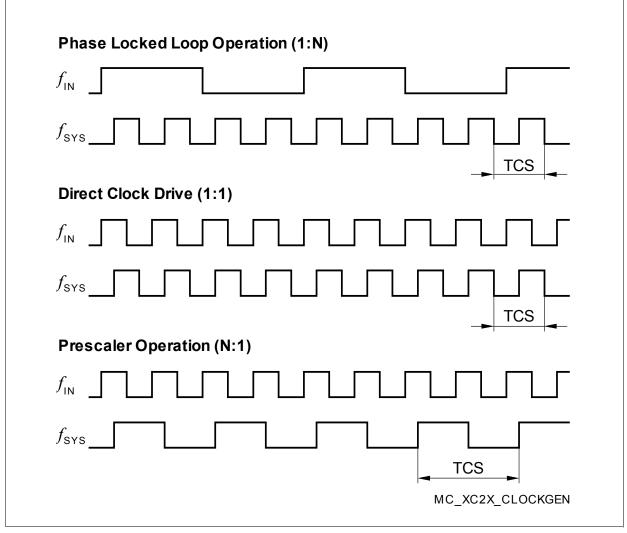

The internal operation of the XC226x is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XC226x.

Figure 18 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 18** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

## **Direct Drive**

When direct drive operation is selected (SYSCON0.CLKSEL =  $11_B$ ), the system clock is derived directly from the input clock signal CLKIN1:

$f_{\text{SYS}} = f_{\text{IN}}$ .

The frequency of  $f_{SYS}$  is the same as the frequency of  $f_{IN}$ . In this case the high and low times of  $f_{SYS}$  are determined by the duty cycle of the input clock  $f_{IN}$ .

Selecting Bypass Operation from the XTAL1<sup>1</sup> input and using a divider factor of 1 results in a similar configuration.

#### Prescaler Operation

When prescaler operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $1_B$ ), the system clock is derived either from the crystal oscillator (input clock signal XTAL1) or from the internal clock source through the output prescaler K1 (= K1DIV+1):

$f_{\rm SYS} = f_{\rm OSC} / {\rm K1}.$

If a divider factor of 1 is selected, the frequency of  $f_{\rm SYS}$  equals the frequency of  $f_{\rm OSC}$ . In this case the high and low times of  $f_{\rm SYS}$  are determined by the duty cycle of the input clock  $f_{\rm OSC}$  (external or internal).

The lowest system clock frequency results from selecting the maximum value for the divider factor K1:

$f_{\rm SYS} = f_{\rm OSC} / 1024.$

## Phase Locked Loop (PLL)

When PLL operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $0_B$ ), the on-chip phase locked loop is enabled and provides the system clock. The PLL multiplies the input frequency by the factor **F** ( $f_{SYS} = f_{IN} \times F$ ).

**F** is calculated from the input divider P (= PDIV+1), the multiplication factor N (= NDIV+1), and the output divider K2 (= K2DIV+1): (**F** = N / (P × K2)).

The input clock can be derived either from an external source at XTAL1 or from the onchip clock source.

The PLL circuit synchronizes the system clock to the input clock. This synchronization is performed smoothly so that the system clock frequency does not change abruptly.

Adjustment to the input clock continuously changes the frequency of  $f_{SYS}$  so that it is locked to  $f_{IN}$ . The slight variation causes a jitter of  $f_{SYS}$  which in turn affects the duration of individual TCSs.

<sup>1)</sup> Voltages on XTAL1 must comply to the core supply voltage  $V_{\text{DDI1}}$ .

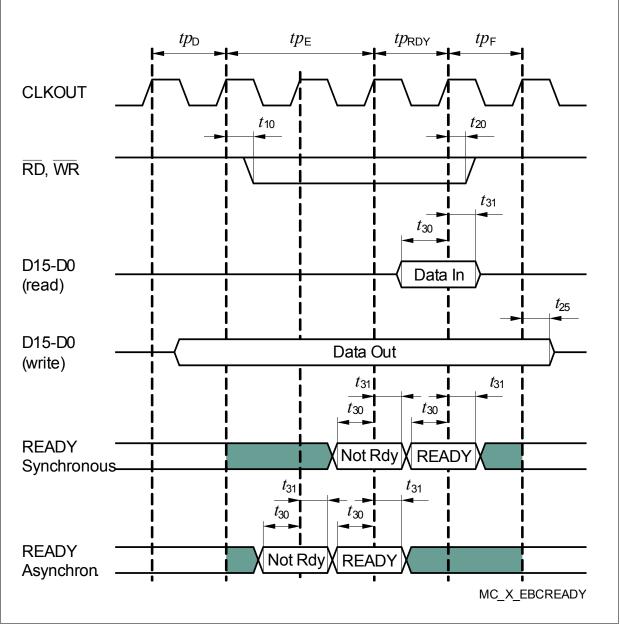

# Table 29External Bus Cycle Timing for Upper Voltage Range<br/>(Operating Conditions apply)

| Parameter                                                         | Symbol                    |      | Limits | 5    | Unit | Note |

|-------------------------------------------------------------------|---------------------------|------|--------|------|------|------|

|                                                                   |                           | Min. | Тур.   | Max. |      |      |

| Output valid delay for:<br>RD, WR(L/H)                            | <i>t</i> <sub>10</sub> CC | -    |        | 13   | ns   |      |

| Output valid delay for:<br>BHE, ALE                               | <i>t</i> <sub>11</sub> CC | -    |        | 13   | ns   |      |

| Output valid delay for:<br>A23 A16, A15 A0 (on P0/P1)             | <i>t</i> <sub>12</sub> CC | _    |        | 14   | ns   |      |

| Output valid delay for:<br>A15 A0 (on P2/P10)                     | <i>t</i> <sub>13</sub> CC | -    |        | 14   | ns   |      |

| Output valid delay for:<br>CS                                     | <i>t</i> <sub>14</sub> CC | -    |        | 13   | ns   |      |

| Output valid delay for:<br>D15 D0 (write data, MUX-mode)          | <i>t</i> <sub>15</sub> CC | -    |        | 14   | ns   |      |

| Output valid delay for:<br>D15 D0 (write data, DEMUX-<br>mode)    | <i>t</i> <sub>16</sub> CC | -    |        | 14   | ns   |      |

| Output hold time for:<br>RD, WR(L/H)                              | <i>t</i> <sub>20</sub> CC | 0    |        | 8    | ns   |      |

| Output hold time for:<br>BHE, ALE                                 | <i>t</i> <sub>21</sub> CC | 0    |        | 8    | ns   |      |

| Output hold time for:<br>A23 A16, A15 A0 (on P2/P10)              | <i>t</i> <sub>23</sub> CC | 0    |        | 8    | ns   |      |

| Output hold time for:<br>CS                                       | <i>t</i> <sub>24</sub> CC | 0    |        | 8    | ns   |      |

| Output hold time for:<br>D15 … D0 (write data)                    | <i>t</i> <sub>25</sub> CC | 0    |        | 8    | ns   |      |

| Input setup time for:<br>READY, D15 … D0 (read data)              | <i>t</i> <sub>30</sub> SR | 18   |        | -    | ns   |      |

| Input hold time for:<br>READY, D15 … D0 (read data) <sup>1)</sup> | <i>t</i> <sub>31</sub> SR | -4   |        | _    | ns   |      |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can change after the rising edge of RD.

## XC2267 / XC2264 XC2000 Family Derivatives

#### **Electrical Parameters**

Figure 24 READY Timing

Note: If the READY input is sampled inactive at the indicated sampling point ("Not Rdy") a READY-controlled waitstate is inserted (tpRDY),

sampling the READY input active at the indicated sampling point ("Ready") terminates the currently running bus cycle.

Note the different sampling points for synchronous and asynchronous READY. This example uses one mandatory waitstate (see tpE) before the READY input value is used.

## XC2267 / XC2264 XC2000 Family Derivatives

#### **Electrical Parameters**