Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| IABLE        | TABLE 4-29:       PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY |        |              |        |        |            |        |       |       |       |             |       |       |            |       |       |       |               |

|--------------|---------------------------------------------------------------------------------------------|--------|--------------|--------|--------|------------|--------|-------|-------|-------|-------------|-------|-------|------------|-------|-------|-------|---------------|

| File<br>Name | Addr.                                                                                       | Bit 15 | Bit 14       | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6       | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0                                                                                        | _      | INT1R<6:0>   |        |        |            |        |       |       | —     |             |       |       |            |       |       | _     | 0000          |

| RPINR1       | 06A2                                                                                        | _      | _            | _      | _      | _          | _      | _     | _     | _     |             |       |       | INT2R<6:0> | >     |       |       | 0000          |

| RPINR3       | 06A6                                                                                        | _      | _            | _      | _      | _          | _      | _     | _     | _     |             |       |       | T2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE                                                                                        | _      |              |        |        | IC2R<6:0>  |        | •     |       | _     |             |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0                                                                                        | _      |              |        |        | IC4R<6:0>  |        |       |       | _     |             |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6                                                                                        | _      | -            | _      | _      | _          | _      | _     | _     | _     |             |       | (     | OCFAR<6:0  | >     |       |       | 0000          |

| RPINR12      | 06B8                                                                                        | _      |              |        |        | FLT2R<6:0> |        | •     |       | _     | FLT1R<6:0>  |       |       |            |       | 0000  |       |               |

| RPINR14      | 06BC                                                                                        | _      |              |        | (      | QEB1R<6:0  | >      |       |       | _     | QEA1R<6:0>  |       |       |            |       |       | 0000  |               |

| RPINR15      | 06BE                                                                                        | _      |              |        | Н      | OME1R<6:0  | )>     |       |       | _     | INDX1R<6:0> |       |       |            |       | 0000  |       |               |

| RPINR18      | 06C4                                                                                        | _      | _            | _      | _      | _          | _      | _     | _     | _     | U1RXR<6:0>  |       |       |            |       | 0000  |       |               |

| RPINR19      | 06C6                                                                                        | _      | _            | _      | _      | _          | _      | _     | _     | _     | U2RXR<6:0>  |       |       |            |       | 0000  |       |               |

| RPINR22      | 06CC                                                                                        |        |              |        | S      | CK2INR<6:( | )>     |       |       | _     |             |       |       | SDI2R<6:0> | >     |       |       | 0000          |

| RPINR23      | 06CE                                                                                        |        | _            | _      | _      | _          | _      | _     | _     | _     |             |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4                                                                                        |        | _            | _      | _      | _          | _      | _     | _     | _     | _           | _     | _     | _          | _     | _     | _     | 0000          |

| RPINR37      | 06EA                                                                                        | _      | SYNCI1R<6:0> |        |        |            |        |       |       | _     | _           | —     | —     | —          | _     | _     | _     | 0000          |

| RPINR38      | 06EC                                                                                        | _      | DTCMP1R<6:0> |        |        |            |        |       |       | _     | _           | —     | —     | —          | _     | _     | _     | 0000          |

| RPINR39      | 06EE                                                                                        | _      |              |        | D      | FCMP3R<6:  | 0>     |       |       | -     |             |       | D     | TCMP2R<6:  | :0>   |       |       | 0000          |

#### TABLE 4-29: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-30: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14     | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|------------|--------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      | INT1R<6:0> |        |        |            |        |       |       | _     | —            | —     | —     | —          | _     | -     | _     | 0000          |

| RPINR1       | 06A2  | _      |            |        |        |            |        |       | _     | _     |              |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3       | 06A6  | _      | _          | _      | _      | _          | _      | _     | _     | _     |              |       | ٦     | F2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  | _      |            |        |        | IC2R<6:0>  |        |       |       | _     | IC1R<6:0>    |       |       |            |       |       | 0000  |               |

| RPINR8       | 06B0  | _      |            |        |        | IC4R<6:0>  |        |       |       | _     |              |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  | _      | _          | _      | _      | _          | _      | _     | _     | _     |              |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  | _      | _          | _      | _      | _          | _      | _     | _     | _     |              |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  | _      | _          | _      | _      | _          | _      | _     | _     | _     |              |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  | —      |            |        | S      | CK2INR<6:0 | )>     |       |       | _     | — SDI2R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR23      | 06CE  | _      | _          | —      | —      | —          | —      | —     | —     | _     |              |       |       | SS2R<6:0>  |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| U-0                                | U-0                                       | U-0            | U-0             | U-0              | U-0              | U-0                | R/W-0   |  |

|------------------------------------|-------------------------------------------|----------------|-----------------|------------------|------------------|--------------------|---------|--|

| _                                  | —                                         | —              |                 | —                | —                | —                  | PLLDIV8 |  |

| bit 15                             |                                           |                |                 |                  |                  |                    | bit 8   |  |

|                                    |                                           |                |                 |                  |                  |                    |         |  |

| R/W-0                              | R/W-0                                     | R/W-1          | R/W-1           | R/W-0            | R/W-0            | R/W-0              | R/W-0   |  |

| PLLDIV7                            | PLLDIV6                                   | PLLDIV5        | PLLDIV4         | PLLDIV3          | PLLDIV2          | PLLDIV1            | PLLDIV0 |  |

| bit 7                              |                                           |                |                 |                  |                  |                    | bit 0   |  |

|                                    |                                           |                |                 |                  |                  |                    |         |  |

| Legend:                            |                                           |                |                 |                  |                  |                    |         |  |

| R = Readable                       | bit                                       | W = Writable   | bit             | U = Unimpler     | mented bit, read | as '0'             |         |  |

| -n = Value at POR '1' = Bit is set |                                           |                |                 | '0' = Bit is cle | ared             | x = Bit is unknown |         |  |

|                                    |                                           |                |                 |                  |                  |                    |         |  |

| bit 15-9                           | Unimplemen                                | ted: Read as ' | 0'              |                  |                  |                    |         |  |

| bit 8-0                            | PLLDIV<8:0>                               | : PLL Feedba   | ck Divisor bits | (also denoted    | as 'M', PLL mul  | tiplier)           |         |  |

|                                    | 111111111 =                               | = 513          |                 |                  |                  |                    |         |  |

|                                    | •                                         |                |                 |                  |                  |                    |         |  |

|                                    | •                                         |                |                 |                  |                  |                    |         |  |

|                                    | •                                         |                |                 |                  |                  |                    |         |  |

|                                    | 000110000 =                               | = 50 (default) |                 |                  |                  |                    |         |  |

|                                    |                                           |                |                 |                  |                  |                    |         |  |

|                                    | •                                         |                |                 |                  |                  |                    |         |  |

|                                    | 000000010 =<br>000000001 =<br>000000000 = | = 3            |                 |                  |                  |                    |         |  |

|                                    |                                           |                |                 |                  |                  |                    |         |  |

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

#### REGISTER 16-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

| R/W-0           | R/W-0                                                                      | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |  |  |  |

|-----------------|----------------------------------------------------------------------------|----------------|-------|--------------|-----------------|----------|-------|--|--|--|

|                 |                                                                            |                | PDC   | <15:8>       |                 |          |       |  |  |  |

| bit 15          |                                                                            |                |       |              |                 |          | bit 8 |  |  |  |

|                 |                                                                            |                |       |              |                 |          |       |  |  |  |

| R/W-0           | R/W-0                                                                      | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |  |  |  |

|                 |                                                                            |                | PDC   | x<7:0>       |                 |          |       |  |  |  |

| bit 7           |                                                                            |                |       |              |                 |          | bit 0 |  |  |  |

|                 |                                                                            |                |       |              |                 |          |       |  |  |  |

| Legend:         |                                                                            |                |       |              |                 |          |       |  |  |  |

| R = Readable    | bit                                                                        | W = Writable b | oit   | U = Unimpler | mented bit, rea | d as '0' |       |  |  |  |

| -n = Value at P | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |       |              |                 |          |       |  |  |  |

bit 15-0 **PDCx<15:0>:** PWMx Generator # Duty Cycle Value bits

#### REGISTER 16-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | PHAS  | Ex<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PHAS  | SEx<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | pit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

Note 1: If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCON<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INDXH | LD<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INDXF | ILD<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

## REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

#### REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                                                                      | R/W-0          | R/W-0                            | R/W-0                               | R/W-0                                                                                 | R/W-0                                                                                                                                                     | R/W-0                                                                                         |  |  |  |  |

|----------------------------------------------------------------------------|----------------|----------------------------------|-------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                            |                | QEIIC                            | <31:24>                             |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |  |

|                                                                            |                |                                  |                                     |                                                                                       |                                                                                                                                                           | bit 8                                                                                         |  |  |  |  |

|                                                                            |                |                                  |                                     |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |  |

| R/W-0                                                                      | R/W-0          | R/W-0                            | R/W-0                               | R/W-0                                                                                 | R/W-0                                                                                                                                                     | R/W-0                                                                                         |  |  |  |  |

|                                                                            |                | QEIIC                            | <23:16>                             |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |  |

|                                                                            |                |                                  |                                     |                                                                                       |                                                                                                                                                           | bit 0                                                                                         |  |  |  |  |

|                                                                            |                |                                  |                                     |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |  |

|                                                                            |                |                                  |                                     |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |  |

| it                                                                         | W = Writable I | bit                              | U = Unimplen                        | nented bit, rea                                                                       | ıd as '0'                                                                                                                                                 |                                                                                               |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |                                  |                                     |                                                                                       |                                                                                                                                                           |                                                                                               |  |  |  |  |

|                                                                            | R/W-0          | R/W-0 R/W-0<br>it W = Writable I | QEIIC<br>R/W-0 R/W-0 QEIIC<br>QEIIC | QEIIC<31:24><br>R/W-0 R/W-0 R/W-0<br>QEIIC<23:16><br>it W = Writable bit U = Unimplen | QEIIC<31:24>           R/W-0         R/W-0         R/W-0           QEIIC<23:16>           it         W = Writable bit         U = Unimplemented bit, real | QEIIC<31:24>           R/W-0         R/W-0         R/W-0         R/W-0           QEIIC<23:16> |  |  |  |  |

bit 15-0 **QEIIC<31:16>:** High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | QEII  | C<15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | QEI   | C<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit C |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 **QEIIC<15:0>:** Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

| R/W-0           | R/W-0                                                                      | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |  |  |

|-----------------|----------------------------------------------------------------------------|----------------|-------|--------------|------------------|----------|-------|--|--|--|--|

|                 |                                                                            |                | INTHL | D<31:24>     |                  |          |       |  |  |  |  |

| bit 15          |                                                                            |                |       |              |                  |          | bit 8 |  |  |  |  |

|                 |                                                                            |                |       |              |                  |          |       |  |  |  |  |

| R/W-0           | R/W-0                                                                      | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |  |  |

|                 |                                                                            |                | INTHL | D<23:16>     |                  |          |       |  |  |  |  |

| bit 7           |                                                                            |                |       |              |                  |          | bit 0 |  |  |  |  |

|                 |                                                                            |                |       |              |                  |          |       |  |  |  |  |

| Legend:         |                                                                            |                |       |              |                  |          |       |  |  |  |  |

| R = Readable I  | bit                                                                        | W = Writable b | oit   | U = Unimplen | nented bit, read | d as '0' |       |  |  |  |  |

| -n = Value at P | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |       |              |                  |          |       |  |  |  |  |

bit 15-0 INTHLD<31:16>: Hold Register for Reading and Writing INT1TMRH bits

## REGISTER 17-20: INT1HLDL: INTERVAL 1 TIMER HOLD LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

|                 |       |                  | INTHL | .D<15:8>         |                  |                 |       |

| bit 15          |       |                  |       |                  |                  |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | INTH  | _D<7:0>          |                  |                 |       |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                  |                 |       |

bit 15-0 INTHLD<15:0>: Hold Register for Reading and Writing INT1TMRL bits

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | <b>`</b>              |                                                 |                                |                          |                  |                 |                 |  |

|---------------|-----------------------|-------------------------------------------------|--------------------------------|--------------------------|------------------|-----------------|-----------------|--|

| R/W-0         | R-0                   | R-0                                             | R-0                            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |  |

| TXENn         | TXABTn                | TXLARBn                                         | TXERRn                         | TXREQn                   | RTRENn           | TXnPRI1         | TXnPRI0         |  |

| bit 15        |                       |                                                 |                                |                          |                  |                 | bit 8           |  |

| R/W-0         | R-0                   | R-0                                             | R-0                            | R/W-0                    | R/W-0            | R/W-0           | R/W-0           |  |

| TXENm         | TXABTm <sup>(1)</sup> | TXLARBm <sup>(1)</sup>                          | TXERRm <sup>(1)</sup>          | TXREQm                   | RTRENm           | TXmPRI1         | TXmPRI0         |  |

| bit 7         |                       | 1                                               | 1                              |                          |                  |                 | bit (           |  |

| Legend:       |                       |                                                 |                                |                          |                  |                 |                 |  |

| R = Readable  | e bit                 | W = Writable                                    | bit                            | U = Unimpler             | mented bit, read | d as '0'        |                 |  |

| -n = Value at | POR                   | '1' = Bit is set                                |                                | '0' = Bit is cle         | ared             | x = Bit is unkr | nown            |  |

| bit 15-8      | See Dofinition        | n for bits<7:0>,                                | Controls Ruffs                 | ar n                     |                  |                 |                 |  |

| bit 7         |                       | RX Buffer Sele                                  |                                |                          |                  |                 |                 |  |

|               |                       | RA Buller Sele                                  |                                |                          |                  |                 |                 |  |

|               |                       | RBn is a receive                                |                                |                          |                  |                 |                 |  |

| bit 6         | TXABTm: M             | essage Aborted                                  | 1 bit <sup>(1)</sup>           |                          |                  |                 |                 |  |

|               | 1 = Message           | •                                               |                                |                          |                  |                 |                 |  |

|               | •                     | completed trar                                  | nsmission succ                 | essfully                 |                  |                 |                 |  |

| bit 5         | TXLARBm: N            | Message Lost A                                  | Arbitration bit <sup>(1)</sup> | )                        |                  |                 |                 |  |

|               |                       | lost arbitration                                |                                |                          |                  |                 |                 |  |

|               | 0 = Message           | did not lose ar                                 | bitration while                | being sent               |                  |                 |                 |  |

| bit 4         | TXERRm: Er            | ror Detected D                                  | uring Transmis                 | ssion bit <sup>(1)</sup> |                  |                 |                 |  |

|               |                       | or occurred wh                                  | •                              | •                        |                  |                 |                 |  |

|               |                       | or did not occu                                 |                                | ssage was bei            | ing sent         |                 |                 |  |

| bit 3         |                       | essage Send F                                   | -                              |                          |                  |                 |                 |  |

|               | sent                  |                                                 | -                              |                          | -                | n the message   | is successfully |  |

|               |                       | the bit to '0' wh                               | •                              | 0                        | abort            |                 |                 |  |

| bit 2         |                       | uto-Remote Tra                                  |                                |                          |                  |                 |                 |  |

|               |                       | emote transmit<br>emote transmit                |                                |                          |                  |                 |                 |  |

| bit 1-0       | TXmPRI<1:0            | TXmPRI<1:0>: Message Transmission Priority bits |                                |                          |                  |                 |                 |  |

|               |                       | message prior                                   |                                |                          |                  |                 |                 |  |

|               |                       | ermediate mes                                   |                                |                          |                  |                 |                 |  |

|               |                       | ermediate mess<br>message priori                |                                |                          |                  |                 |                 |  |

|               | 00 – Lowest           | messaye priori                                  | ıy                             |                          |                  |                 |                 |  |

| Note 1: Th    | nis bit is cleared    | when TXREQ i                                    | s set.                         |                          |                  |                 |                 |  |

|               |                       |                                                 |                                |                          |                  |                 |                 |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

| _                    |                              |                                 |                         |                        |                      |                      |                      |

|----------------------|------------------------------|---------------------------------|-------------------------|------------------------|----------------------|----------------------|----------------------|

| R/W-0                | U-0                          | U-0                             | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| ADRC                 | —                            | —                               | SAMC4 <sup>(1)</sup>    | SAMC3 <sup>(1)</sup>   | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |

| bit 15               |                              |                                 |                         |                        |                      |                      | bit 8                |

|                      |                              |                                 |                         |                        |                      |                      |                      |

| R/W-0                | R/W-0                        | R/W-0                           | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |

| ADCS7 <sup>(2)</sup> | ADCS6 <sup>(2)</sup>         | ADCS5 <sup>(2)</sup>            | ADCS4 <sup>(2)</sup>    | ADCS3 <sup>(2)</sup>   | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |

| bit 7                |                              |                                 |                         |                        |                      |                      | bit 0                |

| r                    |                              |                                 |                         |                        |                      |                      |                      |

| Legend:              |                              |                                 |                         |                        |                      |                      |                      |

| R = Readable b       |                              | W = Writable k                  | bit                     | •                      | nented bit, read     | l as '0'             |                      |

| -n = Value at P      | OR                           | '1' = Bit is set                |                         | '0' = Bit is clea      | ared                 | x = Bit is unkr      | nown                 |

| bit 15               | 1 = ADC inter                |                                 |                         |                        |                      |                      |                      |

|                      |                              | ved from syste                  |                         |                        |                      |                      |                      |

| bit 14-13            | •                            | ted: Read as '0                 |                         |                        |                      |                      |                      |

| bit 12-8             |                              | Auto-Sample T                   | ime bits <sup>(1)</sup> |                        |                      |                      |                      |

|                      | 11111 = <b>31</b> T          | AD                              |                         |                        |                      |                      |                      |

|                      | •                            |                                 |                         |                        |                      |                      |                      |

|                      | •                            |                                 |                         |                        |                      |                      |                      |

|                      | 00001 = 1 TA<br>00000 = 0 TA |                                 |                         |                        |                      |                      |                      |

| bit 7-0              | ADCS<7:0>:                   | ADC1 Convers                    | ion Clock Sele          | ct bits <sup>(2)</sup> |                      |                      |                      |

|                      | 11111111 = <sup>-</sup><br>• | TP • (ADCS<7:                   | 0> + 1) = TP •          | 256 = Tad              |                      |                      |                      |

|                      | •                            |                                 |                         |                        |                      |                      |                      |

|                      | 00000010 = -                 | TP • (ADCS<7:                   | 0> + 1) = TP •          | 3 = TAD                |                      |                      |                      |

|                      | 0000001 =                    | TP • (ADCS<7:<br>TP • (ADCS<7:  | 0> + 1) = TP •          | 2 <b>=</b> Tad         |                      |                      |                      |

|                      | •                            | d if SSRC<2:0><br>if ADRC (AD10 | •                       | ,                      | nd SSRCG (AD         | 1CON1<4>) =          | 0.                   |

#### REGISTER 23-3: AD1CON3: ADC1 CONTROL REGISTER 3

| R/W-0           | R/W-0                                                                                                                      | R/W-0                                                                             | R/W-0                                                                                                                                             | R/W-0                                                                                                        | R/W-0            | R/W-0           | R/W-0   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------|-----------------|---------|

| PTGCLK2         | PTGCLK1                                                                                                                    | PTGCLK0                                                                           | PTGDIV4                                                                                                                                           | PTGDIV3                                                                                                      | PTGDIV2          | PTGDIV1         | PTGDIV0 |

| bit 15          | 1                                                                                                                          | 1                                                                                 | 1                                                                                                                                                 |                                                                                                              | 1                |                 | bit     |

| R/W-0           | R/W-0                                                                                                                      | R/W-0                                                                             | R/W-0                                                                                                                                             | U-0                                                                                                          | R/W-0            | R/W-0           | R/W-0   |

| PTGPWD3         | PTGPWD2                                                                                                                    | PTGPWD1                                                                           | PTGPWD0                                                                                                                                           | _                                                                                                            | PTGWDT2          | PTGWDT1         | PTGWDTC |

| bit 7           |                                                                                                                            |                                                                                   |                                                                                                                                                   |                                                                                                              |                  |                 | bit     |

| Legend:         |                                                                                                                            |                                                                                   |                                                                                                                                                   |                                                                                                              |                  |                 |         |

| R = Readable    | bit                                                                                                                        | W = Writable                                                                      | bit                                                                                                                                               | U = Unimpler                                                                                                 | mented bit, read | l as '0'        |         |

| -n = Value at F | POR                                                                                                                        | '1' = Bit is set                                                                  |                                                                                                                                                   | '0' = Bit is cle                                                                                             | ared             | x = Bit is unkr | nown    |

| bit 15-13       | 111 = Reserv<br>110 = Reserv<br>101 = PTG m<br>100 = PTG m<br>011 = PTG m<br>010 = PTG m<br>001 = PTG m                    |                                                                                   | urce will be T3<br>urce will be T2<br>urce will be T1<br>urce will be TA<br>urce will be Fc                                                       | SCLK<br>SCLK<br>CLK<br>D<br>DSC                                                                              |                  |                 |         |

| bit 12-8        | PTGDIV<4:0> 11111 = Divic 11110 = Divic                                                                                    | de-by-31<br>de-by-2                                                               | Clock Presca                                                                                                                                      | ler (divider) bi                                                                                             | ts               |                 |         |

| bit 7-4         | PTGPWD<3:0<br>1111 = All trig<br>1110 = All trig<br>0001 = All trig                                                        | <b>D&gt;:</b> PTG Trigge<br>gger outputs ar<br>gger outputs ar<br>gger outputs ar | e 16 PTG cloc<br>e 15 PTG cloc<br>e 2 PTG clock                                                                                                   | k cycles wide<br>k cycles wide<br>cycles wide                                                                |                  |                 |         |

| bit 3           | Unimplemen                                                                                                                 | ted: Read as '                                                                    | 0'                                                                                                                                                |                                                                                                              |                  |                 |         |

| bit 2-0         | PTGWDT<2:0<br>111 = Watcho<br>110 = Watcho<br>101 = Watcho<br>011 = Watcho<br>011 = Watcho<br>010 = Watcho<br>010 = Watcho |                                                                                   | Watchdog Tir<br>ime-out after 5<br>ime-out after 2<br>ime-out after 1<br>ime-out after 3<br>ime-out after 3<br>ime-out after 3<br>ime-out after 8 | 12 PTG clock<br>56 PTG clock<br>28 PTG clock<br>4 PTG clocks<br>2 PTG clocks<br>6 PTG clocks<br>6 PTG clocks | S<br>S           | 5               |         |

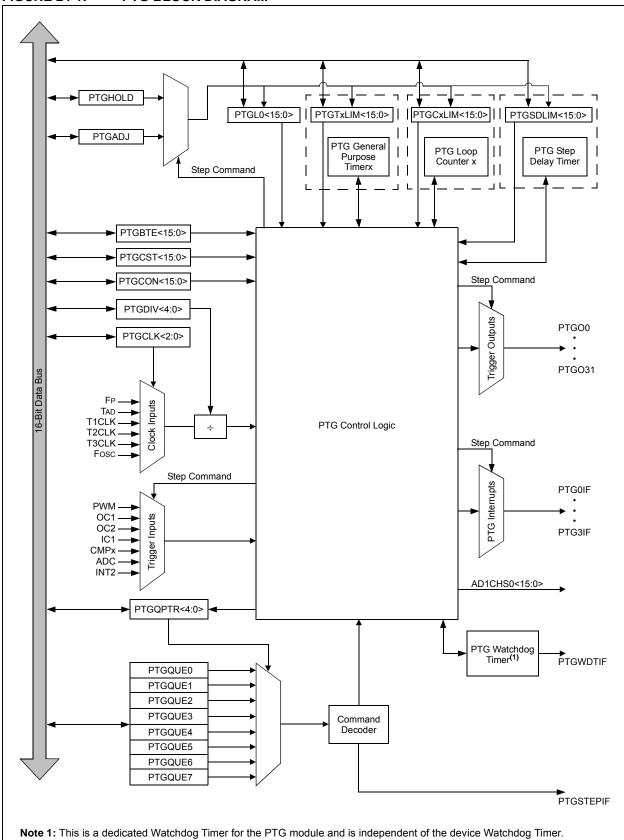

## REGISTER 24-2: PTGCON: PTG CONTROL REGISTER

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | .IM<7:0> |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

# REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|---------------|-------|-------|-------|-------|-------|-------|--|

|        | PTGHOLD<15:8> |       |       |       |       |       |       |  |

| bit 15 |               |       |       |       |       |       | bit 8 |  |

| R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|--------------|-------|-------|-------|-------|-------|-------|--|

|       | PTGHOLD<7:0> |       |       |       |       |       |       |  |

| bit 7 |              |       |       |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

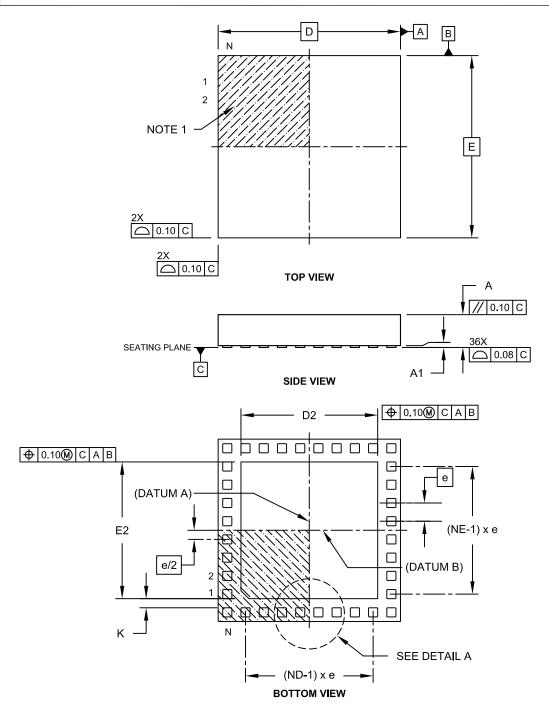

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-187C Sheet 1 of 2

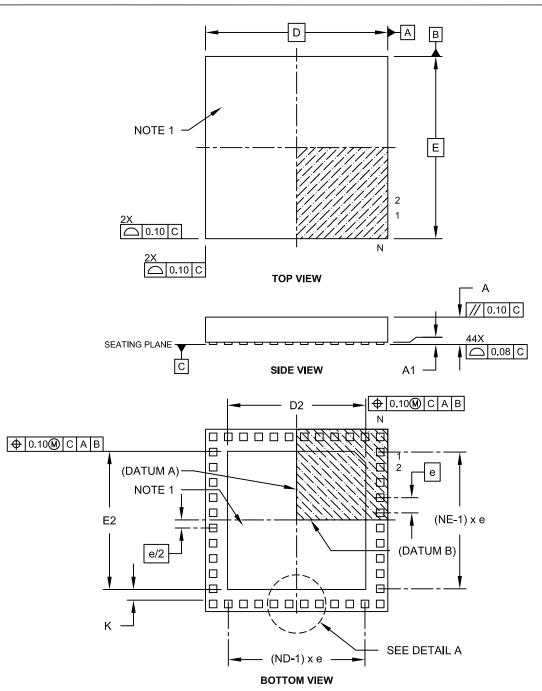

## 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-157C Sheet 1 of 2

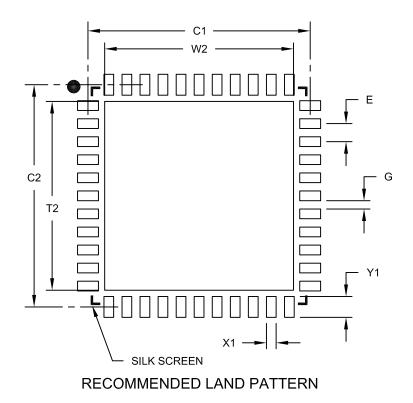

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimension                  | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch              | E           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 6.60 |

| Optional Center Pad Length | T2          |      |          | 6.60 |

| Contact Pad Spacing        | C1          |      | 8.00     |      |

| Contact Pad Spacing        | C2          |      | 8.00     |      |

| Contact Pad Width (X44)    | X1          |      |          | 0.35 |

| Contact Pad Length (X44)   | Y1          |      |          | 0.85 |

| Distance Between Pads      | G           | 0.25 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

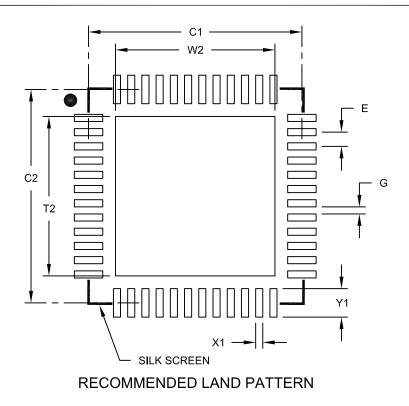

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimensior                  | n Limits    | MIN  | NOM      | MAX  |

| Contact Pitch              | E           |      | 0.40 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 4.45 |

| Optional Center Pad Length | T2          |      |          | 4.45 |

| Contact Pad Spacing        | C1          |      | 6.00     |      |

| Contact Pad Spacing        | C2          |      | 6.00     |      |

| Contact Pad Width (X28)    | X1          |      |          | 0.20 |

| Contact Pad Length (X28)   | Y1          |      |          | 0.80 |

| Distance Between Pads      | G           | 0.20 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A

# TABLE A-1:MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                 | Update Description                                                                                                                                                       |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical<br>Characteristics" | Removed Voltage on VCAP with respect to Vss and added Note 5 in Absolute Maximum Ratings <sup>(1)</sup> .                                                                |

|                                              | Removed Parameter DC18 (VCORE) and Note 3 from the DC Temperature and Voltage Specifications (see Table 30-4).                                                           |

|                                              | Updated Note 1 in the DC Characteristics: Operating Current (IDD) (see Table 30-6).                                                                                      |

|                                              | Updated Note 1 in the DC Characteristics: Idle Current (IIDLE) (see Table 30-7).                                                                                         |

|                                              | Changed the Typical values for Parameters DC60a-DC60d and updated Note 1 in the DC Characteristics: Power-down Current (IPD) (see Table 30-8).                           |

|                                              | Updated Note 1 in the DC Characteristics: Doze Current (IDOZE) (see Table 30-9).                                                                                         |

|                                              | Updated Note 2 in the Electrical Characteristics: BOR (see Table 30-12).                                                                                                 |

|                                              | Updated Parameters CM20 and CM31, and added Parameters CM44 and CM45 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                  |

|                                              | Added the Op amp/Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                            |

|                                              | Added Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                           |

|                                              | Updated Internal FRC Accuracy Parameter F20a (see Table 30-21).                                                                                                          |

|                                              | Updated the Typical value and Units for Parameter CTMUI1, and added Parameters CTMUI4, CTMUFV1, and CTMUFV2 to the CTMU Current Source Specifications (see Table 30-55). |

| Section 31.0 "Packaging<br>Information"      | Updated packages by replacing references of VLAP with TLA.                                                                                                               |

| "Product Identification<br>System"           | Changed VLAP to TLA.                                                                                                                                                     |

#### TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)

NOTES:

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support