#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

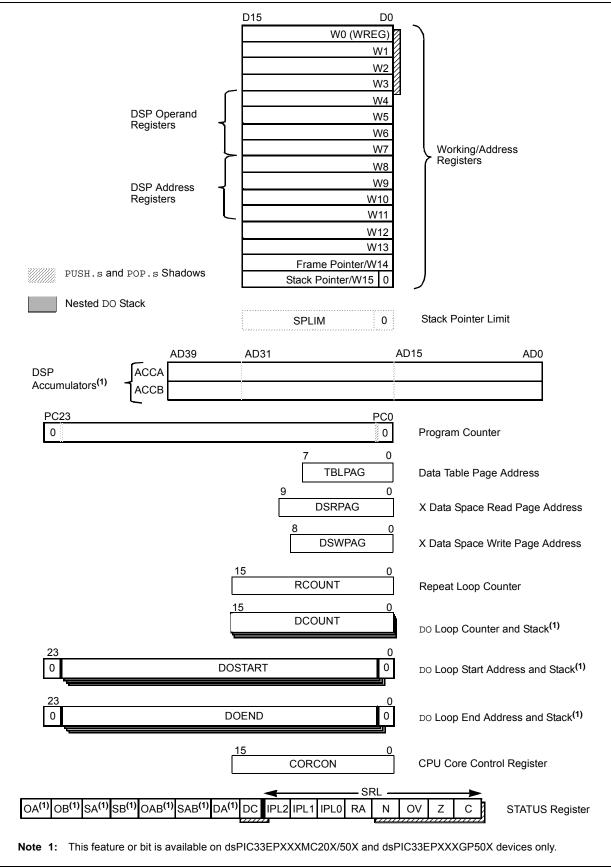

#### 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: Cl                                          | PU STATUS I                            | REGISTER                    |                          |                    |                   |               |

|------------------------|------------------------------------------------------|----------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|

| R/W-0                  | R/W-0                                                | R/W-0                                  | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                    | SA <sup>(1,4)</sup>                    | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |

| bit 15                 |                                                      |                                        |                             |                          |                    |                   | bit 8         |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                               | R/W-0 <sup>(2,3)</sup>                 | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |

| IPL2                   | IPL1                                                 | IPL0                                   | RA                          | N                        | OV                 | Z                 | С             |

| bit 7                  | ·                                                    | •                                      |                             | •                        |                    |                   | bit (         |

| Legend:                |                                                      | C = Clearable                          | e bit                       |                          |                    |                   |               |

| R = Readab             | le bit                                               | W = Writable                           | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |

| -n = Value a           | t POR                                                | '1'= Bit is set                        |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |

|                        |                                                      |                                        |                             |                          |                    |                   |               |

| bit 15                 | OA: Accumul                                          | ator A Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator A has over                        | flowed                      |                          |                    |                   |               |

|                        | 0 = Accumula                                         | ator A has not o                       | verflowed                   |                          |                    |                   |               |

| bit 14                 | OB: Accumul                                          | ator B Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator B has over                        | flowed                      |                          |                    |                   |               |

|                        |                                                      | ator B has not c                       |                             |                          |                    |                   |               |

| bit 13                 | SA: Accumul                                          | ator A Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        |                                                      | ator A is saturat<br>ator A is not sat |                             | en saturated at          | some time          |                   |               |

| bit 12                 | SB: Accumul                                          | ator B Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        | 1 = Accumula                                         | ator B is saturat<br>ator B is not sat | ted or has bee              |                          | some time          |                   |               |

| bit 11                 |                                                      | B Combined A                           |                             | vorflow Status           | ы#(1)              |                   |               |

|                        |                                                      | ators A or B have                      |                             | vernow Status            | DIL                |                   |               |

|                        |                                                      | ccumulators A                          |                             | erflowed                 |                    |                   |               |

| bit 10                 |                                                      | B Combined Ad                          |                             |                          | (1)                |                   |               |

|                        |                                                      |                                        |                             |                          | urated at some     | time              |               |

|                        | 0 = Neither A                                        | ccumulators A                          | or B are satur              | ated                     |                    |                   |               |

| bit 9                  | DA: DO Loop                                          | Active bit <sup>(1)</sup>              |                             |                          |                    |                   |               |

|                        | 1 = DO <b>loop is</b>                                | s in progress                          |                             |                          |                    |                   |               |

|                        | 0 = DO <b>loop</b> is                                | s not in progres                       | S                           |                          |                    |                   |               |

| bit 8                  | DC: MCU AL                                           | U Half Carry/Bo                        | orrow bit                   |                          |                    |                   |               |

|                        |                                                      | out from the 4th sult occurred         | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |

|                        | 0 = No carry                                         |                                        |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |

|                        | his bit is available                                 |                                        |                             |                          |                    |                   | -             |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1. |                                        |                             |                          |                    |                   |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

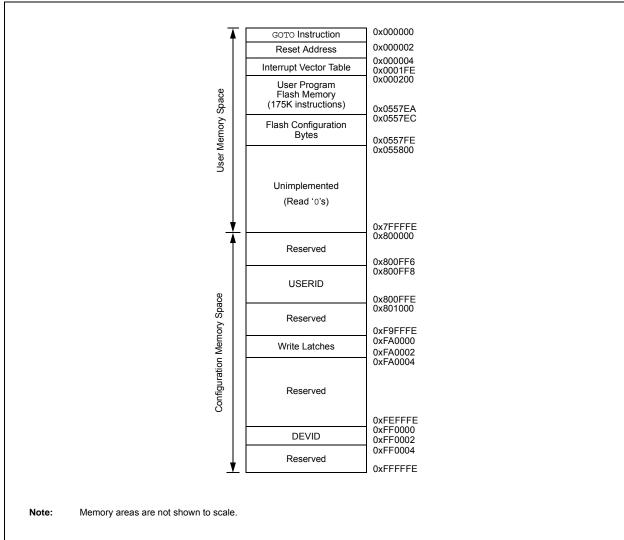

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

# 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

# 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

# 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

# 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

| TABLE 4   | -12:     | PWM RI         | EGISTE      | R MAP      | FOR de      | sPIC33E      | PXXXN   | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE  | S ONI | _Y    |            |       |               |

|-----------|----------|----------------|-------------|------------|-------------|--------------|---------|----------|----------|---------|-------|--------|---------|-------|-------|------------|-------|---------------|

| File Name | Addr.    | Bit 15         | Bit 14      | Bit 13     | Bit 12      | Bit 11       | Bit 10  | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

| PTCON     | 0C00     | PTEN           | —           | PTSIDL     | SESTAT      | SEIEN        | EIPU    | SYNCPOL  | SYNCOEN  | SYNCEN  | SY    | NCSRC< | 2:0>    |       | SEV   | /TPS<3:0>  |       | 0000          |

| PTCON2    | 0C02     | _              | —           | _          | _           | _            | —       | _        | —        | —       | _     | —      | _       | —     |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER     | 0C04     |                |             |            |             |              |         |          | PTPER<15 | :0>     |       |        |         |       |       |            |       | 00F8          |

| SEVTCMP   | 0C06     |                |             |            |             |              |         |          | SEVTCMP< | 5:0>    |       |        |         |       |       |            |       | 0000          |

| MDC       | 0C0A     |                |             |            |             |              |         |          | MDC<15:  | )>      |       |        |         |       |       |            |       | 0000          |

| CHOP      | 0C1A     | CHPCLKEN       | _           | _          | _           | _            | _       |          |          |         |       | CHOPCI | _K<9:0> |       |       |            |       | 0000          |

| PWMKEY    | 0C1E     |                |             |            |             |              |         |          | PWMKEY<1 | 5:0>    |       |        |         |       |       |            |       | 0000          |

| Legend: - | – = unir | mplemented, re | ead as '0'. | Reset valu | es are show | vn in hexade | ecimal. |          |          |         |       |        |         |       |       |            |       | -             |

# TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |         |                |          | I OIT U                                        |        |           |          |        | 1102- |        |       |          |       |       |               |

|-----------|-------|---------|--------|---------|----------------|----------|------------------------------------------------|--------|-----------|----------|--------|-------|--------|-------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12         | Bit 11   | Bit 10                                         | Bit 9  | Bit 8     | Bit 7    | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN         | CLIEN    | TRGIEN                                         | ITB    | MDCS      | DTC<     | :1:0>  | DTCP  | _      | MTBS  | CAM      | XPRES | IUE   | 0000          |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | POLL           | PMOD     | <1:0>                                          | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTDA | T<1:0> | CLDA  | T<1:0>   | SWAP  | OSYNC | C000          |

| FCLCON1   | 0C24  | _       |        | (       | CLSRC<4:       | 0>       | CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0>     |        |           |          |        |       | D<1:0> | 0000  |          |       |       |               |

| PDC1      | 0C26  |         |        |         |                |          | PDC1<15:0> FF                                  |        |           |          |        |       |        | FFF8  |          |       |       |               |

| PHASE1    | 0C28  |         |        |         | PHASE1<15:0> 0 |          |                                                |        |           |          |        |       | 0000   |       |          |       |       |               |

| DTR1      | 0C2A  | _       | _      |         |                |          |                                                |        |           | DTR1<13: | 0>     |       |        |       |          |       |       | 0000          |

| ALTDTR1   | 0C2C  | _       | _      |         |                |          |                                                |        | А         | LTDTR1<1 | 3:0>   |       |        |       |          |       |       | 0000          |

| TRIG1     | 0C32  |         |        |         |                |          |                                                |        | TRGCMP<18 | 5:0>     |        |       |        |       |          |       |       | 0000          |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |                | _        | _                                              | _      | _         | _        | _      |       |        | TRG   | STRT<5:0 | >     |       | 0000          |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLF            | FLTLEBEN | CLLEBEN                                        | _      | _         | _        | _      | BCH   | BCL    | BPHH  | BPHL     | BPLH  | BPLL  | 0000          |

| LEBDLY1   | 0C3C  | _       | _      | —       | —              |          | LEB<11:0> 00                                   |        |           |          |        |       |        | 0000  |          |       |       |               |

| AUXCON1   | 0C3E  | —       | —      | _       |                |          | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN |        |           |          |        |       | 0000   |       |          |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4-2  | 23: E | CAN1 I | REGIST                                  | ER MA  | P WHE                | N WIN        | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC                   | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|--------|-----------------------------------------|--------|----------------------|--------------|--------|---------------|-----------|----------------------------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15 | Bit 14                                  | Bit 13 | Bit 12               | Bit 11       | Bit 10 | Bit 9         | Bit 8     | Bit 7                      | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  |        |                                         |        | EID<                 | :15:8>       |        |               |           |                            |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF12SID | 0470  |        | SID<10:3> SID<2:0> — EXIDE — EID<17:16> |        |                      |              |        |               | xxxx      |                            |          |        |        |        |        |       |       |               |

| C1RXF12EID | 0472  |        | EID<15:8>                               |        |                      | :8> EID<7:0> |        |               |           |                            |          | xxxx   |        |        |        |       |       |               |

| C1RXF13SID | 0474  |        |                                         |        | SID<10:3> SID<2:0> - |              |        |               |           | _                          | EXIDE    | —      | EID<1  | 7:16>  | xxxx   |       |       |               |

| C1RXF13EID | 0476  |        |                                         |        | EID<                 | :15:8>       |        |               |           |                            |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF14SID | 0478  |        |                                         |        | SID<                 | :10:3>       |        |               |           | SID<2:0> — EXIDE — EID<17: |          |        |        |        |        | 7:16> | xxxx  |               |

| C1RXF14EID | 047A  |        |                                         |        | EID<                 | :15:8>       |        |               |           | EID<7:0>                   |          |        |        |        |        |       | xxxx  |               |

| C1RXF15SID | 047C  |        |                                         |        | SID<                 | :10:3>       |        |               |           |                            | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF15EID | 047E  |        |                                         |        | EID<                 | :15:8>       |        |               |           |                            |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

#### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

NOTES:

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |  |  |  |

|--------|-----|-------|------------|-------|--------|-------|-------|--|--|--|--|

| —      | —   |       |            | RP43  | R<5:0> |       |       |  |  |  |  |

| bit 15 |     |       |            |       |        |       | bit 8 |  |  |  |  |

|        |     |       |            |       |        |       |       |  |  |  |  |

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |  |  |  |

| —      | —   |       | RP42R<5:0> |       |        |       |       |  |  |  |  |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|--|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |  |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

| R/W-0                                                                                                                                                                                                                                                                                                                                                           | U-0   | U-0              | U-0   | U-0                  | U-0              | R/W-0              | R/W-0   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------|----------------------|------------------|--------------------|---------|

| CHPCLKEN                                                                                                                                                                                                                                                                                                                                                        | —     | —                | —     | —                    | —                | CHOPC              | LK<9:8> |

| bit 15                                                                                                                                                                                                                                                                                                                                                          |       |                  |       |                      |                  |                    | bit 8   |

|                                                                                                                                                                                                                                                                                                                                                                 |       |                  |       |                      |                  |                    |         |

| R/W-0                                                                                                                                                                                                                                                                                                                                                           | R/W-0 | R/W-0            | R/W-0 | R/W-0                | R/W-0            | R/W-0              | R/W-0   |

|                                                                                                                                                                                                                                                                                                                                                                 |       |                  | CHOPC | LK<7:0>              |                  |                    |         |

| bit 7                                                                                                                                                                                                                                                                                                                                                           |       |                  |       |                      |                  |                    | bit 0   |

|                                                                                                                                                                                                                                                                                                                                                                 |       |                  |       |                      |                  |                    |         |

| Legend:                                                                                                                                                                                                                                                                                                                                                         |       |                  |       |                      |                  |                    |         |

| R = Readable I                                                                                                                                                                                                                                                                                                                                                  | bit   | W = Writable     | bit   | U = Unimplei         | mented bit, read | as '0'             |         |

| -n = Value at P                                                                                                                                                                                                                                                                                                                                                 | OR    | '1' = Bit is set |       | '0' = Bit is cleared |                  | x = Bit is unknown |         |

| bit 15<br>bit 15<br>bit 15<br>cHPCLKEN: Enable Chop Clock Generator bit<br>1 = Chop clock generator is enabled<br>0 = Chop clock generator is disabled<br>bit 14-10<br>bit 9-0<br>cHOPCLK<9:0>: Chop Clock Divider bits<br>The frequency of the chop clock signal is given by the following expression:<br>Chop Frequency = (FP/PCLKDIV<2:0)/(CHOPCLK<9:0> + 1) |       |                  |       |                      |                  |                    |         |

# REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

#### REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                 |       |                  | MDC   | <15:8>                             |       |                 |       |

| bit 15          |       |                  |       |                                    |       |                 | bit 8 |

|                 |       |                  |       |                                    |       |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                 |       |                  | MD    | C<7:0>                             |       |                 |       |

| bit 7           |       |                  |       |                                    |       |                 | bit 0 |

|                 |       |                  |       |                                    |       |                 |       |

| Legend:         |       |                  |       |                                    |       |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

# 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

- 3: There are minimum bit rates of approximately FCY/512. As a result, high processor speeds may not support 100 Kbit/second operation. See timing specifications, IM10 and IM11, and the "Baud Rate Generator" in the "dsPIC33/PIC24 Family Reference Manual".

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two Inter-Integrated Circuit (I<sup>2</sup>C) modules: I2C1 and I2C2.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The  $I^2C$  module has a 2-pin interface:

- · The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

- Intelligent Platform Management Interface (IPMI)

support

- System Management Bus (SMBus) support

# 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier)

acceptance filters

- · Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

# 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F. The PIC24EP instruction set is almost identical to that of the PIC24F and PIC24H.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

# 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X AC characteristics and timing parameters.

#### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |

|--------------------|--------------------------------------------------------------------------|

| AC CHARACTERISTICS | $\begin{array}{llllllllllllllllllllllllllllllllllll$                     |

|                    | Characteristics".                                                        |

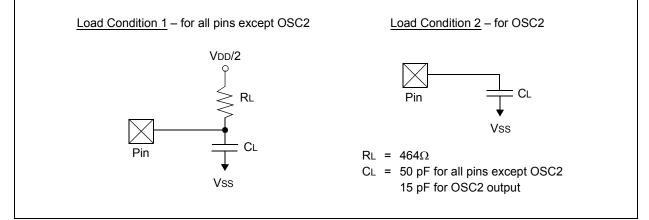

#### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    |      | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | —    | 400  | pF    | In I <sup>2</sup> C™ mode                                           |

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                  | (unless | d Operati<br>otherwis | <b>e stated)</b><br>ature -4 | 0°C ≤ T⁄ | <b>.0V to 3.6V</b><br>A $\leq$ +85°C for Industrial<br>A $\leq$ +125°C for Extended |

|--------------------|--------|------------------------------------------------------------------|---------|-----------------------|------------------------------|----------|-------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                   | Min.    | Typ. <sup>(1)</sup>   | Max.                         | Units    | Conditions                                                                          |

| OS50               | Fplli  | PLL Voltage Controlled Oscillator<br>(VCO) Input Frequency Range | 0.8     | _                     | 8.0                          | MHz      | ECPLL, XTPLL modes                                                                  |

| OS51               | Fvco   | On-Chip VCO System Frequency                                     | 120     | —                     | 340                          | MHz      |                                                                                     |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                    | 0.9     | 1.5                   | 3.1                          | ms       |                                                                                     |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                           | -3      | 0.5                   | 3                            | %        |                                                                                     |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases, or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if Fosc = 120 MHz and the SPIx bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

#### TABLE 30-19: INTERNAL FRC ACCURACY

| AC CHARACTERISTICS          |                        | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |             |       |                                         |                |  |

|-----------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-------|-----------------------------------------|----------------|--|

| Param<br>No. Characteristic |                        | Min.                                                                                                                                                                                                                                                                         | Тур.       | Max.        | Units | Conditions                              |                |  |

| Internal                    | FRC Accuracy @ FRC Fre | equency =                                                                                                                                                                                                                                                                    | : 7.37 MHz | <u>,(1)</u> |       |                                         |                |  |

| F20a                        | FRC                    | -1.5                                                                                                                                                                                                                                                                         | 0.5        | +1.5        | %     | $-40^{\circ}C \le TA \le -10^{\circ}C$  | VDD = 3.0-3.6V |  |

|                             |                        | -1                                                                                                                                                                                                                                                                           | 0.5        | +1          | %     | $-10^{\circ}C \le TA \le +85^{\circ}C$  | VDD = 3.0-3.6V |  |

| F20b                        | FRC                    | -2                                                                                                                                                                                                                                                                           | 1          | +2          | %     | $+85^{\circ}C \le TA \le +125^{\circ}C$ | VDD = 3.0-3.6V |  |

Note 1: Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| AC CHARACTERISTICS |                                                          | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |     |   |                                           |                |

|--------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---|-------------------------------------------|----------------|

| Param<br>No.       | Characteristic   Min.   Typ.   Max.   Units   Conditions |                                                                                                                                                                                                                                                                          | ons |     |   |                                           |                |

| LPRC (             | @ 32.768 kHz <sup>(1)</sup>                              |                                                                                                                                                                                                                                                                          |     |     |   |                                           |                |

| F21a               | LPRC                                                     | -30                                                                                                                                                                                                                                                                      | —   | +30 | % | $-40^{\circ}C \le TA \le -10^{\circ}C$    | VDD = 3.0-3.6V |

|                    |                                                          | -20                                                                                                                                                                                                                                                                      | _   | +20 | % | $-10^{\circ}C \leq TA \leq +85^{\circ}C$  | VDD = 3.0-3.6V |

| F21b               | LPRC                                                     | -30                                                                                                                                                                                                                                                                      | _   | +30 | % | $+85^{\circ}C \leq TA \leq +125^{\circ}C$ | VDD = 3.0-3.6V |

**Note 1:** The change of LPRC frequency as VDD changes.

# TABLE 30-45:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | Standard Op<br>(unless othe<br>Operating ter | rwise st            | <b>ated)</b><br>e -40°C ⊴ | ≤ Ta ≤ +8 | <b>o 3.6V</b><br>35°C for Industrial<br>125°C for Extended |

|--------------------|-----------------------|----------------------------------------------|----------------------------------------------|---------------------|---------------------------|-----------|------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                         | Тур. <sup>(2)</sup> | Max.                      | Units     | Conditions                                                 |

| SP70               | FscP                  | Maximum SCK1 Input<br>Frequency              | _                                            |                     | Lesser of FP or 15        | MHz       | (Note 3)                                                   |

| SP72               | TscF                  | SCK1 Input Fall Time                         | _                                            |                     |                           | ns        | See Parameter DO32<br>(Note 4)                             |

| SP73               | TscR                  | SCK1 Input Rise Time                         | —                                            |                     | —                         | ns        | See Parameter DO31<br>(Note 4)                             |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | —                                            |                     | _                         | ns        | See Parameter DO32<br>(Note 4)                             |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                            |                     | —                         | ns        | See Parameter DO31<br>(Note 4)                             |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                            | 6                   | 20                        | ns        |                                                            |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                           |                     | _                         | ns        |                                                            |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                           |                     |                           | ns        |                                                            |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                           |                     | —                         | ns        |                                                            |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                          |                     | —                         | ns        |                                                            |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                           | _                   | 50                        | ns        | (Note 4)                                                   |

| SP52               | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                        | 1.5 Tcy + 40                                 | _                   | _                         | ns        | (Note 4)                                                   |

| SP60               | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge     | —                                            | _                   | 50                        | ns        |                                                            |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

# 33.0 PACKAGING INFORMATION

#### 33.1 Package Marking Information

#### 28-Lead SPDIP

#### 28-Lead SOIC (.300")

28-Lead SSOP

Example dsPIC33EP64GP 502-I/SP@3 1310017

# Example

#### Example

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>of or customer-specific information.                                                                                                                                                                                              |

# **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources". All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.

All other major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>256-Kbyte Flash and<br>32-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | The content on the first page of this section was extensively reworked to provide the reader with the key features and functionality of this device family in an "at-a-glance" format.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 1.0 "Device<br>Overview"                                                                                                                                        | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X Block Diagram (see Figure 1-1), which now contains a CPU<br>block and a reference to the CPU diagram.<br>Updated the description and Note references in the Pinout I/O Descriptions for these                                                                                                                                                                                                                                                                                                                                                              |

| Section 2.0 "Guidelines for<br>Getting Started with 16-bit<br>Digital Signal Controllers<br>and Microcontrollers"                                                       | pins: C1IN2-, C2IN2-, C3IN2-, OA1OUT, OA2OUT, and OA3OUT (see Table 1-1).<br>Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Section 3.0 "CPU"                                                                                                                                                       | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X CPU Block Diagram (see Figure 3-1).<br>Updated the Status register definition in the Programmer's Model (see Figure 3-2).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Section 4.0 "Memory<br>Organization"                                                                                                                                    | Updated the Data Memory Maps (see Figure 4-6 and Figure 4-11).<br>Removed the DCB<1:0> bits from the OC1CON2, OC2CON2, OC3CON2, and<br>OC4CON2 registers in the Output Compare 1 Through Output Compare 4 Register<br>Map (see Table 4-10).<br>Added the TRIG1 and TRGCON1 registers to the PWM Generator 1 Register Map<br>(see Table 4-13).<br>Added the TRIG2 and TRGCON2 registers to the PWM Generator 2 Register Map<br>(see Table 4-14).<br>Added the TRIG3 and TRGCON3 registers to the PWM Generator 3 Register Map<br>(see Table 4-15).<br>Updated the second note in Section 4.7.1 "Bit-Reversed Addressing<br>Implementation". |

| Section 8.0 "Direct Memory<br>Access (DMA)"                                                                                                                             | Updated the DMA Controller diagram (see Figure 8-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Section 14.0 "Input<br>Capture"                                                                                                                                         | Updated the bit values for the ICx clock source of the ICTSEL<12:10> bits in the ICxCON1 register (see Register 14-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 15.0 "Output<br>Compare"                                                                                                                                        | Updated the bit values for the OCx clock source of the OCTSEL<2:0> bits in the OCxCON1 register (see Register 15-1).<br>Removed the DCB<1:0> bits from the Output Compare x Control Register 2 (see Register 15-2).                                                                                                                                                                                                                                                                                                                                                                                                                        |

TABLE A-2: MAJOR SECTION UPDATES

| Section Name                    | Update Description                                                                                                                                                   |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Section 30.0 "Electrical        | These SPI2 Timing Requirements were updated:                                                                                                                         |  |  |

| Characteristics"<br>(Continued) | <ul> <li>Maximum value for Parameter SP10 and the minimum clock period value for<br/>SCKx in Note 3 (see Table 30-36, Table 30-37, and Table 30-38)</li> </ul>       |  |  |

|                                 | <ul> <li>Maximum value for Parameter SP70 and the minimum clock period value for<br/>SCKx in Note 3 (see Table 30-40 and Table 30-42)</li> </ul>                     |  |  |

|                                 | The Maximum Data Rate values were updated for the SPI2 Maximum Data/Clock<br>Rate Summary (see Table 30-43)                                                          |  |  |

|                                 | These SPI1 Timing Requirements were updated:                                                                                                                         |  |  |

|                                 | Maximum value for Parameters SP10 and the minimum clock period value for SCKx in Note 3 (see Table 30-44, Table 30-45, and Table 30-46)                              |  |  |