#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502-h-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

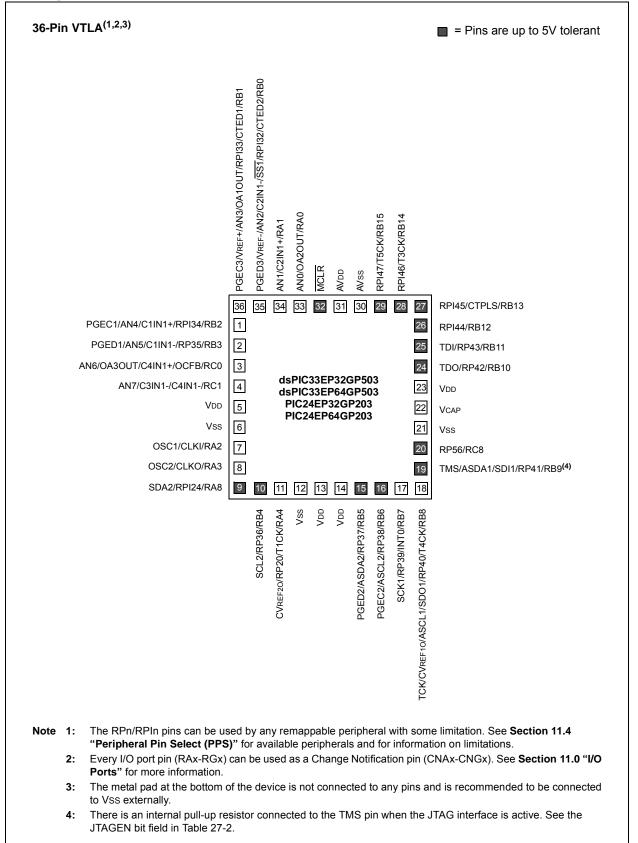

#### **Pin Diagrams (Continued)**

#### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | -      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

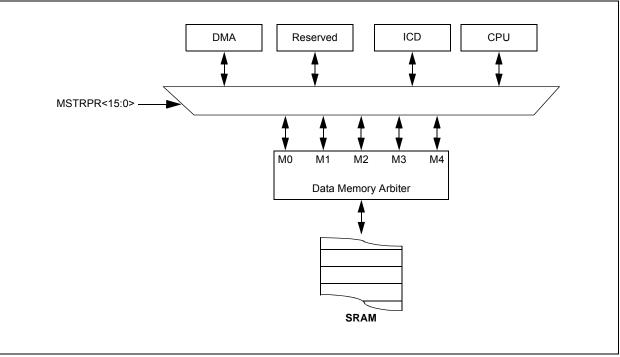

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

### FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

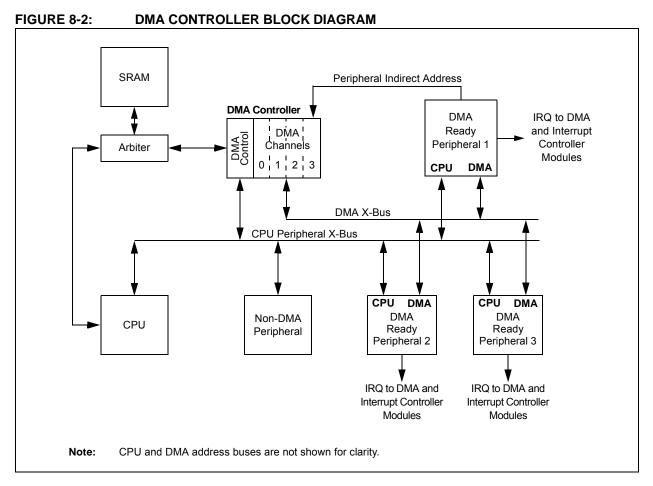

### 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0 | U-0             | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-----|-----------------|-------|--------------|------------------|--------|-------|

| —              | —   | —               | —     | —            | —                | -      | —     |

| bit 15         |     |                 |       |              |                  |        | bit 8 |

|                |     |                 |       |              |                  |        |       |

| R-0            | R-0 | R-0             | R-0   | R-0          | R-0              | R-0    | R-0   |

|                |     |                 | DSADR | <23:16>      |                  |        |       |

| bit 7          |     |                 |       |              |                  |        | bit 0 |

|                |     |                 |       |              |                  |        |       |

| Legend:        |     |                 |       |              |                  |        |       |

| R = Readable b | it  | W = Writable bi | t     | U = Unimpler | nented bit, read | as '0' |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0                                                                        | R-0 | R-0 | R-0  | R-0      | R-0 | R-0 | R-0   |

|----------------------------------------------------------------------------|-----|-----|------|----------|-----|-----|-------|

|                                                                            |     |     | DSAD | DR<15:8> |     |     |       |

| bit 15                                                                     |     |     |      |          |     |     | bit 8 |

|                                                                            |     |     |      |          |     |     |       |

| R-0                                                                        | R-0 | R-0 | R-0  | R-0      | R-0 | R-0 | R-0   |

|                                                                            |     |     | DSA  | DR<7:0>  |     |     |       |

| bit 7                                                                      |     |     |      |          |     |     | bit 0 |

|                                                                            |     |     |      |          |     |     |       |

| Legend:                                                                    |     |     |      |          |     |     |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |     |     |      |          |     |     |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |     |      |          |     | own |       |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

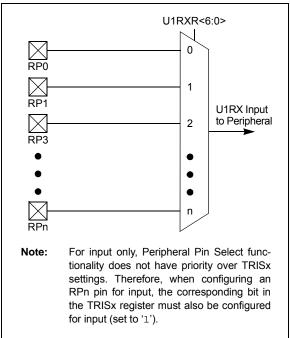

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

# 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

### 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32.

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | R/W-x                                                                                                                         | U-0                           | U-0              | U-0              | R/W-x            | R/W-x            | R/W-x   |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|------------------|------------------|------------------|---------|--|--|--|

| —             | WAKFIL                                                                                                                        |                               | —                |                  | SEG2PH2          | SEG2PH1          | SEG2PH0 |  |  |  |

| bit 15        |                                                                                                                               |                               |                  |                  |                  |                  | bit     |  |  |  |

|               |                                                                                                                               |                               |                  |                  |                  |                  |         |  |  |  |

| R/W-x         | R/W-x                                                                                                                         | R/W-x                         | R/W-x            | R/W-x            | R/W-x            | R/W-x            | R/W-x   |  |  |  |

| SEG2PHTS      | S SAM                                                                                                                         | SEG1PH2                       | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1           | PRSEG0  |  |  |  |

| bit 7         |                                                                                                                               |                               |                  |                  |                  |                  | bit     |  |  |  |

| Legend:       |                                                                                                                               |                               |                  |                  |                  |                  |         |  |  |  |

| R = Readabl   | le bit                                                                                                                        | W = Writable                  | bit              | U = Unimpler     | nented bit, read | d as '0'         |         |  |  |  |

| -n = Value at | t POR                                                                                                                         | '1' = Bit is set              |                  | '0' = Bit is cle |                  | x = Bit is unkr  | nown    |  |  |  |

|               |                                                                                                                               |                               |                  |                  |                  |                  |         |  |  |  |

| bit 15        | Unimplemen                                                                                                                    | nted: Read as '               | 0'               |                  |                  |                  |         |  |  |  |

| bit 14        | WAKFIL: Sel                                                                                                                   | lect CAN Bus L                | ine Filter for V | Vake-up bit      |                  |                  |         |  |  |  |

|               |                                                                                                                               | N bus line filter             |                  |                  |                  |                  |         |  |  |  |

|               |                                                                                                                               | line filter is not            |                  | e-up             |                  |                  |         |  |  |  |

| bit 13-11     | -                                                                                                                             | ted: Read as '                |                  |                  |                  |                  |         |  |  |  |

| bit 10-8      | <b>SEG2PH&lt;2:0&gt;:</b> Phase Segment 2 bits<br>111 = Length is 8 x TQ                                                      |                               |                  |                  |                  |                  |         |  |  |  |

|               |                                                                                                                               |                               |                  |                  |                  |                  |         |  |  |  |

|               | •                                                                                                                             |                               |                  |                  |                  |                  |         |  |  |  |

|               |                                                                                                                               |                               |                  |                  |                  |                  |         |  |  |  |

|               | 000 = Length                                                                                                                  | n is 1 x Tq                   |                  |                  |                  |                  |         |  |  |  |

| bit 7         | SEG2PHTS: Phase Segment 2 Time Select bit                                                                                     |                               |                  |                  |                  |                  |         |  |  |  |

|               | 1 = Freely pro                                                                                                                | ogrammable                    |                  |                  | a Time (IPT). w  | /hichever is are | ater    |  |  |  |

| bit 6         | 0 = Maximum of SEG1PHx bits or Information Processing Time (IPT), whichever is greater<br>SAM: Sample of the CAN Bus Line bit |                               |                  |                  |                  |                  |         |  |  |  |

|               | 1 = Bus line i                                                                                                                | s sampled threes sampled once | e times at the   |                  |                  |                  |         |  |  |  |

| bit 5-3       | SEG1PH<2:0                                                                                                                    | <b>0&gt;:</b> Phase Segr      | nent 1 bits      | -                |                  |                  |         |  |  |  |

|               | 111 = Length is 8 x TQ                                                                                                        |                               |                  |                  |                  |                  |         |  |  |  |

|               | •                                                                                                                             |                               |                  |                  |                  |                  |         |  |  |  |

|               | •                                                                                                                             |                               |                  |                  |                  |                  |         |  |  |  |

|               | •                                                                                                                             |                               |                  |                  |                  |                  |         |  |  |  |

|               | 000 = Length                                                                                                                  |                               |                  |                  |                  |                  |         |  |  |  |

| bit 2-0       |                                                                                                                               | >: Propagation                | Time Segmen      | t bits           |                  |                  |         |  |  |  |

|               | 111 = Length                                                                                                                  | 1 IS 8 X TQ                   |                  |                  |                  |                  |         |  |  |  |

|               |                                                                                                                               |                               |                  |                  |                  |                  |         |  |  |  |

|               | •                                                                                                                             |                               |                  |                  |                  |                  |         |  |  |  |

|               | •                                                                                                                             |                               |                  |                  |                  |                  |         |  |  |  |

### REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

| R/W-0                                                                | R/W-0                                                                            | R/W-0                                 | R/W-0            | R/W-0              | R/W-0          | R/W-0           | R/W-0    |  |  |  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|------------------|--------------------|----------------|-----------------|----------|--|--|--|

| EDG1MOD                                                              | EDG1POL                                                                          | EDG1SEL3                              | EDG1SEL2         | EDG1SEL1           | EDG1SEL0       | EDG2STAT        | EDG1STAT |  |  |  |

| bit 15                                                               |                                                                                  | 1                                     |                  | 11                 |                |                 | bit 8    |  |  |  |

|                                                                      |                                                                                  |                                       |                  |                    |                |                 |          |  |  |  |

| R/W-0                                                                | R/W-0                                                                            | R/W-0                                 | R/W-0            | R/W-0              | R/W-0          | U-0             | U-0      |  |  |  |

| EDG2MOD                                                              | EDG2POL                                                                          | EDG2SEL3                              | EDG2SEL2         | EDG2SEL1           | EDG2SEL0       | _               | _        |  |  |  |

| bit 7                                                                |                                                                                  |                                       |                  | 1 1                |                |                 | bit C    |  |  |  |

|                                                                      |                                                                                  |                                       |                  |                    |                |                 |          |  |  |  |

| Legend:                                                              |                                                                                  |                                       |                  |                    |                |                 |          |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                  |                                       |                  |                    |                |                 |          |  |  |  |

| -n = Value at                                                        | t POR                                                                            | '1' = Bit is set                      |                  | '0' = Bit is clea  | red            | x = Bit is unkr | nown     |  |  |  |

|                                                                      |                                                                                  |                                       |                  |                    |                |                 |          |  |  |  |

| bit 15                                                               | EDG1MOD: E                                                                       | Edge 1 Edge Sa                        | ampling Mode     | Selection bit      |                |                 |          |  |  |  |

|                                                                      | 1 = Edge 1 is                                                                    | s edge-sensitive                      | 9                |                    |                |                 |          |  |  |  |

|                                                                      | •                                                                                | s level-sensitive                     |                  |                    |                |                 |          |  |  |  |

| bit 14                                                               |                                                                                  | dge 1 Polarity                        |                  |                    |                |                 |          |  |  |  |

|                                                                      |                                                                                  | s programmed f                        |                  |                    |                |                 |          |  |  |  |

|                                                                      | •                                                                                | s programmed f                        | •                | •                  |                |                 |          |  |  |  |

| bit 13-10                                                            | EDG1SEL<3:0>: Edge 1 Source Select bits                                          |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | 1xxx = Reserved<br>01xx = Reserved                                               |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | 0011 = CTED1 pin                                                                 |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | 0010 = CTED2 pin                                                                 |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | 0001 = OC1 module<br>0000 = Timer1 module                                        |                                       |                  |                    |                |                 |          |  |  |  |

| hit 0                                                                |                                                                                  |                                       | :+               |                    |                |                 |          |  |  |  |

| bit 9                                                                |                                                                                  | Edge 2 Status b                       |                  | vritten to control | the edge cou   | ree             |          |  |  |  |

|                                                                      | 1 = Edge 2 h                                                                     |                                       |                  |                    | i the edge sou | ice.            |          |  |  |  |

|                                                                      | 0 = Edge 2 has not occurred                                                      |                                       |                  |                    |                |                 |          |  |  |  |

| bit 8                                                                | EDG1STAT: E                                                                      | Edge 1 Status b                       | it               |                    |                |                 |          |  |  |  |

|                                                                      | Indicates the status of Edge 1 and can be written to control the edge source.    |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | <ul> <li>1 = Edge 1 has occurred</li> <li>0 = Edge 1 has not occurred</li> </ul> |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | -                                                                                |                                       |                  |                    |                |                 |          |  |  |  |

| bit 7                                                                |                                                                                  | Edge 2 Edge Sa                        |                  | Selection bit      |                |                 |          |  |  |  |

|                                                                      |                                                                                  | s edge-sensitive<br>s level-sensitive |                  |                    |                |                 |          |  |  |  |

| bit 6                                                                | •                                                                                | dge 2 Polarity                        |                  |                    |                |                 |          |  |  |  |

| Sit 0                                                                |                                                                                  | s programmed f                        |                  | dae response       |                |                 |          |  |  |  |

|                                                                      |                                                                                  | s programmed f                        |                  |                    |                |                 |          |  |  |  |

| bit 5-2                                                              | EDG2SEL<3                                                                        | : <b>0&gt;:</b> Edge 2 So             | urce Select bits | S                  |                |                 |          |  |  |  |

|                                                                      | 1111 = Reserved                                                                  |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | 01xx = Reserved                                                                  |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | 0100 = CMP <sup>2</sup><br>0011 = CTEE                                           |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      |                                                                                  | •                                     |                  |                    |                |                 |          |  |  |  |

|                                                                      | 0010 = CTED1 pin                                                                 |                                       |                  |                    |                |                 |          |  |  |  |

|                                                                      | 0001 = OC1                                                                       | module                                |                  |                    |                |                 |          |  |  |  |

|                                                                      | 0001 = OC1<br>0000 = IC1 m                                                       | module                                |                  |                    |                |                 |          |  |  |  |

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

| U-0          | U-0                                                                                                                                                                                                                  | U-0                                                                                                               | U-0           | U-0                                | U-0               | U-0            | R/W-0   |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------|-------------------|----------------|---------|--|--|--|--|

| —            | —                                                                                                                                                                                                                    | —                                                                                                                 | —             | —                                  | —                 | —              | ADDMAEN |  |  |  |  |

| bit 15       |                                                                                                                                                                                                                      |                                                                                                                   |               |                                    |                   |                | bit 8   |  |  |  |  |

|              |                                                                                                                                                                                                                      |                                                                                                                   |               |                                    |                   |                |         |  |  |  |  |

| U-0          | U-0                                                                                                                                                                                                                  | U-0                                                                                                               | U-0           | U-0                                | R/W-0             | R/W-0          | R/W-0   |  |  |  |  |

| —            |                                                                                                                                                                                                                      | —                                                                                                                 | —             | —                                  | DMABL2            | DMABL1         | DMABL0  |  |  |  |  |

| bit 7        |                                                                                                                                                                                                                      |                                                                                                                   |               |                                    |                   |                | bit 0   |  |  |  |  |

| Levend       |                                                                                                                                                                                                                      |                                                                                                                   |               |                                    |                   |                |         |  |  |  |  |

| Legend:      | le hit                                                                                                                                                                                                               |                                                                                                                   | .:.           |                                    | mented bit meet   |                |         |  |  |  |  |

| R = Readab   |                                                                                                                                                                                                                      | W = Writable b                                                                                                    | DIT           | U = Unimplemented bit, read as '0' |                   |                |         |  |  |  |  |

| -n = Value a | It POR                                                                                                                                                                                                               | '1' = Bit is set                                                                                                  |               | '0' = Bit is cle                   | eared             | x = Bit is unk | nown    |  |  |  |  |

| bit 15-9     | Unimplemen                                                                                                                                                                                                           | ted: Read as '0                                                                                                   | ,             |                                    |                   |                |         |  |  |  |  |

| bit 8        | -                                                                                                                                                                                                                    | ADC1 DMA Ena                                                                                                      |               |                                    |                   |                |         |  |  |  |  |

| DILO         |                                                                                                                                                                                                                      |                                                                                                                   |               |                                    | stor for transfor | to DAM using   |         |  |  |  |  |

|              | <ul> <li>1 = Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA</li> <li>0 = Conversion results are stored in ADC1BUF0 through ADC1BUFF registers; DMA will not be used</li> </ul> |                                                                                                                   |               |                                    |                   |                |         |  |  |  |  |

| bit 7-3      | Unimplemen                                                                                                                                                                                                           | ted: Read as '0                                                                                                   | )'            |                                    |                   |                |         |  |  |  |  |

| bit 2-0      | DMABL<2:0>                                                                                                                                                                                                           | Selects Numb                                                                                                      | per of DMA Bu | uffer Locations                    | per Analog Inp    | ut bits        |         |  |  |  |  |

|              | 111 = Allocates 128 words of buffer to each analog input                                                                                                                                                             |                                                                                                                   |               |                                    |                   |                |         |  |  |  |  |

|              | 110 = Allocates 64 words of buffer to each analog input                                                                                                                                                              |                                                                                                                   |               |                                    |                   |                |         |  |  |  |  |

|              | 101 = Allocates 32 words of buffer to each analog input                                                                                                                                                              |                                                                                                                   |               |                                    |                   |                |         |  |  |  |  |

|              |                                                                                                                                                                                                                      | 100 = Allocates 16 words of buffer to each analog input<br>011 = Allocates 8 words of buffer to each analog input |               |                                    |                   |                |         |  |  |  |  |

|              |                                                                                                                                                                                                                      | es 8 words of b<br>es 4 words of b                                                                                |               |                                    |                   |                |         |  |  |  |  |

|              |                                                                                                                                                                                                                      | es 2 words of b                                                                                                   |               |                                    |                   |                |         |  |  |  |  |

|              |                                                                                                                                                                                                                      | es 1 word of bu                                                                                                   |               | Û Î                                |                   |                |         |  |  |  |  |

|              |                                                                                                                                                                                                                      |                                                                                                                   |               | <b>U</b>                           |                   |                |         |  |  |  |  |

### REGISTER 23-4: AD1CON4: ADC1 CONTROL REGISTER 4

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER      | 25-3: CM40                                                                                                                                                                                                                                                   | CON: COMPA                                                                                                        | RATOR 4 CO          | ONTROL RE        | GISTER             |                     |                     |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------|------------------|--------------------|---------------------|---------------------|--|--|--|

| R/W-0         | R/W-0                                                                                                                                                                                                                                                        | R/W-0                                                                                                             | U-0                 | U-0              | U-0                | R/W-0               | R/W-0               |  |  |  |

| CON           | COE                                                                                                                                                                                                                                                          | CPOL                                                                                                              | —                   | —                | —                  | CEVT                | COUT                |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                              |                                                                                                                   |                     |                  |                    |                     | bit 8               |  |  |  |

| R/W-0         | DAM 0                                                                                                                                                                                                                                                        | U-0                                                                                                               | DAM 0               | U-0              | U-0                |                     | R/W-0               |  |  |  |

|               | R/W-0                                                                                                                                                                                                                                                        | 0-0                                                                                                               | R/W-0               | 0-0              | 0-0                | R/W-0               |                     |  |  |  |

| EVPOL1        | EVPOL0                                                                                                                                                                                                                                                       | —                                                                                                                 | CREF <sup>(1)</sup> | —                | —                  | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                              |                                                                                                                   |                     |                  |                    |                     | bit (               |  |  |  |

| Legend:       |                                                                                                                                                                                                                                                              |                                                                                                                   |                     |                  |                    |                     |                     |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                        | W = Writable                                                                                                      | bit                 | U = Unimple      | mented bit, rea    | d as '0'            |                     |  |  |  |

| -n = Value at |                                                                                                                                                                                                                                                              | '1' = Bit is se                                                                                                   |                     | '0' = Bit is cle |                    | x = Bit is unkn     | iown                |  |  |  |

|               |                                                                                                                                                                                                                                                              |                                                                                                                   |                     | 0 200000         |                    |                     |                     |  |  |  |

| bit 15        | CON: Comp                                                                                                                                                                                                                                                    | arator Enable b                                                                                                   | oit                 |                  |                    |                     |                     |  |  |  |

|               |                                                                                                                                                                                                                                                              | ator is enabled                                                                                                   |                     |                  |                    |                     |                     |  |  |  |

|               |                                                                                                                                                                                                                                                              | ator is disabled                                                                                                  |                     |                  |                    |                     |                     |  |  |  |

| bit 14        | COE: Comp                                                                                                                                                                                                                                                    | arator Output E                                                                                                   | nable bit           |                  |                    |                     |                     |  |  |  |

|               |                                                                                                                                                                                                                                                              | ator output is pr<br>ator output is in                                                                            |                     | xOUT pin         |                    |                     |                     |  |  |  |

| bit 13        | CPOL: Com                                                                                                                                                                                                                                                    | parator Output                                                                                                    | Polarity Select     | bit              |                    |                     |                     |  |  |  |

|               | 1 = Compara                                                                                                                                                                                                                                                  | ator output is in                                                                                                 | verted              |                  |                    |                     |                     |  |  |  |

|               | 0 = Compara                                                                                                                                                                                                                                                  | ator output is no                                                                                                 | ot inverted         |                  |                    |                     |                     |  |  |  |

| bit 12-10     | Unimpleme                                                                                                                                                                                                                                                    | nted: Read as                                                                                                     | '0'                 |                  |                    |                     |                     |  |  |  |

| bit 9         | CEVT: Comp                                                                                                                                                                                                                                                   | CEVT: Comparator Event bit                                                                                        |                     |                  |                    |                     |                     |  |  |  |

|               | interrup                                                                                                                                                                                                                                                     | ts until the bit is                                                                                               | cleared             | POL<1:0> set     | tings occurred;    | disables future     | triggers and        |  |  |  |

|               | •                                                                                                                                                                                                                                                            | ator event did r                                                                                                  |                     |                  |                    |                     |                     |  |  |  |

| bit 8         |                                                                                                                                                                                                                                                              | COUT: Comparator Output bit                                                                                       |                     |                  |                    |                     |                     |  |  |  |

|               | $\frac{\text{When CPOL} = 0 \text{ (non-inverted polarity):}}{1 = \text{VIN} + \text{VIN}}$                                                                                                                                                                  |                                                                                                                   |                     |                  |                    |                     |                     |  |  |  |

|               | 1 = VIN + > VIN - 0 = VIN + < VIN - 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0 = 0                                                                                                                              |                                                                                                                   |                     |                  |                    |                     |                     |  |  |  |

|               | When CPOL = 1 (inverted polarity):                                                                                                                                                                                                                           |                                                                                                                   |                     |                  |                    |                     |                     |  |  |  |

|               | 1 = VIN + < VIN-                                                                                                                                                                                                                                             |                                                                                                                   |                     |                  |                    |                     |                     |  |  |  |

|               | 0 = VIN+ > V                                                                                                                                                                                                                                                 | 'IN-                                                                                                              |                     |                  |                    |                     |                     |  |  |  |