Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   | s)<br>es)                      |                               |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

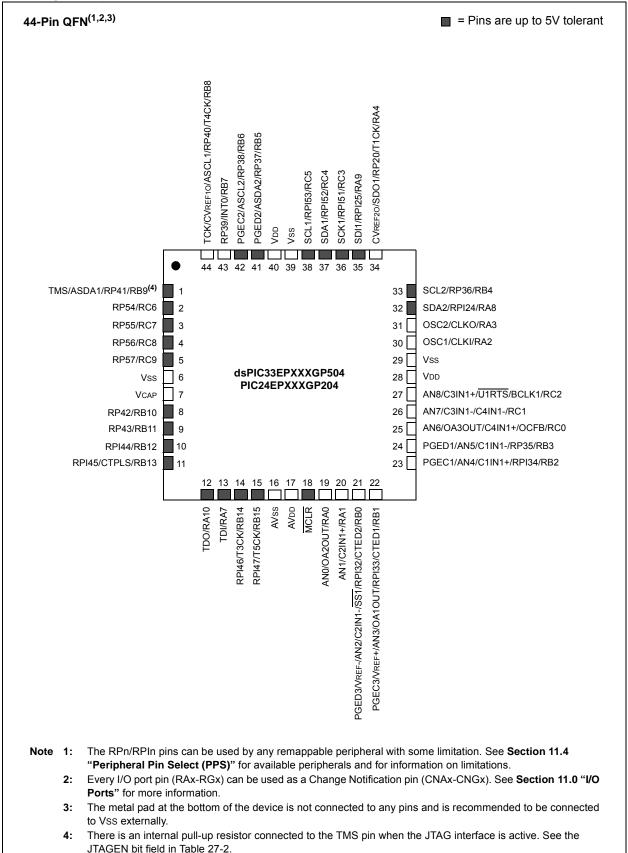

## **Pin Diagrams (Continued)**

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

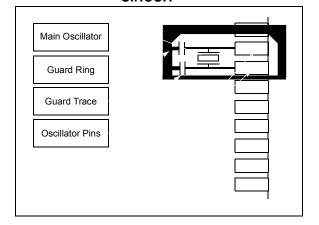

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

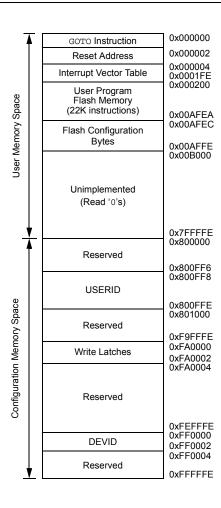

#### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00             |        |        |              | 011 401    |        |       | 20/00/    |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|------------------|--------|--------|--------------|------------|--------|-------|-----------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15           | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8     | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |                  |        |        |              |            |        |       | W0 (WR    | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |                  |        |        |              |            |        |       | W1        |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |                  | W2     |        |              |            |        |       |           |        |       | xxxx   |         |          |          |       |       |               |

| W3        | 0006  |                  |        |        |              |            |        |       | W3        |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |                  |        |        |              |            |        |       | W4        |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |                  |        |        |              |            |        |       | W5        |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |                  |        |        |              |            |        |       | W6        |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |                  |        |        |              |            |        |       | W7        |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |                  |        |        |              |            |        |       | W8        |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |                  |        |        |              |            |        |       | W9        |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |                  |        |        |              |            |        |       | W10       |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |                  |        |        |              |            |        |       | W11       |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |                  |        |        |              |            |        |       | W12       |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |                  |        |        |              |            |        |       | W13       |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |                  |        |        |              |            |        |       | W14       |        |       |        |         |          |          |       |       | xxxx          |

| W15       | 001E  |                  |        |        |              |            |        |       | W15       |        |       |        |         |          |          |       |       | xxxx          |

| SPLIM     | 0020  |                  |        |        |              |            |        |       | SPLI      | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |                  |        |        |              |            |        |       | ACCA      | L      |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |                  |        |        |              |            |        |       | ACCA      | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |                  |        | Si     | gn Extensior | n of ACCA< | 39>    |       |           |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |                  |        |        |              |            |        |       | ACCB      | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |                  |        |        |              |            |        |       | ACCB      | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |                  |        | Si     | gn Extensior | n of ACCB< | 39>    |       |           |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |                  |        |        |              |            |        | F     | PCL<15:0> |        |       |        |         |          |          |       | —     | 0000          |

| PCH       | 0030  | _                | _      | _      | —            | _          | _      | —     | _         | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _                | _      | _      | —            | _          | _      |       |           |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _                |        | _      | —            |            | _      | _     |           |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |                  |        |        |              |            |        |       | RCOUNT<   | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  | DCOUNT<15:0>     |        |        |              |            |        |       |           | 0000   |       |        |         |          |          |       |       |               |

| DOSTARTL  | 003A  | DOSTARTL<15:1> — |        |        |              |            |        |       |           | 0000   |       |        |         |          |          |       |       |               |

| DOSTARTH  | 003C  | _                | —      | —      | _            | —          | —      | _     | _         | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  | DOENDL<15:1> —   |        |        |              |            |        |       |           | 0000   |       |        |         |          |          |       |       |               |

| DOENDH    | 0040  | _                | —      | —      | —            | —          | —      | _     | —         | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |                  |        |        |              |            |        |       |           |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |  |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|--|

| 0/11        |                     |                | Before       |                        | After          |              |                        |  |  |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

## REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|------------------|----------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|

|              |                  |                                                          |       | DTCMP3R<6:0       | )>              |                 |       |

| bit 15       |                  |                                                          |       |                   |                 |                 | bit 8 |

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| 0-0          | R/W-0            | R/W-0                                                    | -     | DTCMP2R<6:0       |                 | R/W-0           | R/W-U |

| bit 7        |                  |                                                          |       |                   | 17              |                 | bit 0 |

| bit i        |                  |                                                          |       |                   |                 |                 | bit 0 |

| Legend:      |                  |                                                          |       |                   |                 |                 |       |

| R = Readab   | ole bit          | W = Writable                                             | bit   | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR           | '1' = Bit is set                                         |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                  |                                                          |       |                   |                 |                 |       |

|              |                  | nput tied to CMI                                         |       |                   |                 |                 |       |

| bit 7        | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |                   |                 |                 |       |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP43  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| —      | —   |       |       | RP42  | R<5:0> |       |       |

## REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP54  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

| R/W-0               | R/W-0          | R/W-0                              | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|---------------------|----------------|------------------------------------|-------|-------------------|-------|-----------------|-------|

|                     |                |                                    | TRGC  | MP<15:8>          |       |                 |       |

| bit 15              |                |                                    |       |                   |       |                 | bit 8 |

|                     |                |                                    |       |                   |       |                 |       |

| R/W-0               | R/W-0          | R/W-0                              | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|                     |                |                                    | TRGC  | MP<7:0>           |       |                 |       |

| bit 7               |                |                                    |       |                   |       |                 | bit 0 |

| Legend:             |                |                                    |       |                   |       |                 |       |

| R = Readable        | W = Writable t | U = Unimplemented bit, read as '0' |       |                   |       |                 |       |

| -n = Value at POR ' |                | '1' = Bit is set                   |       | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

## REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0        | U-0                          | R/W-0                                  | R/W-1, HC                  | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |

|--------------|------------------------------|----------------------------------------|----------------------------|------------------------------|------------------|-----------------|----------------|

| I2CEN        | _                            | I2CSIDL                                | SCLREL                     | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |

| bit 15       |                              |                                        |                            |                              |                  |                 | bit 8          |

|              |                              |                                        |                            |                              |                  |                 |                |

| R/W-0        | R/W-0                        | R/W-0                                  | R/W-0, HC                  | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |

| GCEN         | STREN                        | ACKDT                                  | ACKEN                      | RCEN                         | PEN              | RSEN            | SEN            |

| bit 7        |                              |                                        |                            |                              |                  |                 | bit 0          |

| Legend:      |                              | HC = Hardware                          | Cloarable bit              |                              |                  |                 |                |

| R = Readab   | le hit                       | W = Writable bi                        |                            | II = I Inimpler              | mented bit, rea  | d as '0'        |                |

| -n = Value a |                              | '1' = Bit is set                       | L .                        | '0' = Bit is cle             |                  | x = Bit is unk  | nown           |

|              |                              |                                        |                            |                              |                  |                 | nown           |

| bit 15       | <b>12CEN:</b> 12Cx           | Enable bit                             |                            |                              |                  |                 |                |

|              |                              | he I2Cx module                         |                            |                              |                  |                 | ;              |

|              | 0 = Disables                 | the I2Cx module;                       | all l <sup>2</sup> C™ pins | are controlled               | by port functior | ıs              |                |

| bit 14       | Unimplemen                   | ted: Read as '0'                       |                            |                              |                  |                 |                |

| bit 13       |                              | x Stop in Idle Mo                      |                            |                              |                  |                 |                |

|              |                              | ues module oper<br>s module operation  |                            |                              | dle mode         |                 |                |

| bit 12       |                              | Lx Release Conf                        |                            | _                            | ( clave)         |                 |                |

|              | 1 = Releases                 |                                        |                            |                              | slave)           |                 |                |

|              |                              | Lx clock low (clo                      | ck stretch)                |                              |                  |                 |                |

|              | If STREN = 1                 | <u>:</u>                               | -                          |                              |                  |                 |                |

|              | •                            | ., software can w                      |                            |                              |                  | ,               |                |

|              |                              | ing of every slav<br>reception. Hardw  |                            |                              |                  |                 | t every slave  |

|              | If STREN = 0                 | -                                      |                            |                              |                  |                 |                |

|              |                              | <u>.</u><br>, software can or          | nly write '1' to re        | elease clock). I             | Hardware is cle  | ar at the begir | ning of every  |

|              | -                            | te transmission.                       |                            |                              | -                | address byte re | eception.      |

| bit 11       |                              | ligent Peripheral                      |                            |                              |                  |                 |                |

|              | 1 = IPMI mod<br>0 = IPMI mod | e is enabled; all                      | addresses are              | Acknowledged                 | 1                |                 |                |

| bit 10       |                              | Slave Address b                        | i+                         |                              |                  |                 |                |

|              |                              | is a 10-bit slave                      |                            |                              |                  |                 |                |

|              |                              | is a 7-bit slave a                     |                            |                              |                  |                 |                |

| bit 9        | DISSLW: Dis                  | able Slew Rate C                       | Control bit                |                              |                  |                 |                |

|              |                              | control is disable                     |                            |                              |                  |                 |                |

|              |                              | control is enable                      |                            |                              |                  |                 |                |

| bit 8        |                              | us Input Levels b                      |                            | 0145                         | <b>c</b>         |                 |                |

|              |                              | /O pin thresholds<br>SMBus input thre  |                            | n SMBus speci                | fication         |                 |                |

| bit 7        |                              | ral Call Enable b                      |                            | ing as I <sup>2</sup> C slav | /e)              |                 |                |

|              | 1 = Enables in               | terrupt when a ge<br>all address disat | neral call addre           | -                            |                  | dule is enabled | for reception) |

|              |                              |                                        |                            |                              |                  |                 |                |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

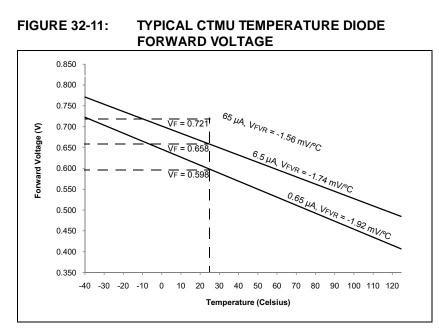

## FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

## 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | —   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

|        |     |     |     |          |          |          |          |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 15-12 Unimplemented: Read as '0'

| DIL 10-12 | Uninpienenteu. Reau as 0                                                                                                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                         |

|           | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

|           | 1110 <b>= FLT2</b>                                                                                                                                                                                                                             |

|           | 1101 <b>= PTGO19</b>                                                                                                                                                                                                                           |

|           | 1100 = PTGO18                                                                                                                                                                                                                                  |

|           | 1011 = Reserved                                                                                                                                                                                                                                |

|           | 1010 = Reserved                                                                                                                                                                                                                                |

|           | 1001 = Reserved                                                                                                                                                                                                                                |

|           | 1000 = Reserved                                                                                                                                                                                                                                |

|           | 0111 = Reserved                                                                                                                                                                                                                                |

|           | 0110 = Reserved                                                                                                                                                                                                                                |

|           | 0101 = PWM3H                                                                                                                                                                                                                                   |

|           | 0100 = PWM3L                                                                                                                                                                                                                                   |

|           | 0011 = PWM2H                                                                                                                                                                                                                                   |

|           | 0010 = PWM2L                                                                                                                                                                                                                                   |

|           | 0001 = PWM1H                                                                                                                                                                                                                                   |

|           | 0000 = PWM1L                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                         |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits 1111 = FLT4                                                                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2                                                                                                                                                                                                                     |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19                                                                                                                                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18                                                                                                                                                                                   |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved                                                                                                                                                                |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                          |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                       |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved                                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | R1 EXTERNAL CLOCK TIMING REQUIREMENTS <sup>(1)</sup> | ) |

|-------------------|------------------------------------------------------|---|

|-------------------|------------------------------------------------------|---|

| AC CHARACTERISTICS |                                      |                                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                                        |      |               |            |                                                                             |

|--------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|------------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol Characteristic <sup>(2)</sup> |                                                                                                    | Min.                                                                                                                                                                                                                                                                                | Тур.                                   | Max. | Units         | Conditions |                                                                             |

| TA10               | ТтхН                                 | T1CK High<br>Time                                                                                  | Synchronous<br>mode                                                                                                                                                                                                                                                                 | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns         | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |                                      |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                        | 35                                     | _    | —             | ns         |                                                                             |

| TA11               | ΤτχL                                 | T1CK Low<br>Time                                                                                   | Synchronous<br>mode                                                                                                                                                                                                                                                                 | Greater of:<br>20 or<br>(Tcy + 20)/N   | _    | _             | ns         | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |                                      |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                        | 10                                     |      | —             | ns         |                                                                             |

| TA15               | ΤτχΡ                                 | T1CK Input<br>Period                                                                               | Synchronous mode                                                                                                                                                                                                                                                                    | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | —             | ns         | N = prescale value<br>(1, 8, 64, 256)                                       |

| OS60               | Ft1                                  | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                                                                                                                                                                                                                                                                                     | DC                                     |      | 50            | kHz        |                                                                             |

| TA20               | TCKEXTMRL                            | Delay from External T1CK<br>Clock Edge to Timer<br>Increment                                       |                                                                                                                                                                                                                                                                                     | 0.75 Tcy + 40                          | _    | 1.75 Tcy + 40 | ns         |                                                                             |

Note 1: Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

### FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS |                 |                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |        |                                                   |

|--------------------|-----------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|--------|---------------------------------------------------|

| Param<br>No.       | Symbol          | Characteristic                                       | Min.                                                                                                                                                                                                                                                                                          | Тур. <sup>(2)</sup> | Max. | Units  | Conditions                                        |

| Compa              | rator AC Ch     | naracteristics                                       |                                                                                                                                                                                                                                                                                               |                     |      |        |                                                   |

| CM10               | TRESP           | Response Time <sup>(3)</sup>                         | —                                                                                                                                                                                                                                                                                             | 19                  | —    | ns     | V+ input step of 100 mV<br>V- input held at VDD/2 |

| CM11               | Тмс2о∨          | Comparator Mode<br>Change to Output Valid            | —                                                                                                                                                                                                                                                                                             | -                   | 10   | μs     |                                                   |

| Compa              | rator DC Ch     | naracteristics                                       |                                                                                                                                                                                                                                                                                               |                     |      |        |                                                   |

| CM30               | VOFFSET         | Comparator Offset<br>Voltage                         | —                                                                                                                                                                                                                                                                                             | ±10                 | 40   | mV     |                                                   |

| CM31               | VHYST           | Input Hysteresis<br>Voltage <sup>(3)</sup>           | _                                                                                                                                                                                                                                                                                             | 30                  | —    | mV     |                                                   |

| CM32               | Trise/<br>Tfall | Comparator Output Rise/<br>Fall Time <sup>(3)</sup>  | —                                                                                                                                                                                                                                                                                             | 20                  | —    | ns     | 1 pF load capacitance<br>on input                 |

| CM33               | Vgain           | Open-Loop Voltage<br>Gain <sup>(3)</sup>             | —                                                                                                                                                                                                                                                                                             | 90                  | —    | db     |                                                   |

| CM34               | VICM            | Input Common-Mode<br>Voltage                         | AVss                                                                                                                                                                                                                                                                                          | -                   | AVDD | V      |                                                   |

| Op Am              | p AC Chara      | cteristics                                           |                                                                                                                                                                                                                                                                                               |                     |      |        |                                                   |

| CM20               | SR              | Slew Rate <sup>(3)</sup>                             |                                                                                                                                                                                                                                                                                               | 9                   | _    | V/µs   | 10 pF load                                        |

| CM21a              | Рм              | Phase Margin<br>(Configuration A) <sup>(3,4)</sup>   | _                                                                                                                                                                                                                                                                                             | 55                  | —    | Degree | G = 100V/V; 10 pF load                            |

| CM21b              | Рм              | Phase Margin<br>(Configuration B) <sup>(3,5)</sup>   | _                                                                                                                                                                                                                                                                                             | 40                  | —    | Degree | G = 100V/V; 10 pF load                            |

| CM22               | Gм              | Gain Margin <sup>(3)</sup>                           | —                                                                                                                                                                                                                                                                                             | 20                  | _    | db     | G = 100V/V; 10 pF load                            |

| CM23a              | Gвw             | Gain Bandwidth<br>(Configuration A) <sup>(3,4)</sup> | _                                                                                                                                                                                                                                                                                             | 10                  | —    | MHz    | 10 pF load                                        |

| CM23b              | GBW             | Gain Bandwidth<br>(Configuration B) <sup>(3,5)</sup> | —                                                                                                                                                                                                                                                                                             | 6                   | —    | MHz    | 10 pF load                                        |

## TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 3: Parameter is characterized but not tested in manufacturing.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: Resistances can vary by ±10% between op amps.

NOTES:

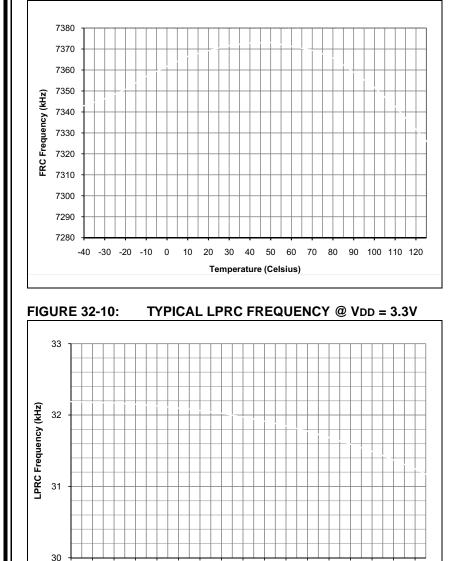

Temperature (Celsius)

70 80 90 100 110 120

TYPICAL FRC FREQUENCY @ VDD = 3.3V

-40 -30 -20 -10

0 10 20 30 40 50 60

**FIGURE 32-9:**

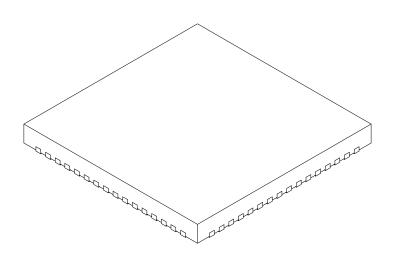

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                  |    | MILLIMETERS |          |      |  |

|------------------------|----|-------------|----------|------|--|

| Dimension Limits       |    | MIN         | NOM      | MAX  |  |

| Number of Pins         | N  | 64          |          |      |  |

| Pitch                  | е  | 0.50 BSC    |          |      |  |

| Overall Height         | A  | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1 | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3 | 0.20 REF    |          |      |  |

| Overall Width          | E  | 9.00 BSC    |          |      |  |

| Exposed Pad Width      | E2 | 5.30        | 5.40     | 5.50 |  |

| Overall Length         | D  |             | 9.00 BSC |      |  |

| Exposed Pad Length     | D2 | 5.30        | 5.40     | 5.50 |  |

| Contact Width          | b  | 0.20        | 0.25     | 0.30 |  |

| Contact Length         | L  | 0.30        | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K  | 0.20        | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2