Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\mathbf{X}$

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502-i-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2 | SFA: Stack Frame Active Status bit                                                        |

|-------|-------------------------------------------------------------------------------------------|

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and |

|       | DSWPAG values                                                                             |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space              |

| hit 1 | PND: Dounding Mode Select hit(1)                                                          |

- bit 1 **RND:** Rounding Mode Select bit<sup>(1)</sup>

- 1 = Biased (conventional) rounding is enabled

- 0 = Unbiased (convergent) rounding is enabled

bit 0 IF: Integer or Fractional Multiplier Mode Select bit<sup>(1)</sup> 1 = Integer mode is enabled for DSP multiply 0 = Fractional mode is enabled for DSP multiply

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- **2:** This bit is always read as '0'.

- 3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

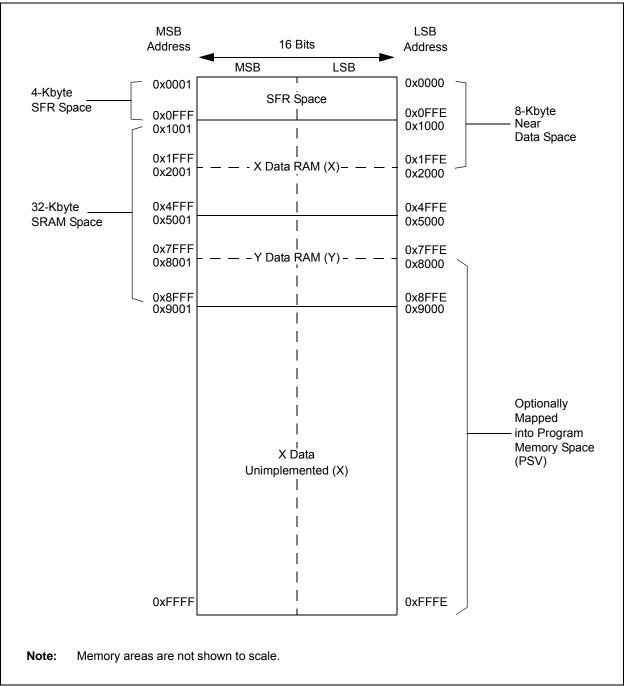

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

|                 |       |                         |                                                                                    |         |        |         |        |        |             |                           |       |       |       |        |          |        |        | All    |

|-----------------|-------|-------------------------|------------------------------------------------------------------------------------|---------|--------|---------|--------|--------|-------------|---------------------------|-------|-------|-------|--------|----------|--------|--------|--------|

| File Name       | Addr. | Bit 15                  | Bit 14                                                                             | Bit 13  | Bit 12 | Bit 11  | Bit 10 | Bit 9  | Bit 8       | Bit 7                     | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1  | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN                   | TGEN — PTGSIDL PTGTOGL — PTGSWT PTGSSEN PTGIVIS PTGSTRT PTGWTO — — — — PTGITM<1:0> |         |        |         |        |        |             |                           |       | 0000  |       |        |          |        |        |        |

| PTGCON          | 0AC2  | F                       | PTGCLK<2:0> PTGDIV<4:0>                                                            |         |        |         |        |        |             | PTGPWD<3:0> — PTGWDT<2:0> |       |       |       |        | 0>       | 0000   |        |        |

| PTGBTE          | 0AC4  |                         | ADC                                                                                | TS<4:1> |        | IC4TSS  | IC3TSS | IC2TSS | IC1TSS      | OC4CS                     | OC3CS | OC2CS | OC1CS | OC4TSS | OC3TSS   | OC2TSS | OC1TSS | 0000   |

| PTGHOLD         | 0AC6  |                         |                                                                                    |         |        |         |        |        | PTGHOLD     | <15:0>                    |       |       |       |        |          |        |        | 0000   |

| <b>PTGT0LIM</b> | 0AC8  |                         |                                                                                    |         |        |         |        |        | PTGT0LIM    | <15:0>                    |       |       |       |        |          |        |        | 0000   |

| PTGT1LIM        | 0ACA  |                         |                                                                                    |         |        |         |        |        | PTGT1LIM    | <15:0>                    |       |       |       |        |          |        |        | 0000   |

| PTGSDLIM        | 0ACC  |                         | PTGSDLIM<15:0> 000                                                                 |         |        |         |        |        |             |                           |       | 0000  |       |        |          |        |        |        |

| <b>PTGC0LIM</b> | 0ACE  |                         | PTGC0LIM<15:0> 000                                                                 |         |        |         |        |        |             |                           |       | 0000  |       |        |          |        |        |        |

| PTGC1LIM        | 0AD0  |                         | PTGC1LIM<15:0> 00                                                                  |         |        |         |        |        |             |                           |       | 0000  |       |        |          |        |        |        |

| PTGADJ          | 0AD2  |                         |                                                                                    |         |        |         |        |        | PTGADJ<     | :15:0>                    |       |       |       |        |          |        |        | 0000   |

| PTGL0           | 0AD4  |                         |                                                                                    |         |        |         |        |        | PTGL0<      | 15:0>                     |       |       |       |        |          |        |        | 0000   |

| PTGQPTR         | 0AD6  | —                       | —                                                                                  | —       | —      | _       | —      | —      | _           | —                         | —     | -     |       | P      | TGQPTR<4 | 4:0>   |        | 0000   |

| PTGQUE0         | 0AD8  |                         |                                                                                    |         | STEP   | 1<7:0>  |        |        |             |                           |       |       | STEPO | )<7:0> |          |        |        | 0000   |

| PTGQUE1         | 0ADA  |                         |                                                                                    |         | STEP   | '3<7:0> |        |        |             |                           |       |       | STEP2 | 2<7:0> |          |        |        | 0000   |

| PTGQUE2         | 0ADC  |                         |                                                                                    |         | STEP   | 25<7:0> |        |        |             |                           |       |       | STEP4 | <7:0>  |          |        |        | 0000   |

| PTGQUE3         | 0ADE  |                         |                                                                                    |         | STEP   | 7<7:0>  |        |        |             |                           |       |       | STEP6 | 6<7:0> |          |        |        | 0000   |

| PTGQUE4         | 0AE0  | STEP9<7:0> STEP8<7:0>   |                                                                                    |         |        |         |        |        |             | 0000                      |       |       |       |        |          |        |        |        |

| PTGQUE5         | 0AE2  | STEP11<7:0> STEP10<7:0> |                                                                                    |         |        |         |        |        |             |                           | 0000  |       |       |        |          |        |        |        |

| PTGQUE6         | 0AE4  | STEP13<7:0>             |                                                                                    |         |        |         |        |        | STEP12<7:0> |                           |       |       |       |        | 0000     |        |        |        |

| PTGQUE7         | 0AE6  |                         |                                                                                    |         | STEP   | 15<7:0> |        |        |             |                           |       |       | STEP1 | 4<7:0> |          |        |        | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

## 5.1 Table Instructions and Flash Programming

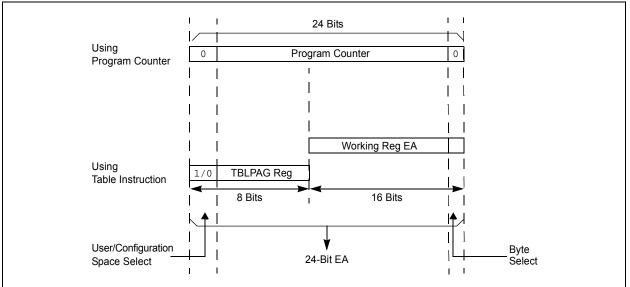

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| REGISTE       | R 16-7: PWMC                                                                                       | CONX: PWMX (                                                                                                                                  | CONTROL R     | EGISTER          |                      |                      |                     |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|----------------------|----------------------|---------------------|--|--|--|

| HS/HC-        | 0 HS/HC-0                                                                                          | HS/HC-0                                                                                                                                       | R/W-0         | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>                                                                         | TRGSTAT                                                                                                                                       | FLTIEN        | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |  |

| bit 15        | ·                                                                                                  | •                                                                                                                                             |               | ÷                |                      |                      | bit                 |  |  |  |

| R/W-0         | R/W-0                                                                                              | R/W-0                                                                                                                                         | U-0           | R/W-0            | R/W-0                | R/W-0                | R/W-0               |  |  |  |

| DTC1          |                                                                                                    | DTCP <sup>(3)</sup>                                                                                                                           | 0-0           | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |  |

| bit 7         | DICO                                                                                               | DICE                                                                                                                                          | _             | INT DO           | CAIM                 | AFRES'               | bit                 |  |  |  |

|               |                                                                                                    |                                                                                                                                               |               |                  |                      |                      | <u> </u>            |  |  |  |

| Legend:       |                                                                                                    | HC = Hardware                                                                                                                                 | Clearable bit | HS = Hardwa      | are Settable bit     |                      |                     |  |  |  |

| R = Reada     | able bit                                                                                           | W = Writable bi                                                                                                                               | t             | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |  |  |  |

| -n = Value    | at POR                                                                                             | '1' = Bit is set                                                                                                                              |               | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |  |  |  |

| bit 15        | ELTSTAT: ES                                                                                        | ult Interrupt Statu                                                                                                                           | is hit(1)     |                  |                      |                      |                     |  |  |  |

| DIL 15        |                                                                                                    | rrupt is pending                                                                                                                              |               |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | interrupt is pendi                                                                                                                            | ng            |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | ared by setting F                                                                                                                             |               |                  |                      |                      |                     |  |  |  |

| bit 14        |                                                                                                    | rent-Limit Interru                                                                                                                            | •             |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | mit interrupt is pe                                                                                                                           |               |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | nt-limit interrupt is<br>ared by setting C                                                                                                    |               |                  |                      |                      |                     |  |  |  |

| bit 13        |                                                                                                    | igger Interrupt S                                                                                                                             |               |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | terrupt is pendin                                                                                                                             |               |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | r interrupt is pen                                                                                                                            |               |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | ared by setting T                                                                                                                             |               |                  |                      |                      |                     |  |  |  |

| bit 12        |                                                                                                    | t Interrupt Enable                                                                                                                            | e bit         |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | rrupt is enabled rrupt is disabled                                                                                                            | and the FLTS  | TAT bit is clear | ed                   |                      |                     |  |  |  |

| bit 11        |                                                                                                    | ent-Limit Interrup                                                                                                                            |               |                  | cu .                 |                      |                     |  |  |  |

|               |                                                                                                    | mit interrupt is er                                                                                                                           |               |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | mit interrupt is di                                                                                                                           |               | e CLSTAT bit is  | s cleared            |                      |                     |  |  |  |

| bit 10        | TRGIEN: Trig                                                                                       | ger Interrupt En                                                                                                                              | able bit      |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | event generates                                                                                                                               |               |                  | T hit is cleared     |                      |                     |  |  |  |

| bit 9         |                                                                                                    | vent interrupts ar<br>dent Time Base I                                                                                                        |               |                  | i bit is cleared     |                      |                     |  |  |  |

| DIL 9         |                                                                                                    | register provides                                                                                                                             |               | riad for this PM | VM generator         |                      |                     |  |  |  |

|               |                                                                                                    | egister provides f                                                                                                                            | •             |                  | •                    |                      |                     |  |  |  |

| bit 8         |                                                                                                    | er Duty Cycle Re                                                                                                                              |               |                  |                      |                      |                     |  |  |  |

|               |                                                                                                    | ister provides du<br>jister provides du                                                                                                       |               |                  |                      | r                    |                     |  |  |  |

| Note 1:       | Software must clea                                                                                 |                                                                                                                                               |               |                  | -                    |                      | t controller        |  |  |  |

| Note 1.<br>2: |                                                                                                    | -                                                                                                                                             |               | -                | -                    | the interrup         |                     |  |  |  |

| 3:            |                                                                                                    | These bits should not be changed after the PWMx is enabled (PTEN = 1).<br>DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored. |               |                  |                      |                      |                     |  |  |  |

| 4:            | The Independent T<br>CAM bit is ignored                                                            | Time Base (ITB =                                                                                                                              |               | •                |                      | igned mode. If       | TTB = 0, the        |  |  |  |

| 5:            | To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx |                                                                                                                                               |               |                  |                      |                      |                     |  |  |  |

### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|              | R/W-0                                               | U-0                 | U-0                         | U-0             | R/W-0                                | R/W-0                | R/W-0                |  |

|--------------|-----------------------------------------------------|---------------------|-----------------------------|-----------------|--------------------------------------|----------------------|----------------------|--|

| CSS31        | CSS30                                               | —                   | —                           | _               | CSS26 <sup>(2)</sup>                 | CSS25 <sup>(2)</sup> | CSS24 <sup>(2)</sup> |  |

| bit 15       | - 1                                                 |                     |                             |                 |                                      |                      | bit 8                |  |

|              |                                                     |                     |                             |                 |                                      |                      |                      |  |

| U-0          | U-0                                                 | U-0                 | U-0                         | U-0             | U-0                                  | U-0                  | U-0                  |  |

| _            |                                                     | _                   | _                           | —               |                                      | _                    |                      |  |

| bit 7        |                                                     |                     |                             |                 |                                      |                      | bit (                |  |

|              |                                                     |                     |                             |                 |                                      |                      |                      |  |

| Legend:      |                                                     |                     |                             |                 |                                      |                      |                      |  |

| R = Readab   | le bit                                              | W = Writable        | bit                         | U = Unimple     | emented bit, read                    | d as '0'             |                      |  |

| -n = Value a | t POR                                               | '1' = Bit is set    |                             | '0' = Bit is cl | eared                                | x = Bit is unk       | nown                 |  |

|              |                                                     |                     |                             |                 |                                      |                      |                      |  |

| bit 15       |                                                     | 1 Input Scan S      |                             |                 |                                      |                      |                      |  |

|              |                                                     |                     |                             |                 | input scan (Ope                      |                      |                      |  |

|              | •                                                   | •                   |                             | surement for ir | nput scan (Open                      | )                    |                      |  |

| bit 14       |                                                     | 1 Input Scan S      |                             |                 |                                      |                      |                      |  |

|              |                                                     |                     |                             |                 | or input scan (CT<br>input scan (CTN |                      |                      |  |

| bit 13-11    | Unimplemen                                          | ted: Read as '      | 0'                          |                 |                                      |                      |                      |  |

| bit 10       | CSS26: ADC                                          | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |  |

|              | 1 = Selects C                                       | )<br>A3/AN6 for inp | ut scan                     |                 |                                      |                      |                      |  |

|              | 0 = Skips OA                                        | 3/AN6 for input     | scan                        |                 |                                      |                      |                      |  |

| bit 9        | CSS25: ADC                                          | 1 Input Scan S      | election bit <sup>(2)</sup> |                 |                                      |                      |                      |  |

|              | 1 = Selects C                                       | 0A2/AN0 for inp     | ut scan                     |                 |                                      |                      |                      |  |

|              | 0 = Skips OA                                        | 2/AN0 for input     | scan                        |                 |                                      |                      |                      |  |

| bit 8        | CSS24: ADC1 Input Scan Selection bit <sup>(2)</sup> |                     |                             |                 |                                      |                      |                      |  |

|              |                                                     | 0A1/AN3 for inp     |                             |                 |                                      |                      |                      |  |

|              | 0 = Skips OA                                        | 1/AN3 for input     | scan                        |                 |                                      |                      |                      |  |

|              |                                                     |                     |                             |                 |                                      |                      |                      |  |

## REGISTER 23-7: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1)</sup>

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| U-0          | U-0                        | U-0              | U-0              | U-0              | U-0              | U-0            | U-0    |

|--------------|----------------------------|------------------|------------------|------------------|------------------|----------------|--------|

|              | —                          | —                | _                |                  | —                |                | _      |

| bit 15       |                            |                  |                  |                  |                  |                | bit    |

| U-0          | R/W-0                      | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0  |

|              | CFSEL2                     | CFSEL1           | CFSEL0           | CFLTREN          | CFDIV2           | CFDIV1         | CFDIV0 |

| bit 7        | OFOLLZ                     | OFOLLT           | OFOLLO           | OFERNEN          | 010172           | OIDIVI         | bit    |

|              |                            |                  |                  |                  |                  |                |        |

| Legend:      |                            |                  |                  |                  |                  |                |        |

| R = Readab   |                            | W = Writable     |                  | -                | mented bit, read |                |        |

| -n = Value a | It POR                     | '1' = Bit is set |                  | '0' = Bit is cle | ared             | x = Bit is unk | nown   |

| bit 15-7     | Unimplomor                 | nted: Read as    | · ^ '            |                  |                  |                |        |

|              | -                          |                  |                  |                  |                  |                |        |

| bit 6-4      |                            | Comparator       | -liter input Cic | OCK Select Dits  |                  |                |        |

|              | 111 = T5CLK<br>110 = T4CLK |                  |                  |                  |                  |                |        |

|              | 110 = T4CLP<br>101 = T3CLP |                  |                  |                  |                  |                |        |

|              | 101 = T3CLr<br>100 = T2CLr |                  |                  |                  |                  |                |        |

|              | 011 = Reser                |                  |                  |                  |                  |                |        |

|              | 011 = Reserve              |                  |                  |                  |                  |                |        |

|              | 001 = Fosc <sup>(4</sup>   |                  |                  |                  |                  |                |        |

|              | $000 = Fe^{(4)}$           |                  |                  |                  |                  |                |        |

| bit 3        |                            | Comparator Filt  | er Enable bit    |                  |                  |                |        |

|              | 1 = Digital filt           | er is enabled    |                  |                  |                  |                |        |

|              | 0 = Digital filt           | er is disabled   |                  |                  |                  |                |        |

| bit 2-0      | CFDIV<2:0>                 | : Comparator F   | ilter Clock Div  | vide Select bits |                  |                |        |

|              | 111 = Clock                | Divide 1:128     |                  |                  |                  |                |        |

|              | 110 = Clock                | Divide 1:64      |                  |                  |                  |                |        |

|              | 101 = Clock                | Divide 1:32      |                  |                  |                  |                |        |

|              | 100 = Clock                | Divide 1:16      |                  |                  |                  |                |        |

|              | 011 = Clock                | Divide 1:8       |                  |                  |                  |                |        |

|              | 010 = Clock                | Divide 1:4       |                  |                  |                  |                |        |

|              | 001 = Clock                |                  |                  |                  |                  |                |        |

|              | 000 = Clock                | Divide 1:1       |                  |                  |                  |                |        |

| Note 1: S    | See the Type C Ti          | mer Block Diag   | gram (Figure 1   | 3-2).            |                  |                |        |

|              | See the Type B Ti          |                  |                  |                  |                  |                |        |

| • •          |                            |                  |                  |                  | D. (E.           |                |        |

## REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 16-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

## 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F. The PIC24EP instruction set is almost identical to that of the PIC24F and PIC24H.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

| DC CHARACTER  | ISTICS | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industi- $-40^{\circ}C \le TA \le +125^{\circ}C$ for Externational Conditions: 3.0V to 3.6V |       |            |       |  |  |  |  |

|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------|--|--|--|--|

| Parameter No. | Тур.   | Max.                                                                                                                                                                                                                                     | Units | Conditions |       |  |  |  |  |

| DC61d         | 8      |                                                                                                                                                                                                                                          | μΑ    | -40°C      |       |  |  |  |  |

| DC61a         | 10     | —                                                                                                                                                                                                                                        | μA    | +25°C      | 2.21/ |  |  |  |  |

| DC61b         | 12     | —                                                                                                                                                                                                                                        | μA    | +85°C      | 3.3V  |  |  |  |  |

| DC61c         | 13     | —                                                                                                                                                                                                                                        | μA    | +125°C     |       |  |  |  |  |

#### TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT $(\triangle Iwdt)^{(1)}$

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |       |       |            |        |       |                 |  |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------------|--------|-------|-----------------|--|--|--|

| Parameter No.                       | Doze<br>Ratio                                                                                                                                                                                                                                                                         | Units |       | Conditions |        |       |                 |  |  |  |

| Doze Current (IDOZE) <sup>(1)</sup> |                                                                                                                                                                                                                                                                                       |       |       |            |        |       |                 |  |  |  |

| DC73a <sup>(2)</sup>                | 35                                                                                                                                                                                                                                                                                    |       | 1:2   | mA         | -40°C  | 3.3V  | Fosc = 140 MHz  |  |  |  |

| DC73g                               | 20                                                                                                                                                                                                                                                                                    | 30    | 1:128 | mA         | -40 C  |       | FUSC - 140 MINZ |  |  |  |

| DC70a <sup>(2)</sup>                | 35                                                                                                                                                                                                                                                                                    | _     | 1:2   | mA         | +25°C  | 3.3V  | Fosc = 140 MHz  |  |  |  |

| DC70g                               | 20                                                                                                                                                                                                                                                                                    | 30    | 1:128 | mA         | +25 C  | 3.3V  | FUSC = 140 MITZ |  |  |  |

| DC71a <sup>(2)</sup>                | 35                                                                                                                                                                                                                                                                                    | _     | 1:2   | mA         | 105%0  | 2.21/ |                 |  |  |  |

| DC71g                               | 20                                                                                                                                                                                                                                                                                    | 30    | 1:128 | mA         | +85°C  | 3.3V  | Fosc = 140 MHz  |  |  |  |

| DC72a <sup>(2)</sup>                | 28                                                                                                                                                                                                                                                                                    | —     | 1:2   | mA         | +125°C | 3.3V  | Fosc = 120 MHz  |  |  |  |

| DC72g                               | 15                                                                                                                                                                                                                                                                                    | 30    | 1:128 | mA         | +125 C | 3.3V  | FUSC - 120 MIHZ |  |  |  |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

| DC CH        | ARACTE | RISTICS                                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |         |    |                        |  |  |

|--------------|--------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|----|------------------------|--|--|

| Param<br>No. | Symbol | Characteristic                                          | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                         |     |         |    |                        |  |  |

|              | VIL    | Input Low Voltage                                       |                                                                                                                                                                                                                                                                                         |     |         |    |                        |  |  |

| DI10         |        | Any I/O Pin and MCLR                                    | Vss                                                                                                                                                                                                                                                                                     | —   | 0.2 VDD | V  |                        |  |  |

| DI18         |        | I/O Pins with SDAx, SCLx                                | Vss                                                                                                                                                                                                                                                                                     | —   | 0.3 VDD | V  | SMBus disabled         |  |  |

| DI19         |        | I/O Pins with SDAx, SCLx                                | Vss                                                                                                                                                                                                                                                                                     | —   | 0.8     | V  | SMBus enabled          |  |  |

|              | Vih    | Input High Voltage                                      |                                                                                                                                                                                                                                                                                         |     |         |    |                        |  |  |

| DI20         |        | I/O Pins Not 5V Tolerant                                | 0.8 VDD                                                                                                                                                                                                                                                                                 | —   | Vdd     | V  | (Note 3)               |  |  |

|              |        | I/O Pins 5V Tolerant and MCLR                           | 0.8 VDD                                                                                                                                                                                                                                                                                 | —   | 5.5     | V  | (Note 3)               |  |  |

|              |        | I/O Pins with SDAx, SCLx                                | 0.8 VDD                                                                                                                                                                                                                                                                                 | —   | 5.5     | V  | SMBus disabled         |  |  |

|              |        | I/O Pins with SDAx, SCLx                                | 2.1                                                                                                                                                                                                                                                                                     | _   | 5.5     | V  | SMBus enabled          |  |  |

|              | ICNPU  | Change Notification Pull-up Current                     |                                                                                                                                                                                                                                                                                         |     |         |    |                        |  |  |

| DI30         |        |                                                         | 150                                                                                                                                                                                                                                                                                     | 250 | 550     | μA | VDD = 3.3V, VPIN = VSS |  |  |

|              | ICNPD  | Change Notification<br>Pull-Down Current <sup>(4)</sup> |                                                                                                                                                                                                                                                                                         |     |         |    |                        |  |  |

| DI31         |        |                                                         | 20                                                                                                                                                                                                                                                                                      | 50  | 100     | μA | Vdd = 3.3V, Vpin = Vdd |  |  |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (VSS 0.3). Characterized but not tested.

**5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- 8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| DC CH        | ARACTE | RISTICS                                 | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                                                                                                                                                   |  |  |

|--------------|--------|-----------------------------------------|-------------------------------------------------------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol | Characteristic                          | Min.                                                  | Тур. | Max. | Units | Conditions                                                                                                                                        |  |  |

|              | liL    | Input Leakage Current <sup>(1,2)</sup>  |                                                       |      |      |       |                                                                                                                                                   |  |  |

| DI50         |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                    | —    | +1   | μA    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in \ at \ high-impedance} \end{split}$                         |  |  |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _    | +1   | μA    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \mbox{ at high-impedance}, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \end{array}$ |  |  |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _    | +1   | μA    | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +85^{\circ}C$                                                           |  |  |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _    | +1   | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                          |  |  |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                    | _    | +1   | μA    | Analog pins shared with external reference pins, $-40^{\circ}C \le TA \le +125^{\circ}C$                                                          |  |  |

| DI55         |        | MCLR                                    | -5                                                    | —    | +5   | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                          |  |  |

| DI56         |        | OSC1                                    | -5                                                    | —    | +5   | μΑ    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &X{\sf T} \text{ and }H{\sf S} \text{ modes} \end{split}$             |  |  |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| AC CHA       | AC CHARACTERISTICS |                                               |           | $ \begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)}^{(1)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq T_A \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq T_A \leq +125^{\circ}C \mbox{ for Extended} \\ \end{array} $ |           |       |                                                         |  |  |  |

|--------------|--------------------|-----------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|---------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol             | Characteristic                                | Min.      | Тур.                                                                                                                                                                                                                                                                                                 | Max.      | Units | Conditions                                              |  |  |  |

|              |                    | ADC A                                         | ccuracy ( | 10-Bit N                                                                                                                                                                                                                                                                                             | lode)     |       |                                                         |  |  |  |

| AD20b        | Nr                 | Resolution                                    | 10        | ) Data B                                                                                                                                                                                                                                                                                             | its       | bits  |                                                         |  |  |  |

| AD21b        | INL                | Integral Nonlinearity                         | -0.625    |                                                                                                                                                                                                                                                                                                      | 0.625     | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                             |  |  |  |

|              |                    |                                               | -1.5      |                                                                                                                                                                                                                                                                                                      | 1.5       | LSb   | +85°C < TA ≤ +125°C (Note 2)                            |  |  |  |

| AD22b        | DNL                | Differential Nonlinearity                     | -0.25     | —                                                                                                                                                                                                                                                                                                    | 0.25      | LSb   | -40°C ≤ TA ≤ +85°C (Note 2)                             |  |  |  |

|              |                    |                                               | -0.25     | —                                                                                                                                                                                                                                                                                                    | 0.25      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |  |  |  |

| AD23b        | Gerr               | Gain Error                                    | -2.5      | —                                                                                                                                                                                                                                                                                                    | 2.5       | LSb   | -40°C $\leq$ TA $\leq$ +85°C (Note 2)                   |  |  |  |

|              |                    |                                               | -2.5      |                                                                                                                                                                                                                                                                                                      | 2.5       | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |  |  |  |

| AD24b        | EOFF               | Offset Error                                  | -1.25     | —                                                                                                                                                                                                                                                                                                    | 1.25      | LSb   | $-40^{\circ}C \le TA \le +85^{\circ}C \text{ (Note 2)}$ |  |  |  |

|              |                    |                                               | -1.25     | —                                                                                                                                                                                                                                                                                                    | 1.25      | LSb   | +85°C < TA $\leq$ +125°C (Note 2)                       |  |  |  |

| AD25b        | —                  | Monotonicity                                  | _         |                                                                                                                                                                                                                                                                                                      | _         | —     | Guaranteed                                              |  |  |  |

|              |                    | Dynamic P                                     | erforman  | ce (10-E                                                                                                                                                                                                                                                                                             | Bit Mode) |       |                                                         |  |  |  |

| AD30b        | THD                | Total Harmonic Distortion <sup>(3)</sup>      | _         | 64                                                                                                                                                                                                                                                                                                   |           | dB    |                                                         |  |  |  |

| AD31b        | SINAD              | Signal to Noise and Distortion <sup>(3)</sup> |           | 57                                                                                                                                                                                                                                                                                                   |           | dB    |                                                         |  |  |  |

| AD32b        | SFDR               | Spurious Free Dynamic<br>Range <sup>(3)</sup> | —         | 72                                                                                                                                                                                                                                                                                                   | —         | dB    |                                                         |  |  |  |

| AD33b        | Fnyq               | Input Signal Bandwidth <sup>(3)</sup>         | —         | 550                                                                                                                                                                                                                                                                                                  | —         | kHz   |                                                         |  |  |  |