Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\times$  FI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502t-e-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0               | U-0                          | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |

|---------------------|------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|

| VAR                 | —                            | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15              |                              |                                                          |                         |                             |                           |                    | bit                |

| R/W-0               | R/W-0                        | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |

| bit 7               | I                            |                                                          |                         |                             | I                         | 1                  | bit                |

| Legend:             |                              | C = Clearable                                            | e bit                   |                             |                           |                    |                    |

| R = Readabl         | e bit                        | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |

| -n = Value at       | POR                          | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |

| bit 14              |                              | nted: Read as '                                          |                         |                             |                           |                    |                    |

| bit 13-12           | -                            | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |

| bit 10-8            |                              | Loop Nesting<br>oops are active                          |                         | (1)                         |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |

| bit 7               | SATA: ACCA                   | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |

| bit 6               | SATB: ACCE                   | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |

| bit 5               | SATDW: Dat                   | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |

|                     |                              | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |

| bit 4               |                              | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |

|                     |                              | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |

| bit 3               |                              | nterrupt Priority                                        |                         |                             |                           |                    |                    |

|                     |                              | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |

|                     | nis bit is availabl          |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |

| 2: Th               | nis bit is always            | reau as 0.                                               |                         |                             |                           |                    |                    |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            | VELEN  |        |        |            |        |       |         | DEVICE      |         |         |          |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|---------|-------------|---------|---------|----------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF   | IC2IF       | DMA0IF  | T1IF    | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _       | —           | INT1IF  | CNIF    | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —          | _      | _     | IC4IF   | IC3IF       | DMA3IF  | _       | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIF   | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      | _      | —          | —      | _     | _       | _           | _       | _       | —        | —            | —       | 0000          |

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IF  | PTG2IF      | PTG1IF  | PTG0IF  | PTGWDTIF | PTGSTEPIF    | _       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE   | IC2IE       | DMA0IE  | T1IE    | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _       | _           | INT1IE  | CNIE    | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _          | _      | _     | IC4IE   | IC3IE       | DMA3IE  | _       | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | —          | —      | _     | _       | _           | _       | _       | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIE   | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | _        | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IE  | PTG2IE      | PTG1IE  | PTG0IE  | PTGWDTIE | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     |         | IC1IP<2:0>  |         | —       |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |         | IC2IP<2:0>  |         | _       | C        | 0MA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |         | SPI1EIP<2:0 | >       | _       |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _     |         | AD1IP<2:0>  |         | _       | ι        | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _     |         | MI2C1IP<2:0 | >       | _       | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | —           | _       | _       | I        | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |         | OC3IP<2:0>  |         | _       | C        | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |        | I      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _     |         | INT2IP<2:0> |         | _       |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —          | —      | _     |         | SPI2IP<2:0> |         | _       | S        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          |        |        |        | IC4IP<2:0  | >      | _     |         | IC3IP<2:0>  |         | _       | C        | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          |        |        | N      | 112C2IP<2: | 0>     | _     |         | SI2C2IP<2:0 | >       | _       | _        | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _     |         | U1EIP<2:0>  |         | _       | _        | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _          | _      | _     |         | CTMUIP<2:0  | >       | _       | _        | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _     | _       | _           | _       | _       | _        | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P       | TGSTEPIP<2  | :0>     | _       | _        | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _     |         | PTG2IP<2:0  | >       | _       | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            | —      | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR   | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |            | _      | _     |         | —           | —       | _       | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      | _          | _      |        |        | _          | _      | _     | _       | DAE         | DOOVR   | _       | _        | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —          | _      | _     | _       | _           | _       | _       | _        |              | SGHT    | 0000          |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>       |        |       |         |             | VECN    | UM<7:0> |          |              |         | 0000          |

|              |       |        |        |            |        |        |        |            |        |       |         |             |         |         |          |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

## TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | —      | _      | _      | _      | —     | —      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | —      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | —      | _      | _      | —      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | —      | _      | _      |        | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _      | —      | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

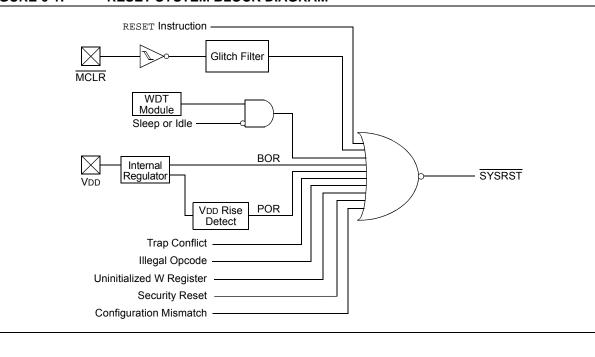

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

| R/W-0                 | R/W-0                                         | R/W-0                                                | R/W-0                                         | R/W-0                              | U-0              | U-0             | U-0     |

|-----------------------|-----------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------|------------------|-----------------|---------|

| CHEN                  | SIZE                                          | DIR                                                  | HALF                                          | NULLW                              |                  |                 |         |

| bit 15                |                                               |                                                      |                                               |                                    |                  |                 | bit     |

| U-0                   | U-0                                           | R/W-0                                                | R/W-0                                         | U-0                                | U-0              | R/W-0           | R/W-0   |

|                       | 0-0                                           | AMODE1                                               | AMODE0                                        | 0-0                                | 0-0              | MODE1           | MODE0   |

| bit 7                 |                                               | AWODET                                               | 7 WIODE0                                      |                                    |                  | MODET           | bit     |

| Lovende               |                                               |                                                      |                                               |                                    |                  |                 |         |

| Legend:<br>R = Readab | lo hit                                        | M - Mritabla                                         | hit.                                          |                                    | monted bit rec   | ud aa '0'       |         |

|                       |                                               | W = Writable                                         |                                               | -                                  | mented bit, rea  |                 |         |

| -n = Value a          | IT POR                                        | '1' = Bit is set                                     |                                               | '0' = Bit is cle                   | ared             | x = Bit is unkr | nown    |

| bit 15                | CHEN: DMA                                     | Channel Enabl                                        | e bit                                         |                                    |                  |                 |         |

|                       | 1 = Channel<br>0 = Channel                    |                                                      |                                               |                                    |                  |                 |         |

| bit 14                |                                               | ata Transfer S                                       | ze hit                                        |                                    |                  |                 |         |

|                       | 1 = Byte                                      |                                                      |                                               |                                    |                  |                 |         |

|                       | 0 = Word                                      |                                                      |                                               |                                    |                  |                 |         |

| bit 13                | DIR: DMA Tra                                  | ansfer Directior                                     | n bit (source/d                               | estination bus                     | select)          |                 |         |

|                       |                                               | om RAM addre<br>om peripheral a                      |                                               | •                                  |                  |                 |         |

| bit 12                |                                               | Block Transfer                                       |                                               |                                    |                  |                 |         |

|                       | 1 = Initiates i                               | nterrupt when                                        | half of the data                              | a has been mo                      |                  |                 |         |

| bit 11                |                                               | Data Periphera                                       |                                               |                                    |                  |                 |         |

|                       |                                               | write to periph                                      |                                               |                                    | e (DIR bit must  | also be clear)  |         |

| bit 10-6              | Unimplemen                                    | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |

| bit 5-4               | AMODE<1:0                                     | -: DMA Chann                                         | el Addressing                                 | Mode Select b                      | oits             |                 |         |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register |                                                      | ressing mode<br>ut Post-Increm                | nent mode                          |                  |                 |         |

| bit 3-2               | Unimplemen                                    | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |

| bit 1-0               | -                                             | DMA Channel                                          |                                               | de Select bits                     |                  |                 |         |

|                       | 11 = One-Sho<br>10 = Continue                 | ot, Ping-Pong r<br>ous, Ping-Pong<br>ot, Ping-Pong r | nodes are ena<br>modes are e<br>nodes are dis | abled (one bloc<br>nabled<br>abled | ck transfer fror | n/to each DMA t | ouffer) |

## REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

## 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

## REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                              | R/W-0         | R/W-0           | R/W-0 |  |  |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------|---------------|-----------------|-------|--|--|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                       | >             |                 |       |  |  |  |

| bit 15             |                                            |                                                 |                                            |                                    |               |                 | bit 8 |  |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                 |       |  |  |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                                | U-0           | U-0             | U-0   |  |  |  |

| _                  |                                            |                                                 | —                                          |                                    |               | <u> </u>        | _     |  |  |  |

| bit 7              |                                            |                                                 |                                            |                                    |               |                 | bit 0 |  |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                 |       |  |  |  |

| Legend:            |                                            |                                                 |                                            |                                    |               |                 |       |  |  |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplemented bit, read as '0' |               |                 |       |  |  |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea                  | ared          | x = Bit is unkn | iown  |  |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                 |       |  |  |  |

|                    |                                            |                                                 |                                            |                                    |               |                 |       |  |  |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                                    |               |                 |       |  |  |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers)        | the Correspon | ding RPn Pin b  | its   |  |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b  | its   |  |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b  | its   |  |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                                    | the Correspon | ding RPn Pin b  | its   |  |  |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                                    | the Correspon | ding RPn Pin b  | its   |  |  |  |

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0                                | U-0        | U-0            | U-0 | U-0              | U-0                     | U-0                     | U-0         |

|------------------------------------|------------|----------------|-----|------------------|-------------------------|-------------------------|-------------|

| —                                  | —          | —              | _   | —                | —                       | —                       | _           |

| bit 15                             |            |                |     |                  |                         |                         | bit 8       |

|                                    |            |                |     |                  |                         |                         |             |

| U-0                                | U-0        | U-0            | U-0 | U-0              | R/W-0                   | R/W-0                   | R/W-0       |

| —                                  | —          | —              | _   | —                | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |

| bit 7                              |            |                |     |                  |                         |                         | bit 0       |

|                                    |            |                |     |                  |                         |                         |             |

| Legend:                            |            |                |     |                  |                         |                         |             |

| R = Readable                       | bit        | W = Writable   | bit | U = Unimpler     | mented bit, read        | as '0'                  |             |

| -n = Value at POR '1' = Bit is set |            |                |     | '0' = Bit is cle | ared                    | x = Bit is unkn         | own         |

|                                    |            |                |     |                  |                         |                         |             |

| bit 15-3                           | Unimplemen | ted: Read as ' | י'  |                  |                         |                         |             |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

## 23.1 Key Features

## 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

## 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

## REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

# REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGHOL | _D<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------|-------|-------|-------|

|       |       |       | PTGHO | LD<7:0> |       |       |       |

| bit 7 |       |       |       |         |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                 |  |  |  |  |  |

|---------|------------------------|-------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 0001        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                  |  |  |  |  |  |

|         |                        | 0011        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 0100        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 0101        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                   |  |  |  |  |  |

|         |                        | 0111        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                              |  |  |  |  |  |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                              |  |  |  |  |  |

|         |                        | 1010        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = 0 to 1). |  |  |  |  |  |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                   |  |  |  |  |  |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                   |  |  |  |  |  |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                   |  |  |  |  |  |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                     |  |  |  |  |  |

|         | PTGADD <sup>(1)</sup>  | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                    |  |  |  |  |  |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                    |  |  |  |  |  |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                       |  |  |  |  |  |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                       |  |  |  |  |  |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                    |  |  |  |  |  |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                             |  |  |  |  |  |

|         |                        | 0110        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 0111        | Reserved.                                                                                          |  |  |  |  |  |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                  |  |  |  |  |  |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                  |  |  |  |  |  |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                     |  |  |  |  |  |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                     |  |  |  |  |  |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                 |  |  |  |  |  |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                           |  |  |  |  |  |

|         |                        | 1110        | Reserved.                                                                                          |  |  |  |  |  |

|         |                        | 1111        | Reserved.                                                                                          |  |  |  |  |  |

## TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| U-0                                                          | U-0                              | U-0              | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|--------------------------------------------------------------|----------------------------------|------------------|---------|------------------|------------------|-----------------|---------|

| _                                                            | —                                | —                | DWIDTH4 | DWIDTH3          | DWIDTH2          | DWIDTH1         | DWIDTH0 |

| bit 15                                                       |                                  |                  |         |                  |                  |                 | bit 8   |

|                                                              |                                  |                  |         |                  |                  |                 |         |

| U-0                                                          | U-0                              | U-0              | R/W-0   | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| —                                                            | —                                | —                | PLEN4   | PLEN3            | PLEN2            | PLEN1           | PLEN0   |

| bit 7                                                        |                                  |                  |         |                  |                  |                 | bit 0   |

|                                                              |                                  |                  |         |                  |                  |                 |         |

| Legend:                                                      |                                  |                  |         |                  |                  |                 |         |

| R = Readable                                                 | e bit                            | W = Writable     | bit     | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at                                                | POR                              | '1' = Bit is set |         | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                                                              |                                  |                  |         |                  |                  |                 |         |

| bit 15-13                                                    | Unimplemen                       | ted: Read as '   | 0'      |                  |                  |                 |         |

| bit 12-8 DWIDTH<4:0>: Data Width Select bits                 |                                  |                  |         |                  |                  |                 |         |

| These bits set the width of the data word (DWIDTH<4:0> + 1). |                                  |                  |         |                  |                  |                 |         |

| bit 7-5                                                      | t 7-5 Unimplemented: Read as '0' |                  |         |                  |                  |                 |         |

|                                                              |                                  |                  |         |                  |                  |                 |         |

## REGISTER 26-2: CRCCON2: CRC CONTROL REGISTER 2

bit 4-0 **PLEN<4:0>:** Polynomial Length Select bits

These bits set the length of the polynomial (Polynomial Length = PLEN<4:0> + 1).

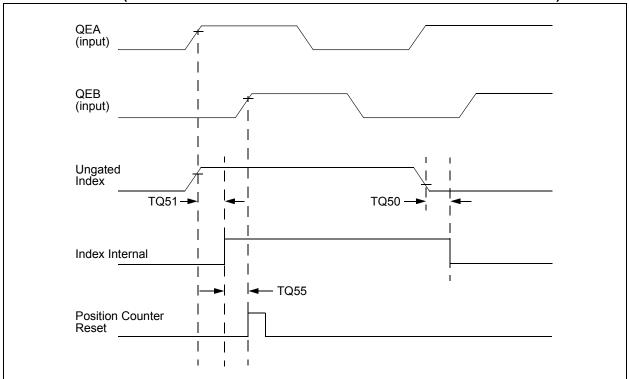

## FIGURE 30-13: QEI MODULE INDEX PULSE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

## TABLE 30-32: QEI INDEX PULSE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |   |    |                                                         |  |

|--------------------|--------|---------------------------------------------------------------------|-------------------------------------------------------|---|----|---------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                       | Min. Max. Units Conditions                            |   |    |                                                         |  |

| TQ50               | TqiL   | Filter Time to Recognize Low,<br>with Digital Filter                | 3 * N * Tcy                                           | _ | ns | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |  |

| TQ51               | TqiH   | Filter Time to Recognize High,<br>with Digital Filter               | 3 * N * Tcy                                           | — | ns | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |  |

| TQ55               | Tqidxr | Index Pulse Recognized to Position<br>Counter Reset (ungated index) | 3 TCY                                                 | — | ns |                                                         |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Alignment of index pulses to QEA and QEB is shown for position counter Reset timing only. Shown for forward direction only (QEA leads QEB). Same timing applies for reverse direction (QEA lags QEB) but index pulse recognition occurs on the falling edge.

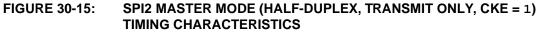

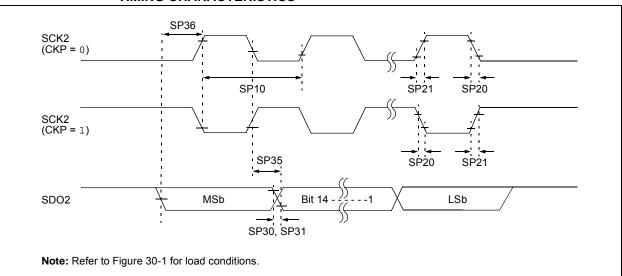

#### TABLE 30-34: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |                     |      |       |                                |

|--------------------|-----------------------|----------------------------------------------|----------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                     | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP10               | FscP                  | Maximum SCK2 Frequency                       | —                                                        | _                   | 15   | MHz   | (Note 3)                       |

| SP20               | TscF                  | SCK2 Output Fall Time                        | —                                                        | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP21               | TscR                  | SCK2 Output Rise Time                        | —                                                        | —                   | _    | ns    | See Parameter DO31<br>(Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                   | —                                                        | —                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                   | -                                                        | _                   |      | ns    | See Parameter DO31<br>(Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge    | —                                                        | 6                   | 20   | ns    |                                |

| SP36               | TdiV2scH,<br>TdiV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30                                                       | —                   | _    | ns    |                                |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

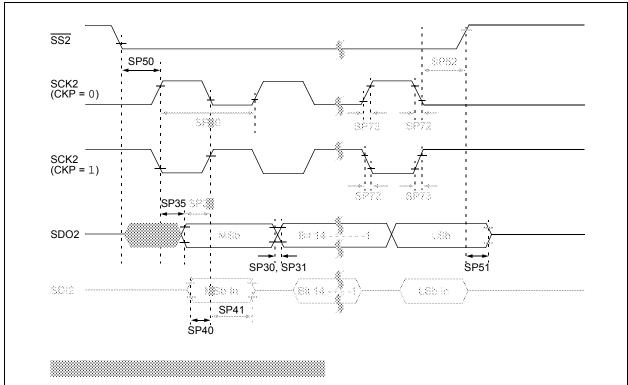

## FIGURE 30-21: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-47:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |                             |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP70               | FscP                  | Maximum SCK1 Input Frequency                 | —                                                                                                                                                                                                   | —                   | 15   | MHz   | (Note 3)                    |

| SP72               | TscF                  | SCK1 Input Fall Time                         | —                                                                                                                                                                                                   | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP73               | TscR                  | SCK1 Input Rise Time                         | —                                                                                                                                                                                                   | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | —                                                                                                                                                                                                   | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                   | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                   | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                  | —                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                                                                                                                                                                                  | —                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                                                                                                                                                                                  | —                   | _    | ns    |                             |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                                                                                                                                                                                 | —                   | _    | ns    |                             |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                                                                                                                                                                                  | —                   | 50   | ns    | (Note 4)                    |

| SP52               | TscH2ssH,<br>TscL2ssH | SS1                                          | 1.5 Tcy + 40                                                                                                                                                                                        | —                   |      | ns    | (Note 4)                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

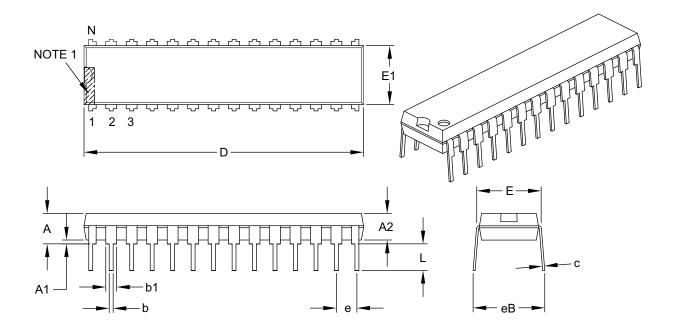

#### 33.2 Package Details

## 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |       |          | INCHES |  |  |  |

|----------------------------|----------|-------|----------|--------|--|--|--|

| Dimension                  | n Limits | MIN   | NOM      | MAX    |  |  |  |

| Number of Pins             | Ν        |       | 28       |        |  |  |  |

| Pitch                      | е        |       | .100 BSC |        |  |  |  |

| Top to Seating Plane       | Α        | -     | -        | .200   |  |  |  |

| Molded Package Thickness   | A2       | .120  | .135     | .150   |  |  |  |

| Base to Seating Plane      | A1       | .015  | -        | -      |  |  |  |

| Shoulder to Shoulder Width | E        | .290  | .310     | .335   |  |  |  |

| Molded Package Width       | E1       | .240  | .285     | .295   |  |  |  |

| Overall Length             | D        | 1.345 | 1.365    | 1.400  |  |  |  |

| Tip to Seating Plane       | L        | .110  | .130     | .150   |  |  |  |

| Lead Thickness             | С        | .008  | .010     | .015   |  |  |  |

| Upper Lead Width           | b1       | .040  | .050     | .070   |  |  |  |

| Lower Lead Width           | b        | .014  | .018     | .022   |  |  |  |

| Overall Row Spacing §      | eB       | _     | -        | .430   |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A