Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502t-e-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

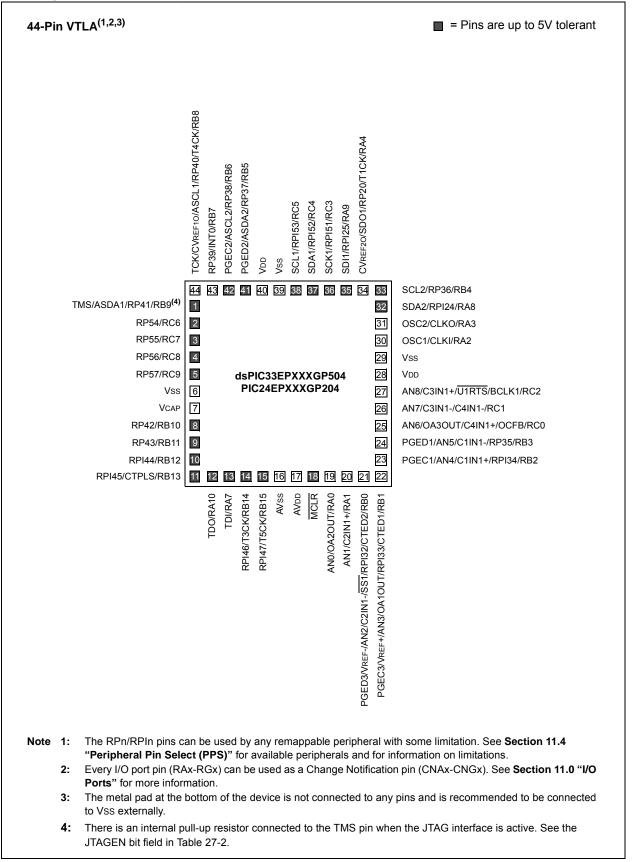

## **Pin Diagrams (Continued)**

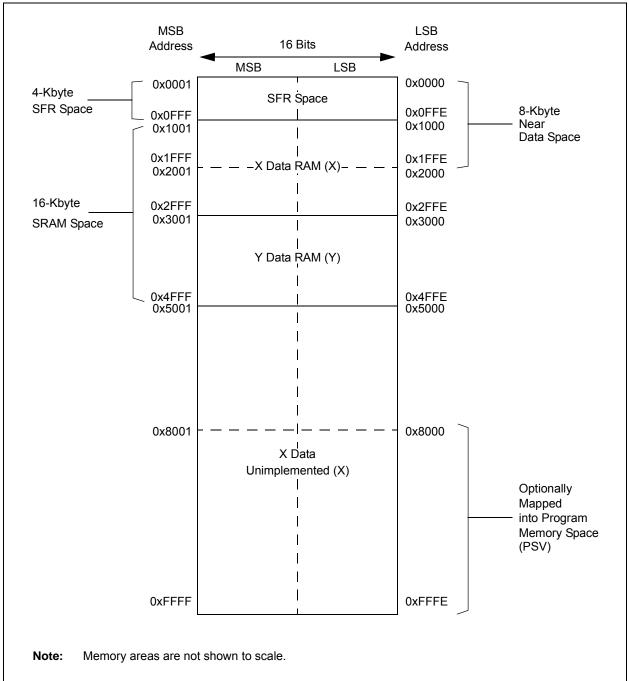

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

## TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC23        | 086E  |        | F      | PWM2IP<2:0 | )>      |         | Р      | WM1IP<2:   | 0>    |          |         | _           |         | —       | _      | -           |        | 4400          |

| IPC24        | 0870  |        | _      | _          | _       | -       | _      | _          | _     | _        | _       | _           | _       | _       | F      | WM3IP<2:0>  |        | 0004          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >       | -       |        | ICDIP<2:0  | >     | _        | _       | _           | _       | _       | _      | _           | _      | 4400          |

| IPC36        | 0888  |        | I      | PTG0IP<2:0 | )>      | -       | PT     | GWDTIP<    | 2:0>  | _        | P       | GSTEPIP<2:  | :0>     | _       | _      | _           | _      | 4440          |

| IPC37        | 088A  | _      | _      |            | —       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | •       | —       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | _          |       |          |         | _           |         | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      |            | —       | _       | _      | _          |       |          |         | DAE         | DOOVR   | _       | —      | _           |        | 0000          |

| INTCON4      | 08C6  | _      | _      |            | —       | _       | _      | _          | _     | _        |         | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      |            | —       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | JM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-49: PORTD REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 0E30  | _      | _      | _      |        | _      | _      | _     | TRISD8 |       | TRISD6 | TRISD5 |       |       |       |       | _     | 0160          |

| PORTD        | 0E32  | _      | _      |        | _      | _      | _      |       | RD8    | —     | RD6    | RD5    | —     | _     | _     | _     |       | xxxx          |

| LATD         | 0E34  | _      | _      |        | _      | _      | _      |       | LATD8  | —     | LATD6  | LATD5  | —     | _     | _     | _     |       | xxxx          |

| ODCD         | 0E36  | _      |        |        | -      |        |        |       | ODCD8  | —     | ODCD6  | ODCD5  | —     | _     | _     | _     |       | 0000          |

| CNEND        | 0E38  | _      |        |        | -      |        |        |       | CNIED8 | —     | CNIED6 | CNIED5 | —     | _     | _     | _     |       | 0000          |

| CNPUD        | 0E3A  | _      | _      |        | _      | _      | _      |       | CNPUD8 | —     | CNPUD6 | CNPUD5 | —     | _     | _     | _     |       | 0000          |

| CNPDD        | 0E3C  | _      | _      |        | _      | _      | _      |       | CNPDD8 | —     | CNPDD6 | CNPDD5 | —     | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PORTE REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE        | 0E40  | TRISE15 | TRISE14 | TRISE13 | TRISE12 | —      | _      | _     | —     | _     |       | -     | —     | —     | _     | —     |       | F000          |

| PORTE        | 0E42  | RE15    | RE14    | RE13    | RE12    | _      | —      | —     | —     |       | —     | —     | _     | —     | —     | —     | —     | xxxx          |

| LATE         | 0E44  | LATE15  | LATE14  | LATE13  | LATE12  | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | xxxx          |

| ODCE         | 0E46  | ODCE15  | ODCE14  | ODCE13  | ODCE12  | —      | -      | -     | -     |       |       | -     | —     | —     | _     | _     |       | 0000          |

| CNENE        | 0E48  | CNIEE15 | CNIEE14 | CNIEE13 | CNIEE12 | _      | —      | —     | —     |       | —     | —     | _     | —     | —     | —     | —     | 0000          |

| CNPUE        | 0E4A  | CNPUE15 | CNPUE14 | CNPUE13 | CNPUE12 | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | 0000          |

| CNPDE        | 0E4C  | CNPDE15 | CNPDE14 | CNPDE13 | CNPDE12 | _      | _      | _     | _     | -     | _     | —     | _     | —     | _     | _     | _     | 0000          |

| ANSELE       | 0E4E  | ANSE15  | ANSE14  | ANSE13  | ANSE12  |        | —      | _     | —     | _     | _     | _     |       |       | _     |       | _     | F000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-51: PORTF REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISF        | 0E50  | —      | -      | —      |        | —      |        | —     | -     | -     | —     | -     | -     | —     | -     | TRISF1 | TRISF0 | 0003          |

| PORTF        | 0E52  | —      | —      | _      | —      | —      | —      | —     | _     | —     | —     | —     | —     | —     | —     | RF1    | RF0    | xxxx          |

| LATF         | 0E54  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | LATF1  | LATF0  | xxxx          |

| ODCF         | 0E56  | _      | -      | _      | -      | —      | -      | —     |       |       | —     |       |       | _     | -     | ODCF1  | ODCF0  | 0000          |

| CNENF        | 0E58  |        | —      | -      |        | —      | -      | _     | -     | -     | —     | -     | -     | —     | -     | CNIEF1 | CNIEF0 | 0000          |

| CNPUF        | 0E5A  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | CNPUF1 | CNPUF0 | 0000          |

| CNPDF        | 0E5C  | _      | _      | _      | _      | -      |        | _     | _     | _     | _     | _     | _     | _     | -     | CNPDF1 | CNPDF0 | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | -      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

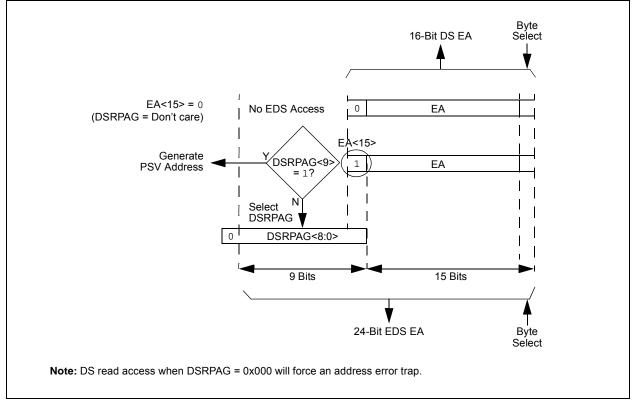

### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/11        |                     |                | Before       |                        |                | After        |                        |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

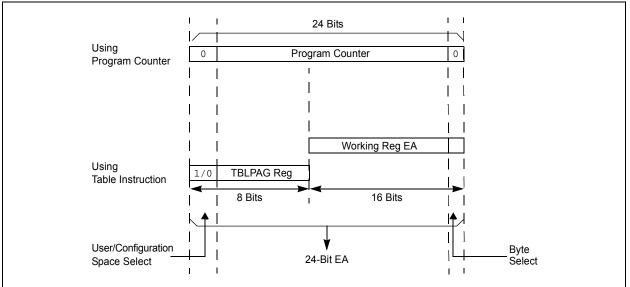

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

## REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|-----------------|-----------------|

| _                 |                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                 |                 |

| bit 15            |                                            |                                                                            |                                              |                            |                 |                 | bit 8           |

|                   | <b>D</b> AALO                              | <b>D</b> 444 0                                                             | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | D M M A         | <b>D</b> # 44 0 |

| U-0               | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|                   |                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                 |                 |

| bit 7             |                                            |                                                                            |                                              |                            |                 |                 | bit C           |

| Legend:           |                                            |                                                                            |                                              |                            |                 |                 |                 |

| R = Readabl       | le bit                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'       |                 |

| -n = Value at     | t POR                                      | '1' = Bit is set                                                           |                                              | '0' = Bit is clea          | ared            | x = Bit is unkr | nown            |

| bit 14-8          | <b>FLT2R&lt;6:0&gt;</b><br>(see Table 11   | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI                    | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8<br>bit 7 | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits        |                 |

| R/W-1           | R/W-1              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |

|-----------------|--------------------|----------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|

| PENH            | PENL               | POLH                                   | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |

| bit 15          |                    | •                                      |                            |                      |                           |                 | bit    |

| R/W-0           | R/W-0              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |

| -               | -                  | -                                      |                            | -                    | -                         | -               | R/W-0  |

| OVRDAT1         | OVRDAT0            | FLTDAT1                                | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |

| bit 7           |                    |                                        |                            |                      |                           |                 | bit    |

| Legend:         |                    |                                        |                            |                      |                           |                 |        |

| R = Readable    | bit                | W = Writable                           | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |

| -n = Value at F | POR                | '1' = Bit is set                       |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |

| bit 15          |                    | xH Output Pin                          | Ownorshin hit              |                      |                           |                 |        |

| bit 15          |                    | odule controls                         | •                          |                      |                           |                 |        |

|                 |                    | dule controls F                        |                            |                      |                           |                 |        |

| bit 14          |                    | L Output Pin                           | •                          |                      |                           |                 |        |

|                 | 1 = PWMx mo        | odule controls                         | PWMxL pin                  |                      |                           |                 |        |

|                 | 0 = GPIO mo        | dule controls F                        | WMxL pin                   |                      |                           |                 |        |

| bit 13          | POLH: PWM          | xH Output Pin                          | Polarity bit               |                      |                           |                 |        |

|                 |                    | oin is active-low                      |                            |                      |                           |                 |        |

|                 |                    | oin is active-hig                      | •                          |                      |                           |                 |        |

| bit 12          |                    | L Output Pin F                         | •                          |                      |                           |                 |        |

|                 |                    | in is active-low<br>in is active-hig   |                            |                      |                           |                 |        |

| bit 11-10       | PMOD<1:0>:         | PWMx # I/O F                           | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |

|                 | 11 = Reserve       | ,                                      |                            |                      |                           |                 |        |

|                 |                    | /O pin pair is ir<br>/O pin pair is ir |                            |                      |                           |                 |        |

|                 |                    | O pin pair is in<br>O pin pair is ir   |                            |                      |                           |                 |        |

| bit 9           |                    | verride Enable                         | •                          |                      |                           |                 |        |

|                 |                    | <1> controls or                        |                            |                      |                           |                 |        |

|                 |                    | nerator contro                         | •                          | •                    |                           |                 |        |

| bit 8           | OVRENL: Ov         | erride Enable                          | for PWMxL Pir              | n bit                |                           |                 |        |

|                 | 1 = OVRDAT         | <0> controls or                        | utput on PWM               | xL pin               |                           |                 |        |

|                 | •                  | nerator contro                         |                            |                      |                           |                 |        |

| bit 7-6         |                    |                                        |                            |                      | de is Enabled b           |                 |        |

|                 |                    |                                        |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |

| bit 5-4         | FLTDAT<1:0         | >: Data for PW                         | MxH and PWN                | ۰<br>۸xL Pins if FLT | MOD is Enable             | ed bits         |        |

|                 | If Fault is active | ve, PWMxH is                           | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |

|                 | If Fault is active | ve, PWMxL is                           | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |

| bit 3-2         | CLDAT<1:0>         | : Data for PWN                         | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |

|                 |                    |                                        |                            | •                    | ecified by CLDA           |                 |        |

|                 |                    | IS AULIVE. F VVI                       |                            |                      |                           |                 |        |

| Note 1: The     |                    |                                        |                            |                      | enabled (PTEN             |                 |        |

## REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 17-7: VEL1CNT: VELOCITY COUNTER 1 REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | VELC  | NT<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | VELC  | NT<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

## REGISTER 17-8: INDX1CNTH: INDEX COUNTER 1 HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------------------|----------|-------|-------|-------|

|        |       |       | INDXCN <sup>®</sup> | T<31:24> |       |       |       |

| bit 15 |       |       |                     |          |       |       | bit 8 |

|        |       |       |                     |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | INDXCN              | T<23:16> |       |       |       |

| bit 7  |       |       |                     |          |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

### REGISTER 17-9: INDX1CNTL: INDEX COUNTER 1 LOW WORD REGISTER

'1' = Bit is set

| R/W-0          | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------|-------|------------------|-------|--------------|------------------|----------|-------|

|                |       |                  | INDXC | NT<15:8>     |                  |          |       |

| bit 15         |       |                  |       |              |                  |          | bit 8 |

|                |       |                  |       |              |                  |          |       |

| R/W-0          | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                |       |                  | INDXC | NT<7:0>      |                  |          |       |

| bit 7          |       |                  |       |              |                  |          | bit 0 |

|                |       |                  |       |              |                  |          |       |

| Legend:        |       |                  |       |              |                  |          |       |

| R = Readable b | oit   | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

|                |       |                  |       |              |                  |          |       |

'0' = Bit is cleared

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

-n = Value at POR

x = Bit is unknown

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                                                       | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|-------------------------------------------------------------|-------|-------|-----------------|------------------------------------|-------|-------|-------|

|                                                             |       |       | INTHL           | D<31:24>                           |       |       |       |

| bit 15                                                      |       |       |                 |                                    |       |       | bit 8 |

|                                                             |       |       |                 |                                    |       |       |       |

| R/W-0                                                       | R/W-0 | R/W-0 | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                             |       |       | INTHL           | D<23:16>                           |       |       |       |

| bit 7                                                       |       |       |                 |                                    |       |       | bit 0 |

|                                                             |       |       |                 |                                    |       |       |       |

| Legend:                                                     |       |       |                 |                                    |       |       |       |

| R = Readable bit W = Writable bit                           |       |       | oit             | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = |       |       | x = Bit is unkr | nown                               |       |       |       |

bit 15-0 INTHLD<31:16>: Hold Register for Reading and Writing INT1TMRH bits

## REGISTER 17-20: INT1HLDL: INTERVAL 1 TIMER HOLD LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|------------------------------------|-------|-------|-------|------------------------------------|-------|-----------------|-------|

|                                    |       |       | INTHL | .D<15:8>                           |       |                 |       |

| bit 15                             |       |       |       |                                    |       |                 | bit 8 |

|                                    |       |       |       |                                    |       |                 |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

|                                    |       |       | INTH  | _D<7:0>                            |       |                 |       |

| bit 7                              |       |       |       |                                    |       |                 | bit 0 |

|                                    |       |       |       |                                    |       |                 |       |

| Legend:                            |       |       |       |                                    |       |                 |       |

| R = Readable bit W = Writable bit  |       |       | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |

|                                    |       |       |       |                                    |       |                 |       |

bit 15-0 INTHLD<15:0>: Hold Register for Reading and Writing INT1TMRL bits

## FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

## TABLE 30-54: OP AMP/COMPARATOR VOLTAGE REFERENCE SETTLING TIME SPECIFICATIONS

| AC CHARACTERISTICS |        |                | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 2): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |            |

|--------------------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|

| Param.             | Symbol | Characteristic | Min.                                                                                                                                                                                                                                                                                                 | Тур. | Max. | Units | Conditions |

| VR310              | TSET   | Settling Time  | —                                                                                                                                                                                                                                                                                                    | 1    | 10   | μS    | (Note 1)   |

**Note 1:** Settling time is measured while CVRR = 1 and CVR<3:0> bits transition from '0000' to '1111'.

2: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-55: OP AMP/COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                            | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |            |       |               |  |

|--------------------|--------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|-------|---------------|--|

| Param<br>No.       | Symbol | Characteristics                            | Min.                                                                                                                                                                                                                                                                                                 | Тур. | Max.       | Units | Conditions    |  |

| VRD310             | CVRES  | Resolution                                 | CVRSRC/24                                                                                                                                                                                                                                                                                            | _    | CVRSRC/32  | LSb   |               |  |

| VRD311             | CVRAA  | Absolute Accuracy <sup>(2)</sup>           | —                                                                                                                                                                                                                                                                                                    | ±25  | _          | mV    | CVRSRC = 3.3V |  |

| VRD313             | CVRSRC | Input Reference Voltage                    | 0                                                                                                                                                                                                                                                                                                    | _    | AVDD + 0.3 | V     |               |  |

| VRD314             | CVRout | Buffer Output<br>Resistance <sup>(2)</sup> | _                                                                                                                                                                                                                                                                                                    | 1.5k | _          | Ω     |               |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

2: Parameter is characterized but not tested in manufacturing.

# 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

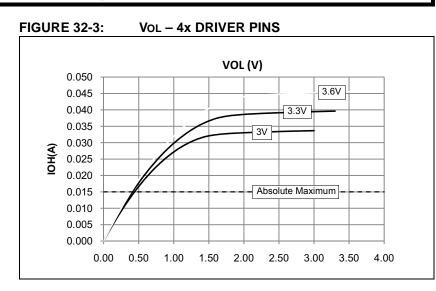

**FIGURE 32-1: VOH – 4x DRIVER PINS** VOH (V) -0.050 -0.045 3.6V -0.040 3.3V -0.035 3V -0.030 IOH(A) -0.025 -0.020 Absolute Maximum -0.015 -0.010 -0.005 0.000 0.50 1.00 2.00 2.50 3.00 3.50 0.00 1.50 4.00

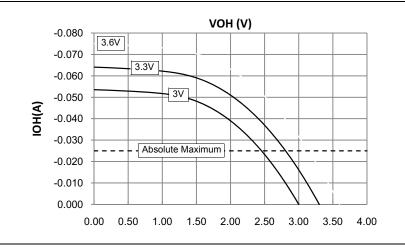

## FIGURE 32-2: VOH – 8x DRIVER PINS

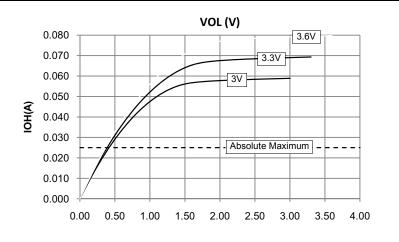

## FIGURE 32-4: Vol – 8x DRIVER PINS

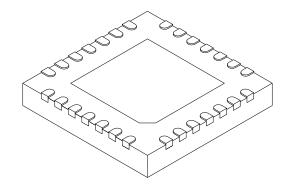

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |      |          |      |

|-------------------------|-------------|------|----------|------|

| Dimension               | Limits      | MIN  | NOM      | MAX  |

| Number of Pins          | Ν           |      | 28       |      |

| Pitch                   | е           |      | 0.65 BSC |      |

| Overall Height          | А           | 0.80 | 0.90     | 1.00 |

| Standoff                | A1          | 0.00 | 0.02     | 0.05 |

| Terminal Thickness      | A3          |      | 0.20 REF |      |

| Overall Width           | Е           |      | 6.00 BSC |      |

| Exposed Pad Width       | E2          | 3.65 | 3.70     | 4.70 |

| Overall Length          | D           |      | 6.00 BSC |      |

| Exposed Pad Length      | D2          | 3.65 | 3.70     | 4.70 |

| Terminal Width          | b           | 0.23 | 0.30     | 0.35 |

| Terminal Length         | L           | 0.30 | 0.40     | 0.50 |

| Terminal-to-Exposed Pad | К           | 0.20 | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

$\label{eq:REF:Reference} \ensuremath{\mathsf{REF:}} \ensuremath{\mathsf{Reference}}\xspace \ensuremath{\mathsf{Dimension}}, \ensuremath{\mathsf{usually}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace, \ensuremath{\mathsf{for}}\xspace \ensuremath{\mathsf{oterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{rescale}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{$

Microchip Technology Drawing C04-124C Sheet 2 of 2

## **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources". All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.

All other major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>256-Kbyte Flash and<br>32-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | The content on the first page of this section was extensively reworked to provide the reader with the key features and functionality of this device family in an "at-a-glance" format.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 1.0 "Device<br>Overview"                                                                                                                                        | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X Block Diagram (see Figure 1-1), which now contains a CPU<br>block and a reference to the CPU diagram.<br>Updated the description and Note references in the Pinout I/O Descriptions for these                                                                                                                                                                                                                                                                                                                                                              |

| Section 2.0 "Guidelines for<br>Getting Started with 16-bit<br>Digital Signal Controllers<br>and Microcontrollers"                                                       | pins: C1IN2-, C2IN2-, C3IN2-, OA1OUT, OA2OUT, and OA3OUT (see Table 1-1).<br>Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Section 3.0 "CPU"                                                                                                                                                       | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X CPU Block Diagram (see Figure 3-1).<br>Updated the Status register definition in the Programmer's Model (see Figure 3-2).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Section 4.0 "Memory<br>Organization"                                                                                                                                    | Updated the Data Memory Maps (see Figure 4-6 and Figure 4-11).<br>Removed the DCB<1:0> bits from the OC1CON2, OC2CON2, OC3CON2, and<br>OC4CON2 registers in the Output Compare 1 Through Output Compare 4 Register<br>Map (see Table 4-10).<br>Added the TRIG1 and TRGCON1 registers to the PWM Generator 1 Register Map<br>(see Table 4-13).<br>Added the TRIG2 and TRGCON2 registers to the PWM Generator 2 Register Map<br>(see Table 4-14).<br>Added the TRIG3 and TRGCON3 registers to the PWM Generator 3 Register Map<br>(see Table 4-15).<br>Updated the second note in Section 4.7.1 "Bit-Reversed Addressing<br>Implementation". |

| Section 8.0 "Direct Memory<br>Access (DMA)"                                                                                                                             | Updated the DMA Controller diagram (see Figure 8-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Section 14.0 "Input<br>Capture"                                                                                                                                         | Updated the bit values for the ICx clock source of the ICTSEL<12:10> bits in the ICxCON1 register (see Register 14-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 15.0 "Output<br>Compare"                                                                                                                                        | Updated the bit values for the OCx clock source of the OCTSEL<2:0> bits in the OCxCON1 register (see Register 15-1).<br>Removed the DCB<1:0> bits from the Output Compare x Control Register 2 (see Register 15-2).                                                                                                                                                                                                                                                                                                                                                                                                                        |

TABLE A-2: MAJOR SECTION UPDATES

## TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)

NOTES: