Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

⊡XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502t-i-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name  | Addr          | Bit 15 | Bit 14                                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7                      | Bit 6    | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|----------------------------------------|--------|--------|--------|--------|--------|-------|----------------------------|----------|--------|-------|--------|--------|--------|--------|---------------|

|            | 0400-<br>041E |        | See definition when WIN = $\mathbf{x}$ |        |        |        |        |        |       |                            |          |        |       |        |        |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BP<3:0> F2BP<3:0>                    |        |        |        |        | F1BP   | <3:0> |                            |          | F0BP   | <3:0> |        | 0000   |        |        |               |

| C1BUFPNT2  | 0422          |        | F7BF                                   | ><3:0> |        |        | F6BI   | ><3:0> |       |                            | F5BP     | <3:0>  |       |        | F4BP   | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11B                                   | P<3:0> |        |        | F10B   | P<3:0> |       |                            | F9BP     | <3:0>  |       |        | F8BP   | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15B                                   | P<3:0> |        |        | F14B   | P<3:0> |       |                            | F13B     | D<3:0> |       |        | F12BF  | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | _     | MIDE   | _      | EID<   | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |        |                                        |        | EID<   | :15:8> |        |        |       |                            |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXM1SID  | 0434          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | _     | MIDE   | —      | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |        |                                        |        | EID<   | :15:8> |        |        |       |                            |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXM2SID  | 0438          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | MIDE   | —      | EID<   | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |        |                                        |        | EID<   | :15:8> |        |        |       |                            |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXF0SID  | 0440          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |        |                                        |        | EID<   | :15:8> |        |        |       |                            |          |        | EID<  | 7:0>   |        | -      |        | xxxx          |

| C1RXF1SID  | 0444          |        |                                        |        | SID<   | :10:3> |        |        |       | SID<2:0> — EXIDE — EI      |          |        | EID<  | 17:16> | xxxx   |        |        |               |

| C1RXF1EID  | 0446          |        |                                        |        | EID<   | :15:8> |        |        |       | EID<7:0>                   |          |        |       | xxxx   |        |        |        |               |

| C1RXF2SID  | 0448          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |        |                                        |        | EID<   | :15:8> |        |        |       | EID                        |          |        | EID<  | <7:0>  |        |        |        | xxxx          |

| C1RXF3SID  | 044C          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |        |                                        |        | EID<   | :15:8> |        |        |       | EID<7:0>                   |          |        |       |        | xxxx   |        |        |               |

| C1RXF4SID  | 0450          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |        |                                        |        | EID<   | :15:8> |        |        |       |                            | EID<7:0> |        |       |        | xxxx   |        |        |               |

| C1RXF5SID  | 0454          |        |                                        |        | SID<   | :10:3> |        |        |       | SID<2:0> — EXIDE — EID<17: |          |        |       |        | 17:16> | xxxx   |        |               |

| C1RXF5EID  | 0456          |        |                                        |        | EID<   | :15:8> |        |        |       |                            |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXF6SID  | 0458          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |                                        |        | EID<   | :15:8> |        |        |       |                            |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXF7SID  | 045C          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |                                        |        | EID<   | :15:8> |        |        |       |                            |          |        | EID<  | 7:0>   |        |        |        | xxxx          |

| C1RXF8SID  | 0460          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |        |                                        |        |        | :15:8> |        |        |       |                            |          |        | EID<  | -      |        |        |        | xxxx          |

| C1RXF9SID  | 0464          |        |                                        |        |        | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |        |                                        |        |        | :15:8> |        |        |       |                            |          |        | EID<  |        |        |        |        | xxxx          |

| C1RXF10SID | 0468          |        |                                        |        |        | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | —      | EID<   | 17:16> | xxxx          |

| C1RXF10EID | 046A          |        |                                        |        |        | :15:8> |        |        |       |                            |          |        | EID<  | -      |        |        |        | xxxx          |

| C1RXF11SID | 046C          |        |                                        |        | SID<   | :10:3> |        |        |       |                            | SID<2:0> |        | —     | EXIDE  | -      | EID<   | 17:16> | xxxx          |

### TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                         | SV SI ACE BOON |              |                        |                |              |                        |  |

|-------------|---------------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|

| 0/11        |                           |                | Before       |                        | After          |              |                        |  |

| O/U,<br>R/W | Operation                 | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |  |

| O,<br>Read  |                           | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |

| O,<br>Read  | [++Wn]                    | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |  |

| O,<br>Read  | <b>Or</b><br>[Wn++]       | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |

| O,<br>Write |                           | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |

| U,<br>Read  |                           | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |  |

| U,<br>Read  | [Wn]<br><b>or</b><br>[Wn] | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |  |

| U,<br>Read  | [ //11 - ]                | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

### 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

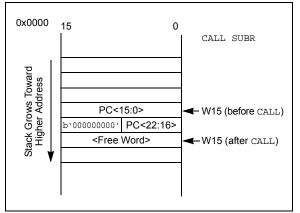

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

### 4.8 Interfacing Program and Data Memory Spaces

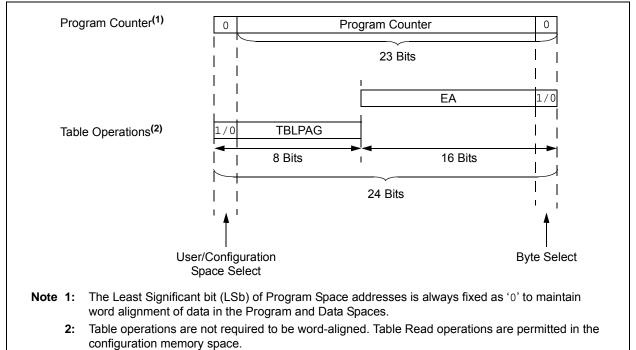

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

### TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address      |             |          |               |     |  |  |

|------------------------|---------------|----------------------------|-------------|----------|---------------|-----|--|--|

| Access Type            | Space         | <23>                       | <22:16>     | <15>     | <14:1>        | <0> |  |  |

| Instruction Access     | User          | 0                          | 0 PC<22:1>  |          |               |     |  |  |

| (Code Execution)       |               | 0xx xxxx xxxx xxxx xxxx xx |             |          |               |     |  |  |

| TBLRD/TBLWT            | User          | TBLPAG<7:0> Data EA<15:0>  |             |          |               |     |  |  |

| (Byte/Word Read/Write) |               | 0                          | xxx xxxx    | XXXX XXX | ***           |     |  |  |

|                        | Configuration | TB                         | TBLPAG<7:0> |          | Data EA<15:0> |     |  |  |

|                        |               | 1                          | xxx xxxx    | XXXX XX  | ***           |     |  |  |

### FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

### 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

### **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, WO | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

### REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                       | R/W-0         | R/W-0              | R/W-0 |  |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|-----------------------------|---------------|--------------------|-------|--|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                | >             |                    |       |  |  |

| bit 15             |                                            |                                                 |                                            |                             |               |                    | bit 8 |  |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                         | U-0           | U-0                | U-0   |  |  |

| _                  |                                            |                                                 | —                                          |                             |               | <u> </u>           | _     |  |  |

| bit 7              |                                            |                                                 |                                            |                             |               |                    | bit 0 |  |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |  |

| Legend:            |                                            |                                                 |                                            |                             |               |                    |       |  |  |

| R = Readab         | ole bit                                    | W = Writable                                    | ble bit U = Unimplemented bit, read as '0' |                             |               |                    |       |  |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea           | ared          | x = Bit is unknown |       |  |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                             |               |                    |       |  |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers) | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                             | the Correspon | ding RPn Pin b     | its   |  |  |

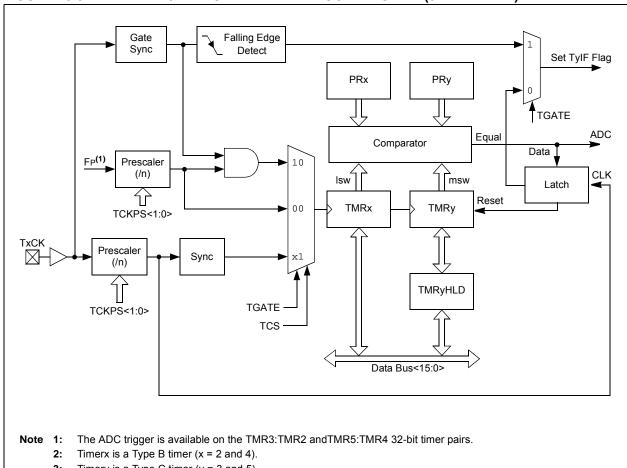

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

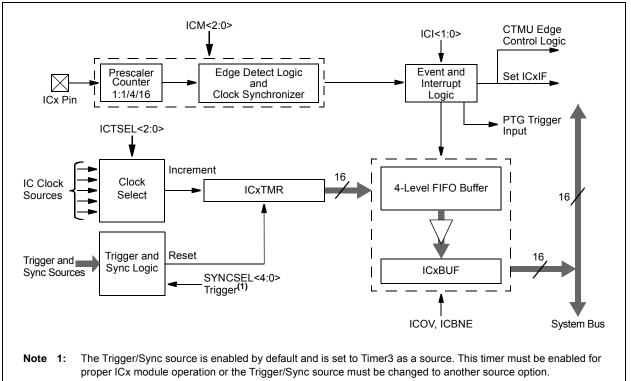

### 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

## 14.2 Input Capture Registers

### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit HS = Ha |                                    | Hardware Settable bit |  |  |

|-------------------|-------------------------------------|------------------------------------|-----------------------|--|--|

| R = Readable bit  | W = Writable bit                    | U = Unimplemented bit, read as '0' |                       |  |  |

| -n = Value at POR | '1' = Bit is set                    | '0' = Bit is cleared               | x = Bit is unknown    |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|       | R/W-0            | R/W-0           | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                  | R/W-0                                                                                                    |

|-------|------------------|-----------------|---------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|       |                  | QEIG            | EC<31:24>                             |                                                                  |                                                                                                        |                                                                                                          |

|       |                  |                 |                                       |                                                                  |                                                                                                        | bit 8                                                                                                    |

|       | DAMO             |                 |                                       |                                                                  | DAMO                                                                                                   |                                                                                                          |

| R/W-U | R/W-0            |                 |                                       | R/W-U                                                            | R/W-U                                                                                                  | R/W-0                                                                                                    |

|       |                  | QEIGE           | EC<23:16>                             |                                                                  |                                                                                                        |                                                                                                          |

|       |                  |                 |                                       |                                                                  |                                                                                                        | bit (                                                                                                    |

|       |                  |                 |                                       |                                                                  |                                                                                                        |                                                                                                          |

|       | W = Writable bi  | t               | U = Unimplemented bit, read as '0'    |                                                                  |                                                                                                        |                                                                                                          |

| २     | '1' = Bit is set |                 | '0' = Bit is cleared                  |                                                                  | x = Bit is unknown                                                                                     |                                                                                                          |

|       | R/W-0            | W = Writable bi | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit       U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |

### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | QEIGE | C<15:8>                                 |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | QEIG  | EC<7:0>                                 |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable I  | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |           |              |                                         |                |                |          |       |  |

|------------------------------------|-----------|--------------|-----------------------------------------|----------------|----------------|----------|-------|--|

|                                    | R/W-0     | R/W-0        | R/W-0                                   | R/W-0          | R/W-0          | R/W-0    | R/W-0 |  |

| F7BP<3:0>                          |           |              |                                         |                | F6BF           | P<3:0>   |       |  |

| bit 15                             |           |              |                                         |                |                |          | bit 8 |  |

| R/W-0                              | R/W-0     | R/W-0        | R/W-0                                   | R/W-0          | R/W-0          | R/W-0    | R/W-0 |  |

|                                    | F5BP<3:0> |              |                                         | F4BP<3:0>      |                |          |       |  |

| bit 7                              |           |              |                                         |                |                |          | bit 0 |  |

| Legend:                            |           |              |                                         |                |                |          |       |  |

| R = Readable bi                    | t         | W = Writable | bit                                     | U = Unimplemer | nted bit, read | d as '0' |       |  |

| -n = Value at POR '1' = Bit is set |           |              | '0' = Bit is cleared x = Bit is unknown |                |                | nown     |       |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0                             | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0   | R/W-0 |

|-----------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----------------|---------|-------|

|                                   | F11BP<3:0>                                         |                                                                                               |                                                |                                         | F10B           | SP<3:0> |       |

| bit 15                            |                                                    |                                                                                               |                                                |                                         |                |         | bit 8 |

| R/W-0                             | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0   | R/W-0 |

| F9BP<3:0>                         |                                                    |                                                                                               |                                                |                                         | F8B            | P<3:0>  |       |

| bit 7                             |                                                    |                                                                                               |                                                |                                         |                |         | bit 0 |

| Legend:                           |                                                    |                                                                                               |                                                |                                         |                |         |       |

| R = Readable bit W = Writable bit |                                                    | bit                                                                                           | U = Unimplemented bit, read as '0'             |                                         |                |         |       |

| -n = Value at                     | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cleared x = Bit is unknown |                |         | nown  |

| bit 15-12                         | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4                              |                |         |       |

| bit 11-8                          | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val                        | ues as bits<1  | 5:12>)  |       |

| bit 7-4                           | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value                        | s as bits<15:1 | 2>)     |       |

| bit 3-0                           | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value                        | s as bits<15:1 | 2>)     |       |

|                                   |                                                    |                                                                                               |                                                |                                         |                |         |       |

© 2011-2013 Microchip Technology Inc.

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0                                                                 | R/W-0 | R/W-0          | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|-----------------------------------------------------------------------|-------|----------------|-----------------|------------------------------------|-------|-------|-------|

|                                                                       |       |                | PTGSD           | LIM<15:8>                          |       |       |       |

| bit 15                                                                |       |                |                 |                                    |       |       | bit 8 |

|                                                                       |       |                |                 |                                    |       |       |       |

| R/W-0                                                                 | R/W-0 | R/W-0          | R/W-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                                                       |       |                | PTGSE           | )LIM<7:0>                          |       |       |       |

| bit 7                                                                 |       |                |                 |                                    |       |       | bit 0 |

|                                                                       |       |                |                 |                                    |       |       |       |

| Legend:                                                               |       |                |                 |                                    |       |       |       |

| R = Readable                                                          | bit   | W = Writable b | it              | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is un |       |                | x = Bit is unkr | nown                               |       |       |       |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                                                                  | R/W-0 | R/W-0           | R/W-0 | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|------------------------------------------------------------------------|-------|-----------------|-------|--------------|-----------------|-----------|-------|

|                                                                        |       |                 | PTGC0 | LIM<15:8>    |                 |           |       |

| bit 15                                                                 |       |                 |       |              |                 |           | bit 8 |

|                                                                        |       |                 |       |              |                 |           |       |

| R/W-0                                                                  | R/W-0 | R/W-0           | R/W-0 | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|                                                                        |       |                 | PTGC  | )LIM<7:0>    |                 |           |       |

| bit 7                                                                  |       |                 |       |              |                 |           | bit 0 |

|                                                                        |       |                 |       |              |                 |           |       |

| Legend:                                                                |       |                 |       |              |                 |           |       |

| R = Readable                                                           | bit   | W = Writable bi | it    | U = Unimplem | nented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk |       |                 |       | nown         |                 |           |       |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | R1 EXTERNAL CLOCK TIMING REQUIREMENTS <sup>(1)</sup> | ) |

|-------------------|------------------------------------------------------|---|

|-------------------|------------------------------------------------------|---|

| AC CHARACTERISTICS |           |                                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                        |      |               |       |                                                                             |

|--------------------|-----------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(2)</sup>                                                                      |                                                                                                                                                                                                                                                                                         | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                  | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                            | 35                                     | _    | —             | ns    |                                                                             |

| TA11               | ΤτχL      | T1CK Low<br>Time                                                                                   | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                            | 10                                     | _    | _             | ns    |                                                                             |

| TA15               | ΤτχΡ      | T1CK Input<br>Period                                                                               | Synchronous mode                                                                                                                                                                                                                                                                        | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |

| OS60               | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                                                                                                                                                                                                                                                                                         | DC                                     |      | 50            | kHz   |                                                                             |

| TA20               | TCKEXTMRL | Delay from External T1CK<br>Clock Edge to Timer<br>Increment                                       |                                                                                                                                                                                                                                                                                         | 0.75 Tcy + 40                          | —    | 1.75 Tcy + 40 | ns    |                                                                             |

Note 1: Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

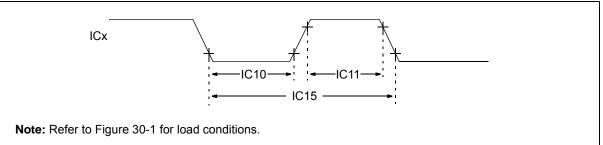

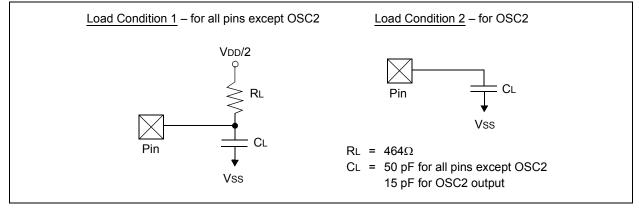

### FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS                                  |                       |                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |       |                                  |                                  |  |

|-----------------------------------------------------|-----------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|

| Param.<br>No. Symbol Characteristics <sup>(1)</sup> |                       |                     | Min.                                                                                                                                                                                                                                                                                | Max. | Units | Conditions                       |                                  |  |

| IC10                                                | TccL                  | ICx Input Low Time  | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                      |      | ns    | Must also meet<br>Parameter IC15 |                                  |  |

| IC11                                                | ТссН                  | ICx Input High Time | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                                                      | —    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |  |

| IC15                                                | TCCP ICx Input Period |                     | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50                                                                                                                                                                                                                                       | _    | ns    |                                  |                                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

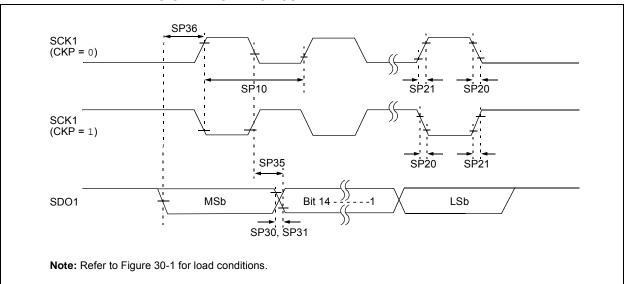

### FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

### TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS                          |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |  |

|---------------------------------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|--|

| Param. Symbol Characteristic <sup>(1)</sup> |                       |                                              | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |  |

| SP10                                        | FscP                  | Maximum SCK1 Frequency                       | —                                                                                                                                                                                                                                                                                       |                     | 15   | MHz   | (Note 3)                       |  |

| SP20                                        | TscF                  | SCK1 Output Fall Time                        | -                                                                                                                                                                                                                                                                                       | -                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP21                                        | TscR                  | SCK1 Output Rise Time                        | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4)    |  |

| SP30                                        | TdoF                  | SDO1 Data Output Fall Time                   | -                                                                                                                                                                                                                                                                                       | -                   | _    | ns    | See Parameter DO32<br>(Note 4) |  |

| SP31                                        | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4)    |  |

| SP35                                        | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                |  |

| SP36                                        | TdiV2scH,<br>TdiV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                                                                                                                                                                                                                                                                      |                     |      | ns    |                                |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

#### 31.2 **AC Characteristics and Timing Parameters**