Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

| Product Status            | Active                                                                            |

| Core Processor            | dsPIC                                                                             |

| Core Size                 | 16-Bit                                                                            |

| Speed                     | 70 MIPs                                                                           |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O             | 21                                                                                |

| Program Memory Size       | 128KB (43K x 24)                                                                  |

| rogram Memory Type        | FLASH                                                                             |

| EPROM Size                | -                                                                                 |

| RAM Size                  | 8K x 16                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| ata Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type           | Internal                                                                          |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Nounting Type             | Surface Mount                                                                     |

| ackage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| upplier Device Package    | 28-SOIC                                                                           |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

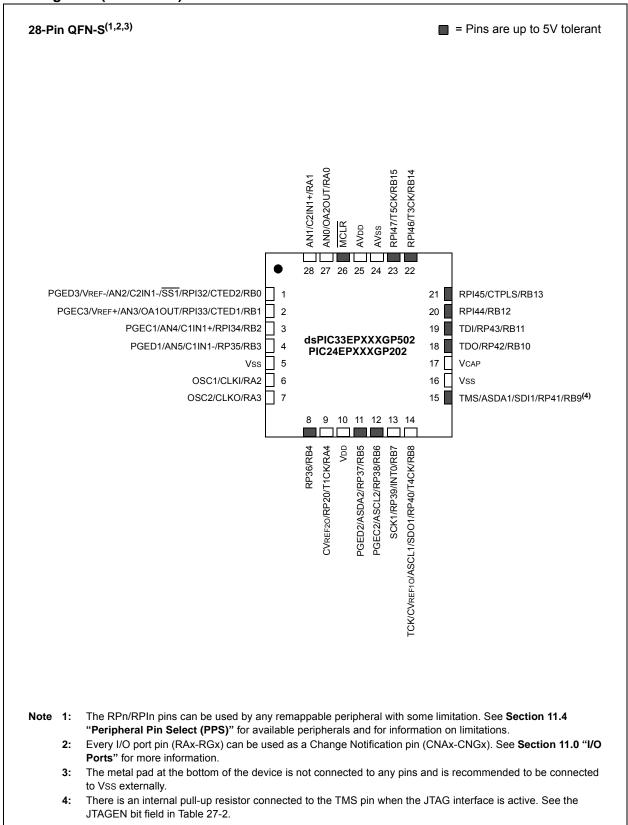

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

TABLE 4-62: DATA MEMORY BUS ARBITER PRIORITY

| Priority     | MSTRPR<15:0 | > Bit Setting <sup>(1)</sup> |

|--------------|-------------|------------------------------|

| Priority     | 0x0000      | 0x0020                       |

| M0 (highest) | CPU         | DMA                          |

| M1           | Reserved    | CPU                          |

| M2           | Reserved    | Reserved                     |

| M3           | DMA         | Reserved                     |

| M4 (lowest)  | ICD         | ICD                          |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

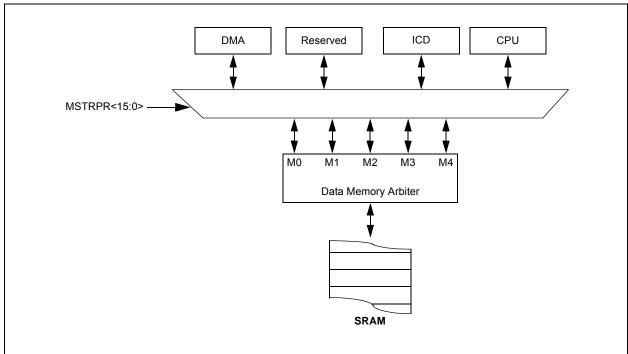

# 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Type            | Access        | Program Space Address         |             |      |               |     |  |

|------------------------|---------------|-------------------------------|-------------|------|---------------|-----|--|

| Access Type            | Space         | <23>                          | <22:16>     | <15> | <14:1>        | <0> |  |

| Instruction Access     | User          | 0 PC<22:1>                    |             |      | 0             |     |  |

| (Code Execution)       |               | 0xx xxxx xxxx xxxx xxxx xxx0  |             |      |               |     |  |

| TBLRD/TBLWT            | User          | TBLPAG<7:0> Data EA<15:0>     |             |      |               |     |  |

| (Byte/Word Read/Write) |               | 0xxx xxxx xxxx xxxx xxxx      |             |      |               |     |  |

|                        | Configuration | ТВ                            | TBLPAG<7:0> |      | Data EA<15:0> |     |  |

|                        |               | 1xxx xxxx xxxx xxxx xxxx xxxx |             |      | xxx xxxx xxxx |     |  |

FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

- **Note 1:** The Least Significant bit (LSb) of Program Space addresses is always fixed as '0' to maintain word alignment of data in the Program and Data Spaces.

- **2:** Table operations are not required to be word-aligned. Table Read operations are permitted in the configuration memory space.

#### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## REGISTER 8-5: DMAXSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-------|-------|-------|--------|-------|-------|-------|--|

|       |       |       | STB<  | 23:16> |       |       |       |  |

| bit 7 |       |       |       |        |       |       |       |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **STB<23:16>:** Secondary Start Address bits (source or destination)

# REGISTER 8-6: DMAXSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-------|-------|--------|-------|-------|-------|-------|--|--|

|        |       |       | STB<   | 15:8> |       |       |       |  |  |

| bit 15 |       |       | bit 15 |       |       |       |       |  |  |

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|----------|-------|-------|-------|-------|-------|-------|--|

|       | STB<7:0> |       |       |       |       |       |       |  |

| bit 7 |          |       |       |       |       |       |       |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

## 13.2 Timer Control Registers

#### REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|--------|-----|-------|-----|-----|-----|-----|-----|

| TON    | _   | TSIDL | _   | _   | _   | _   | _   |

| bit 15 |     |       |     |     |     |     |     |

| U-0   | R/W-0 | R/W-0  | R/W-0  | R/W-0 | U-0 | R/W-0 | U-0   |

|-------|-------|--------|--------|-------|-----|-------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | T32   | _   | TCS   | _     |

| bit 7 |       |        |        |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timerx On bit

When T32 = 1:

1 = Starts 32-bit Timerx/y 0 = Stops 32-bit Timerx/y

When T32 = 0:

1 = Starts 16-bit Timerx

0 = Stops 16-bit Timerx

bit 14 **Unimplemented:** Read as '0'

bit 13 TSIDL: Timerx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 TGATE: Timerx Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timerx Input Clock Prescale Select bits

11 = 1:256 10 = 1:64 01 = 1:8

00 = 1:1

bit 3 T32: 32-Bit Timer Mode Select bit

1 = Timerx and Timery form a single 32-bit timer 0 = Timerx and Timery act as two 16-bit timers

bit 2 Unimplemented: Read as '0'

bit 1 TCS: Timerx Clock Source Select bit

1 = External clock is from pin, TxCK (on the rising edge)

0 = Internal clock (FP)

bit 0 Unimplemented: Read as '0'

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0                 | R/W/HS-0                | U-0 | R/W-0                   | R/W-1                   | R/W-1       | R/W-0       | R/W-1                   |

|-----------------------|-------------------------|-----|-------------------------|-------------------------|-------------|-------------|-------------------------|

| ICTRIG <sup>(2)</sup> | TRIGSTAT <sup>(3)</sup> | _   | SYNCSEL4 <sup>(4)</sup> | SYNCSEL3 <sup>(4)</sup> | SYNCSEL2(4) | SYNCSEL1(4) | SYNCSEL0 <sup>(4)</sup> |

| bit 7                 |                         |     |                         |                         |             |             | bit 0                   |

**Legend:** HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 **Unimplemented:** Read as '0'

bit 8 IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

0 = Cascade module operation is disabled

bit 7 ICTRIG: Input Capture Trigger Operation Select bit<sup>(2)</sup>

1 = Input source used to trigger the input capture timer (Trigger mode)

0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

bit 6 TRIGSTAT: Timer Trigger Status bit (3)

1 = ICxTMR has been triggered and is running

0 = ICxTMR has not been triggered and is being held clear

bit 5 **Unimplemented:** Read as '0'

Note 1: The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- 3: This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See **Section 24.0** "**Peripheral Trigger Generator (PTG) Module**" for more information.

PTGO8 = IC1

PTGO9 = IC2

PTGO10 = IC3

PTGO11 = IC4

## REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

3: Do not set both primary and secondary prescalers to the value of 1:1.

```

bit 4-2

SPRE<2:0>: Secondary Prescale bits (Master mode)(3)

111 = Secondary prescale 1:1

110 = Secondary prescale 2:1

•

000 = Secondary prescale 8:1

bit 1-0

PPRE<1:0>: Primary Prescale bits (Master mode)(3)

11 = Primary prescale 1:1

10 = Primary prescale 4:1

01 = Primary prescale 4:1

01 = Primary prescale 16:1

00 = Primary prescale 64:1

Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

```

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

**Legend:** C = Writable bit, but only '0' can be written to clear the bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **RXOVF<15:0>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxrXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

**Legend:** C = Writable bit, but only '0' can be written to clear the bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 15-0 **RXOVF<31:16>:** Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2

| R/W-0  | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----|-----|-------|-------|-------|

| VCFG2  | VCFG1 | VCFG0 | _   | _   | CSCNA | CHPS1 | CHPS0 |

| bit 15 |       |       |     |     |       |       | bit 8 |

| R-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BUFS  | SMPI4 | SMPI3 | SMPI2 | SMPI1 | SMPI0 | BUFM  | ALTS  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-13 VCFG<2:0>: Converter Voltage Reference Configuration bits

| Value | VREFH          | VREFL          |  |  |

|-------|----------------|----------------|--|--|

| 000   | Avdd           | Avss           |  |  |

| 001   | External VREF+ | Avss           |  |  |

| 010   | Avdd           | External VREF- |  |  |

| 011   | External VREF+ | External VREF- |  |  |

| 1xx   | Avdd           | Avss           |  |  |

bit 12-11 **Unimplemented:** Read as '0'

bit 10 CSCNA: Input Scan Select bit

1 = Scans inputs for CH0+ during Sample MUXA

0 = Does not scan inputs

bit 9-8 CHPS<1:0>: Channel Select bits

In 12-bit mode (AD21B = 1), the CHPS<1:0> bits are Unimplemented and are Read as '0':

1x = Converts CH0, CH1, CH2 and CH3

01 = Converts CH0 and CH1

00 = Converts CH0

bit 7 **BUFS:** Buffer Fill Status bit (only valid when BUFM = 1)

- 1 = ADC is currently filling the second half of the buffer; the user application should access data in the first half of the buffer

- 0 = ADC is currently filling the first half of the buffer; the user application should access data in the second half of the buffer

#### bit 6-2 **SMPI<4:0>:** Increment Rate bits

#### When ADDMAEN = 0:

x1111 = Generates interrupt after completion of every 16th sample/conversion operation x1110 = Generates interrupt after completion of every 15th sample/conversion operation

•

•

x0001 = Generates interrupt after completion of every 2nd sample/conversion operation

x0000 = Generates interrupt after completion of every sample/conversion operation

#### When ADDMAEN = 1:

11111 = Increments the DMA address after completion of every 32nd sample/conversion operation 11110 = Increments the DMA address after completion of every 31st sample/conversion operation

•

•

00001 = Increments the DMA address after completion of every 2nd sample/conversion operation

00000 = Increments the DMA address after completion of every sample/conversion operation

#### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER

| R/W-0  | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----|-----|-----|-------|-------|

| CON    | COE   | CPOL  | _   | _   | _   | CEVT  | COUT  |

| bit 15 |       |       |     |     |     |       | bit 8 |

| R/W-0  | R/W-0  | U-0 | R/W-0               | U-0 | U-0 | R/W-0               | R/W-0               |

|--------|--------|-----|---------------------|-----|-----|---------------------|---------------------|

| EVPOL1 | EVPOL0 | _   | CREF <sup>(1)</sup> | _   | _   | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |

| bit 7  |        |     |                     |     |     |                     | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CON: Comparator Enable bit

1 = Comparator is enabled

0 = Comparator is disabled

bit 14 **COE:** Comparator Output Enable bit

1 = Comparator output is present on the CxOUT pin

0 = Comparator output is internal only

bit 13 **CPOL:** Comparator Output Polarity Select bit

1 = Comparator output is inverted

0 = Comparator output is not inverted

bit 12-10 **Unimplemented:** Read as '0'

bit 9 **CEVT:** Comparator Event bit

1 = Comparator event according to EVPOL<1:0> settings occurred; disables future triggers and interrupts until the bit is cleared

0 = Comparator event did not occur

bit 8 **COUT:** Comparator Output bit

When CPOL = 0 (non-inverted polarity):

1 = VIN+ > VIN-

0 = VIN+ < VIN-

When CPOL = 1 (inverted polarity):

1 = VIN+ < VIN-

0 = VIN+ > VIN-

bit 7-6 **EVPOL<1:0>:** Trigger/Event/Interrupt Polarity Select bits

11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

Low-to-high transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

High-to-low transition of the comparator output.

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

Low-to-high transition of the comparator output.

00 = Trigger/event/interrupt generation is disabled

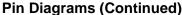

**Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

# 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- · Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- · Configurable interrupt output

- Data FIFO

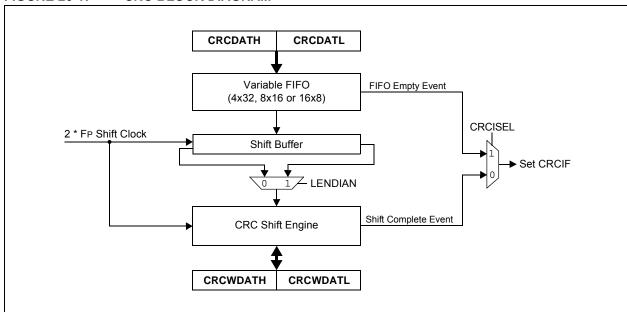

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

FIGURE 26-1: CRC BLOCK DIAGRAM

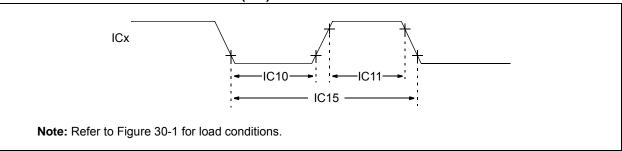

# FIGURE 30-6: INPUT CAPTURE x (ICx) TIMING CHARACTERISTICS

#### TABLE 30-26: INPUT CAPTURE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |      |       |                                  |                                  |  |

|--------------------|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|----------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                                                                                                                                                                                                             | Max. | Units | Conditions                       |                                  |  |

| IC10               | TccL   | ICx Input Low Time             | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                   | _    | ns    | Must also meet<br>Parameter IC15 |                                  |  |

| IC11               | TccH   | ICx Input High Time            | Greater of<br>12.5 + 25 or<br>(0.5 Tcy/N) + 25                                                                                                                                                                                                   | _    | ns    | Must also meet<br>Parameter IC15 | N = prescale value<br>(1, 4, 16) |  |

| IC15               | TccP   | ICx Input Period               | Greater of<br>25 + 50<br>or<br>(1 Tcy/N) + 50                                                                                                                                                                                                    | _    | ns    |                                  |                                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

TABLE 30-39: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)

TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |

|--------------------|-----------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>              | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP70               | FscP                  | Maximum SCK2 Input Frequency               | _                                                                                                                                                                                                                                                | _                   | 15   | MHz   | (Note 3)                    |

| SP72               | TscF                  | SCK2 Input Fall Time                       | _                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter DO32 (Note 4) |

| SP73               | TscR                  | SCK2 Input Rise Time                       | _                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                 | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                 | _                                                                                                                                                                                                                                                |                     | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge     | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to First SCK2 Edge  | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge  | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP50               | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input            | 120                                                                                                                                                                                                                                              | _                   | _    | ns    |                             |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance     | 10                                                                                                                                                                                                                                               | _                   | 50   | ns    | (Note 4)                    |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                      | 1.5 Tcy + 40                                                                                                                                                                                                                                     | _                   | _    | ns    | (Note 4)                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support