Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp502t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

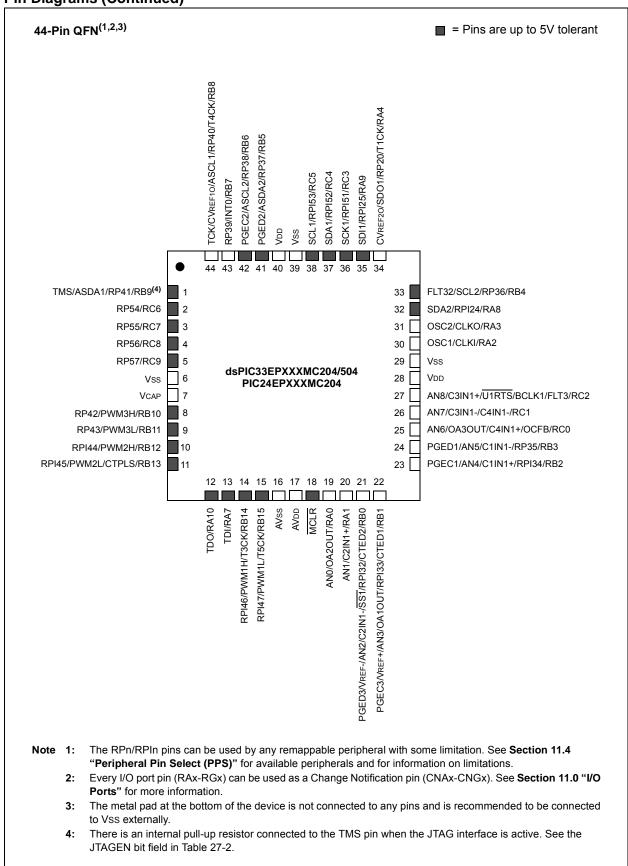

# Pin Diagrams (Continued)

# 3.7 CPU Control Registers

#### REGISTER 3-1: SR: CPU STATUS REGISTER

| R/W-0             | R/W-0             | R/W-0               | R/W-0               | R/C-0              | R/C-0              | R-0               | R/W-0 |

|-------------------|-------------------|---------------------|---------------------|--------------------|--------------------|-------------------|-------|

| OA <sup>(1)</sup> | OB <sup>(1)</sup> | SA <sup>(1,4)</sup> | SB <sup>(1,4)</sup> | OAB <sup>(1)</sup> | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC    |

| bit 15            |                   |                     |                     |                    |                    |                   | bit 8 |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------------------|------------------------|------------------------|-----|-------|-------|-------|-------|

| IPL2                   | IPL1                   | IPL0                   | RA  | N     | OV    | Z     | С     |

| bit 7                  |                        |                        |     |       |       |       | bit 0 |

| Legend:           | C = Clearable bit |                             |                    |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 OA: Accumulator A Overflow Status bit<sup>(1)</sup>

1 = Accumulator A has overflowed

0 = Accumulator A has not overflowed

bit 14 **OB:** Accumulator B Overflow Status bit<sup>(1)</sup>

1 = Accumulator B has overflowed

0 = Accumulator B has not overflowed

bit 13 **SA:** Accumulator A Saturation 'Sticky' Status bit (1,4)

1 = Accumulator A is saturated or has been saturated at some time

0 = Accumulator A is not saturated

bit 12 SB: Accumulator B Saturation 'Sticky' Status bit (1,4)

1 = Accumulator B is saturated or has been saturated at some time

0 = Accumulator B is not saturated

bit 11 OAB: OA || OB Combined Accumulator Overflow Status bit (1)

1 = Accumulators A or B have overflowed

0 = Neither Accumulators A or B have overflowed

bit 10 SAB: SA || SB Combined Accumulator 'Sticky' Status bit (1)

1 = Accumulators A or B are saturated or have been saturated at some time

0 = Neither Accumulators A or B are saturated

bit 9 **DA:** DO Loop Active bit<sup>(1)</sup>

1 = DO loop is in progress

0 = DO loop is not in progress

bit 8 **DC:** MCU ALU Half Carry/Borrow bit

- 1 = A carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- 0 = No carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9     | Bit 8 | Bit 7       | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1      | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|-----------|-------|-------------|---------|-------------|---------|---------|--------|------------|--------|---------------|

| IPC35        | 0886  | 1      | ,      | JTAGIP<2:0 | )>      | _       |        | ICDIP<2:0 | >     | 1           | _       | -           | 1       | _       | _      | _          | _      | 4400          |

| IPC36        | 0888  | -      | ı      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<   | 2:0>  | ı           | P       | TGSTEPIP<2  | :0>     | _       | -      | ı          | -      | 4440          |

| IPC37        | 088A  | -      | _      | _          | _       | _       | P      | TG3IP<2:0 | )>    | ı           |         | PTG2IP<2:0> | >       | _       | F      | TG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE     | COVTE | SFTACERR    | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL    | -      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | -       | _       | _      | _         | -     | ı           | _       | _           | ı       | _       | INT2EP | INT1EP     | INT0EP | 8000          |

| INTCON3      | 08C4  | ı      | _      | _          | -       | _       | _      | _         | -     | ı           | _       | DAE         | DOOVR   | _       | -      | ı          | -      | 0000          |

| INTCON4      | 08C6  | -      | _      | _          | _       | _       | _      | _         | _     | -           | _       | _           |         | _       | _      | _          | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _          | _       |         | ILR<   | 3:0>      |       | VECNUM<7:0> |         |             |         |         | 0000   |            |        |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions, which apply to dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note:

For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- · Register Direct

- Register Indirect

- · Register Indirect Post-modified

- · Register Indirect Pre-modified

- · Register Indirect with Register Offset (Indexed)

- · Register Indirect with Literal Offset

- 8-Bit Literal

- · 16-Bit Literal

Note:

Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

# 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- · Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- · Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

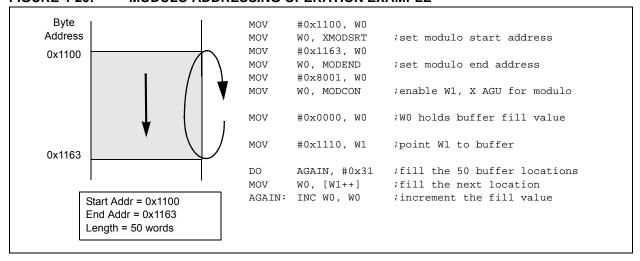

# 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

**Note:** Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

# 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

#### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0   | U-0                   | R/W-0                 | R/W-0 | U-0 | U-0 | U-0   |

|-------|-------|-----------------------|-----------------------|-------|-----|-----|-------|

|       |       | DMA0MD <sup>(1)</sup> |                       |       |     |     |       |

|       |       |                       | DMA1MD <sup>(1)</sup> | DTCMD |     |     |       |

| _     | _   _ | _   _                 | DMA2MD <sup>(1)</sup> | PTGMD | _   | _   | _     |

|       |       |                       | DMA3MD <sup>(1)</sup> |       |     |     |       |

| bit 7 |       |                       |                       |       |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 Unimplemented: Read as '0'

bit 4 **DMA0MD:** DMA0 Module Disable bit<sup>(1)</sup>

1 = DMA0 module is disabled 0 = DMA0 module is enabled

DMA1MD: DMA1 Module Disable bit(1)

1 = DMA1 module is disabled0 = DMA1 module is enabled

DMA2MD: DMA2 Module Disable bit(1)

1 = DMA2 module is disabled0 = DMA2 module is enabled

**DMA3MD:** DMA3 Module Disable bit<sup>(1)</sup>

1 = DMA3 module is disabled 0 = DMA3 module is enabled

bit 3 PTGMD: PTG Module Disable bit

1 = PTG module is disabled0 = PTG module is enabled

bit 2-0 **Unimplemented:** Read as '0'

Note 1: This single bit enables and disables all four DMA channels.

# REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------------|-------|-------|-------|

| _      |       |       |       | SCK2INR<6:0 | )>    |       |       |

| bit 15 |       |       |       |             |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | SDI2R<6:0> | •     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 SCK2INR<6:0>: Assign SPI2 Clock Input (SCK2) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

•

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 Unimplemented: Read as '0'

bit 6-0 SDI2R<6:0>: Assign SPI2 Data Input (SDI2) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

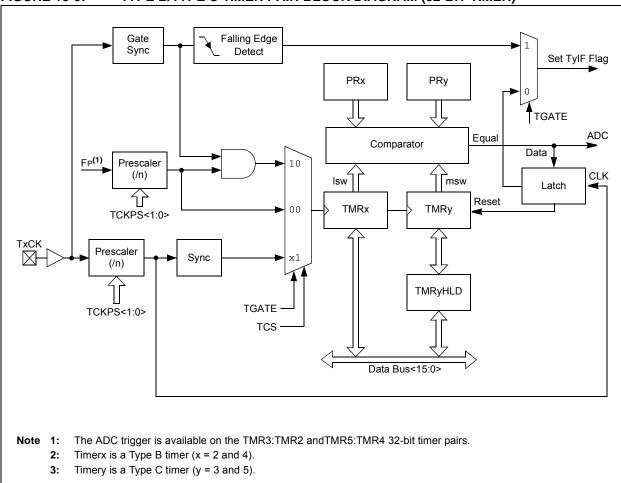

FIGURE 13-3: TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

# 13.1 Timerx/y Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/

wwwproducts/Devices.aspx?d

DocName=en555464

### 13.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

DS70000657H-page 274

# REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

bit 5 ABAUD: Auto-Baud Enable bit

1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion

0 = Baud rate measurement is disabled or completed

bit 4 URXINV: UARTx Receive Polarity Inversion bit

1 = UxRX Idle state is '0'

0 = UxRX Idle state is '1'

bit 3 BRGH: High Baud Rate Enable bit

1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)

0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)

bit 2-1 PDSEL<1:0>: Parity and Data Selection bits

11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity

bit 0 STSEL: Stop Bit Selection bit

1 = Two Stop bits 0 = One Stop bit

**Note 1:** Refer to the "**UART**" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.

2: This feature is only available for the 16x BRG mode (BRGH = 0).

3: This feature is only available on 44-pin and 64-pin devices.

4: This feature is only available on 64-pin devices.

# REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER(1)

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | PTGAD | J<15:8> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------|-------|-------|-------|

|       |       |       | PTGAE | )J<7:0> |       |       |       |

| bit 7 |       |       |       |         |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **PTGADJ<15:0>:** PTG Adjust Register bits

This register holds user-supplied data to be added to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGADD command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 24-11: PTGL0: PTG LITERAL 0 REGISTER(1)

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | PTGL0 | <15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------|-------|-------|-------|-------|-------|-------|-------|

| PTGL0<7:0> |       |       |       |       |       |       |       |

| bit 7      |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **PTGL0<15:0>:** PTG Literal 0 Register bits

This register holds the 16-bit value to be written to the AD1CHS0 register with the PTGCTRL Step command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3)

| R/W-0  | R/W-0              | R/W-0 | U-0 | U-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|--------------------|-------|-----|-----|--------|-------|-------|

| CON    | COE <sup>(2)</sup> | CPOL  | _   | _   | OPMODE | CEVT  | COUT  |

| bit 15 |                    |       |     |     |        |       | bit 8 |

| R/W-0  | R/W-0  | U-0 | R/W-0               | U-0 | U-0 | R/W-0               | R/W-0               |

|--------|--------|-----|---------------------|-----|-----|---------------------|---------------------|

| EVPOL1 | EVPOL0 | _   | CREF <sup>(1)</sup> | _   | _   | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |

| bit 7  |        |     |                     |     |     |                     | bit 0               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CON: Op Amp/Comparator Enable bit

1 = Op amp/comparator is enabled

0 = Op amp/comparator is disabled

bit 14 **COE**: Comparator Output Enable bit<sup>(2)</sup>

1 = Comparator output is present on the CxOUT pin

0 = Comparator output is internal only

bit 13 **CPOL:** Comparator Output Polarity Select bit

1 = Comparator output is inverted

0 = Comparator output is not inverted

bit 12-11 Unimplemented: Read as '0'

bit 10 **OPMODE:** Op Amp/Comparator Operation Mode Select bit

1 = Circuit operates as an op amp

0 = Circuit operates as a comparator

bit 9 **CEVT:** Comparator Event bit

1 = Comparator event according to the EVPOL<1:0> settings occurred; disables future triggers and interrupts until the bit is cleared

0 = Comparator event did not occur

bit 8 **COUT**: Comparator Output bit

When CPOL = 0 (non-inverted polarity):

1 = VIN+ > VIN-

0 = VIN+ < VIN-

When CPOL = 1 (inverted polarity):

1 = VIN+ < VIN-

0 = VIN+ > VIN-

**Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

2: This output is not available when OPMODE (CMxCON<10>) = 1.

### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

bit 7-6 **EVPOL<1:0>:** Trigger/Event/Interrupt Polarity Select bits

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

Low-to-high transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

High-to-low transition of the comparator output.

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

Low-to-high transition of the comparator output

00 = Trigger/event/interrupt generation is disabled

- bit 5 **Unimplemented:** Read as '0'

- bit 4 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage(2)

- 0 = VIN+ input connects to CxIN1+ pin

- bit 3-2 **Unimplemented:** Read as '0'

- bit 1-0 CCH<1:0>: Op Amp/Comparator Channel Select bits<sup>(1)</sup>

- 11 = Unimplemented

- 10 = Unimplemented

- 01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup>

- 00 = Inverting input of the op amp/comparator connects to the CxIN1- pin

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                        | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|------------------------------------|---------------|-------------------------------|--------------------------|

| 72                 | SL                   | SL     | f               | f = Left Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG          | WREG = Left Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd           | Wd = Left Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Wb, Wns, Wnd    | Wnd = Left Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 73                 | SUB                  | SUB    | Acc(1)          | Subtract Accumulators              | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SUB    | f               | f = f – WREG                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | f,WREG          | WREG = f – WREG                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | #lit10,Wn       | Wn = Wn – lit10                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,#lit5,Wd     | Wd = Wb – lit5                     | 1             | 1                             | C,DC,N,OV,Z              |

| 74                 | SUBB                 | SUBB   | £               | $f = f - WREG - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | f,WREG          | WREG = $f - WREG - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 75                 | SUBR                 | SUBR   | f               | f = WREG – f                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | f,WREG          | WREG = WREG - f                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,Ws,Wd        | Wd = Ws - Wb                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                     | 1             | 1                             | C,DC,N,OV,Z              |

| 76                 | SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | f,WREG          | WREG = WREG – $f - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb, Ws, Wd      | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 77                 | SWAP                 | SWAP.b | Wn              | Wn = nibble swap Wn                | 1             | 1                             | None                     |

|                    |                      | SWAP   | Wn              | Wn = byte swap Wn                  | 1             | 1                             | None                     |

| 78                 | TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>        | 1             | 5                             | None                     |

| 79                 | TBLRDL               | TBLRDL | Ws,Wd           | Read Prog<15:0> to Wd              | 1             | 5                             | None                     |

| 80                 | TBLWTH               | TBLWTH | Ws,Wd           | Write Ws<7:0> to Prog<23:16>       | 1             | 2                             | None                     |

| 81                 | TBLWTL               | TBLWTL | Ws,Wd           | Write Ws to Prog<15:0>             | 1             | 2                             | None                     |

| 82                 | ULNK                 | ULNK   |                 | Unlink Frame Pointer               | 1             | 1                             | SFA                      |

| 83                 | XOR                  | XOR    | f               | f = f .XOR. WREG                   | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | f,WREG          | WREG = f.XOR. WREG                 | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | #lit10,Wn       | Wd = lit10 .XOR. Wd                | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd        | Wd = Wb .XOR. Ws                   | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd     | Wd = Wb .XOR. lit5                 | 1             | 1                             | N,Z                      |

| 84                 | ZE                   | ZE     | Ws, Wnd         | Wnd = Zero-extend Ws               | 1             | 1                             | C,Z,N                    |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

<sup>2:</sup> Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

#### 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>TM</sup> Object Linker/ MPLIB<sup>TM</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows®, Linux and Mac OS® X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

#### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# **TABLE 31-11: INTERNAL RC ACCURACY**

| .,           |                                    |                                                                                                                                                          |     |     |       |                                                              |                |  |  |

|--------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------------------------------------------------|----------------|--|--|

| AC CH        | ARACTERISTICS                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ |     |     |       |                                                              |                |  |  |

| Param<br>No. | Characteristic                     | Min                                                                                                                                                      | Тур | Max | Units | Conditions                                                   |                |  |  |

|              | LPRC @ 32.768 kHz <sup>(1,2)</sup> |                                                                                                                                                          |     |     |       |                                                              |                |  |  |

| HF21         | LPRC                               | -30                                                                                                                                                      | _   | +30 | %     | $-40^{\circ}\text{C} \le \text{Ta} \le +150^{\circ}\text{C}$ | VDD = 3.0-3.6V |  |  |

Note 1: Change of LPRC frequency as VDD changes.

<sup>2:</sup> LPRC accuracy impacts the Watchdog Timer Time-out Period (TWDT). See Section 27.5 "Watchdog Timer (WDT)" for more information.

# Revision E (April 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

TABLE A-4: MAJOR SECTION UPDATES

| Section Name                           | Update Description                                                                              |

|----------------------------------------|-------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers               | The following 512-Kbyte devices were added to the General Purpose Families table                |

| and Digital Signal                     | (see Table 1):                                                                                  |

| Controllers (up to 512-Kbyte Flash and | • PIC24EP512GP202                                                                               |

| 48-Kbyte SRAM) with High-              | • PIC24EP512GP204                                                                               |

| Speed PWM, Op amps, and                | • PIC24EP512GP206                                                                               |

| Advanced Analog"                       | • dsPIC33EP512GP502                                                                             |

|                                        | • dsPIC33EP512GP504                                                                             |

|                                        | • dsPIC33EP512GP506                                                                             |

|                                        | The following 512-Kbyte devices were added to the Motor Control Families table (see Table 2):   |

|                                        | • PIC24EP512MC202                                                                               |

|                                        | • PIC24EP512MC204                                                                               |

|                                        | • PIC24EP512MC206                                                                               |

|                                        | • dsPIC33EP512MC202                                                                             |

|                                        | • dsPIC33EP512MC204                                                                             |

|                                        | • dsPIC33EP512MC206                                                                             |

|                                        | • dsPIC33EP512MC502                                                                             |

|                                        | • dsPIC33EP512MC504                                                                             |

|                                        | • dsPIC33EP512MC506                                                                             |

|                                        | Certain Pin Diagrams were updated to include the new 512-Kbyte devices.                         |

| Section 4.0 "Memory                    | Added a Program Memory Map for the new 512-Kbyte devices (see Figure 4-4).                      |

| Organization"                          | Added a Data Memory Map for the new dsPIC 512-Kbyte devices (see Figure 4-11).                  |

|                                        | Added a Data Memory Map for the new PIC24 512-Kbyte devices (see Figure 4-16).                  |

| Section 7.0 "Interrupt Controller"     | Updated the VECNUM bits in the INTTREG register (see Register 7-7).                             |

| Section 11.0 "I/O Ports"               | Added tip 6 to Section 11.5 "I/O Helpful Tips".                                                 |

| Section 27.0 "Special Features"        | The following modifications were made to the Configuration Byte Register Map (see Table 27-1):  |

|                                        | Added the column Device Memory Size (Kbytes)                                                    |

|                                        | Removed Notes 1 through 4                                                                       |

|                                        | Added addresses for the new 512-Kbyte devices                                                   |

| Section 30.0 "Electrical               | Updated the Minimum value for Parameter DC10 (see Table 30-4).                                  |

| Characteristics"                       | Added Power-Down Current (lpd) parameters for the new 512-Kbyte devices (see Table 30-8).       |

|                                        | Updated the Minimum value for Parameter CM34 (see Table 30-53).                                 |

|                                        | Updated the Minimum and Maximum values and the Conditions for paramteer SY12 (see Table 30-22). |

# **INDEX**

| A                                                    | Timer1 External Clock Requirements         |      |

|------------------------------------------------------|--------------------------------------------|------|

| Absolute Maximum Ratings401                          | Timer2/Timer4 External Clock Requirements  |      |

| AC Characteristics413, 471                           | Timer3/Timer5 External Clock Requirements  | 419  |

| 10-Bit ADC Conversion Requirements                   | UARTx I/O Requirements                     | 454  |

| 12-Bit ADC Conversion Requirements                   | ADC                                        |      |

| ADC Module459                                        | Control Registers                          | 325  |

| ADC Module (10-Bit Mode)                             | Helpful Tips                               | 324  |

| ADC Module (10-Bit Mode)                             | Key Features                               | 321  |

| ,                                                    | Resources                                  | 324  |

| Capacitive Loading Requirements on                   | Arithmetic Logic Unit (ALU)                | 44   |

| Output Pins                                          | Assembler                                  |      |

| DMA Module Requirements                              | MPASM Assembler                            | 398  |

| ECANx I/O Requirements                               |                                            |      |

| External Clock 414                                   | В                                          |      |

| High-Speed PWMx Requirements422                      | Bit-Reversed Addressing                    | 115  |

| I/O Timing Requirements416                           | Example                                    |      |

| I2Cx Bus Data Requirements (Master Mode)451          | Implementation                             |      |

| I2Cx Bus Data Requirements (Slave Mode)453           | Sequence Table (16-Entry)                  |      |

| Input Capture x Requirements420                      | Block Diagrams                             |      |

| Internal FRC Accuracy415                             | Data Access from Program Space             |      |

| Internal LPRC Accuracy415                            | Address Generation                         | 117  |

| Internal RC Accuracy472                              | 16-Bit Timer1 Module                       |      |

| Load Conditions 413, 471                             |                                            |      |

| OCx/PWMx Mode Requirements421                        | ADC Conversion Clock Period                | 323  |

| Op Amp/Comparator Voltage Reference                  | ADC with Connection Options for ANx Pins   | 200  |

| Settling Time Specifications457                      | and Op Amps                                |      |

| Output Compare x Requirements421                     | Arbiter Architecture                       |      |

| PLL Clock415, 471                                    | BEMF Voltage Measurement Using ADC         |      |

| QEI External Clock Requirements                      | Boost Converter Implementation             |      |

| QEI Index Pulse Requirements425                      | CALL Stack Frame                           |      |

| Quadrature Decoder Requirements                      | Comparator (Module 4)                      |      |

| Reset, Watchdog Timer, Oscillator Start-up Timer,    | Connections for On-Chip Voltage Regulator  |      |

| Power-up Timer Requirements417                       | CPU Core                                   |      |

| SPI1 Master Mode (Full-Duplex, CKE = 0, CKP = x,     | CRC Module                                 |      |

| SMP = 1) Requirements                                | CRC Shift Engine                           |      |

| SPI1 Master Mode (Full-Duplex, CKE = 1, CKP = x,     | CTMU Module                                | 316  |

| SMP = 1) Requirements                                | Digital Filter Interconnect                |      |

| SPI1 Master Mode (Half-Duplex, Transmit Only)        | DMA Controller                             | 141  |

| Requirements439                                      | DMA Controller Module                      | 139  |

| SPI1 Maximum Data/Clock Rate Summary                 | dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/      | /50X |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,               | and PIC24EPXXXGP/MC20X                     | 25   |

| CKP = 0, SMP = 0) Requirements449                    | ECAN Module                                | 288  |

|                                                      | EDS Read Address Generation                | 105  |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,               | EDS Write Address Generation               | 106  |

| CKP = 1, SMP = 0) Requirements                       | Example of MCLR Pin Connections            | 30   |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,               | High-Speed PWMx Architectural Overview     | 227  |

| CKP = 0, SMP = 0) Requirements443                    | High-Speed PWMx Register Interconnection   |      |

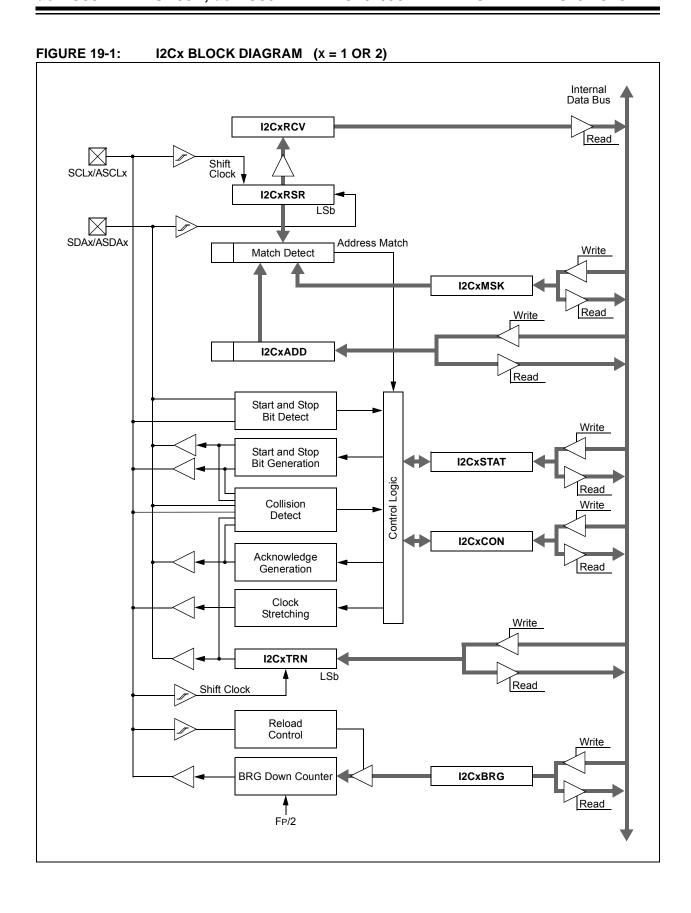

| SPI1 Slave Mode (Full-Duplex, CKE = 1,               | I2Cx Module                                |      |

| CKP = 1, SMP = 0) Requirements445                    | Input Capture x                            |      |

| SPI2 Master Mode (Full-Duplex, CKE = 0, CKP = x, SMP | Interleaved PFC                            |      |

| = 1) Requirements429                                 | Multiphase Synchronous Buck Converter      |      |

| SPI2 Master Mode (Full-Duplex, CKE = 1,              | Multiplexing Remappable Output for RPn     |      |

| CKP = x, SMP = 1) Requirements 428                   | Op Amp Configuration A                     |      |

| SPI2 Master Mode (Half-Duplex, Transmit Only)        | Op Amp Configuration B                     |      |

| Requirements427                                      | Op Amp/Comparator Voltage Reference Module |      |

| SPI2 Maximum Data/Clock Rate Summary 426             | Op Amp/Comparator x (Modules 1, 2, 3)      |      |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,               | Oscillator System                          |      |

| CKP = 0, SMP = 0) Requirements437                    |                                            |      |

| SPI2 Slave Mode (Full-Duplex, CKE = 0, CKP = 1, SMP  | Output Compare x Module<br>PLL             |      |

| = 0) Requirements435                                 |                                            |      |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,               | Programmer's Model                         |      |

| CKP = 0, SMP = 0) Requirements431                    | PTG Module                                 |      |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,               | Quadrature Encoder Interface               |      |

| CKP = 1, SMP = 0) Requirements433                    | Recommended Minimum Connection             | 30   |

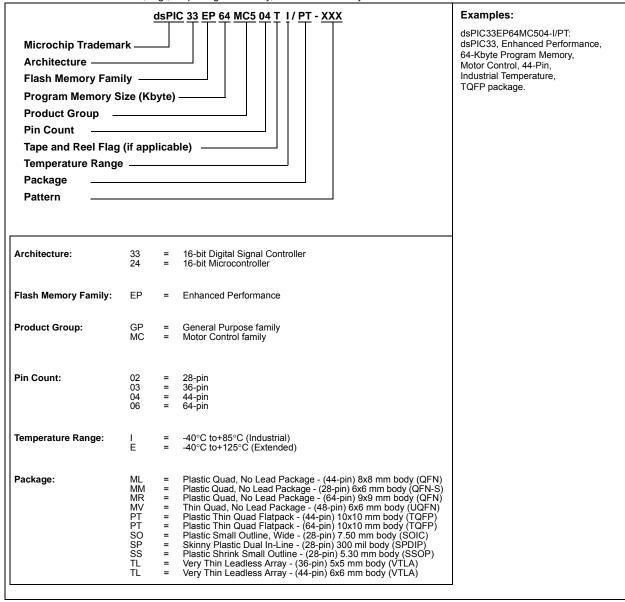

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.