Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp504-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

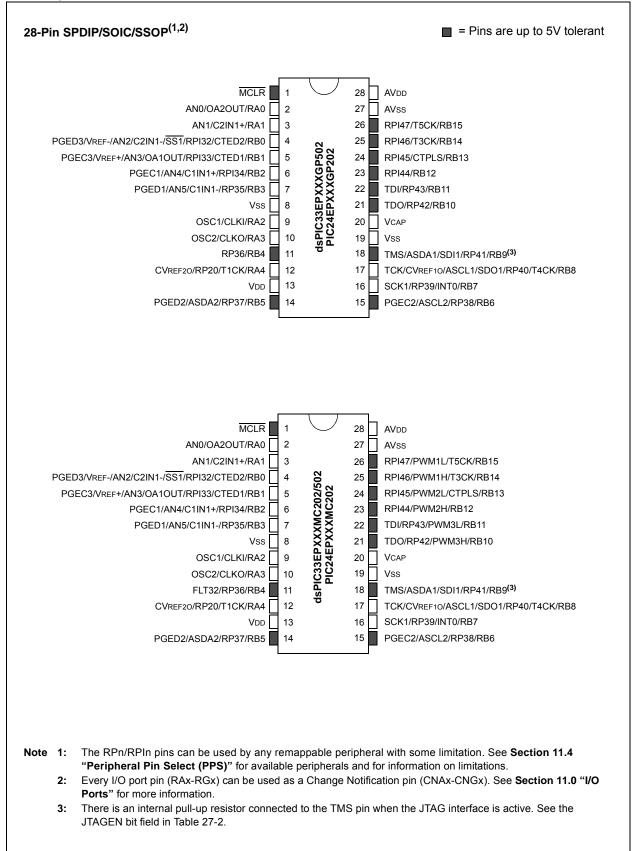

#### **Pin Diagrams**

| File Name  | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8                         | Bit 7                        | Bit 6    | Bit 5  | Bit 4  | Bit 3              | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|-----------|--------|--------|--------|--------|----------|-------------------------------|------------------------------|----------|--------|--------|--------------------|--------|--------|--------|---------------|

|            | 0400-<br>041E |        |           |        |        |        |        |          | See defini                    | ion when W                   | 'IN = x  |        |        |                    |        |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BF      | P<3:0> |        |        | F2BI   | ><3:0>   |                               |                              | F1BP     | <3:0>  |        |                    | F0BP   | <3:0>  |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BF      | ><3:0> |        |        | F6BI   | ><3:0>   |                               |                              | F5BP     | <3:0>  |        |                    | F4BP   | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11B      | P<3:0> |        |        | F10B   | P<3:0>   |                               |                              | F9BP     | <3:0>  |        |                    | F8BP   | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15B      | P<3:0> |        |        | F14B   | P<3:0>   |                               |                              | F13B     | D<3:0> |        |                    | F12BF  | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |        | SID<10:3> |        |        |        |        |          | SID<2:0>                      |                              | _        | MIDE   | _      | EID<               | 17:16> | xxxx   |        |               |

| C1RXM0EID  | 0432          |        |           |        | EID<   | :15:8> |        |          |                               |                              |          |        | EID<   | 7:0>               |        |        |        | xxxx          |

| C1RXM1SID  | 0434          |        |           |        | SID<   | :10:3> |        |          |                               | SID<2:0> —                   |          |        |        | MIDE               | —      | EID<   | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |        | EID<15:8> |        |        |        |        |          |                               |                              |          |        | EID<   | 7:0>               |        |        |        | xxxx          |

| C1RXM2SID  | 0438          |        | SID<10:3> |        |        |        |        |          |                               | SID<2:0>                     |          | —      | MIDE   | —                  | EID<   | 17:16> | xxxx   |               |

| C1RXM2EID  | 043A          |        | EID<15:8> |        |        |        |        | EID<7:0> |                               |                              |          |        |        | xxxx               |        |        |        |               |

| C1RXF0SID  | 0440          |        | SID<10:3> |        |        |        |        |          | SID<2:0>                      |                              | —        | EXIDE  | —      | EID<               | 17:16> | xxxx   |        |               |

| C1RXF0EID  | 0442          |        | EID<15:8> |        |        |        |        | EID<7:0> |                               |                              |          |        |        | -                  |        | xxxx   |        |               |

| C1RXF1SID  | 0444          |        | SID<10:3> |        |        |        |        |          |                               | SID<2:0>                     |          | _      | EXIDE  | —                  | EID<   | 17:16> | xxxx   |               |

| C1RXF1EID  | 0446          |        | EID<15:8> |        |        |        |        |          |                               |                              | EID<     | 7:0>   |        |                    |        | xxxx   |        |               |

| C1RXF2SID  | 0448          |        |           |        | SID<   | :10:3> |        |          |                               |                              | SID<2:0> |        | —      | EXIDE              | —      | EID<   | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |        |           |        | EID<   | :15:8> |        |          |                               |                              |          |        | EID<   | 7:0>               |        |        |        | xxxx          |

| C1RXF3SID  | 044C          |        |           |        | SID<   | :10:3> |        |          |                               |                              | SID<2:0> |        | —      | EXIDE              | —      | EID<   | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |        |           |        | EID<   | :15:8> |        |          |                               | EID<7:0>                     |          |        |        |                    |        | xxxx   |        |               |

| C1RXF4SID  | 0450          |        |           |        | SID<   | :10:3> |        |          |                               |                              | SID<2:0> |        | —      | EXIDE — EID<17:16> |        |        | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |        |           |        | EID<   | :15:8> |        |          |                               | EID<7:0>                     |          |        |        |                    |        | xxxx   |        |               |

| C1RXF5SID  | 0454          |        |           |        | SID<   | :10:3> |        |          |                               | SID<2:0> — EXIDE — EID<17:16 |          |        |        |                    |        | 17:16> | xxxx   |               |

| C1RXF5EID  | 0456          |        |           |        | EID<   | :15:8> |        |          |                               | EID<7:0>                     |          |        |        |                    |        |        |        | xxxx          |

| C1RXF6SID  | 0458          |        |           |        | SID<   | :10:3> |        |          |                               |                              | SID<2:0> |        | —      | EXIDE              | —      | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |           |        | EID<   | :15:8> |        |          |                               |                              |          |        | EID<   | 7:0>               |        |        |        | xxxx          |

| C1RXF7SID  | 045C          |        |           |        | SID<   | :10:3> |        |          |                               |                              | SID<2:0> |        | —      | EXIDE              | —      | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |           |        | EID<   | :15:8> |        |          |                               | EID<7:0>                     |          |        |        |                    |        | xxxx   |        |               |

| C1RXF8SID  | 0460          |        | SID<10:3> |        |        |        |        |          | SID<2:0> — EXIDE — EID<17:1   |                              |          |        |        | 17:16>             | xxxx   |        |        |               |

| C1RXF8EID  | 0462          |        | EID<15:8> |        |        |        |        |          | EID<7:0>                      |                              |          |        |        |                    |        | xxxx   |        |               |

| C1RXF9SID  | 0464          |        | SID<10:3> |        |        |        |        |          | SID<2:0> — EXIDE — EID<17:16> |                              |          |        |        |                    | 17:16> | xxxx   |        |               |

| C1RXF9EID  | 0466          |        | EID<15:8> |        |        |        |        |          | EID<7:0>                      |                              |          |        |        |                    | xxxx   |        |        |               |

| C1RXF10SID | 0468          |        | SID<10:3> |        |        |        |        |          | SID<2:0> — EXIDE — EID<17:    |                              |          |        | 17:16> | xxxx               |        |        |        |               |

| C1RXF10EID | 046A          |        | EID<15:8> |        |        |        |        |          |                               |                              |          | EID<   | -      |                    |        |        | xxxx   |               |

| C1RXF11SID | 046C          |        | SID<10:3> |        |        |        |        |          |                               |                              | SID<2:0> |        | —      | EXIDE              | -      | EID<   | 17:16> | xxxx          |

#### TABLE 4-23: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-46: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|---------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      |        | TRISA12 | TRISA11 | TRISA10 | TRISA9 | TRISA8 | TRISA7 | _     |       | TRISA4 | _     |       | TRISA1 | TRISA0 | 1F93          |

| PORTA        | 0E02  | _      | _      | -      | RA12    | RA11    | RA10    | RA9    | RA8    | RA7    | _     |       | RA4    | _     | -     | RA1    | RA0    | 0000          |

| LATA         | 0E04  |        | _      | _      | LATA12  | LATA11  | LATA10  | LATA9  | LATA8  | LATA7  |       | _     | LATA4  |       | _     | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  |        | _      | _      | ODCA12  | ODCA11  | ODCA10  | ODCA9  | ODCA8  | ODCA7  |       | _     | ODCA4  |       | _     | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  |        | _      | _      | CNIEA12 | CNIEA11 | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 |       | _     | CNIEA4 |       | _     | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  |        | _      | _      | CNPUA12 | CNPUA11 | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 |       | _     | CNPUA4 |       | _     | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  |        | _      | _      | CNPDA12 | CNPDA11 | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 |       | _     | CNPDA4 |       | _     | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | _      | _      | ANSA12  | ANSA11  |         | _      | -      | _      | _     | _     | ANSA4  | _     | _     | ANSA1  | ANSA0  | 1813          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-47: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | —       | _       | -       | _       | _      | ANSB8  | -      | _      | -      | -      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-48: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|--------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | TRISC15 | _      | TRISC13 | TRISC12 | TRISC11 | TRISC10 | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | BFFF          |

| PORTC        | 0E22  | RC15    | _      | RC13    | RC12    | RC11    | RC10    | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | LATC15  | _      | LATC13  | LATC12  | LATC11  | LATC10  | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | ODCC15  | -      | ODCC13  | ODCC12  | ODCC11  | ODCC10  | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | CNIEC15 | —      | CNIEC13 | CNIEC12 | CNIEC11 | CNIEC10 | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | CNPUC15 | —      | CNPUC13 | CNPUC12 | CNPUC11 | CNPUC10 | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | CNPDC15 | —      | CNPDC13 | CNPDC12 | CNPDC11 | CNPDC10 | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | _       | _      | _       | _       | ANSC11  | _       | _      | _      | _      | _      | _      | _      | _      | ANSC2  | ANSC1  | ANSC0  | 0807          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

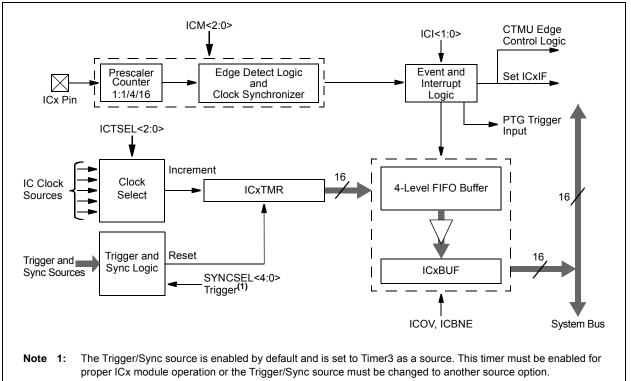

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

| U-0              | R/W-0                                               | R/W-0                              | R/W-0           | R/W-0                       | R/W-0                          | R/W-0                | R/W-0           |  |  |  |  |  |

|------------------|-----------------------------------------------------|------------------------------------|-----------------|-----------------------------|--------------------------------|----------------------|-----------------|--|--|--|--|--|

| _                | CLSRC4                                              | CLSRC3                             | CLSRC2          | CLSRC1                      | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |  |

| bit 15           |                                                     |                                    | •               |                             |                                |                      | bit 8           |  |  |  |  |  |

|                  | <b>D</b> 4 4                                        | D 0.01 4                           | <b>D</b> 444    |                             | DAMA                           | DAMA                 | <b>D</b> 444.0  |  |  |  |  |  |

| R/W-1            | R/W-1                                               | R/W-1                              | R/W-1           | R/W-1                       | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3                                             | FLTSRC2                            | FLTSRC1         | FLTSRC0                     | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |  |  |

|                  |                                                     |                                    |                 |                             |                                |                      | DI              |  |  |  |  |  |

| Legend:          |                                                     |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

| R = Readable     | bit                                                 | W = Writable                       | bit             | U = Unimpler                | mented bit, read               | l as '0'             |                 |  |  |  |  |  |

| -n = Value at I  | POR                                                 | '1' = Bit is set                   |                 | '0' = Bit is cle            | ared                           | x = Bit is unkr      | nown            |  |  |  |  |  |

|                  |                                                     |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

| bit 15           | Unimplemen                                          | ted: Read as '                     | 0'              |                             |                                |                      |                 |  |  |  |  |  |

| bit 14-10        | CLSRC<4:0>                                          | Current-Limit                      | Control Signa   | al Source Selec             | ct for PWM Ger                 | nerator # bits       |                 |  |  |  |  |  |

|                  | 11111 = Fault 32                                    |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 11110 = Reserved                                    |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | •                                                   |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | •                                                   |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | •<br>01100 = Reserved                               |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 01011 = Comparator 4                                |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  |                                                     | Amp/Comparat                       | or 3            |                             |                                |                      |                 |  |  |  |  |  |

|                  | •                                                   | Amp/Comparat                       |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  |                                                     | Amp/Comparat                       |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 00111 = Res                                         |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 00110 <b>= Res</b>                                  | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 00101 = Res                                         | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 00100 <b>= Res</b>                                  | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 00011 <b>= Fau</b>                                  |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 00010 <b>= Fau</b>                                  |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 00001 <b>= Fau</b>                                  |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 00000 <b>= Fau</b>                                  | ( <i>)</i>                         |                 |                             | ~                              |                      |                 |  |  |  |  |  |

| bit 9            | CLPOL: Curr                                         | ent-Limit Polar                    | ity for PWM G   | enerator # bit <sup>(</sup> | 2)                             |                      |                 |  |  |  |  |  |

|                  | 1 = The selected current-limit source is active-low |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | 0 = The selec                                       | cted current-lim                   | it source is ac | tive-high                   |                                |                      |                 |  |  |  |  |  |

| bit 8            | CLMOD: Cur                                          | rent-Limit Mode                    | e Enable for P  | WM Generator                | r # bit                        |                      |                 |  |  |  |  |  |

|                  |                                                     | imit mode is er<br>imit mode is di |                 |                             |                                |                      |                 |  |  |  |  |  |

|                  | ne PWMLOCK                                          |                                    |                 | <6>) is a '1', th           | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |  |  |

| the              | unlock sequen                                       | ce has been ex                     | ecuted.         |                             |                                |                      |                 |  |  |  |  |  |

|                  |                                                     |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |

# REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

- bit 7-3 FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator # bits 11111 = Fault 32 (default) 11110 = Reserved . . 01100 = Reserved 01011 = Comparator 4 01010 = Op Amp/Comparator 3

- 01001 = Op Amp/Comparator 2

- 01000 = Op Amp/Comparator 1

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = Reserved

- 00011 = Fault 4

- 00010 = Fault 3

- 00001 = Fault 2 00000 = Fault 1

- bit 2 ELTROL Fault Delarity for DWM Concrete

# bit 2 **FLTPOL:** Fault Polarity for PWM Generator # bit<sup>(2)</sup>

- 1 = The selected Fault source is active-low

- 0 = The selected Fault source is active-high

- bit 1-0 FLTMOD<1:0>: Fault Mode for PWM Generator # bits

- 11 = Fault input is disabled

- 10 = Reserved

- 01 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (cycle)

- 00 = The selected Fault source forces PWMxH, PWMxL pins to FLTDAT values (latched condition)

- **Note 1:** If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

- **2:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

### 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R-0, HSC                          | R-0, HSC  | U-0             | U-0         | U-0               | R/C-0, HS        | R-0, HSC              | R-0, HSC |  |  |

|-----------------------------------|-----------|-----------------|-------------|-------------------|------------------|-----------------------|----------|--|--|

| ACKSTAT                           | TRSTAT    | _               |             |                   | BCL              | GCSTAT                | ADD10    |  |  |

| bit 15                            |           |                 |             |                   |                  |                       | bit 8    |  |  |

|                                   |           |                 |             |                   |                  |                       |          |  |  |

| R/C-0, HS                         | R/C-0, HS | R-0, HSC        | R/C-0, HSC  | R/C-0, HSC        | R-0, HSC         | R-0, HSC              | R-0, HSC |  |  |

| IWCOL                             | I2COV     | D_A             | Р           | S                 | R_W              | RBF                   | TBF      |  |  |

| bit 7                             |           |                 |             |                   |                  |                       | bit 0    |  |  |

|                                   |           |                 |             |                   |                  |                       |          |  |  |

| Legend: C = Clearable bit         |           |                 | HS = Hardwa | re Settable bit   | HSC = Hardware S | ettable/Clearable bit |          |  |  |

| R = Readable bit W = Writable bit |           |                 | e bit       | U = Unimplem      | nented bit, read | as '0'                |          |  |  |

| -n = Value at POR                 |           | '1' = Bit is se | et          | '0' = Bit is clea | ared             | x = Bit is unknown    |          |  |  |

### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

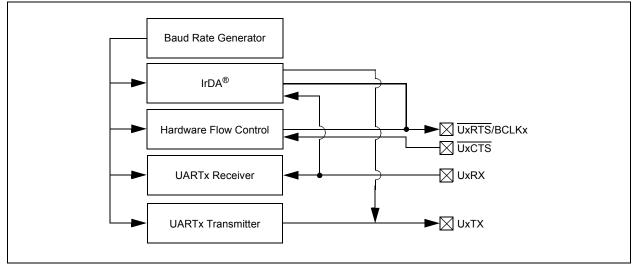

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

#### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 24.4 Step Commands and Format

#### TABLE 24-1: PTG STEP COMMAND FORMAT

| Step Command Byte: |             |             |  |  |  |  |  |

|--------------------|-------------|-------------|--|--|--|--|--|

|                    | STEPx<7:0>  |             |  |  |  |  |  |

| CMD<3:0>           |             | OPTION<3:0> |  |  |  |  |  |

| bit 7              | bit 4 bit 3 | bit 0       |  |  |  |  |  |

| bit 7-4 | CMD<3:0> | Step<br>Command | Command Description                                                                                                                                                                      |

|---------|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0000     | PTGCTRL         | Execute control command as described by OPTION<3:0>.                                                                                                                                     |

|         | 0001     | PTGADD          | Add contents of PTGADJ register to target register as described by<br>OPTION<3:0>.                                                                                                       |

|         |          | PTGCOPY         | Copy contents of PTGHOLD register to target register as described by<br>OPTION<3:0>.                                                                                                     |

|         | 001x     | PTGSTRB         | Copy the value contained in CMD<0>:OPTION<3:0> to the CH0SA<4:0> bits (AD1CHS0<4:0>).                                                                                                    |

|         | 0100     | PTGWHI          | Wait for a low-to-high edge input from the selected PTG trigger input as described by OPTION<3:0>.                                                                                       |

|         | 0101     | PTGWLO          | Wait for a high-to-low edge input from the selected PTG trigger input as described by OPTION<3:0>.                                                                                       |

|         | 0110     | Reserved        | Reserved.                                                                                                                                                                                |

|         | 0111     | PTGIRQ          | Generate individual interrupt request as described by OPTION3<:0>.                                                                                                                       |

|         | 100x     | PTGTRIG         | Generate individual trigger output as described by < <cmd<0>:OPTION&lt;3:0&gt;&gt;.</cmd<0>                                                                                              |

|         | 101x     | PTGJMP          | Copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR) and jump to that Step queue.</cmd<0>                                                          |

|         | 110x     | PTGJMPC0        | PTGC0 = PTGC0LIM: Increment the Queue Pointer (PTGQPTR).                                                                                                                                 |

|         |          |                 | $PTGC0 \neq PTGC0LIM$ : Increment Counter 0 (PTGC0) and copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR), and jump to that Step queue</cmd<0>  |

|         | 111x     | PTGJMPC1        | PTGC1 = PTGC1LIM: Increment the Queue Pointer (PTGQPTR).                                                                                                                                 |

|         |          |                 | $PTGC1 \neq PTGC1LIM$ : Increment Counter 1 (PTGC1) and copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR), and jump to that Step queue.</cmd<0> |

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | —   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

|        |     |     |     |          |          |          |          |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

# bit 15-12 Unimplemented: Read as '0'

| DIL 10-12 | Uninpienienieu. Reau as 0                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                         |

|           | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

|           | 1110 <b>= FLT2</b>                                                                                                                                                                                                                             |

|           | 1101 <b>= PTGO19</b>                                                                                                                                                                                                                           |

|           | 1100 = PTGO18                                                                                                                                                                                                                                  |

|           | 1011 = Reserved                                                                                                                                                                                                                                |

|           | 1010 = Reserved                                                                                                                                                                                                                                |

|           | 1001 = Reserved                                                                                                                                                                                                                                |

|           | 1000 = Reserved                                                                                                                                                                                                                                |

|           | 0111 = Reserved                                                                                                                                                                                                                                |

|           | 0110 = Reserved                                                                                                                                                                                                                                |

|           | 0101 = PWM3H                                                                                                                                                                                                                                   |

|           | 0100 = PWM3L                                                                                                                                                                                                                                   |

|           | 0011 = PWM2H                                                                                                                                                                                                                                   |

|           | 0010 = PWM2L                                                                                                                                                                                                                                   |

|           | 0001 = PWM1H                                                                                                                                                                                                                                   |

|           | 0000 = PWM1L                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                         |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits 1111 = FLT4                                                                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2                                                                                                                                                                                                                     |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19                                                                                                                                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18                                                                                                                                                                                   |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved                                                                                                                                                                |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                          |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                       |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved                                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

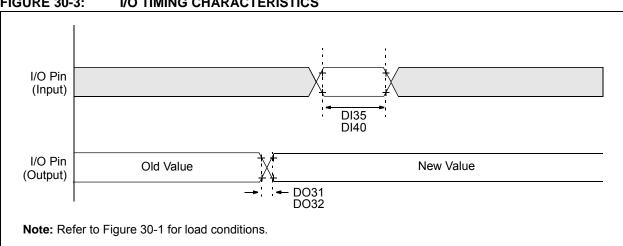

#### **FIGURE 30-3: I/O TIMING CHARACTERISTICS**

#### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature } -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |            |

|--------------------|--------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                    | Min.                                                                                                                                                                                                                                                                             | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DO31               | TioR   | Port Output Rise Time             |                                                                                                                                                                                                                                                                                  | 5                   | 10   | ns    |            |

| DO32               | TIOF   | Port Output Fall Time             | _                                                                                                                                                                                                                                                                                | 5                   | 10   | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                                                                                                                                                                                                                                               | —                   | _    | ns    |            |

| DI40               | Trbp   | CNx High or Low Time (input)      | 2                                                                                                                                                                                                                                                                                | _                   | _    | Тсү   |            |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

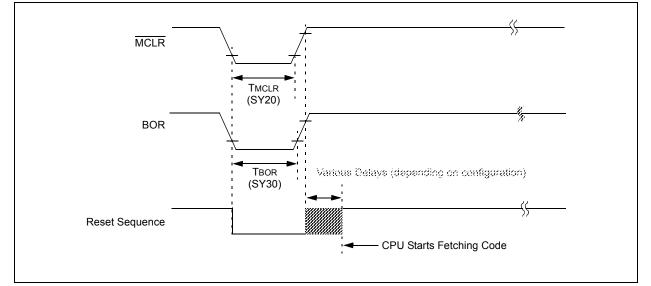

#### FIGURE 30-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

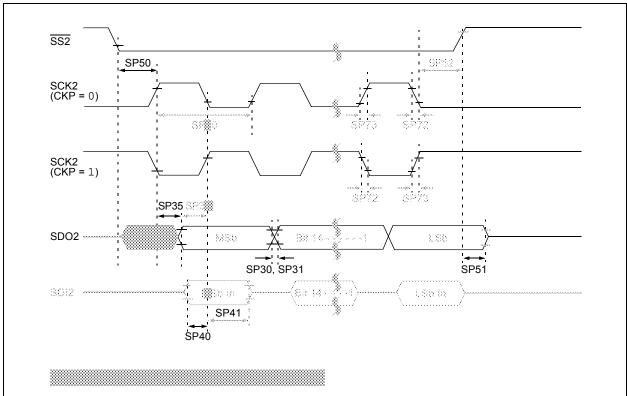

#### FIGURE 30-20: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-45:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | Standard Op<br>(unless othe<br>Operating ter | rwise st                            | <b>ated)</b><br>e -40°C ⊴ | ≤ Ta ≤ +8  | <b>o 3.6V</b><br>35°C for Industrial<br>125°C for Extended |

|--------------------|-----------------------|----------------------------------------------|----------------------------------------------|-------------------------------------|---------------------------|------------|------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                         | Min. Typ. <sup>(2)</sup> Max. Units |                           | Conditions |                                                            |

| SP70               | FscP                  | Maximum SCK1 Input<br>Frequency              | _                                            |                                     | Lesser of FP or 15        | MHz        | (Note 3)                                                   |

| SP72               | TscF                  | SCK1 Input Fall Time                         | —                                            |                                     |                           | ns         | See Parameter DO32<br>(Note 4)                             |

| SP73               | TscR                  | SCK1 Input Rise Time                         | —                                            |                                     | —                         | ns         | See Parameter DO31<br>(Note 4)                             |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | —                                            |                                     | _                         | ns         | See Parameter DO32<br>(Note 4)                             |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                            |                                     | —                         | ns         | See Parameter DO31<br>(Note 4)                             |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                            | 6                                   | 20                        | ns         |                                                            |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                           |                                     | _                         | ns         |                                                            |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                           |                                     |                           | ns         |                                                            |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                           |                                     | —                         | ns         |                                                            |

| SP50               | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                          |                                     | —                         | ns         |                                                            |

| SP51               | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                           | _                                   | 50                        | ns         | (Note 4)                                                   |

| SP52               | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                        | 1.5 Tcy + 40                                 | _                                   | _                         | ns         | (Note 4)                                                   |

| SP60               | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge     | —                                            |                                     | 50                        | ns         |                                                            |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

# 36-Terminal Very Thin Thermal Leadless Array Package (TL) – 5x5x0.9 mm Body with Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | N   | MILLIMETERS    |          |       |  |

|-------------------------|-----|----------------|----------|-------|--|

| Dimension               | MIN | NOM            | MAX      |       |  |

| Number of Pins          | Ν   |                | 36       |       |  |

| Number of Pins per Side | ND  |                | 10       |       |  |

| Number of Pins per Side | NE  |                | 8        |       |  |

| Pitch                   | е   | 0.50 BSC       |          |       |  |

| Overall Height          | Α   | 0.80           | 0.90     | 1.00  |  |

| Standoff                | A1  | 0.025          | -        | 0.075 |  |

| Overall Width           | E   |                | 5.00 BSC |       |  |

| Exposed Pad Width       | E2  | 3.60 3.75 3.90 |          |       |  |

| Overall Length          | D   | 5.00 BSC       |          |       |  |

| Exposed Pad Length      | D2  | 3.60           | 3.75     | 3.90  |  |

| Contact Width           | b   | 0.20           | 0.25     | 0.30  |  |

| Contact Length L        |     | 0.20           | 0.25     | 0.30  |  |

| Contact-to-Exposed Pad  | К   | 0.20           | -        | -     |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-187C Sheet 2 of 2

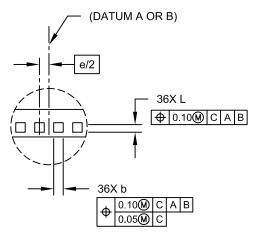

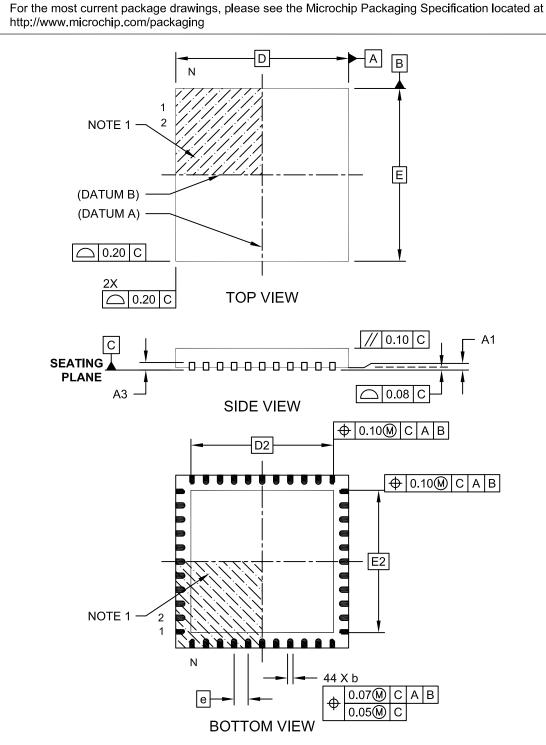

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

Note:

Microchip Technology Drawing C04-103C Sheet 1 of 2

48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | N                | MILLIMETERS |          |      |  |

|------------------------|------------------|-------------|----------|------|--|

| Dimension              | Dimension Limits |             |          | MAX  |  |

| Number of Pins         | N                |             | 48       |      |  |

| Pitch                  | е                |             | 0.40 BSC |      |  |

| Overall Height         | Α                | 0.45        | 0.50     | 0.55 |  |

| Standoff               | A1               | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3 0.127 REF     |             |          |      |  |

| Overall Width          | E 6.00 BSC       |             |          |      |  |

| Exposed Pad Width      | E2               | 4.45        | 4.60     | 4.75 |  |

| Overall Length         | D                | 6.00 BSC    |          |      |  |

| Exposed Pad Length     | D2               | 4.45        | 4.60     | 4.75 |  |

| Contact Width          | b                | 0.15        | 0.20     | 0.25 |  |

| Contact Length         |                  | 0.30        | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K                | 0.20        | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2

## **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources". All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.

All other major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>256-Kbyte Flash and<br>32-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | The content on the first page of this section was extensively reworked to provide the reader with the key features and functionality of this device family in an "at-a-glance" format.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 1.0 "Device<br>Overview"                                                                                                                                        | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X Block Diagram (see Figure 1-1), which now contains a CPU<br>block and a reference to the CPU diagram.<br>Updated the description and Note references in the Pinout I/O Descriptions for these                                                                                                                                                                                                                                                                                                                                                              |

| Section 2.0 "Guidelines for<br>Getting Started with 16-bit<br>Digital Signal Controllers<br>and Microcontrollers"                                                       | pins: C1IN2-, C2IN2-, C3IN2-, OA1OUT, OA2OUT, and OA3OUT (see Table 1-1).<br>Updated the Recommended Minimum Connection diagram (see Figure 2-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |