Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 48-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp504-i-mv |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

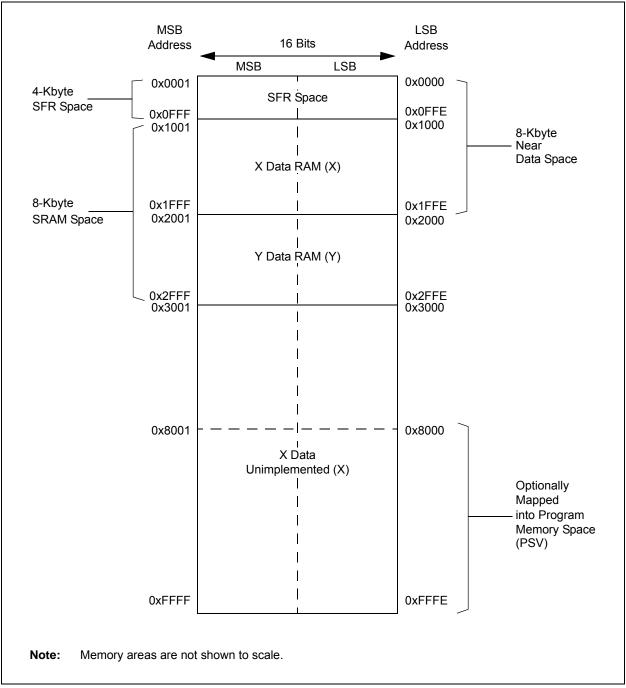

## FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

#### 4.4.1 PAGED MEMORY SCHEME

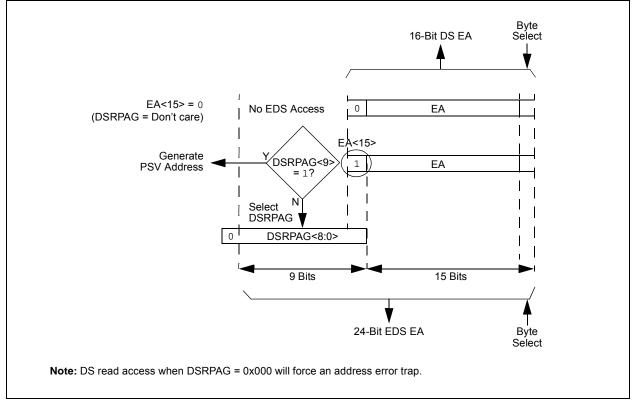

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

|                                                     | Vector  | IRQ        |                   | Interrupt Bit Location |          |              |  |

|-----------------------------------------------------|---------|------------|-------------------|------------------------|----------|--------------|--|

| Interrupt Source                                    | # #     |            | IVT Address       | Flag                   | Enable   | Priority     |  |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10>               | IEC3<10> | IPC14<10:8>  |  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _                      | _        | _            |  |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>                | IEC4<1>  | IPC16<6:4>   |  |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>                | IEC4<2>  | IPC16<10:8>  |  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>                | IEC4<3>  | IPC16<14:12> |  |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —                      | _        | —            |  |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>                | IEC4<6>  | IPC17<10:8>  |  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —                      | _        | —            |  |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13>               | IEC4<13> | IPC19<6:4>   |  |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —                      | _        | —            |  |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14>               | IEC5<14> | IPC23<10:8>  |  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15>               | IEC5<15> | IPC23<14:12> |  |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>                | IEC6<0>  | IPC24<2:0>   |  |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —                      | _        | —            |  |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14>               | IEC8<14> | IPC35<10:8>  |  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15>               | IEC8<15> | IPC35<14:12> |  |

| Reserved                                            | 152     | 144        | 0x000134          | —                      | —        | _            |  |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>                | IEC9<1>  | IPC36<6:4>   |  |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>                | IEC9<2>  | IPC36<10:8>  |  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>                | IEC9<3>  | IPC36<14:12> |  |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>                | IEC9<4>  | IPC37<2:0>   |  |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>                | IEC9<5>  | IPC37<6:4>   |  |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>                | IEC9<6>  | IPC37<10:8>  |  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —                      | —        | _            |  |

|                                                     | Lowe    | est Natura | I Order Priority  |                        |          |              |  |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

#### 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

## EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

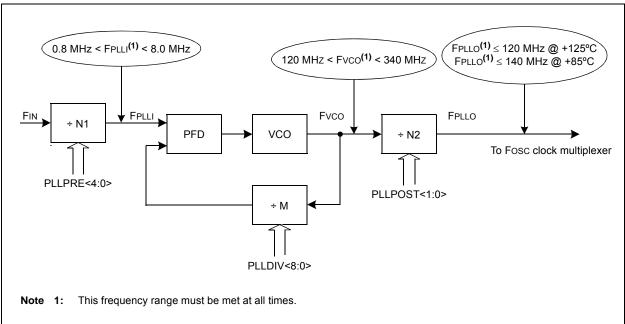

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

#### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

#### FIGURE 9-2: PLL BLOCK DIAGRAM

| R/W-0           | R/W-0                                                                                                | R/W-1                             | R/W-1                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|------------------------|--------------------|-----------------|-----------|--|--|--|

| ROI             | DOZE2 <sup>(1)</sup>                                                                                 | DOZE1 <sup>(1)</sup>              | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2            | FRCDIV1         | FRCDIV0   |  |  |  |

| bit 15          |                                                                                                      |                                   | •                    |                        |                    |                 | bit 8     |  |  |  |

|                 |                                                                                                      |                                   |                      |                        |                    |                 |           |  |  |  |

| R/W-0           | R/W-1                                                                                                | U-0                               | R/W-0                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |

| PLLPOST1        | PLLPOST0                                                                                             | —                                 | PLLPRE4              | PLLPRE3                | PLLPRE2            | PLLPRE1         | PLLPRE0   |  |  |  |

| bit 7           |                                                                                                      |                                   |                      |                        |                    |                 | bit (     |  |  |  |

|                 |                                                                                                      |                                   |                      |                        |                    |                 |           |  |  |  |

| Legend:         |                                                                                                      |                                   |                      |                        |                    |                 |           |  |  |  |

| R = Readable    |                                                                                                      | W = Writable                      |                      | -                      | nented bit, read   |                 |           |  |  |  |

| -n = Value at F | POR                                                                                                  | '1' = Bit is set                  |                      | '0' = Bit is cle       | ared               | x = Bit is unkr | nown      |  |  |  |

| h:+ 45          |                                                                                                      | on Interview h                    |                      |                        |                    |                 |           |  |  |  |

| bit 15          |                                                                                                      | on Interrupt bis will clear the l |                      |                        |                    |                 |           |  |  |  |

|                 |                                                                                                      | s have no effect                  |                      | EN bit                 |                    |                 |           |  |  |  |

| bit 14-12       | •                                                                                                    | Processor Clo                     |                      |                        |                    |                 |           |  |  |  |

|                 | 111 = Fcy div                                                                                        |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 110 = Fcy div                                                                                        | vided by 64                       |                      |                        |                    |                 |           |  |  |  |

|                 | 101 = Fcy divided by 32                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 100 = Fcy divided by 16                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 011 = Fcy divided by 8 (default)<br>010 = Fcy divided by 4                                           |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 001 = Fcy divided by 2                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 000 = Fcy div                                                                                        | •                                 |                      |                        |                    |                 |           |  |  |  |

| bit 11          |                                                                                                      | e Mode Enable                     |                      |                        |                    |                 |           |  |  |  |

|                 |                                                                                                      |                                   |                      |                        | pheral clocks a    | nd the process  | or clocks |  |  |  |

|                 |                                                                                                      | -                                 | -                    | ratio is forced to     |                    |                 |           |  |  |  |

| bit 10-8        | FRCDIV<2:0>: Internal Fast RC Oscillator Postscaler bits                                             |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 111 = FRC divided by 256<br>110 = FRC divided by 64                                                  |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 100 = FRC divided by 64<br>101 = FRC divided by 32                                                   |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 100 = FRC divided by 16                                                                              |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 011 = FRC divided by 8                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 010 = FRC divided by 4                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 001 = FRC divided by 2<br>000 = FRC divided by 1 (default)                                           |                                   |                      |                        |                    |                 |           |  |  |  |

| bit 7-6         | <b>PLLPOST&lt;1:0&gt;:</b> PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler) |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 11 = Output divided by 8                                                                             |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | 10 = Reserved                                                                                        |                                   |                      |                        |                    |                 |           |  |  |  |

|                 |                                                                                                      | livided by 4 (de                  | efault)              |                        |                    |                 |           |  |  |  |

| bit 5           | 00 = Output d                                                                                        | ted: Read as '                    | o'                   |                        |                    |                 |           |  |  |  |

|                 | •                                                                                                    |                                   |                      |                        |                    |                 |           |  |  |  |

|                 | e DOZE<2:0> b<br>ZE<2:0> are ig                                                                      |                                   | written to whe       | en the DOZEN           | bit is clear. If D | OZEN = 1, any   | writes to |  |  |  |

| <b>2:</b> This  | s bit is cleared                                                                                     | when the ROI I                    | oit is set and a     | an interrupt occ       | urs.               |                 |           |  |  |  |

|                 | DOJENUS                                                                                              |                                   |                      |                        | ~ ~                |                 | <i>.</i>  |  |  |  |

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2                                                                                           | 2: PERIPHER                                                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|

| U-0          | U-0                                                                                                            | U-0                                                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

| _            |                                                                                                                | —                                                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |

| bit 15       |                                                                                                                |                                                                                     |                 |                   |                 |                 | bit   |  |  |  |

| U-0          | U-0                                                                                                            | U-0                                                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |

|              |                                                                                                                |                                                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |

| bit 7        |                                                                                                                |                                                                                     |                 |                   |                 |                 | bit   |  |  |  |

|              |                                                                                                                |                                                                                     |                 |                   |                 |                 |       |  |  |  |

| Legend:      | 1.1.1                                                                                                          |                                                                                     |                 |                   |                 |                 |       |  |  |  |

| R = Readab   |                                                                                                                | W = Writable b                                                                      | Dit             | •                 | nented bit, rea |                 |       |  |  |  |

| -n = Value a | at POR                                                                                                         | '1' = Bit is set                                                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |

| bit 15-12    | Unimplemen                                                                                                     | ted: Read as '0                                                                     | ,               |                   |                 |                 |       |  |  |  |

| bit 11       | -                                                                                                              |                                                                                     |                 |                   |                 |                 |       |  |  |  |

|              | •                                                                                                              | IC4MD: Input Capture 4 Module Disable bit<br>1 = Input Capture 4 module is disabled |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Input Cap                                                                                                  | oture 4 module is                                                                   | s enabled       |                   |                 |                 |       |  |  |  |

| bit 10       | IC3MD: Input                                                                                                   | IC3MD: Input Capture 3 Module Disable bit                                           |                 |                   |                 |                 |       |  |  |  |

|              | 1 = Input Capture 3 module is disabled                                                                         |                                                                                     |                 |                   |                 |                 |       |  |  |  |

|              |                                                                                                                | oture 3 module is                                                                   |                 |                   |                 |                 |       |  |  |  |

| bit 9        |                                                                                                                | IC2MD: Input Capture 2 Module Disable bit                                           |                 |                   |                 |                 |       |  |  |  |

|              |                                                                                                                | oture 2 module is<br>oture 2 module is                                              |                 |                   |                 |                 |       |  |  |  |

| bit 8        | IC1MD: Input                                                                                                   | t Capture 1 Mod                                                                     | ule Disable bit |                   |                 |                 |       |  |  |  |

|              | 1 = Input Cap                                                                                                  | oture 1 module is<br>oture 1 module is                                              | s disabled      |                   |                 |                 |       |  |  |  |

| bit 7-4      |                                                                                                                | ted: Read as '0                                                                     |                 |                   |                 |                 |       |  |  |  |

| bit 3        | OC4MD: Out                                                                                                     | put Compare 4                                                                       | Module Disable  | e bit             |                 |                 |       |  |  |  |

|              | 1 = Output Compare 4 module is disabled                                                                        |                                                                                     |                 |                   |                 |                 |       |  |  |  |

|              | -                                                                                                              | ompare 4 modu                                                                       |                 |                   |                 |                 |       |  |  |  |

| bit 2        |                                                                                                                | OC3MD: Output Compare 3 Module Disable bit                                          |                 |                   |                 |                 |       |  |  |  |

|              | 1 = Output Compare 3 module is disabled                                                                        |                                                                                     |                 |                   |                 |                 |       |  |  |  |

| L:1 4        | <ul> <li>0 = Output Compare 3 module is enabled</li> <li>OC2MD: Output Compare 2 Module Disable bit</li> </ul> |                                                                                     |                 |                   |                 |                 |       |  |  |  |

| bit 1        |                                                                                                                |                                                                                     |                 |                   |                 |                 |       |  |  |  |

|              | $\perp$ – Output Co                                                                                            | ompare 2 modu                                                                       |                 |                   |                 |                 |       |  |  |  |

|              | 0 = Output Co                                                                                                  | ompare 2 modul                                                                      | le is enabled   |                   |                 |                 |       |  |  |  |

| bit 0        |                                                                                                                | ompare 2 modul<br>put Compare 1                                                     |                 | e bit             |                 |                 |       |  |  |  |

| bit 0        | OC1MD: Out                                                                                                     | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul                                 | Module Disable  | e bit             |                 |                 |       |  |  |  |

#### ~

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

#### REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

#### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0          | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |  |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|

| _      | —            | —     | _     | _     | _     | —     | —     |  |  |  |

| bit 15 | bit 15 bit 8 |       |       |       |       |       |       |  |  |  |

|        |              |       |       |       |       |       |       |  |  |  |

| U-0    | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|        | C1RXR<6:0>   |       |       |       |       |       |       |  |  |  |

| bit 7  |              |       |       |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

| U-0              | R/W-0                                                                       | R/W-0                              | R/W-0           | R/W-0             | R/W-0                          | R/W-0                | R/W-0           |  |  |  |  |

|------------------|-----------------------------------------------------------------------------|------------------------------------|-----------------|-------------------|--------------------------------|----------------------|-----------------|--|--|--|--|

| _                | CLSRC4                                                                      | CLSRC3                             | CLSRC2          | CLSRC1            | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |

| bit 15           |                                                                             |                                    | •               |                   |                                |                      | bit 8           |  |  |  |  |

|                  | <b>D</b> 4 4                                                                | D 0.01 4                           | <b>D</b> 444    |                   | DAMA                           | DAMA                 | DAMO            |  |  |  |  |

| R/W-1            | R/W-1                                                                       | R/W-1                              | R/W-1           | R/W-1             | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3                                                                     | FLTSRC2                            | FLTSRC1         | FLTSRC0           | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      | DI              |  |  |  |  |

| Legend:          |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

| R = Readable     | bit                                                                         | W = Writable                       | bit             | U = Unimpler      | mented bit, read               | l as '0'             |                 |  |  |  |  |

| -n = Value at I  | POR                                                                         | '1' = Bit is set                   |                 | '0' = Bit is cle  | ared                           | x = Bit is unkr      | nown            |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

| bit 15           | Unimplemen                                                                  | ted: Read as '                     | 0'              |                   |                                |                      |                 |  |  |  |  |

| bit 14-10        | CLSRC<4:0>                                                                  | Current-Limit                      | Control Signa   | al Source Seleo   | ct for PWM Ger                 | nerator # bits       |                 |  |  |  |  |

|                  | 11111 = Fault 32                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 11110 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | •                                                                           |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | •<br>01100 = Reserved                                                       |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 01011 = Comparator 4                                                        |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             | Amp/Comparat                       | or 3            |                   |                                |                      |                 |  |  |  |  |

|                  | •                                                                           | Amp/Comparat                       |                 |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             | Amp/Comparat                       |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00111 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00110 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00101 = Res                                                                 | erved                              |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00100 = Reserved                                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00011 = Fault 4                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00010 = Fault 3                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00001 = Fault 2                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 00000 <b>= Fau</b>                                                          | ( <i>)</i>                         |                 |                   | ~                              |                      |                 |  |  |  |  |

| bit 9            | <b>CLPOL:</b> Current-Limit Polarity for PWM Generator # bit <sup>(2)</sup> |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 1 = The selected current-limit source is active-low                         |                                    |                 |                   |                                |                      |                 |  |  |  |  |

|                  | 0 = The selec                                                               | cted current-lim                   | it source is ac | tive-high         |                                |                      |                 |  |  |  |  |

| bit 8            | CLMOD: Cur                                                                  | rent-Limit Mode                    | e Enable for P  | WM Generator      | r # bit                        |                      |                 |  |  |  |  |

|                  |                                                                             | imit mode is er<br>imit mode is di |                 |                   |                                |                      |                 |  |  |  |  |

|                  | ne PWMLOCK                                                                  |                                    |                 | <6>) is a '1', th | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |  |

| the              | unlock sequen                                                               | ce has been ex                     | ecuted.         |                   |                                |                      |                 |  |  |  |  |

|                  |                                                                             |                                    |                 |                   |                                |                      |                 |  |  |  |  |

#### REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R-0, HSC      | R-0, HSC  | U-0             | U-0                                                 | U-0         | R/C-0, HS       | R-0, HSC                              | R-0, HSC |  |

|---------------|-----------|-----------------|-----------------------------------------------------|-------------|-----------------|---------------------------------------|----------|--|

| ACKSTAT       | TRSTAT    | _               | _                                                   | —           | BCL             | GCSTAT                                | ADD10    |  |

| bit 15        |           |                 |                                                     |             |                 |                                       | bit 8    |  |

|               |           |                 |                                                     |             |                 |                                       |          |  |

| R/C-0, HS     | R/C-0, HS | R-0, HSC        | R/C-0, HSC                                          | R/C-0, HSC  | R-0, HSC        | R-0, HSC                              | R-0, HSC |  |

| IWCOL         | I2COV     | D_A             | Р                                                   | S           | R_W             | RBF                                   | TBF      |  |

| bit 7         |           |                 |                                                     |             |                 |                                       | bit 0    |  |

|               |           |                 |                                                     |             |                 |                                       |          |  |

| Legend:       |           | C = Clearab     | le bit                                              | HS = Hardwa | re Settable bit | HSC = Hardware Settable/Clearable bit |          |  |

| R = Readabl   | e bit     | W = Writable    | / = Writable bit U = Unimplemented bit, read as '0' |             |                 |                                       |          |  |

| -n = Value at | POR       | '1' = Bit is se | et '0' = Bit is cleared x = Bit is unknown          |             |                 |                                       |          |  |

#### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables baud rate measurement on the next character – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                              |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                           |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                        |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                             |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                             |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                     |

|         | Refer to the " <b>UART</b> " (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for receive or transmit operation.                                                             |

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- 3: This feature is only available on 44-pin and 64-pin devices.

- 4: This feature is only available on 64-pin devices.

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                                          | U-0                                                                                       | U-0              | U-0             | U-0                                | U-0                  | U-0    | U-0                |  |  |  |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|-----------------|------------------------------------|----------------------|--------|--------------------|--|--|--|

| —                                                                                            | —                                                                                         | —                | _               | —                                  | —                    | —      | —                  |  |  |  |

| bit 15                                                                                       |                                                                                           |                  |                 |                                    |                      |        | bit 8              |  |  |  |

|                                                                                              |                                                                                           |                  |                 |                                    |                      |        |                    |  |  |  |

| U-0                                                                                          | U-0                                                                                       | U-0              | R-0             | R-0                                | R-0                  | R-0    | R-0                |  |  |  |

| —                                                                                            | —                                                                                         | —                | DNCNT4          | DNCNT3                             | DNCNT2               | DNCNT1 | DNCNT0             |  |  |  |

| bit 7                                                                                        |                                                                                           |                  |                 |                                    |                      |        | bit 0              |  |  |  |

|                                                                                              |                                                                                           |                  |                 |                                    |                      |        |                    |  |  |  |

| Legend:                                                                                      |                                                                                           |                  |                 |                                    |                      |        |                    |  |  |  |

| R = Readable                                                                                 | e bit                                                                                     | W = Writable bit |                 | U = Unimplemented bit, read as '0' |                      |        |                    |  |  |  |

| -n = Value at                                                                                | POR                                                                                       | '1' = Bit is set | 1' = Bit is set |                                    | '0' = Bit is cleared |        | x = Bit is unknown |  |  |  |

|                                                                                              |                                                                                           |                  |                 |                                    |                      |        |                    |  |  |  |

| bit 15-5                                                                                     | Unimplemen                                                                                | ted: Read as '   | 0'              |                                    |                      |        |                    |  |  |  |

| bit 4-0                                                                                      | DNCNT<4:0>                                                                                | : DeviceNet™     | Filter Bit Num  | iber bits                          |                      |        |                    |  |  |  |

|                                                                                              | 10010-11111 = Invalid selection<br>10001 = Compares up to Data Byte 3, bit 6 with EID<17> |                  |                 |                                    |                      |        |                    |  |  |  |

|                                                                                              | •                                                                                         |                  |                 |                                    |                      |        |                    |  |  |  |

|                                                                                              | •                                                                                         |                  |                 |                                    |                      |        |                    |  |  |  |

|                                                                                              | •                                                                                         |                  |                 |                                    |                      |        |                    |  |  |  |

| 00001 = Compares up to Data Byte 1, bit 7 with EID<0><br>00000 = Does not compare data bytes |                                                                                           |                  |                 |                                    |                      |        |                    |  |  |  |

#### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0         | R/W-0                                                                               | R/W-0                                                        | R/W-0            | R/W-0             | R/W-0            | R/W-0              | R/W-0  |

|---------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------|-------------------|------------------|--------------------|--------|

| F7MSK<1:0>    |                                                                                     | F6MSK<1:0>                                                   |                  | F5MSK<1:0>        |                  | F4MSK<1:0>         |        |

| bit 15        |                                                                                     | ·                                                            |                  |                   |                  |                    | bit    |

| R/W-0         | R/W-0                                                                               | R/W-0                                                        | R/W-0            | R/W-0             | R/W-0            | R/W-0              | R/W-0  |

| F3MS          | SK<1:0>                                                                             | F2MS                                                         | K<1:0>           | F1MS              | K<1:0>           | F0MS               | K<1:0> |

| bit 7         |                                                                                     |                                                              |                  |                   |                  |                    | bit (  |

| Legend:       |                                                                                     |                                                              |                  |                   |                  |                    |        |

| R = Readable  | e bit                                                                               | W = Writable                                                 | bit              | U = Unimplen      | nented bit, read | d as '0'           |        |

| -n = Value at | POR                                                                                 | '1' = Bit is set                                             |                  | '0' = Bit is clea | ared             | x = Bit is unknown |        |

|               | 01 = Accept                                                                         | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg | gisters contain  | mask              |                  |                    |        |

| bit 13-12     | F6MSK<1:0                                                                           | >: Mask Source                                               | for Filter 6 bit | s (same values    | s as bits<15:14  | >)                 |        |

| bit 11-10     | F5MSK<1:0                                                                           | >: Mask Source                                               | for Filter 5 bit | s (same values    | s as bits<15:14  | >)                 |        |

| bit 9-8       | F4MSK<1:0                                                                           | >: Mask Source                                               | for Filter 4 bit | s (same values    | s as bits<15:14  | >)                 |        |

| bit 7-6       | F3MSK<1:0                                                                           | >: Mask Source                                               | for Filter 3 bit | s (same values    | s as bits<15:14  | >)                 |        |

| bit 5-4       | F2MSK<1:0                                                                           | >: Mask Source                                               | for Filter 2 bit | s (same values    | s as bits<15:14  | >)                 |        |

| bit 3-2       | F1MSK<1:0>: Mask Source for Filter 1 bits (same values as bits<15:14>)              |                                                              |                  |                   |                  |                    |        |

|               | <b>F0MSK&lt;1:0&gt;:</b> Mask Source for Filter 0 bits (same values as bits<15:14>) |                                                              |                  |                   |                  | . )                |        |

#### 23.4 ADC Control Registers

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                                                                                                                   | R/W-0                             | R/W-0               | U-0               | R/W-0            | R/W-0                               | R/W-0               |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|-------------------|------------------|-------------------------------------|---------------------|--|--|--|

| ADON          | —                                                                                                                     | ADSIDL                            | ADDMABM             |                   | AD12B            | FORM1                               | FORM0               |  |  |  |

| bit 15        | •                                                                                                                     |                                   |                     |                   |                  |                                     | bit 8               |  |  |  |

| R/W-0         | R/W-0                                                                                                                 | R/W-0                             | R/W-0               | R/W-0             | R/W-0            | R/W-0, HC, HS                       | R/C-0. HC. HS       |  |  |  |

| SSRC2         | SSRC1                                                                                                                 | SSRC0                             | SSRCG               | SIMSAM            | ASAM             | SAMP                                | DONE <sup>(3)</sup> |  |  |  |

| bit 7         |                                                                                                                       |                                   |                     |                   |                  |                                     | bit (               |  |  |  |

| Legend:       |                                                                                                                       | HC - Hardwar                      | e Clearable bit     | HS - Hardwa       | re Settable bit  | C = Clearable bi                    | +                   |  |  |  |

| R = Readable  | a hit                                                                                                                 | W = Writable b                    |                     |                   | nented bit, read |                                     | L                   |  |  |  |

| -n = Value at |                                                                                                                       | '1' = Bit is set                  | nt -                | '0' = Bit is clea |                  | x = Bit is unknov                   | vp.                 |  |  |  |

|               | FUR                                                                                                                   | I - DILIS SEL                     |                     |                   | aieu             | x – Bit is unknov                   |                     |  |  |  |

| bit 15        | ADON: ADO                                                                                                             | C1 Operating M                    | ode bit             |                   |                  |                                     |                     |  |  |  |

|               | 1 = ADC mo<br>0 = ADC is 0                                                                                            | odule is operatir<br>off          | ng                  |                   |                  |                                     |                     |  |  |  |

| bit 14        | Unimpleme                                                                                                             | nted: Read as                     | <b>'</b> 0 <b>'</b> |                   |                  |                                     |                     |  |  |  |

| bit 13        | ADSIDL: A                                                                                                             | DC1 Stop in Idle                  | e Mode bit          |                   |                  |                                     |                     |  |  |  |

|               | 1 = Discontinues module operation when device enters Idle mode                                                        |                                   |                     |                   |                  |                                     |                     |  |  |  |

|               | 0 = Continues module operation in Idle mode                                                                           |                                   |                     |                   |                  |                                     |                     |  |  |  |

| bit 12        |                                                                                                                       | : DMA Buffer B                    |                     |                   |                  |                                     |                     |  |  |  |

|               |                                                                                                                       |                                   |                     |                   |                  | rovides an addre                    | ess to the DM       |  |  |  |

|               |                                                                                                                       |                                   |                     |                   |                  | nd-alone buffer<br>des a Scatter/Ga | ther address t      |  |  |  |