Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

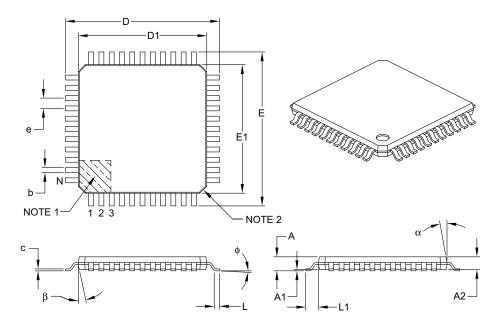

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp504t-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| Input Name <sup>(1)</sup>                   | Function Name | Register | Configuration Bits |

|---------------------------------------------|---------------|----------|--------------------|

| External Interrupt 1                        | INT1          | RPINR0   | INT1R<6:0>         |

| External Interrupt 2                        | INT2          | RPINR1   | INT2R<6:0>         |

| Timer2 External Clock                       | T2CK          | RPINR3   | T2CKR<6:0>         |

| Input Capture 1                             | IC1           | RPINR7   | IC1R<6:0>          |

| Input Capture 2                             | IC2           | RPINR7   | IC2R<6:0>          |

| Input Capture 3                             | IC3           | RPINR8   | IC3R<6:0>          |

| Input Capture 4                             | IC4           | RPINR8   | IC4R<6:0>          |

| Output Compare Fault A                      | OCFA          | RPINR11  | OCFAR<6:0>         |

| PWM Fault 1 <sup>(3)</sup>                  | FLT1          | RPINR12  | FLT1R<6:0>         |

| PWM Fault 2 <sup>(3)</sup>                  | FLT2          | RPINR12  | FLT2R<6:0>         |

| QEI1 Phase A <sup>(3)</sup>                 | QEA1          | RPINR14  | QEA1R<6:0>         |

| QEI1 Phase B <sup>(3)</sup>                 | QEB1          | RPINR14  | QEB1R<6:0>         |

| QEI1 Index <sup>(3)</sup>                   | INDX1         | RPINR15  | INDX1R<6:0>        |

| QEI1 Home <sup>(3)</sup>                    | HOME1         | RPINR15  | HOM1R<6:0>         |

| UART1 Receive                               | U1RX          | RPINR18  | U1RXR<6:0>         |

| UART2 Receive                               | U2RX          | RPINR19  | U2RXR<6:0>         |

| SPI2 Data Input                             | SDI2          | RPINR22  | SDI2R<6:0>         |

| SPI2 Clock Input                            | SCK2          | RPINR22  | SCK2R<6:0>         |

| SPI2 Slave Select                           | SS2           | RPINR23  | SS2R<6:0>          |

| CAN1 Receive <sup>(2)</sup>                 | C1RX          | RPINR26  | C1RXR<6:0>         |

| PWM Sync Input 1 <sup>(3)</sup>             | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |

| PWM Dead-Time Compensation 1 <sup>(3)</sup> | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time Compensation 2 <sup>(3)</sup> | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time Compensation 3 <sup>(3)</sup> | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |

# TABLE 11-1: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION)

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input source is available on dsPIC33EPXXXGP/MC50X devices only.

3: This input source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

# 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nown                                                                                                                                                                                                                                                                                                                                                                                                |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Unimplemer                   | nted: Read as '0                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| (see Table 11<br>1111001 = I | I-2 for input pin's nput tied to RPI1                                                                                                                                  | election num<br>21                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          | onding RPn Pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | e bit<br>POR<br>Unimplemen<br>IC2R<6:0>: /<br>(see Table 11<br>1111001 = I<br>0000001 = I<br>0000000 = I<br>Unimplemen<br>IC1R<6:0>: /<br>(see Table 11<br>1111001 = I | e bit W = Writable b<br>POR '1' = Bit is set<br>Unimplemented: Read as '0<br>IC2R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s<br>1111001 = Input tied to RPI1<br>0000001 = Input tied to CMP<br>0000000 = Input tied to Vss<br>Unimplemented: Read as '0<br>IC1R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s | e bit W = Writable bit<br>POR '1' = Bit is set<br>Unimplemented: Read as '0'<br>IC2R<6:0>: Assign Input Capture 2 (IC2)<br>(see Table 11-2 for input pin selection num<br>1111001 = Input tied to RPI121 | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>       IC1R<6:0>         e bit       W = Writable bit       U = Unimplem         POR       '1' = Bit is set       '0' = Bit is clear         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>         e bit       W = Writable bit       U = Unimplemented bit, real         POR       '1' = Bit is set       '0' = Bit is cleared         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>    e bit W = Writable bit U = Unimplemented bit, read as '0' POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkr Unimplemented: Read as '0' IC2R<6:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 <p< td=""></p<> |

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

# REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|------------------|----------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|

|              |                  |                                                          |       | DTCMP3R<6:0       | )>              |                 |       |

| bit 15       |                  |                                                          |       |                   |                 |                 | bit 8 |

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| 0-0          | R/W-0            | R/W-0                                                    |       | DTCMP2R<6:0       |                 | R/W-0           | R/W-U |

| bit 7        |                  |                                                          |       |                   | 17              |                 | bit 0 |

| bit i        |                  |                                                          |       |                   |                 |                 | bit 0 |

| Legend:      |                  |                                                          |       |                   |                 |                 |       |

| R = Readab   | ole bit          | W = Writable                                             | bit   | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR           | '1' = Bit is set                                         |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                  |                                                          |       |                   |                 |                 |       |

|              |                  | nput tied to CMI                                         |       |                   |                 |                 |       |

| bit 7        | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |                   |                 |                 |       |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|------------|-------|-------|--------|-------|-------|

| —      | —   |            |       | RP43  | R<5:0> |       |       |

| bit 15 |     |            |       |       |        |       | bit 8 |

|        |     |            |       |       |        |       |       |

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| —      | —   | RP42R<5:0> |       |       |        |       |       |

## REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

| REGISTER 16-2: | PTCON2: PWMx PRIMARY MASTER CLOCK DIVIDER SELECT REGISTER 2 |

|----------------|-------------------------------------------------------------|

|----------------|-------------------------------------------------------------|

| U-0               | U-0        | U-0              | U-0 | U-0              | U-0                     | U-0                     | U-0         |

|-------------------|------------|------------------|-----|------------------|-------------------------|-------------------------|-------------|

| —                 | —          | —                | _   | —                | —                       | —                       | _           |

| bit 15            |            |                  |     |                  |                         |                         | bit 8       |

|                   |            |                  |     |                  |                         |                         |             |

| U-0               | U-0        | U-0              | U-0 | U-0              | R/W-0                   | R/W-0                   | R/W-0       |

| —                 | —          | —                | _   | —                | PCLKDIV2 <sup>(1)</sup> | PCLKDIV1 <sup>(1)</sup> | PCLKDIV0(1) |

| bit 7             |            |                  |     |                  |                         |                         | bit 0       |

|                   |            |                  |     |                  |                         |                         |             |

| Legend:           |            |                  |     |                  |                         |                         |             |

| R = Readable      | bit        | W = Writable     | bit | U = Unimpler     | mented bit, read        | as '0'                  |             |

| -n = Value at POR |            | '1' = Bit is set |     | '0' = Bit is cle | ared                    | x = Bit is unknown      |             |

|                   |            |                  |     |                  |                         |                         |             |

| bit 15-3          | Unimplemen | ted: Read as '   | י'  |                  |                         |                         |             |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWMx Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64 101 = Divide-by-32

- 100 = Divide-by-32100 = Divide-by-16

- 011 = Divide-by-8

- 010 = Divide-by-4

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWMx timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0   | U-0              | U-0   | U-0              | U-0              | R/W-0           | R/W-0     |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------|------------------|------------------|-----------------|-----------|--|

| CHPCLKEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —     | —                | —     | —                | —                | CHOPC           | LK<9:8>   |  |

| bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                  |       |                  |                  |                 | bit 8     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                  |       |                  |                  |                 |           |  |

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                  | CHOPC | LK<7:0>          |                  |                 |           |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |                  |       |                  |                  |                 | bit 0     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                  |       |                  |                  |                 |           |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |                  |       |                  |                  |                 |           |  |

| R = Readable I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit   | W = Writable     | bit   | U = Unimplei     | mented bit, read | as '0'          |           |  |

| -n = Value at P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OR    | '1' = Bit is set |       | '0' = Bit is cle | eared            | x = Bit is unkr | s unknown |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       CHPCLKEN: Enable Chop Clock Generator bit       1 = Chop clock generator is enabled       0 = Chop clock generator is disabled         bit 14-10       Unimplemented: Read as '0'       CHOPCLK<9:0>: Chop Clock Divider bits       The frequency of the chop clock signal is given by the following expression:         Chop Frequency = (FP/PCLKDIV<2:0)/(CHOPCLK<9:0> + 1)       Chop Clock Divider bits |       |                  |       |                  |                  |                 |           |  |

# REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

## REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------|-------|-------|-------|-----------------|-------|-------|-------|

|                                                                      |       |       | MDC   | <15:8>          |       |       |       |

| bit 15                                                               |       |       |       |                 |       |       | bit 8 |

|                                                                      |       |       |       |                 |       |       |       |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|                                                                      |       |       | MD    | C<7:0>          |       |       |       |

| bit 7                                                                |       |       |       |                 |       |       | bit 0 |

|                                                                      |       |       |       |                 |       |       |       |

| Legend:                                                              |       |       |       |                 |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |                 |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is u |       |       |       | x = Bit is unkr | nown  |       |       |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

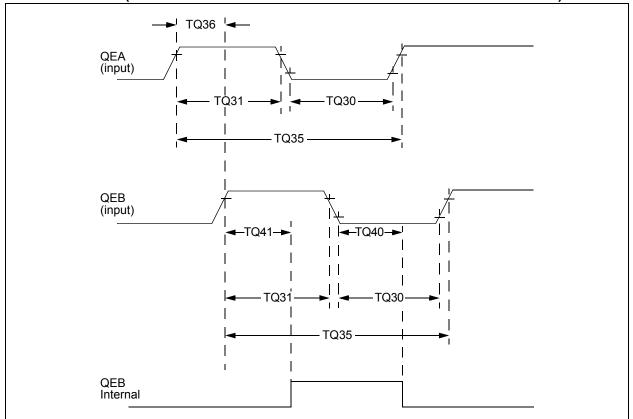

## 17.2 QEI Control Registers

|  | REGISTER 17-1: | QEI1CON: QEI1 CONTROL REGISTER |

|--|----------------|--------------------------------|

|--|----------------|--------------------------------|