Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

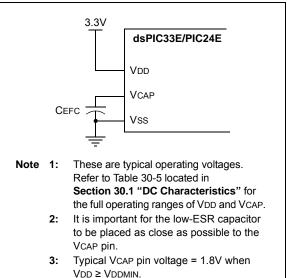

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-UFQFN Exposed Pad                                                              |

| Supplier Device Package    | 48-UQFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp504t-i-mv |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

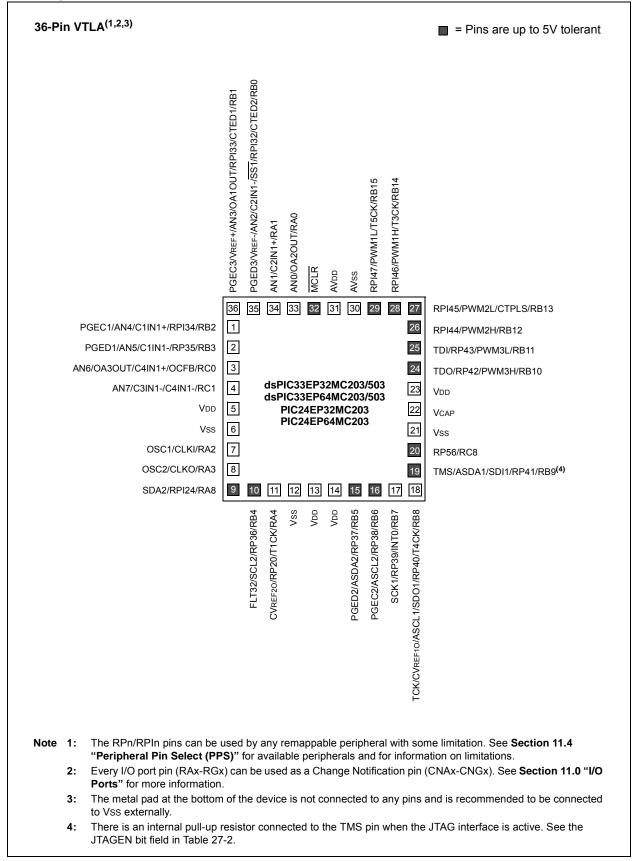

## Pin Diagrams (Continued)

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

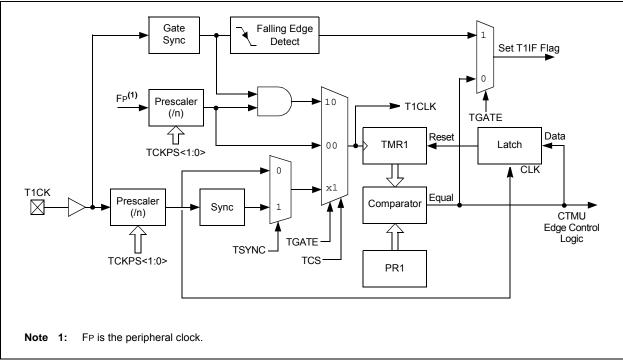

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

## TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

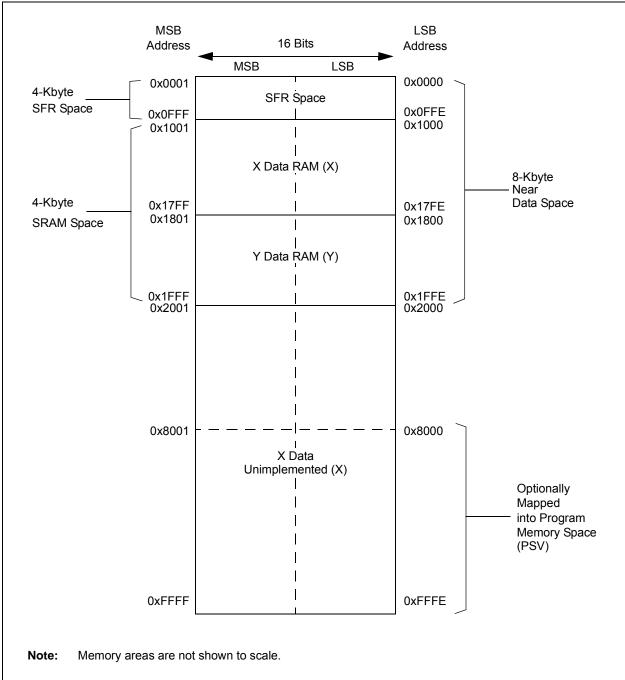

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1       | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|-------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF       | <b>INTOIF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF     | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | —      |        | _          | —      | _     | IC4IF  | IC3IF       | DMA3IF | C1IF   | C1RXIF   | SPI2IF      | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | MI2C2IF  | SI2C2IF     | —             | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | —      |        | _          | —      | _     | C1TXIF | _           | —      | CRCIF  | U2EIF    | U1EIF       | —             | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | —          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | —             | 0000          |

| IFS9         | 0812  |        |        | _          | _      | _      | _      | _          | _      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF   | _             | 0000          |

| IEC0         | 0820  |        | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE       | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _      | _           | INT1IE | CNIE   | CMIE     | MI2C1IE     | SI2C1IE       | 0000          |

| IEC2         | 0824  |        |        | _          | _      | _      | _      | _          | _      | _     | IC4IE  | IC3IE       | DMA3IE | C1IE   | C1RXIE   | SPI2IE      | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | MI2C2IE  | SI2C2IE     | _             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | —      |        |        |            | _      | —     | C1TXIE |             |        | CRCIE  | U2EIE    | U1EIE       |               | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | _        | _           | _             | 0000          |

| IEC9         | 0832  | _      | _      | —          | —      |        | _      |            | _      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE   | _             | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  | >      | _      | (      | OC1IP<2:0  | >      | _     |        | IC1IP<2:0>  |        | _      |          | NT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  | >      | _      | (      | C2IP<2:0   | >      | _     |        | IC2IP<2:0>  |        | _      | D        | MA0IP<2:0>  |               | 4444          |

| IPC2         | 0844  |        | ι      | J1RXIP<2:0 | 0>     | _      | Ş      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | _      |          | T3IP<2:0>   |               | 4444          |

| IPC3         | 0846  |        |        | _          | _      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | _      | U        | J1TXIP<2:0> |               | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0   | >      | _      |        | CMIP<2:0   | >      | _     |        | WI2C1IP<2:0 | >      | _      | S        | I2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  |        |        | _          | _      | _      | _      | _          | _      | _     | _      | _           | _      | _      |          | NT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  |        |        | T4IP<2:0>  | >      | _      | (      | C4IP<2:0   | >      | _     |        | OC3IP<2:0>  |        | _      | D        | MA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  |        | ι      | U2TXIP<2:0 | )>     | _      | L      | I2RXIP<2:  | 0>     | _     |        | INT2IP<2:0> | •      | _      |          | T5IP<2:0>   |               | 4444          |

| IPC8         | 0850  |        |        | C1IP<2:0>  | >      | _      | C      | 1RXIP<2:   | 0>     | _     |        | SPI2IP<2:0> | •      | _      | S        | PI2EIP<2:0> |               | 4444          |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | _      | D        | MA3IP<2:0>  |               | 0444          |

| IPC11        | 0856  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | _        | _           | _             | 0000          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | II2C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | _      | _        | _           | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>     | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _           | _             | 4440          |

| IPC17        | 0862  | _      | _      | _          | _      | _      | C      | 1TXIP<2:   | )>     | _     | _      | _           | —      | _      | _        | _           | _             | 0400          |

| IPC19        | 0866  | _      | _      | —          | _      | _      |        | _          | —      | _     |        | CTMUIP<2:0  | >      | _      | —        |             |               | 0040          |

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>     | _      |        | ICDIP<2:0  | >      | _     | _      | _           | _      | _      | —        | _           | _             | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:  | 0>     | —      | PT     | GWDTIP<    | 2:0>   | _     | PT     | GSTEPIP<2   | :0>    | _      | _        | _           | _             | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | TG3IP<2:   | )>     | _     |        | PTG2IP<2:0  | >      | _      | P        | TG1IP<2:0>  |               | 0444          |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name         Addr.           IFS0         0800           IFS1         0802           IFS2         0804           IFS3         0806           IFS4         0808           IFS5         080A           IFS6         080C           IFS8         0810           IFS9         0812           IEC1         0822           IEC2         0824           IEC3         0826           IEC4         0828 | U2TXIF           U2TXIF           U2TXIF           PWM2IF           U2TXIF           U2 | DMA1IF           TXIF         U2RXIF           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         -           -         - | Bit 13<br>AD1IF<br>INT2IF<br>—<br>CTMUIF<br>—<br>— | Bit 12<br>U1TXIF<br>T5IF<br>—<br>— | Bit 11<br>U1RXIF<br>T4IF<br>—<br>— | Bit 10<br>SPI1IF<br>OC4IF<br><br>QEI1IF | Bit 9<br>SPI1EIF<br>OC3IF<br>— | Bit 8<br>T3IF<br>DMA2IF | Bit 7<br>T2IF | Bit 6<br>OC2IF | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1       | Bit 0   | All<br>Resets |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------|------------------------------------|-----------------------------------------|--------------------------------|-------------------------|---------------|----------------|-------------|--------|--------|----------|-------------|---------|---------------|

| IFS1         0802           IFS2         0804           IFS3         0806           IFS4         0808           IFS5         080A           IFS6         080C           IFS8         0810           IFS9         0812           IEC0         0822           IEC1         0822           IEC2         0826                                                                                              | 2         U2TXIF           4         —           5         —           6         —           7         PWM2IF           7         —           10         JTAGIF           12         —           10         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TXIF         U2RXIF                                                                                                                                                                                                                                                                                                                                                                                  | INT2IF<br>—<br>—<br>CTMUIF                         | T5IF<br>—                          | T4IF<br>—<br>—                     | OC4IF                                   | OC3IF                          | DMA2IF                  |               | OC2IF          | IC2IF       | DMA0IF | T1IF   | OC1IE    | IC1IF       | INTOIF  |               |

| IFS2         0804           IFS3         0806           IFS4         0808           IFS5         080A           IFS6         080C           IFS8         0810           IFS9         0812           IEC0         0820           IEC1         0822           IEC2         0824           IEC3         0826                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      | —<br>—<br>CTMUIF                                   |                                    | _                                  | _                                       | _                              |                         |               |                |             |        |        | 00111    | 10111       |         | 0000          |

| IFS3         0806           IFS4         0808           IFS5         080A           IFS6         080C           IFS8         0810           IFS9         0812           IEC0         0820           IEC1         0822           IEC2         0824           IEC3         0826                                                                                                                          | i            ii            iii            iiii            iiiii            iiiiii            iiiiiiiiii            iiiiiiiiiiiiiiii            iiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      | —<br>CTMUIF                                        | —                                  | _                                  |                                         |                                |                         |               | —              | _           | INT1IF | CNIF   | CMIF     | MI2C1IF     | SI2C1IF | 0000          |

| IFS4         0808           IFS5         080A           IFS6         080C           IFS8         0810           IFS9         0812           IEC0         0820           IEC1         0822           IEC2         0824           IEC3         0826                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      | CTMUIF                                             |                                    |                                    | QEI1IF                                  |                                | —                       | _             | IC4IF          | IC3IF       | DMA3IF | _      | _        | SPI2IF      | SPI2EIF | 0000          |

| IFS5         080A           IFS6         080C           IFS8         0810           IFS9         0812           IEC0         0820           IEC1         0822           IEC2         0824           IEC3         0826                                                                                                                                                                                  | PWM2IF              JTAGIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | M2IF PWM1IF                                                                                                                                                                                                                                                                                                                                                                                          |                                                    | _                                  | _                                  |                                         | PSEMIF                         | —                       | _             | _              | _           | _      | _      | MI2C2IF  | SI2C2IF     | _       | 0000          |

| IFS6         080C           IFS8         0810           IFS9         0812           IEC0         0820           IEC1         0822           IEC2         0824           IEC3         0826                                                                                                                                                                                                              | JTAGIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                  |                                    |                                    | —                                       | _                              | —                       | _             | _              | _           | _      | CRCIF  | U2EIF    | U1EIF       | _       | 0000          |

| IFS8         0810           IFS9         0812           IEC0         0820           IEC1         0822           IEC2         0824           IEC3         0826                                                                                                                                                                                                                                          | JTAGIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AGIF ICDIF                                                                                                                                                                                                                                                                                                                                                                                           | —                                                  | _                                  | _                                  | _                                       | —                              | —                       | _             | —              | _           | _      | _      | —        | —           | —       | 0000          |

| IFS9         0812           IEC0         0820           IEC1         0822           IEC2         0824           IEC3         0826                                                                                                                                                                                                                                                                      | 2 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AGIF ICDIF                                                                                                                                                                                                                                                                                                                                                                                           |                                                    | _                                  | _                                  | _                                       | _                              | —                       | _             | _              | _           | _      | _      | _        | _           | PWM3IF  | 0000          |

| IEC0         0820           IEC1         0822           IEC2         0824           IEC3         0826                                                                                                                                                                                                                                                                                                  | )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                  | _                                  | _                                  | _                                       | _                              | —                       | _             | _              | _           | _      | _      | _        | _           | _       | 0000          |

| IEC1         0822           IEC2         0824           IEC3         0826                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                  | _                                  | _                                  | _                                       | _                              | —                       | _             | PTG3IF         | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF   | _       | 0000          |

| IEC2 0824<br>IEC3 0826                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | – DMA1IE                                                                                                                                                                                                                                                                                                                                                                                             | AD1IE                                              | U1TXIE                             | U1RXIE                             | SPI1IE                                  | SPI1EIE                        | T3IE                    | T2IE          | OC2IE          | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE       | INT0IE  | 0000          |

| IEC3 0826                                                                                                                                                                                                                                                                                                                                                                                              | 2 U2TXIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TXIE U2RXIE                                                                                                                                                                                                                                                                                                                                                                                          | INT2IE                                             | T5IE                               | T4IE                               | OC4IE                                   | OC3IE                          | DMA2IE                  | _             | _              | _           | INT1IE | CNIE   | CMIE     | MI2C1IE     | SI2C1IE | 0000          |

|                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                  | _                                  | _                                  | _                                       | _                              | —                       | _             | IC4IE          | IC3IE       | DMA3IE | _      | _        | SPI2IE      | SPI2EIE | 0000          |

| IEC4 0828                                                                                                                                                                                                                                                                                                                                                                                              | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                  | _                                  | _                                  | QEI1IE                                  | PSEMIE                         | —                       | _             | _              | _           | _      | _      | MI2C2IE  | SI2C2IE     | _       | 0000          |

|                                                                                                                                                                                                                                                                                                                                                                                                        | - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      | CTMUIE                                             | _                                  | _                                  | _                                       | _                              | —                       | _             | _              | _           | _      | CRCIE  | U2EIE    | U1EIE       | _       | 0000          |

| IEC5 082A                                                                                                                                                                                                                                                                                                                                                                                              | PWM2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | M2IE PWM1IE                                                                                                                                                                                                                                                                                                                                                                                          | _                                                  | _                                  | _                                  | _                                       | _                              | —                       | _             | _              | _           | _      | _      | _        | _           | _       | 0000          |

| IEC6 082C                                                                                                                                                                                                                                                                                                                                                                                              | - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                  | _                                  | _                                  | _                                       | _                              | —                       | _             | _              | _           | _      | _      | _        | _           | PWM3IE  | 0000          |

| IEC8 0830                                                                                                                                                                                                                                                                                                                                                                                              | JTAGIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AGIE ICDIE                                                                                                                                                                                                                                                                                                                                                                                           | —                                                  | -                                  |                                    | _                                       | _                              | —                       | _             | _              | -           | -      | _      | _        | _           | _       | 0000          |

| IEC9 0832                                                                                                                                                                                                                                                                                                                                                                                              | 2 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                  | -                                  |                                    | _                                       | _                              | —                       | _             | PTG3IE         | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE   | _       | 0000          |

| IPC0 0840                                                                                                                                                                                                                                                                                                                                                                                              | ) _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      | T1IP<2:0>                                          |                                    |                                    | (                                       | OC1IP<2:0                      | )>                      | _             |                | IC1IP<2:0>  |        | _      | I        | NT0IP<2:0>  |         | 4444          |

| IPC1 0842                                                                                                                                                                                                                                                                                                                                                                                              | 2 —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      | T2IP<2:0>                                          |                                    |                                    | (                                       | OC2IP<2:0                      | )>                      | _             |                | IC2IP<2:0>  |        | _      | D        | MA0IP<2:0>  |         | 4444          |

| IPC2 0844                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | – u                                                                                                                                                                                                                                                                                                                                                                                                  | J1RXIP<2:0                                         | >                                  |                                    | ŝ                                       | SPI1IP<2:0                     | )>                      | _             |                | SPI1EIP<2:0 | >      | _      |          | T3IP<2:0>   |         | 4444          |

| IPC3 0846                                                                                                                                                                                                                                                                                                                                                                                              | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                  | -                                  |                                    | D                                       | MA1IP<2:                       | 0>                      | _             |                | AD1IP<2:0>  |        | _      | L        | J1TXIP<2:0> |         | 0444          |

| IPC4 0848                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                      | CNIP<2:0>                                          |                                    |                                    |                                         | CMIP<2:0                       | >                       | _             |                | MI2C1IP<2:0 | >      | _      | S        | I2C1IP<2:0> |         | 4444          |

| IPC5 084A                                                                                                                                                                                                                                                                                                                                                                                              | · -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      | —                                                  | _                                  | _                                  | _                                       | —                              | —                       | —             | _              | _           | _      | —      | I        | NT1IP<2:0>  |         | 0004          |

| IPC6 084C                                                                                                                                                                                                                                                                                                                                                                                              | - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                      | T4IP<2:0>                                          |                                    |                                    | (                                       | OC4IP<2:0                      | )>                      | _             |                | OC3IP<2:0>  |        | _      | D        | MA2IP<2:0>  |         | 4444          |