Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| N-4-11-                   |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

| Details                   |                                                                                   |

| Product Status            | Active                                                                            |

| Core Processor            | dsPIC                                                                             |

| Core Size                 | 16-Bit                                                                            |

| peed                      | 70 MIPs                                                                           |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| lumber of I/O             | 35                                                                                |

| Program Memory Size       | 128KB (43K x 24)                                                                  |

| rogram Memory Type        | FLASH                                                                             |

| EPROM Size                | -                                                                                 |

| AM Size                   | 8K x 16                                                                           |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| ata Converters            | A/D 9x10b/12b                                                                     |

| Scillator Type            | Internal                                                                          |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| lounting Type             | Surface Mount                                                                     |

| ackage / Case             | 44-TQFP                                                                           |

| Supplier Device Package   | 44-TQFP (10x10)                                                                   |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp504t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

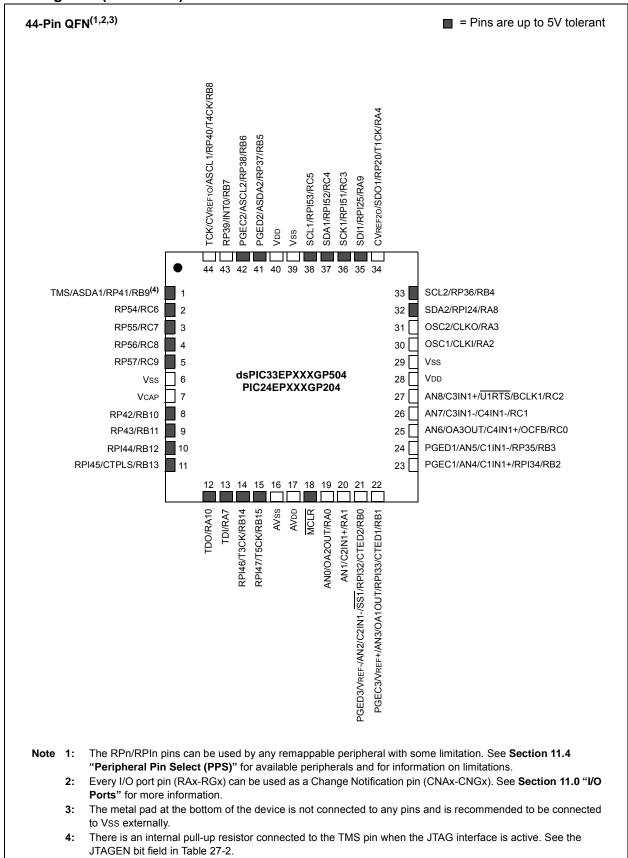

#### Pin Diagrams (Continued)

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the "dsPIC33/PIC24 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C™)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name <sup>(4)</sup>              | Pin<br>Type    | Buffer<br>Type             | PPS                   | Description                                                                                                                                                                                                              |

|--------------------------------------|----------------|----------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                             | I              | Analog                     | No                    | Analog input channels.                                                                                                                                                                                                   |

| CLKI                                 | I              | ST/<br>CMOS                | No                    | External clock source input. Always associated with OSC1 pin function.                                                                                                                                                   |

| CLKO                                 | 0              | _                          | No                    | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function.                                       |

| OSC1<br>OSC2                         | I<br>I/O       | ST/<br>CMOS<br>—           | No<br>No              | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |

| REFCLKO                              | 0              | _                          | Yes                   | Reference clock output.                                                                                                                                                                                                  |

| IC1-IC4                              | I              | ST                         | Yes                   | Capture Inputs 1 through 4.                                                                                                                                                                                              |

| OCFA<br>OCFB<br>OC1-OC4              | <br>           | ST<br>ST                   | Yes<br>No<br>Yes      | Compare Fault A input (for Compare channels). Compare Fault B input (for Compare channels). Compare Outputs 1 through 4.                                                                                                 |

| INTO<br>INT1<br>INT2                 | <br> -<br> -   | ST<br>ST<br>ST             | No<br>Yes<br>Yes      | External Interrupt 0. External Interrupt 1. External Interrupt 2.                                                                                                                                                        |

| RA0-RA4, RA7-RA12                    | I/O            | ST                         | No                    | PORTA is a bidirectional I/O port.                                                                                                                                                                                       |

| RB0-RB15                             | I/O            | ST                         | No                    | PORTB is a bidirectional I/O port.                                                                                                                                                                                       |

| RC0-RC13, RC15                       | I/O            | ST                         | No                    | PORTC is a bidirectional I/O port.                                                                                                                                                                                       |

| RD5, RD6, RD8                        | I/O            | ST                         | No                    | PORTD is a bidirectional I/O port.                                                                                                                                                                                       |

| RE12-RE15                            | I/O            | ST                         | No                    | PORTE is a bidirectional I/O port.                                                                                                                                                                                       |

| RF0, RF1                             | I/O            | ST                         | No                    | PORTF is a bidirectional I/O port.                                                                                                                                                                                       |

| RG6-RG9                              | I/O            | ST                         | No                    | PORTG is a bidirectional I/O port.                                                                                                                                                                                       |

| T1CK<br>T2CK<br>T3CK<br>T4CK<br>T5CK | <br>           | ST<br>ST<br>ST<br>ST<br>ST | No<br>Yes<br>No<br>No | Timer1 external clock input. Timer2 external clock input. Timer3 external clock input. Timer4 external clock input. Timer5 external clock input.                                                                         |

| CTPLS                                | 0              | ST                         | No                    | CTMU pulse output.                                                                                                                                                                                                       |

| CTED1<br>CTED2                       | I<br>I         | ST<br>ST                   | No<br>No              | CTMU External Edge Input 1. CTMU External Edge Input 2.                                                                                                                                                                  |

| U1CTS<br>U1RTS<br>U1RX               | <br>  0<br>  1 | ST<br>—<br>ST              | No<br>No<br>Yes       | UART1 Clear-To-Send. UART1 Ready-To-Send. UART1 receive.                                                                                                                                                                 |

| U1TX<br>BCLK1                        | 0 0            | —<br>ST                    | Yes<br>No             | UART1 transmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                                                            |

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

P = Power

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

PPS = Peripheral Pin Select

TTL = TTL input buffer

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

- 3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

- 4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

- 5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

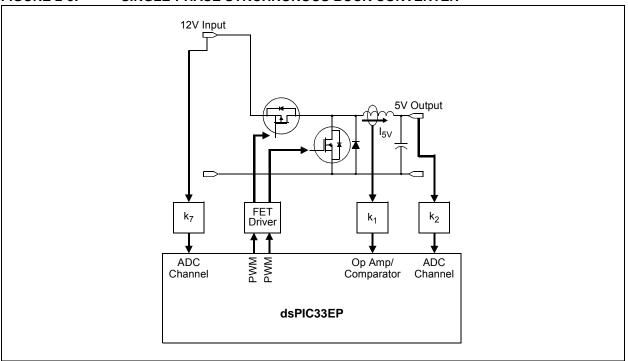

FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

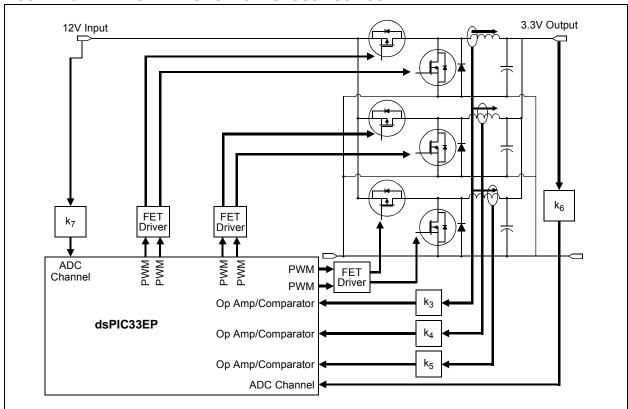

FIGURE 2-6: MULTIPHASE SYNCHRONOUS BUCK CONVERTER

| ഗ             |

|---------------|

| Ñ             |

| 0             |

| Ō             |

| ō             |

| $\overline{}$ |

| ∺             |

| ŏ             |

| ₹i            |

| ~             |

| ㅗ             |

|               |

| 0             |

| а             |

| 9             |

| Œ             |

| ∞             |

|               |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14            | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|-------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| QEI1CON   | 01C0  | QEIEN  | _                 | QEISIDL  |            | PIMOD<2:0> |          | IMV<     | :1:0>       | _      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM-   | <1:0>  | 0000          |

| QEI1IOC   | 01C2  | QCAPEN | FLTREN            |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| QEI1STAT  | 01C4  | _      | _                 | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL  | 01C6  |        | POSCNT<15:0>      |          |            |            |          |          |             | 0000   |        |            |          |        |        |        |        |               |

| POS1CNTH  | 01C8  |        |                   |          |            |            |          | F        | POSCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| POS1HLD   | 01CA  |        |                   |          |            |            |          |          | POSHLD<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| VEL1CNT   | 01CC  |        |                   |          |            |            |          |          | VELCNT<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL  | 01CE  |        | INTTMR<15:0> 000  |          |            |            |          |          |             |        |        | 0000       |          |        |        |        |        |               |

| INT1TMRH  | 01D0  |        | INTTMR<31:16> 00  |          |            |            |          |          |             |        |        | 0000       |          |        |        |        |        |               |

| INT1HLDL  | 01D2  |        | INTHLD<15:0> 0    |          |            |            |          |          |             |        |        | 0000       |          |        |        |        |        |               |

| INT1HLDH  | 01D4  |        |                   |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL | 01D6  |        |                   |          |            |            |          | I        | NDXCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH | 01D8  |        |                   |          |            |            |          | II       | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD  | 01DA  |        |                   |          |            |            |          | I        | NDXHLD<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL  | 01DC  |        |                   |          |            |            |          |          | QEIGEC<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| QEI1ICL   | 01DC  |        |                   |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH  | 01DE  |        | QEIGEC<31:16> 000 |          |            |            |          |          |             |        |        |            | 0000     |        |        |        |        |               |

| QEI1ICH   | 01DE  |        | QEIIC<31:16> 000  |          |            |            |          |          |             |        |        |            | 0000     |        |        |        |        |               |

| QEI1LECL  | 01E0  |        | QEILEC<15:0> 000  |          |            |            |          |          |             |        |        | 0000       |          |        |        |        |        |               |

| QEI1LECH  | 01E2  |        | ·-                | <u>'</u> | <u>'</u>   |            |          |          | QEILEC<31:1 | 6>     |        |            |          | ·      | ·      |        | ·-     | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

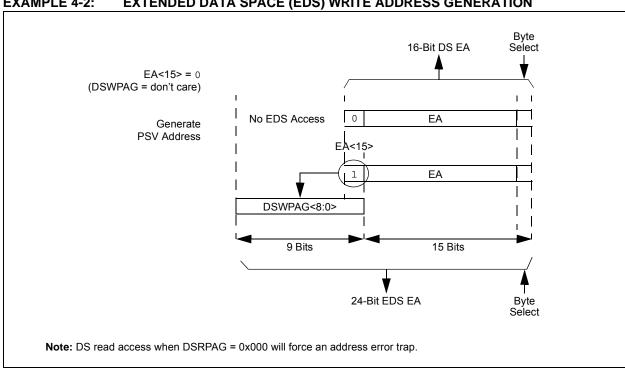

**EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION**

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

#### REGISTER 5-2: NVMADRH: NONVOLATILE MEMORY ADDRESS REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-x | R/W-x | R/W-x | R/W-x  | R/W-x    | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|--------|----------|-------|-------|-------|

|       |       |       | NVMADF | R<23:16> |       |       |       |

| bit 7 |       |       |        |          |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMADR<23:16>: Nonvolatile Memory Write Address High bits

Selects the upper 8 bits of the location to program or erase in program Flash memory. This register

may be read or written by the user application.

#### REGISTER 5-3: NVMADRL: NONVOLATILE MEMORY ADDRESS REGISTER LOW

| R/W-x        | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| NVMADR<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |  |

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| NVMADR<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **NVMADR<15:0>:** Nonvolatile Memory Write Address Low bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register

may be read or written by the user application.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-0         | W-0 | W-0 | W-0 | W-0 | W-0 | W-0 | W-0 |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| NVMKEY<7:0> |     |     |     |     |     |     |     |  |  |

| bit 7 bit 0 |     |     |     |     |     |     |     |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

#### REGISTER 8-5: DMAXSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| STB<23:16> |       |       |       |       |       |       |       |  |  |

| bit 7      |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **STB<23:16>:** Secondary Start Address bits (source or destination)

### REGISTER 8-6: DMAXSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| STB<15:8> |       |       |       |       |       |       |       |

| bit 15    |       |       |       |       |       |       | bit 8 |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| STB<7:0> |       |       |       |       |       |       |       |

| bit 7    |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

#### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   |     | _   |     | _   |     | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0   | U-0 | U-0 | R-1 | R-1   | R-1    | R-1   |

|-------|-------|-----|-----|-----|-------|--------|-------|

| _     | _     | _   | _   |     | LSTCH | 1<3:0> |       |

| bit 7 | pit 7 |     |     |     |       |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3-0 LSTCH<3:0>: Last DMAC Channel Active Status bits

1111 = No DMA transfer has occurred since system Reset

1110 = Reserved

•

•

•

0100 = Reserved

0011 = Last data transfer was handled by Channel 3

0010 = Last data transfer was handled by Channel 2

0001 = Last data transfer was handled by Channel 1

0000 = Last data transfer was handled by Channel 0

#### **REGISTER 10-3:** PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-------|-----|-------|

| _      | _   |     | _   | _   | CMPMD | 1   | _     |

| bit 15 |     |     |     |     |       |     | bit 8 |

| R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | U-0   |

|-------|-----|-----|-----|-----|-----|--------|-------|

| CRCMD | _   | _   | _   | _   | _   | I2C2MD | _     |

| bit 7 |     |     |     |     |     |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 Unimplemented: Read as '0'

bit 10 **CMPMD:** Comparator Module Disable bit

1 = Comparator module is disabled

0 = Comparator module is enabled

bit 9-8 Unimplemented: Read as '0' bit 7

CRCMD: CRC Module Disable bit

1 = CRC module is disabled 0 = CRC module is enabled

Unimplemented: Read as '0'

bit 6-2 bit 1 I2C2MD: I2C2 Module Disable bit

1 = I2C2 module is disabled

0 = I2C2 module is enabled

bit 0 Unimplemented: Read as '0'

#### **REGISTER 10-4:** PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |

|-------|-----|-----|-----|--------|--------|-----|-------|

| _     | _   | _   | _   | REFOMD | CTMUMD | _   | _     |

| bit 7 |     |     |     |        |        |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3 **REFOMD:** Reference Clock Module Disable bit

> 1 = Reference clock module is disabled 0 = Reference clock module is enabled

bit 2 CTMUMD: CTMU Module Disable bit

1 = CTMU module is disabled

0 = CTMU module is enabled

bit 1-0 Unimplemented: Read as '0'

#### 11.4.4.2 Output Mapping

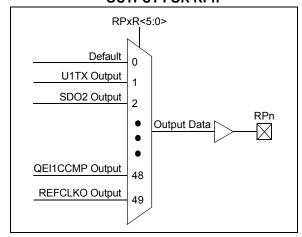

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

#### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

#### 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | _   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _   | _     |

| bit 15 | _   |        |         |         | _       |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| _     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit | į –                |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, rea | nd as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 **Unimplemented:** Read as '0'

bit 13 ICSIDL: Input Capture Stop in Idle Control bit

1 = Input capture will Halt in CPU Idle mode

0 = Input capture will continue to operate in CPU Idle mode

bit 12-10 ICTSEL<2:0>: Input Capture Timer Select bits

111 = Peripheral clock (FP) is the clock source of the ICx

110 = Reserved 101 = Reserved

100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)

011 = T5CLK is the clock source of the ICx 010 = T4CLK is the clock source of the ICx

001 = T2CLK is the clock source of the ICx

000 = T3CLK is the clock source of the ICx

bit 9-7 Unimplemented: Read as '0'

bit 6-5 ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture buffer overflow occurred0 = No input capture buffer overflow occurred

bit 3 **ICBNE:** Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty, at least one more capture value can be read

0 = Input capture buffer is empty

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)

110 = Unused (module is disabled)

101 = Capture mode, every 16th rising edge (Prescaler Capture mode)

100 = Capture mode, every 4th rising edge (Prescaler Capture mode)

011 = Capture mode, every rising edge (Simple Capture mode)

010 = Capture mode, every falling edge (Simple Capture mode)

001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)

000 = Input capture module is turned off

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola® SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0 "Electrical Characteristics"** for more information.

The SPIx serial interface consists of four pins, as follows:

- · SDIx: Serial Data Input

- · SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

#### 22.2 CTMU Control Registers

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0    | R/W-0                  | R/W-0  |

|--------|-----|----------|-------|-------|----------|------------------------|--------|

| CTMUEN | _   | CTMUSIDL | TGEN  | EDGEN | EDGSEQEN | IDISSEN <sup>(1)</sup> | CTTRIG |

| bit 15 |     |          |       |       |          |                        | bit 8  |

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|-------------|-----|-----|-----|-----|-----|-----|-----|

| _           | _   | _   | _   | _   | _   | _   | _   |

| bit 7 bit 0 |     |     |     |     |     |     |     |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 CTMUEN: CTMU Enable bit

1 = Module is enabled0 = Module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 CTMUSIDL: CTMU Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 **TGEN:** Time Generation Enable bit

1 = Enables edge delay generation

0 = Disables edge delay generation

bit 11 EDGEN: Edge Enable bit

1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)

0 = Software is used to trigger edges (manual set of EDGxSTAT)

bit 10 EDGSEQEN: Edge Sequence Enable bit

1 = Edge 1 event must occur before Edge 2 event can occur

0 = No edge sequence is needed

bit 9 **IDISSEN:** Analog Current Source Control bit<sup>(1)</sup>

1 = Analog current source output is grounded

0 = Analog current source output is not grounded

bit 8 CTTRIG: ADC Trigger Control bit

1 = CTMU triggers ADC start of conversion

0 = CTMU does not trigger ADC start of conversion

bit 7-0 **Unimplemented:** Read as '0'

Note 1: The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

#### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

bit 5 **Unimplemented:** Read as '0'

bit 4 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

1 = VIN+ input connects to internal CVREFIN voltage

0 = VIN+ input connects to C4IN1+ pin

bit 3-2 **Unimplemented:** Read as '0'

bit 1-0 **CCH<1:0>:** Comparator Channel Select bits<sup>(1)</sup>

11 = VIN- input of comparator connects to OA3/AN6 10 = VIN- input of comparator connects to OA2/AN0 01 = VIN- input of comparator connects to OA1/AN3 00 = VIN- input of comparator connects to C4IN1-

**Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |                           | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                  |        |       |            |

|--------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|-------|------------|

| Parameter<br>No.   | Тур.                      | Max.                                                                                                                                                                                                                                              | Units Conditions |        |       |            |

| Operating Cur      | rent (IDD) <sup>(1)</sup> |                                                                                                                                                                                                                                                   |                  |        |       |            |

| DC20d              | 9                         | 15                                                                                                                                                                                                                                                | mA               | -40°C  |       |            |

| DC20a              | 9                         | 15                                                                                                                                                                                                                                                | mA               | +25°C  | 3.3V  | 10 MIPS    |

| DC20b              | 9                         | 15                                                                                                                                                                                                                                                | mA               | +85°C  |       | 10 MIFS    |

| DC20c              | 9                         | 15                                                                                                                                                                                                                                                | mA               | +125°C |       |            |

| DC22d              | 16                        | 25                                                                                                                                                                                                                                                | mA               | -40°C  |       |            |

| DC22a              | 16                        | 25                                                                                                                                                                                                                                                | mA               | +25°C  | 3.3V  | 20 MIPS    |

| DC22b              | 16                        | 25                                                                                                                                                                                                                                                | mA               | +85°C  |       | 20 10111 3 |

| DC22c              | 16                        | 25                                                                                                                                                                                                                                                | mA               | +125°C |       |            |

| DC24d              | 27                        | 40                                                                                                                                                                                                                                                | mA               | -40°C  |       |            |

| DC24a              | 27                        | 40                                                                                                                                                                                                                                                | mA               | +25°C  | 3.3V  | 40 MIPS    |

| DC24b              | 27                        | 40                                                                                                                                                                                                                                                | mA               | +85°C  | 3.5 V | 40 WIII 3  |

| DC24c              | 27                        | 40                                                                                                                                                                                                                                                | mA               | +125°C |       |            |

| DC25d              | 36                        | 55                                                                                                                                                                                                                                                | mA               | -40°C  |       |            |

| DC25a              | 36                        | 55                                                                                                                                                                                                                                                | mA               | +25°C  | 3.3V  | 60 MIPS    |

| DC25b              | 36                        | 55                                                                                                                                                                                                                                                | mA               | +85°C  |       | 00 WIIF 3  |

| DC25c              | 36                        | 55                                                                                                                                                                                                                                                | mA               | +125°C |       |            |

| DC26d              | 41                        | 60                                                                                                                                                                                                                                                | mA               | -40°C  |       |            |

| DC26a              | 41                        | 60                                                                                                                                                                                                                                                | mA               | +25°C  | 3.3V  | 70 MIPS    |

| DC26b              | 41                        | 60                                                                                                                                                                                                                                                | mA               | +85°C  |       |            |

- **Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) {NOP();} statement

- · JTAG is disabled

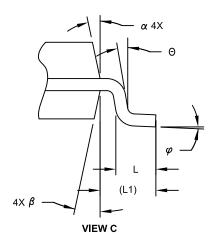

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |           |          | MILLIMETERS |  |  |  |

|--------------------------|-----------|-----------|----------|-------------|--|--|--|

| Dimensi                  | on Limits | MIN       | NOM      | MAX         |  |  |  |

| Number of Pins           | N         |           | 28       | •           |  |  |  |

| Pitch                    | е         |           | 1.27 BSC |             |  |  |  |

| Overall Height           | Α         | -         | -        | 2.65        |  |  |  |

| Molded Package Thickness | A2        | 2.05      | -        | -           |  |  |  |

| Standoff §               | A1        | 0.10      | =        | 0.30        |  |  |  |

| Overall Width            | E         | 10.30 BSC |          |             |  |  |  |

| Molded Package Width     | E1        | 7.50 BSC  |          |             |  |  |  |

| Overall Length           | D         | 17.90 BSC |          |             |  |  |  |

| Chamfer (Optional)       | h         | 0.25      | -        | 0.75        |  |  |  |

| Foot Length              | L         | 0.40      | -        | 1.27        |  |  |  |

| Footprint                | L1        | 1.40 REF  |          |             |  |  |  |

| Lead Angle               | Θ         | 0°        | -        | -           |  |  |  |

| Foot Angle               | φ         | 0°        | -        | 8°          |  |  |  |

| Lead Thickness           | С         | 0.18      | -        | 0.33        |  |  |  |

| Lead Width               | b         | 0.31      | -        | 0.51        |  |  |  |

| Mold Draft Angle Top     | α         | 5°        | -        | 15°         |  |  |  |

| Mold Draft Angle Bottom  | β         | 5°        | _        | 15°         |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

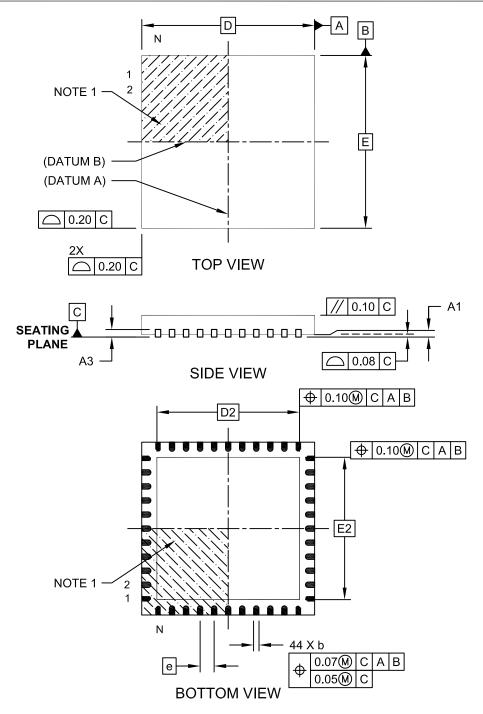

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-103C Sheet 1 of 2

## Revision E (April 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

TABLE A-4: MAJOR SECTION UPDATES

| Section Name                           | Update Description                                                                              |  |  |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| "16-bit Microcontrollers               | The following 512-Kbyte devices were added to the General Purpose Families table                |  |  |  |  |  |

| and Digital Signal                     | (see Table 1):                                                                                  |  |  |  |  |  |

| Controllers (up to 512-Kbyte Flash and | • PIC24EP512GP202                                                                               |  |  |  |  |  |

| 48-Kbyte SRAM) with High-              | • PIC24EP512GP204                                                                               |  |  |  |  |  |

| Speed PWM, Op amps, and                | • PIC24EP512GP206                                                                               |  |  |  |  |  |

| Advanced Analog"                       | • dsPIC33EP512GP502                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512GP504                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512GP506                                                                             |  |  |  |  |  |

|                                        | The following 512-Kbyte devices were added to the Motor Control Families table (see Table 2):   |  |  |  |  |  |

|                                        | • PIC24EP512MC202                                                                               |  |  |  |  |  |

|                                        | • PIC24EP512MC204                                                                               |  |  |  |  |  |

|                                        | • PIC24EP512MC206                                                                               |  |  |  |  |  |

|                                        | • dsPIC33EP512MC202                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC204                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC206                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC502                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC504                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC506                                                                             |  |  |  |  |  |

|                                        | Certain Pin Diagrams were updated to include the new 512-Kbyte devices.                         |  |  |  |  |  |

| Section 4.0 "Memory                    | Added a Program Memory Map for the new 512-Kbyte devices (see Figure 4-4).                      |  |  |  |  |  |

| Organization"                          | Added a Data Memory Map for the new dsPIC 512-Kbyte devices (see Figure 4-11).                  |  |  |  |  |  |

|                                        | Added a Data Memory Map for the new PIC24 512-Kbyte devices (see Figure 4-16).                  |  |  |  |  |  |

| Section 7.0 "Interrupt Controller"     | Updated the VECNUM bits in the INTTREG register (see Register 7-7).                             |  |  |  |  |  |

| Section 11.0 "I/O Ports"               | Added tip 6 to Section 11.5 "I/O Helpful Tips".                                                 |  |  |  |  |  |

| Section 27.0 "Special Features"        | The following modifications were made to the Configuration Byte Register Map (see Table 27-1):  |  |  |  |  |  |

|                                        | Added the column Device Memory Size (Kbytes)                                                    |  |  |  |  |  |

|                                        | Removed Notes 1 through 4                                                                       |  |  |  |  |  |

|                                        | Added addresses for the new 512-Kbyte devices                                                   |  |  |  |  |  |

| Section 30.0 "Electrical               | Updated the Minimum value for Parameter DC10 (see Table 30-4).                                  |  |  |  |  |  |

| Characteristics"                       | Added Power-Down Current (lpd) parameters for the new 512-Kbyte devices (see Table 30-8).       |  |  |  |  |  |

|                                        | Updated the Minimum value for Parameter CM34 (see Table 30-53).                                 |  |  |  |  |  |

|                                        | Updated the Minimum and Maximum values and the Conditions for paramteer SY12 (see Table 30-22). |  |  |  |  |  |

| dsPIC33EPXXXGP5 | 0X, dsPIC33EPXXXN | 1C20X/50X AND P | IC24EPXXXGP/M | C20X |

|-----------------|-------------------|-----------------|---------------|------|

| NOTES:          |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |

|                 |                   |                 |               |      |