Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

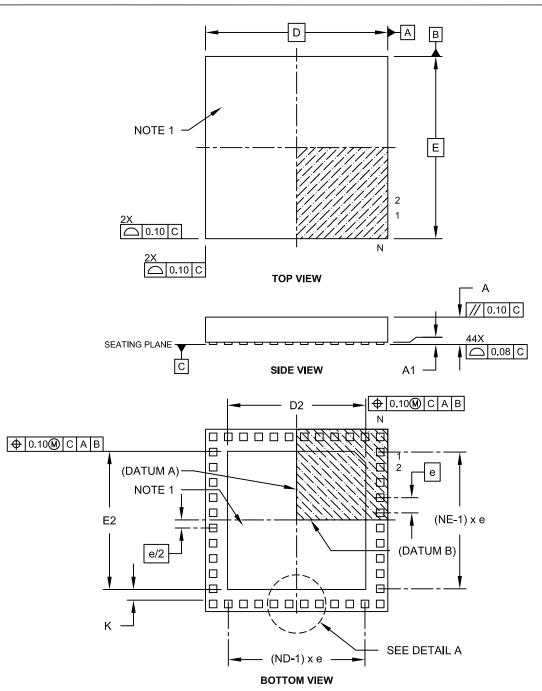

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128gp506-h-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2 | SFA: Stack Frame Active Status bit                                                        |

|-------|-------------------------------------------------------------------------------------------|

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and |

|       | DSWPAG values                                                                             |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space              |

| hit 1 | PND: Dounding Mode Select hit(1)                                                          |

- bit 1 **RND:** Rounding Mode Select bit<sup>(1)</sup>

- 1 = Biased (conventional) rounding is enabled

- 0 = Unbiased (convergent) rounding is enabled

bit 0 IF: Integer or Fractional Multiplier Mode Select bit<sup>(1)</sup> 1 = Integer mode is enabled for DSP multiply 0 = Fractional mode is enabled for DSP multiply

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- **2:** This bit is always read as '0'.

- 3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

### TABLE 4-49: PORTD REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 0E30  | _      | _      | _      |        | _      | _      | _     | TRISD8 |       | TRISD6 | TRISD5 |       |       |       |       | _     | 0160          |

| PORTD        | 0E32  | _      | _      |        | _      | _      | _      |       | RD8    | —     | RD6    | RD5    | —     | _     | _     | _     |       | xxxx          |

| LATD         | 0E34  | _      | _      |        | _      | _      | _      |       | LATD8  | —     | LATD6  | LATD5  | —     | _     | _     | _     |       | xxxx          |

| ODCD         | 0E36  | _      |        |        | -      |        |        |       | ODCD8  | —     | ODCD6  | ODCD5  | —     | _     | _     | _     |       | 0000          |

| CNEND        | 0E38  | _      |        |        | -      |        |        |       | CNIED8 | —     | CNIED6 | CNIED5 | —     | _     | _     | _     |       | 0000          |

| CNPUD        | 0E3A  | _      | _      |        | _      | _      | _      |       | CNPUD8 | —     | CNPUD6 | CNPUD5 | —     | _     | _     | _     |       | 0000          |

| CNPDD        | 0E3C  | _      | _      |        | _      | _      | _      |       | CNPDD8 | —     | CNPDD6 | CNPDD5 | —     | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PORTE REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE        | 0E40  | TRISE15 | TRISE14 | TRISE13 | TRISE12 | —      | _      | _     | —     | _     |       | -     | —     | —     | _     | —     |       | F000          |

| PORTE        | 0E42  | RE15    | RE14    | RE13    | RE12    | _      | —      | —     | —     |       | —     | —     | _     | —     | —     | —     | —     | xxxx          |

| LATE         | 0E44  | LATE15  | LATE14  | LATE13  | LATE12  | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | xxxx          |

| ODCE         | 0E46  | ODCE15  | ODCE14  | ODCE13  | ODCE12  | —      | -      | -     | -     |       |       | -     | —     | —     | _     | _     |       | 0000          |

| CNENE        | 0E48  | CNIEE15 | CNIEE14 | CNIEE13 | CNIEE12 | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | 0000          |

| CNPUE        | 0E4A  | CNPUE15 | CNPUE14 | CNPUE13 | CNPUE12 | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | 0000          |

| CNPDE        | 0E4C  | CNPDE15 | CNPDE14 | CNPDE13 | CNPDE12 | _      | _      | _     | _     | -     | _     | —     | _     | —     | _     | _     | _     | 0000          |

| ANSELE       | 0E4E  | ANSE15  | ANSE14  | ANSE13  | ANSE12  |        | —      | _     | —     | _     | _     | _     |       |       | _     |       | _     | F000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-51: PORTF REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISF        | 0E50  | —      | -      | —      |        | —      |        | —     | -     | -     | —     | -     | -     | —     | -     | TRISF1 | TRISF0 | 0003          |

| PORTF        | 0E52  | —      | —      | _      | —      | —      | —      | —     | _     | —     | —     | —     | —     | —     | —     | RF1    | RF0    | xxxx          |

| LATF         | 0E54  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | LATF1  | LATF0  | xxxx          |

| ODCF         | 0E56  | _      | -      | _      | -      | —      | -      | —     |       |       | —     |       |       | _     | -     | ODCF1  | ODCF0  | 0000          |

| CNENF        | 0E58  |        | _      | -      |        | —      | -      | _     | -     | -     | —     | -     | -     | —     | -     | CNIEF1 | CNIEF0 | 0000          |

| CNPUF        | 0E5A  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | CNPUF1 | CNPUF0 | 0000          |

| CNPDF        | 0E5C  | _      | _      | _      | _      | -      |        | _     | _     | _     | _     | _     | _     | _     | -     | CNPDF1 | CNPDF0 | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

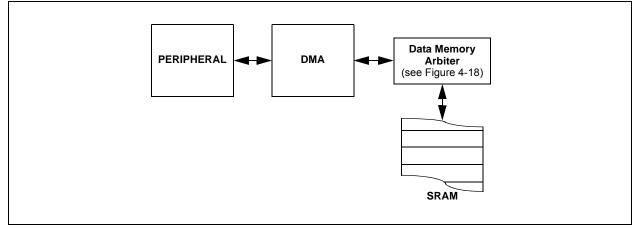

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

## FIGURE 8-1: DMA CONTROLLER MODULE

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision Fl  | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| —       | —     | —     | —     | —          | —     | —     | —     |

| bit 15  | •     |       |       |            | •     |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| _       |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7   | •     |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Leaend: |       |       |       |            |       |       |       |

### REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

| U-0                   | U-0                                | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------------|----------|

| _                     | —                                  | PCHEQIRQ                           | PCHEQIEN         | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                    |                                    |                  |                  |                  |                       | bit 8    |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                              | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                             | VELOVIRQ                           | VELOVIEN         | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                    |                                    |                  |                  |                  |                       | bit 0    |

| r                     |                                    |                                    |                  |                  |                  |                       |          |

| Legend:               |                                    | HS = Hardware                      |                  | C = Clearable    |                  |                       |          |

| R = Readable I        |                                    | W = Writable b                     | bit              | •                | nented bit, rea  |                       |          |

| -n = Value at P       | OR                                 | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr       | iown     |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| bit 15-14             | -                                  | ted: Read as '0                    |                  |                  |                  | .,                    |          |

| bit 13                |                                    | Position Counte                    | er Greater Tha   | n or Equal Cor   | npare Status b   | it                    |          |

|                       |                                    | T ≥ QEI1GEC<br>T < QEI1GEC         |                  |                  |                  |                       |          |

| bit 12                |                                    | Position Counte                    | r Greater Tha    | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    | s disabled                         |                  |                  |                  |                       |          |

| bit 11                |                                    | Position Counte                    | r Less Than o    | r Equal Compa    | are Status bit   |                       |          |

|                       | 1 = POS1CN                         |                                    |                  |                  |                  |                       |          |

| bit 10                |                                    | Position Counte                    | r Less Than or   | - Equal Compa    | ire Interrunt En | ahla hit              |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 9                 | POSOVIRQ:                          | Position Counte                    | er Overflow Sta  | itus bit         |                  |                       |          |

|                       | 1 = Overflow                       |                                    |                  |                  |                  |                       |          |

|                       |                                    | ow has occurred                    |                  |                  |                  |                       |          |

| bit 8                 |                                    | Position Counte                    | r Overflow Inte  | errupt Enable b  | Dit              |                       |          |

|                       | 1 = Interrupt i<br>0 = Interrupt i |                                    |                  |                  |                  |                       |          |

| bit 7                 | •                                  | tion Counter (H                    | oming) Initializ | ation Process    | Complete Stat    | us bit <sup>(1)</sup> |          |

|                       |                                    | T was reinitialize                 | •                |                  | · · · · · · · ·  |                       |          |

|                       | 0 = POS1CN                         | T was not reiniti                  | alized           |                  |                  |                       |          |

| bit 6                 | PCIIEN: Posi                       | tion Counter (He                   | oming) Initializ | ation Process    | Complete inter   | rupt Enable bit       |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 5                 | 0 = Interrupt i                    |                                    | r Overflow Sta   | tuo hit          |                  |                       |          |

| DIL 5                 | 1 = Overflow                       | Velocity Counter                   | I Overnow Sta    |                  |                  |                       |          |

|                       |                                    | ow has not occu                    | irred            |                  |                  |                       |          |

| bit 4                 | VELOVIEN:                          | /elocity Counter                   | Overflow Inte    | rrupt Enable bi  | it               |                       |          |

|                       | 1 = Interrupt i                    | s enabled                          |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 3                 |                                    | atus Flag for Ho                   |                  | us bit           |                  |                       |          |

|                       |                                    | ent has occurred<br>event has occu |                  |                  |                  |                       |          |

|                       |                                    |                                    |                  |                  |                  |                       |          |

#### REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

## REGISTER 17-4: POSICNTH: POSITION COUNTER 1 HIGH WORD REGISTER

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unkno |           | nown  |       |       |

|------------------------------------|-------|-------|---------------------------------------|-----------|-------|-------|-------|

| R = Readable bit W = Writable bit  |       | it    | U = Unimplemented bit, read as '0'    |           |       |       |       |

| Legend:                            |       |       |                                       |           |       |       |       |

|                                    |       |       |                                       |           |       |       |       |

| bit 7                              |       |       |                                       |           |       |       | bit 0 |

|                                    |       |       | POSCN                                 | IT<23:16> |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| bit 15                             |       |       |                                       |           |       |       | bit 8 |

|                                    |       |       | POSCN                                 | IT<31:24> |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

bit 15-0 **POSCNT<31:16>:** High Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

#### REGISTER 17-5: POS1CNTL: POSITION COUNTER 1 LOW WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | POSCN | T<15:8> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

|        |       |       |       |         |       |       |       |

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------------|-------|-------|-------|-------|-------|-------|

|       | POSCNT<7:0> |       |       |       |       |       |       |

| bit 7 |             |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 POSCNT<15:0>: Low Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

#### REGISTER 17-6: POS1HLD: POSITION COUNTER 1 HOLD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|---------------------------------------|----------|-------|-------|-------|

|                                    |       |       | POSHL                                 | _D<15:8> |       |       |       |

| bit 15                             |       |       |                                       |          |       |       | bit 8 |

|                                    |       |       |                                       |          |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | POSH                                  | LD<7:0>  |       |       |       |

| bit 7                              |       |       |                                       |          |       |       | bit 0 |

|                                    |       |       |                                       |          |       |       |       |

| Legend:                            |       |       |                                       |          |       |       |       |

| R = Readable bit W = Writable bit  |       | bit   | U = Unimplemented bit, read as '0'    |          |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unkno |          | nown  |       |       |

bit 15-0 **POSHLD<15:0>:** Hold Register for Reading and Writing POS1CNTH bits

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0        | U-0                                                                           | R/W-0                                                                                                                                                                                                             | R/W-1, HC                  | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |  |  |  |

|--------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------|------------------|-----------------|----------------|--|--|--|

| I2CEN        | —                                                                             | I2CSIDL                                                                                                                                                                                                           | SCLREL                     | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |  |  |  |

| bit 15       |                                                                               |                                                                                                                                                                                                                   |                            |                              |                  |                 | bit 8          |  |  |  |

|              |                                                                               |                                                                                                                                                                                                                   |                            |                              |                  |                 |                |  |  |  |

| R/W-0        | R/W-0                                                                         | R/W-0                                                                                                                                                                                                             | R/W-0, HC                  | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |  |  |  |

| GCEN         | STREN                                                                         | ACKDT                                                                                                                                                                                                             | ACKEN                      | RCEN                         | PEN              | RSEN            | SEN            |  |  |  |

| bit 7        |                                                                               |                                                                                                                                                                                                                   |                            |                              |                  |                 | bit 0          |  |  |  |

| Legend:      |                                                                               | HC = Hardware                                                                                                                                                                                                     | Cloarable bit              |                              |                  |                 |                |  |  |  |

| R = Readab   | le hit                                                                        | W = Writable bi                                                                                                                                                                                                   |                            | II = I Inimpler              | mented bit, rea  | d as '0'        |                |  |  |  |

| -n = Value a |                                                                               | '1' = Bit is set                                                                                                                                                                                                  | L .                        | '0' = Bit is cle             |                  | x = Bit is unk  | nown           |  |  |  |

|              |                                                                               |                                                                                                                                                                                                                   |                            |                              |                  |                 | nown           |  |  |  |

| bit 15       | <b>12CEN:</b> 12Cx                                                            | Enable bit                                                                                                                                                                                                        |                            |                              |                  |                 |                |  |  |  |

|              |                                                                               | he I2Cx module                                                                                                                                                                                                    |                            |                              |                  |                 | ;              |  |  |  |

|              | 0 = Disables                                                                  | the I2Cx module;                                                                                                                                                                                                  | all l <sup>2</sup> C™ pins | are controlled               | by port functior | ıs              |                |  |  |  |

| bit 14       | Unimplemen                                                                    | ted: Read as '0'                                                                                                                                                                                                  |                            |                              |                  |                 |                |  |  |  |

| bit 13       |                                                                               | x Stop in Idle Mo                                                                                                                                                                                                 |                            |                              |                  |                 |                |  |  |  |

|              |                                                                               | ues module oper<br>s module operation                                                                                                                                                                             |                            |                              | dle mode         |                 |                |  |  |  |

| bit 12       |                                                                               | •                                                                                                                                                                                                                 |                            | _                            | ( clave)         |                 |                |  |  |  |

|              |                                                                               | <b>SCLREL:</b> SCLx Release Control bit (when operating as I <sup>2</sup> C slave)<br>1 = Releases SCLx clock                                                                                                     |                            |                              |                  |                 |                |  |  |  |

|              |                                                                               | 0 = Holds SCLx clock low (clock stretch)                                                                                                                                                                          |                            |                              |                  |                 |                |  |  |  |

|              | If STREN = 1                                                                  | If STREN = 1:                                                                                                                                                                                                     |                            |                              |                  |                 |                |  |  |  |

|              | •                                                                             | t is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear<br>the beginning of every slave data byte transmission. Hardware is clear at the end of every slave |                            |                              |                  |                 |                |  |  |  |

|              |                                                                               | reception. Hardw                                                                                                                                                                                                  |                            |                              |                  |                 | t every slave  |  |  |  |

|              | If STREN = 0                                                                  | -                                                                                                                                                                                                                 |                            |                              |                  |                 |                |  |  |  |

|              |                                                                               | <u>.</u><br>, software can or                                                                                                                                                                                     | nly write '1' to re        | elease clock). I             | Hardware is cle  | ar at the begir | ning of every  |  |  |  |

|              | -                                                                             | te transmission.                                                                                                                                                                                                  |                            |                              | -                | address byte re | eception.      |  |  |  |

| bit 11       |                                                                               | ligent Peripheral                                                                                                                                                                                                 |                            |                              |                  |                 |                |  |  |  |

|              |                                                                               | <ul> <li>1 = IPMI mode is enabled; all addresses are Acknowledged</li> <li>0 = IPMI mode disabled</li> </ul>                                                                                                      |                            |                              |                  |                 |                |  |  |  |

| bit 10       |                                                                               |                                                                                                                                                                                                                   | i+                         |                              |                  |                 |                |  |  |  |

|              |                                                                               | A10M: 10-Bit Slave Address bit<br>1 = I2CxADD is a 10-bit slave address                                                                                                                                           |                            |                              |                  |                 |                |  |  |  |

|              | 1 = 12CxADD is a 10-bit slave address<br>0 = 12CxADD is a 7-bit slave address |                                                                                                                                                                                                                   |                            |                              |                  |                 |                |  |  |  |

| bit 9        | DISSLW: Dis                                                                   | ISSLW: Disable Slew Rate Control bit                                                                                                                                                                              |                            |                              |                  |                 |                |  |  |  |

|              |                                                                               | 1 = Slew rate control is disabled                                                                                                                                                                                 |                            |                              |                  |                 |                |  |  |  |

|              |                                                                               | control is enable                                                                                                                                                                                                 |                            |                              |                  |                 |                |  |  |  |

| bit 8        |                                                                               | us Input Levels b                                                                                                                                                                                                 |                            | 0145                         | <b>c</b>         |                 |                |  |  |  |

|              |                                                                               | /O pin thresholds<br>SMBus input thre                                                                                                                                                                             |                            | n SMBus speci                | fication         |                 |                |  |  |  |

| bit 7        |                                                                               | ral Call Enable b                                                                                                                                                                                                 |                            | ing as I <sup>2</sup> C slav | /e)              |                 |                |  |  |  |

|              | 1 = Enables in                                                                | terrupt when a ge<br>all address disat                                                                                                                                                                            | neral call addre           | -                            |                  | dule is enabled | for reception) |  |  |  |

|              |                                                                               |                                                                                                                                                                                                                   |                            |                              |                  |                 |                |  |  |  |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

| U-0                     | U-0                                                             | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

|-------------------------|-----------------------------------------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|

| _                       | _                                                               |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |

| bit 15                  | <b>I</b>                                                        | •                                  |         |                  |                 |                 | bit 8   |  |  |  |

|                         |                                                                 |                                    |         |                  |                 |                 |         |  |  |  |

| U-0                     | R-1                                                             | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

| _                       | ICODE6                                                          | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |

| bit 7                   |                                                                 |                                    |         |                  |                 |                 | bit     |  |  |  |

| Logondi                 |                                                                 |                                    |         |                  |                 |                 |         |  |  |  |

| Legend:<br>R = Readable | - hit                                                           |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |

| -n = Value at           |                                                                 | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |

| -n = value at           | POR                                                             | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |

| bit 15-13               | Unimplemen                                                      | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 12-8                | =                                                               | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |

|                         |                                                                 | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |

|                         | 01111 = Filter 15                                               |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                                               |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                                               |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •<br>00001 = Filter 1                                           |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 00001 = Filter 1 $00000 = Filter 0$                             |                                    |         |                  |                 |                 |         |  |  |  |

| bit 7                   |                                                                 | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 6-0                 | -                                                               |                                    |         |                  |                 |                 |         |  |  |  |

|                         | ICODE<6:0>: Interrupt Flag Code bits 1000101-1111111 = Reserved |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 1000100 = FIFO almost full interrupt                            |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                                                 | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |

|                         | 1000010 = K<br>1000001 = E                                      | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |

|                         | 1000000 = N                                                     |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                                               |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                                               |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                                               |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                                                 | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         | 0001111 = RB15 buffer interrupt                                 |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                                               |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                                                 |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 0001001 <b>= R</b>                                              | B9 buffer inter                    | rupt    |                  |                 |                 |         |  |  |  |

|                         |                                                                 | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |

|                         |                                                                 | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |

|                         |                                                                 | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         |                                                                 | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         | 0000011 <b>= T</b>                                              | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |

|                         |                                                                 |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                                                 | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |

## REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| Legend:C = WritableR = Readable bitW = Writable |       |       |      |        | n to clear the bit<br>mented bit, read |       |       |

|-------------------------------------------------|-------|-------|------|--------|----------------------------------------|-------|-------|

| <b></b>                                         |       |       |      |        |                                        |       |       |

| bit 7                                           |       |       |      |        |                                        |       | bit 0 |

| IVRIF                                           | WAKIF | ERRIF | _    | FIFOIF | RBOVIF                                 | RBIF  | TBIF  |

| R/C-0                                           | R/C-0 | R/C-0 | U-0  | R/C-0  | R/C-0                                  | R/C-0 | R/C-0 |

|                                                 |       |       |      |        |                                        |       |       |

| bit 15                                          | •     |       |      |        |                                        |       | bit 8 |

| _                                               | —     | ТХВО  | TXBP | RXBP   | TXWAR                                  | RXWAR | EWARN |

| U-0                                             | U-0   | R-0   | R-0  | R-0    | R-0                                    | R-0   | R-0   |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER

'1' = Bit is set

| bit 15-14 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 13    | <b>TXBO:</b> Transmitter in Error State Bus Off bit                                                    |

|           | 1 = Transmitter is in Bus Off state                                                                    |

|           | 0 = Transmitter is not in Bus Off state                                                                |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                                                |

|           | 1 = Transmitter is in Bus Passive state                                                                |

|           | 0 = Transmitter is not in Bus Passive state                                                            |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                                                   |

|           | 1 = Receiver is in Bus Passive state                                                                   |

|           | 0 = Receiver is not in Bus Passive state                                                               |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                                          |

|           | 1 = Transmitter is in Error Warning state                                                              |

| h:+ 0     | 0 = Transmitter is not in Error Warning state                                                          |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                                             |

|           | 1 = Receiver is in Error Warning state<br>0 = Receiver is not in Error Warning state                   |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                                              |

| bit o     | 1 = Transmitter or receiver is in Error Warning state                                                  |

|           | 0 = Transmitter or receiver is not in Error Warning state                                              |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                                              |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                                         |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CxINTF<13:8>)                                     |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 4     | Unimplemented: Read as '0'                                                                             |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                                            |

|           | 1 = Interrupt request has occurred                                                                     |

| hit O     | 0 = Interrupt request has not occurred                                                                 |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                                          |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |

|           |                                                                                                        |

-n = Value at POR

#### FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

### 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a То comprehensive reference source. complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

# 27.1 Configuration Bits

In dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration bytes, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

The Configuration Flash bytes map is shown in Table 27-1.

#### **30.1 DC Characteristics**

|                |                             |                       | Maximum MIPS                                                          |  |  |

|----------------|-----------------------------|-----------------------|-----------------------------------------------------------------------|--|--|

| Characteristic | VDD Range<br>(in Volts)     | Temp Range<br>(in °C) | dsPIC33EPXXXGP50X,<br>dsPIC33EPXXXMC20X/50X and<br>PIC24EPXXXGP/MC20X |  |  |

|                | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +85°C        | 70                                                                    |  |  |

| —              | 3.0V to 3.6V <sup>(1)</sup> | -40°C to +125°C       | 60                                                                    |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

#### TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      |    | Min.          | Тур. | Max. | Unit |

|---------------------------------------------------------------------------------------------|----|---------------|------|------|------|

| Industrial Temperature Devices                                                              |    |               |      |      |      |

| Operating Junction Temperature Range                                                        | TJ | -40           | —    | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA | -40           | _    | +85  | °C   |

| Extended Temperature Devices                                                                |    |               |      |      |      |

| Operating Junction Temperature Range                                                        |    | -40           | —    | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA | -40           | —    | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ |    | Pint + Pi/o   |      | W    |      |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$     |    |               |      |      |      |