Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc202-e-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   | <i>•</i>                       | (se                           |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0               | U-0                          | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |

|---------------------|------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|

| VAR                 | —                            | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15              |                              |                                                          |                         |                             |                           |                    | bit                |

| R/W-0               | R/W-0                        | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |

| bit 7               | I                            |                                                          |                         |                             | 1                         | 1                  | bit                |

| Legend:             |                              | C = Clearable                                            | e bit                   |                             |                           |                    |                    |

| R = Readabl         | e bit                        | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |

| -n = Value at       | POR                          | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |

| bit 14              |                              | nted: Read as '                                          |                         |                             |                           |                    |                    |

| bit 13-12           | -                            | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |

| bit 10-8            |                              | Loop Nesting<br>oops are active                          |                         | (1)                         |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |

| bit 7               | SATA: ACCA                   | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |

| bit 6               | SATB: ACCE                   | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |

| bit 5               | SATDW: Dat                   | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |

|                     |                              | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |

| bit 4               |                              | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |

|                     |                              | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |

| bit 3               |                              | nterrupt Priority                                        |                         |                             |                           |                    |                    |

|                     |                              | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |

|                     | nis bit is availabl          |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |

| 2: Th               | nis bit is always            | reau as 0.                                               |                         |                             |                           |                    |                    |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>      | —       |        | ICDIP<2:0  | >     | _        | —       | —           | _       | —       | _      | -           |        | 4400          |

| IPC36        | 0888  | -      | l      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<    | 2:0>  | _        | P       | TGSTEPIP<2  | :0>     | —       | —      |             |        | 4440          |

| IPC37        | 088A  |        | _      | _          | _       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | >       | _       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | —       | _      |            |       | —        | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | —          | —       | —       | _      |            |       | —        | _       | DAE         | DOOVR   | _       | —      |             |        | 0000          |

| INTCON4      | 08C6  | -      | _      | —          | _       | _       | _      |            | _     | _        | _       | —           | —       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | -      | —      | —          | _       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | M<7:0>  |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7 | Bit 6  | Bit 5           | Bit 4         | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Reset |

|--------------|-------|--------|--------|------------|--------|--------|--------|----------------|--------|-------|--------|-----------------|---------------|--------|----------|--------------|---------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF        | T3IF   | T2IF  | OC2IF  | IC2IF           | DMA0IF        | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF          | DMA2IF | _     | _      | _               | INT1IF        | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000         |

| IFS2         | 0804  | _      | _      | _          | _      |        |        |                | _      | _     | IC4IF  | IC3IF           | DMA3IF        | C1IF   | C1RXIF   | SPI2IF       | SPI2EIF | 0000         |

| IFS3         | 0806  | _      | _      | _          | _      |        | QEI1IF | PSEMIF         | _      | _     | _      | _               | _             | _      | MI2C2IF  | SI2C2IF      | _       | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |        |        |        | -              | _      | _     | C1TXIF | _               | _             | CRCIF  | U2EIF    | U1EIF        |         | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS6         | 080C  | _      | _      | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IF  | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |        |        |        |                | _      | _     | _      | _               | _             | _      | _        | _            |         | 0000         |

| IFS9         | 0812  | _      | —      | _          | _      | _      |        |                | _      | —     | PTG3IF | PTG2IF          | PTG1IF        | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE        | T3IE   | T2IE  | OC2IE  | IC2IE           | DMA0IE        | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE          | DMA2IE | —     | _      | —               | INT1IE        | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000         |

| IEC2         | 0824  | _      | _      | _          | _      | _      |        | _              | _      | _     | IC4IE  | IC3IE           | <b>DMA3IE</b> | C1IE   | C1RXIE   | SPI2IE       | SPI2EIE | 0000         |

| IEC3         | 0826  | _      | _      | _          | _      | _      | QEI1IE | PSEMIE         | _      | _     | _      | _               | _             | _      | MI2C2IE  | SI2C2IE      | _       | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      |        |        | _              | _      | _     | C1TXIE | _               | _             | CRCIE  | U2EIE    | U1EIE        | _       | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC6         | 082C  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | PWM3IE  | 0000         |

| IEC7         | 082E  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      |        | _              | _      | _     | _      | _               | _             | _      | _        | _            | _       | 0000         |

| IEC9         | 0832  | _      | _      | _          | _      | _      |        | _              | _      | _     | PTG3IE | PTG2IE          | PTG1IE        | PTG0IE | PTGWDTIE | PTGSTEPIE    | _       | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0      | >      | _     |        | IC1IP<2:0>      |               | _      |          | INT0IP<2:0>  |         | 4444         |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0      | >      | _     |        | IC2IP<2:0>      |               | _      | [        | DMA0IP<2:0>  |         | 4444         |

| IPC2         | 0844  | _      | l      | J1RXIP<2:0 | >      | _      |        | SPI1IP<2:0     | )>     | _     |        | SPI1EIP<2:0     | >             |        |          | T3IP<2:0>    |         | 4444         |

| IPC3         | 0846  | _      | _      | _          | _      | _      | C      | MA1IP<2:       | 0>     | _     |        | AD1IP<2:0>      |               |        |          | U1TXIP<2:0>  |         | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0       | >      | _     |        | MI2C1IP<2:0     | >             |        | 5        | SI2C1IP<2:0> |         | 4444         |

| IPC5         | 084A  | _      | _      | _          | _      | _      |        | _              | _      | _     | _      | _               | _             |        |          | INT1IP<2:0>  |         | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0      | >      | _     |        | OC3IP<2:0>      |               |        | [        | DMA2IP<2:0>  |         | 4444         |

| IPC7         | 084E  | _      | 1      | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:      | 0>     | _     |        | INT2IP<2:0>     |               |        |          | T5IP<2:0>    |         | 4444         |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |        | _      | C      | 2:<br>2:<br>2: | 0>     | _     |        | SPI2IP<2:0>     |               |        | 5        | SPI2EIP<2:0> |         | 4444         |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0      | >      | _     |        | IC3IP<2:0>      |               |        | [        | DMA3IP<2:0>  |         | 0444         |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | 112C2IP<2:     | 0>     | _     |        | SI2C2IP<2:0     | >             | _      | _        | _            | _       | 0440         |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:(     | )>     | _     |        | PSEMIP<2:0      | >             | _      | _        | _            | _       | 0440         |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0      |        | _     |        | U1EIP<2:0>      |               | _      | <u> </u> | _            | _       | 4440         |

| IPC17        | 0862  | _      | _      | _          | _      | _      |        | C1TXIP<2:      |        | _     | _      | _               | —             | _      | _        | _            | _       | 0400         |

| IPC19        | 0866  | _      | _      |            | _      | _      |        |                |        |       |        | L<br>CTMUIP<2:0 | >             |        | <u> </u> | _            | _       | 0040         |

## TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

# TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                                                     | Bit 8                                                | Bit 7 | Bit 6 | Bit 5     | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|-----------------------------------------------------------|------------------------------------------------------|-------|-------|-----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —                                                         | _                                                    |       |       |           | I2C1 Recei   | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —                                                         | _                                                    |       |       |           | I2C1 Transi  | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _                                                         |                                                      |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                                                    | DISSLW SMEN GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN |       |       |           |              |              |       | 1000  |       |               |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                                                    | ADD10                                                | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      | I2C1 Address Register                                     |                                                      |       |       |           |              |              | 0000  |       |       |               |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |                                                           |                                                      |       |       | I2C1 Add  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _                                                         | _                                                    |       |       |           | I2C2 Recei   | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _                                                         | _                                                    |       |       |           | I2C2 Transi  | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _                                                         |                                                      |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | I DISSLW SMEN GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN 10 |                                                      |       |       |           |              | 1000         |       |       |       |               |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT ADD10 IWCOL I2COV D_A P S R_W RBF TBF 00           |                                                      |       |       |           |              | 0000         |       |       |       |               |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      |                                                           |                                                      |       |       | I2C2 Addr | ess Register | r            |       |       |       | 0000          |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | _      | - I2C2 Address Mask 000                                   |                                                      |       |       |           |              | 0000         |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr.                                | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9                    | Bit 8                                                    | Bit 7 | Bit 6    | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|--------------------------------------|----------|--------|----------|--------|--------|--------|--------------------------|----------------------------------------------------------|-------|----------|-------|--------|-------|-------|--------|-------|---------------|

| U1MODE      | 0220                                 | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN<                     | :1:0>                                                    | WAKE  | LPBACK   | ABAUD | URXINV | BRGH  | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222                                 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                    | UTXBF TRMT URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXDA |       |          |       |        |       | 0110  |        |       |               |

| U1TXREG     | 0224                                 | _        | _      | _        | _      | _      | _      | UART1 Transmit Register  |                                                          |       |          |       |        |       | xxxx  |        |       |               |

| U1RXREG     | 0226                                 | _        | _      | _        | _      | _      | _      | UART1 Receive Register   |                                                          |       |          |       |        |       | 0000  |        |       |               |

| U1BRG       | 0228                                 |          |        |          |        |        |        |                          |                                                          |       |          |       |        |       |       | 0000   |       |               |

| U2MODE      | 0230                                 | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN<                     | :1:0>                                                    | WAKE  | LPBACK   | ABAUD | URXINV | BRGH  | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232                                 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                    | TRMT                                                     | URXIS | SEL<1:0> | ADDEN | RIDLE  | PERR  | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234                                 | _        | _      | _        | _      | _      | _      | UART2 Transmit Register  |                                                          |       |          |       |        |       | xxxx  |        |       |               |

| U2RXREG     | 0236                                 | _        | _      | _        | _      | —      | _      | UART2 Receive Register 0 |                                                          |       |          |       |        |       | 0000  |        |       |               |

| U2BRG       | 0238 Baud Rate Generator Prescaler 0 |          |        |          |        |        |        |                          |                                                          |       |          | 0000  |        |       |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

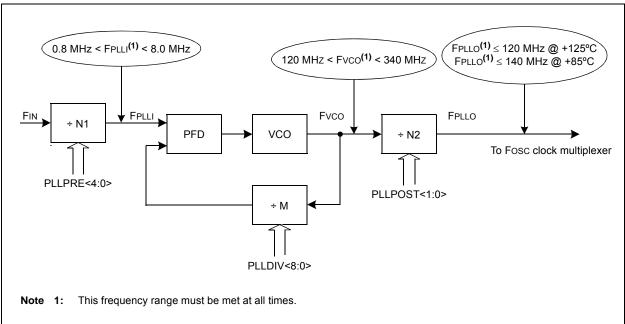

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

## EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

# FIGURE 9-2: PLL BLOCK DIAGRAM

## REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          | -               | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     |       |       | —          | —     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

#### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

#### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| 0-0     | 0-0   | 0-0   | 0-0   | 0-0        | 0-0   | 0-0   | 0-0   |

|         | —     |       | _     | _          | —     | —     |       |

| bit 15  |       |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —       |       |       |       | U2RXR<6:0> | >     |       |       |

| bit 7   |       |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Legend: |       |       |       |            |       |       |       |

|         |       |       |       |            |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

<sup>0000000 =</sup> Input tied to Vss

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|------------|------------------|----------------|-------------------|------------------|-----------------|-------|

| _             | —          |                  |                | RP39              | R<5:0>           |                 |       |

| bit 15        |            |                  |                |                   |                  |                 | bit 8 |

|               |            |                  |                |                   |                  |                 |       |

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| —             | —          |                  |                | RP38              | R<5:0>           |                 |       |

| bit 7         |            |                  |                |                   |                  |                 | bit 0 |

|               |            |                  |                |                   |                  |                 |       |

| Legend:       |            |                  |                |                   |                  |                 |       |

| R = Readable  | e bit      | W = Writable     | bit            | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at | POR        | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|               |            |                  |                |                   |                  |                 |       |

| bit 15-14     | Unimplemer | nted: Read as '  | 0'             |                   |                  |                 |       |

| bit 13-8      | RP39R<5:0> | : Peripheral Ou  | Itput Function | n is Assigned to  | RP39 Output F    | Pin bits        |       |

#### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

# 16.0 HIGH-SPEED PWM MODULE (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM generators

- Two PWM outputs per PWM generator

- Individual period and duty cycle for each PWM pair

- Duty cycle, dead time, phase shift and frequency resolution of Tcy/2 (7.14 ns at Fcy = 70MHz)

- Independent Fault and current-limit inputs for six PWM outputs

- · Redundant output

- Center-Aligned PWM mode

- Output override control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for input clock

- PWMxL and PWMxH output pin swapping

- Independent PWM frequency, duty cycle and phase-shift changes for each PWM generator

- Dead-time compensation

- Enhanced Leading-Edge Blanking (LEB) functionality

- Frequency resolution enhancement

- PWM capture functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on either of the two master time bases.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNC01 pin is an output pin that provides a synchronous signal to an external device.

Figure 16-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

# 16.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs to include FLT1 and FLT2 which are remappable using the PPS feature, FLT3 and FLT4 which are available only on the larger 44-pin and 64-pin packages, and FLT32 which has been implemented with Class B safety features, and is available on a fixed pin on all dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

## 16.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

Note: The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCON<1:0>), regardless of the state of FLT32. NOTES:

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

## 27.2 User ID Words

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices contain four User ID Words, located at addresses, 0x800FF8 through 0x800FFE. The User ID Words can be used for storing product information such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

The User ID Words register map is shown in Table 27-3.

TABLE 27-3: USER ID WORDS REGISTER MAP

| File Name | Address  | Bits 23-16 | Bits 15-0 |

|-----------|----------|------------|-----------|

| FUID0     | 0x800FF8 | _          | UID0      |

| FUID1     | 0x800FFA | _          | UID1      |

| FUID2     | 0x800FFC | _          | UID2      |

| FUID3     | 0x800FFE | _          | UID3      |

**Legend:** — = unimplemented, read as '1'.

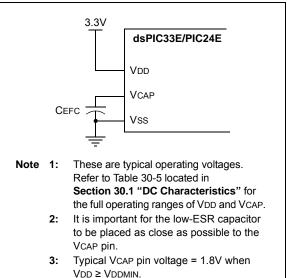

## 27.3 On-Chip Voltage Regulator

All of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family incorporate an onchip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5 located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

# FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE

REGULATOR<sup>(1,2,3)</sup>

# 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

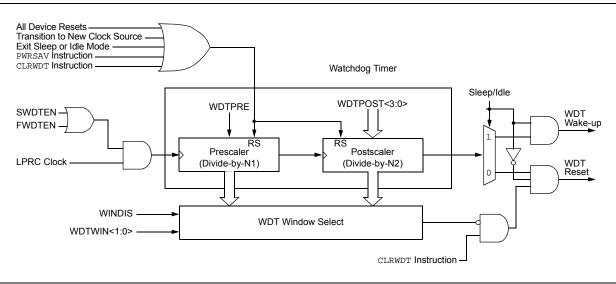

# 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

## FIGURE 27-2: WDT BLOCK DIAGRAM

# 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

# 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

## 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X AC characteristics and timing parameters.

### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated) |

|--------------------|--------------------------------------------------------------------------|

| AC CHARACTERISTICS | $\begin{array}{llllllllllllllllllllllllllllllllllll$                     |

|                    | Characteristics".                                                        |

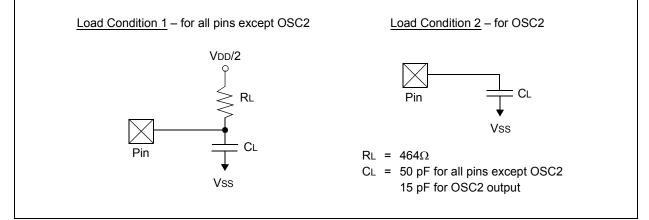

## FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

## TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   |       | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    |      | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                           |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CH/                    | ARACTERIS            | TICS                                                                   | Standard Op<br>(unless other<br>Operating ten | rwise st            | re -40°C ≤ TA                | ≤ +85°C | SV<br>for Industrial<br>C for Extended     |  |  |  |

|---------------------------|----------------------|------------------------------------------------------------------------|-----------------------------------------------|---------------------|------------------------------|---------|--------------------------------------------|--|--|--|

| Param<br>No.              | Symbol               | Characteristic                                                         | Min.                                          | Тур. <sup>(2)</sup> | Max.                         | Units   | Conditions                                 |  |  |  |

| Op Amp DC Characteristics |                      |                                                                        |                                               |                     |                              |         |                                            |  |  |  |

| CM40                      | VCMR                 | Common-Mode Input<br>Voltage Range                                     | AVss                                          | _                   | AVDD                         | V       |                                            |  |  |  |

| CM41                      | CMRR                 | Common-Mode<br>Rejection Ratio <sup>(3)</sup>                          | —                                             | 40                  | —                            | db      | VCM = AVDD/2                               |  |  |  |

| CM42                      | VOFFSET              | Op Amp Offset<br>Voltage <sup>(3)</sup>                                | —                                             | ±5                  | —                            | mV      |                                            |  |  |  |

| CM43                      | Vgain                | Open-Loop Voltage<br>Gain <sup>(3)</sup>                               | _                                             | 90                  | _                            | db      |                                            |  |  |  |

| CM44                      | los                  | Input Offset Current                                                   | _                                             | -                   | _                            | _       | See pad leakage currents in Table 30-11    |  |  |  |

| CM45                      | lв                   | Input Bias Current                                                     | —                                             | _                   | _                            | _       | See pad leakage currents in Table 30-11    |  |  |  |

| CM46                      | Ιουτ                 | Output Current                                                         | _                                             |                     | 420                          | μA      | With minimum value of RFEEDBACK (CM48)     |  |  |  |

| CM48                      | RFEEDBACK            | Feedback Resistance<br>Value                                           | 8                                             | -                   | _                            | kΩ      |                                            |  |  |  |

| CM49a                     | VOADC                | Output Voltage                                                         | AVss + 0.077                                  |                     | AVDD - 0.077                 | V       | Ιουτ = 420 μΑ                              |  |  |  |

|                           |                      | Measured at OAx Using ADC <sup>(3,4)</sup>                             | AVss + 0.037<br>AVss + 0.018                  |                     | AVDD – 0.037<br>AVDD – 0.018 | V<br>V  | ΙΟυΤ = 200 μΑ<br>Ιουτ = 100 μΑ             |  |  |  |

| CM49b                     | Vout                 | Output Voltage                                                         | AVss + 0.210                                  | _                   | AVDD - 0.210                 | V       | Ιουτ = 420 μΑ                              |  |  |  |

|                           |                      | Measured at OAxOUT<br>Pin <sup>(3,4,5)</sup>                           | AVss + 0.100<br>AVss + 0.050                  | _                   | AVDD – 0.100<br>AVDD – 0.050 | V<br>V  | Ιουτ = 200 μΑ<br>Ιουτ = 100 μΑ             |  |  |  |

| CM51                      | RINT1 <sup>(6)</sup> | Internal Resistance 1<br>(Configuration A<br>and B) <sup>(3,4,5)</sup> | 198                                           | 264                 | 317                          | Ω       | Min = -40°C<br>Typ = +25°C<br>Max = +125°C |  |  |  |

### TABLE 30-53: OP AMP/COMPARATOR SPECIFICATIONS (CONTINUED)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** Parameter is characterized but not tested in manufacturing.

- 4: See Figure 25-6 for configuration information.

- 5: See Figure 25-7 for configuration information.

- 6: Resistances can vary by ±10% between op amps.

| AC CHARACTERISTICS |                                           |                           |          | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ |          |                   |                                                  |  |  |  |  |

|--------------------|-------------------------------------------|---------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|--------------------------------------------------|--|--|--|--|

| Param<br>No.       | Symbol                                    | Characteristic            | Min      | Тур                                                                                                                                    | Max      | Units             | Conditions                                       |  |  |  |  |

|                    | ADC Accuracy (12-Bit Mode) <sup>(1)</sup> |                           |          |                                                                                                                                        |          |                   |                                                  |  |  |  |  |

| HAD20a             | Nr                                        | Resolution <sup>(3)</sup> | 12       | 2 Data B                                                                                                                               | its      | bits              |                                                  |  |  |  |  |

| HAD21a             | INL                                       | Integral Nonlinearity     | -5.5     | _                                                                                                                                      | 5.5      | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |  |

| HAD22a             | DNL                                       | Differential Nonlinearity | -1       | _                                                                                                                                      | 1        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |  |

| HAD23a             | Gerr                                      | Gain Error                | -10      |                                                                                                                                        | 10       | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |  |

| HAD24a             | EOFF                                      | Offset Error              | -5       | —                                                                                                                                      | 5        | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |  |

|                    |                                           | Dynamic I                 | Performa | nce (12-                                                                                                                               | Bit Mode | e) <sup>(2)</sup> |                                                  |  |  |  |  |

| HAD33a             | Fnyq                                      | Input Signal Bandwidth    | _        | _                                                                                                                                      | 200      | kHz               |                                                  |  |  |  |  |

# TABLE 31-12: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

## TABLE 31-13: ADC MODULE SPECIFICATIONS (10-BIT MODE)

| AC CHARACTERISTICS |        |                           |         | otherwi     | ise stated           | d)                | : <b>3.0V to 3.6V</b><br>TA ≤ +150°C             |

|--------------------|--------|---------------------------|---------|-------------|----------------------|-------------------|--------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic            | Min     | Min Typ Max |                      |                   | Conditions                                       |

|                    |        | ADC A                     | ccuracy | (10-Bit I   | Mode) <sup>(1)</sup> |                   |                                                  |

| HAD20b             | Nr     | Resolution <sup>(3)</sup> | 10      | ) Data B    | its                  | bits              |                                                  |

| HAD21b             | INL    | Integral Nonlinearity     | -1.5    | _           | 1.5                  | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD22b             | DNL    | Differential Nonlinearity | -0.25   | -           | 0.25                 | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

| HAD23b             | Gerr   | Gain Error                | -2.5    |             | 2.5                  | LSb               | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| HAD24b             | EOFF   | Offset Error              | -1.25   |             | 1.25                 | LSb               | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 3.6V |

|                    |        | Dynamic P                 | erforma | nce (10-    | Bit Mode             | e) <sup>(2)</sup> |                                                  |

| HAD33b             | Fnyq   | Input Signal Bandwidth    | _       | _           | 400                  | kHz               |                                                  |

Note 1: These parameters are characterized, but are tested at 20 ksps only.

2: These parameters are characterized by similarity, but are not tested in manufacturing.

3: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | N      | ILLIMETER      | S        |      |  |

|------------------------|--------|----------------|----------|------|--|

| Dimension              | Limits | MIN            | NOM      | MAX  |  |

| Number of Pins         | N      |                | 64       |      |  |

| Pitch                  | е      |                | 0.50 BSC |      |  |

| Overall Height         | A      | 0.80           | 0.90     | 1.00 |  |

| Standoff               | A1     | 0.00           | 0.02     | 0.05 |  |

| Contact Thickness      | A3     | 0.20 REF       |          |      |  |

| Overall Width          | E      |                | 9.00 BSC |      |  |

| Exposed Pad Width      | E2     | 5.30           | 5.40     | 5.50 |  |

| Overall Length         | D      |                | 9.00 BSC |      |  |

| Exposed Pad Length     | D2     | 5.30           | 5.40     | 5.50 |  |

| Contact Width          | b      | 0.20 0.25 0.30 |          |      |  |

| Contact Length         | L      | 0.30 0.40 0.50 |          |      |  |

| Contact-to-Exposed Pad | K      | 0.20           | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.