#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decalis                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc202-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

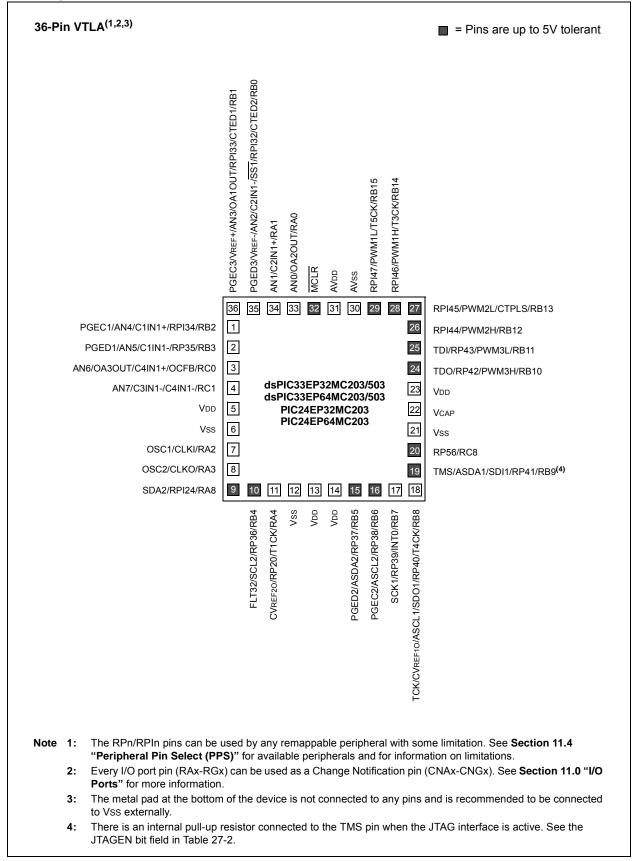

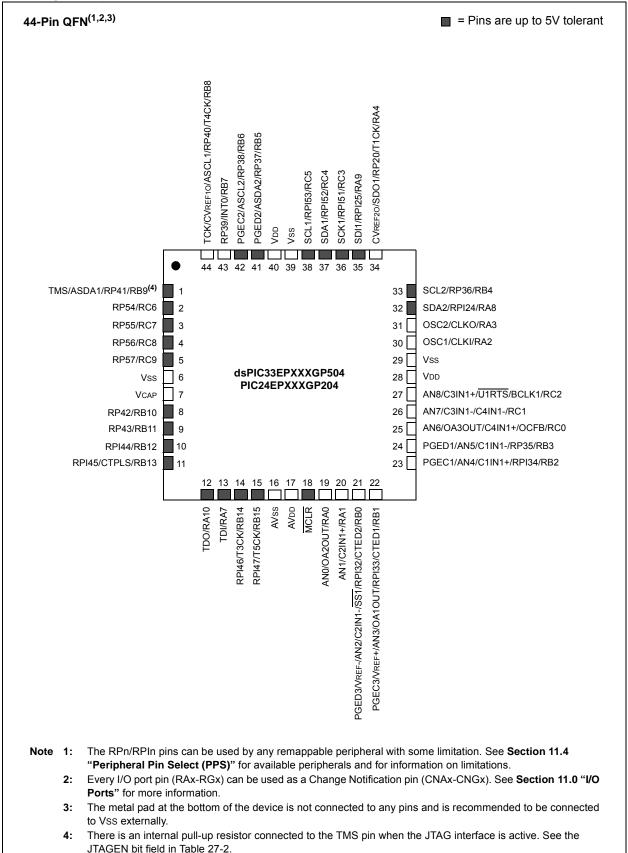

# Pin Diagrams (Continued)

### **Pin Diagrams (Continued)**

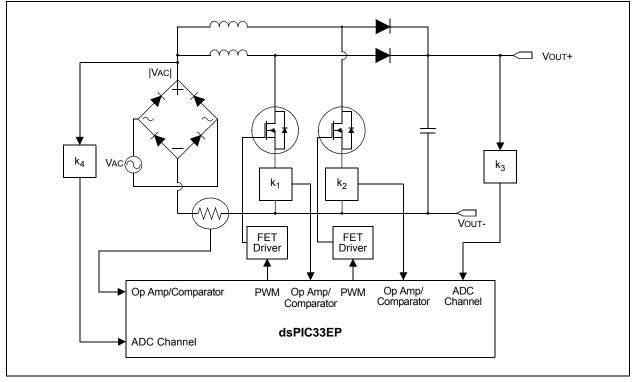

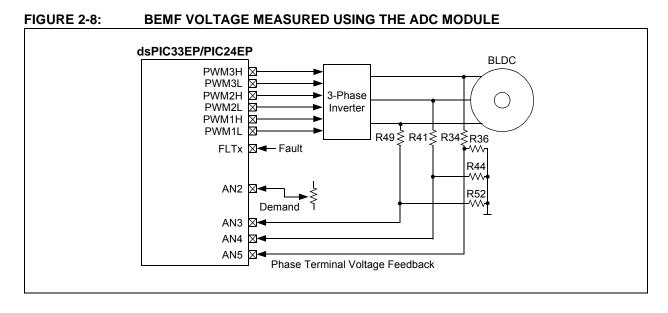

#### FIGURE 2-7: INTERLEAVED PFC

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|--------------|---------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  | _      |        | _          | _      | _      |        | _          | _      |       | IC4IF  | IC3IF       | DMA3IF | _      | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | QEI1IF | PSEMIF     | _      | _     | _      | _           | _      | _      | MI2C2IF  | SI2C2IF      | —       | 0000          |

| IFS4         | 0808  | -      | _      | CTMUIF     | _      | _      |        | —          | _      | _     |        | _           | _      | CRCIF  | U2EIF    | U1EIF        |         | 0000          |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            |         | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            | PWM3IF  | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      |        | —          | _      | _     |        | _           | _      | _      | _        | _            | _       | 0000          |

| IFS9         | 0812  | _      | _      | _          | -      | _      | _      | _          | _      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | —     | _      | —           | INT1IE | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | —          | -      | _      |        | —          | —      | _     | IC4IE  | IC3IE       | DMA3IE |        | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | -      | _      | QEI1IE | PSEMIE     | —      | _     | _      | —           | —      | -      | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | -      | _      |        | —          | —      | _     | _      | —           | _      | CRCIE  | U2EIE    | U1EIE        |         | 0000          |

| IEC5         | 082A  | PWM2IE | PWM1IE | —          | -      | _      | _      | _          | —      | _     | _      | —           | _      |        | _        | —            |         | 0000          |

| IEC6         | 082C  | _      | _      | _          | -      | _      | _      | _          | —      | _     | _      | —           | _      | -      | _        | _            | PWM3IE  | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | -      | _      | _      | _          | —      | _     | _      | —           | _      | -      | _        | _            | —       | 0000          |

| IEC9         | 0832  | _      | _      | _          | -      | _      | _      | _          | —      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE    |         | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0  | )>     | _     |        | IC1IP<2:0>  |        |        |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0  | )>     | _     |        | IC2IP<2:0>  |        | -      | [        | DMA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | -      | U1RXIP<2:0 | >      | _      | :      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | -      |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | —      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | -      |          | U1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0   | >      | _     |        | MI2C1IP<2:0 | >      | -      | 5        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | —      | _      |        | —          | —      | _     | _      | —           | —      | -      |          | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0  | )>     |       |        | OC3IP<2:0>  |        |        | [        | DMA2IP<2:0>  |         | 4444          |

| IPC7         | 084E  | _      |        | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:  | 0>     |       |        | INT2IP<2:0> | •      |        |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  | _      | _      | _          | —      | _      |        | —          | —      | _     |        | SPI2IP<2:0> | •      | -      | 5        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  | _      | _      | _          |        | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | -      | [        | DMA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  | _      | _      | _          |        | _      | N      | 112C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | -      | _        | —            |         | 0440          |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:0 | )>     | _     |        | PSEMIP<2:0  | >      | _      | _        | _            | _       | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _            | _       | 4440          |

| IPC19        | 0866  | _      | _      | —          | —      | _      | —      | —          | _      | _     |        | CTMUIP<2:0  | >      | _      | _        | _            | _       | 0040          |

| IPC23        | 086E  | _      | F      | PWM2IP<2:0 | )>     | _      | P      | WM1IP<2:   | 0>     | _     | _      | _           | —      | _      | _        | _            | _       | 4400          |

| IPC24        | 0870  | _      | _      |            |        | _      |        | _          |        |       | _      | _           | _      | _      | F        | PWM3IP<2:0>  |         | 4004          |

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6  | Bit 5       | Bit 4  | Bit 3  | Bit 2    | Bit 1       | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|--------|-------------|--------|--------|----------|-------------|---------------|---------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF  | IC2IF       | DMA0IF | T1IF   | OC1IF    | IC1IF       | <b>INTOIF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _      | _           | INT1IF | CNIF   | CMIF     | MI2C1IF     | SI2C1IF       | 0000          |

| IFS2         | 0804  | _      | _      | _          | _      | —      |        | _          | —      | _     | IC4IF  | IC3IF       | DMA3IF | C1IF   | C1RXIF   | SPI2IF      | SPI2EIF       | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | MI2C2IF  | SI2C2IF     | —             | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | —      |        | _          | —      | _     | C1TXIF | _           | —      | CRCIF  | U2EIF    | U1EIF       | —             | 0000          |

| IFS6         | 080C  | _      | _      | _          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | PWM3IF        | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | —          | _      | —      |        | _          | —      | _     | _      | _           | —      | _      | —        | _           | —             | 0000          |

| IFS9         | 0812  |        |        | _          | _      | _      | _      | _          | _      | _     | PTG3IF | PTG2IF      | PTG1IF | PTG0IF | PTGWDTIF | PTGSTEPIF   | _             | 0000          |

| IEC0         | 0820  |        | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE  | IC2IE       | DMA0IE | T1IE   | OC1IE    | IC1IE       | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _      | _           | INT1IE | CNIE   | CMIE     | MI2C1IE     | SI2C1IE       | 0000          |

| IEC2         | 0824  |        |        | _          | _      | _      | _      | _          | _      | _     | IC4IE  | IC3IE       | DMA3IE | C1IE   | C1RXIE   | SPI2IE      | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | _      | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | MI2C2IE  | SI2C2IE     | _             | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | —      |        |        |            | _      | —     | C1TXIE |             |        | CRCIE  | U2EIE    | U1EIE       |               | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | —          | —      |        | _      |            | _      | _     | _      |             |        | —      | _        | _           | _             | 0000          |

| IEC9         | 0832  | _      | _      | —          | —      |        | _      |            | _      | _     | PTG3IE | PTG2IE      | PTG1IE | PTG0IE | PTGWDTIE | PTGSTEPIE   | _             | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  | >      | _      | (      | OC1IP<2:0  | >      | _     |        | IC1IP<2:0>  |        | _      |          | NT0IP<2:0>  |               | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  | >      | _      | (      | C2IP<2:0   | >      | _     |        | IC2IP<2:0>  |        | _      | D        | MA0IP<2:0>  |               | 4444          |

| IPC2         | 0844  |        | ι      | J1RXIP<2:0 | 0>     | _      | Ş      | SPI1IP<2:0 | )>     | _     |        | SPI1EIP<2:0 | >      | _      |          | T3IP<2:0>   |               | 4444          |

| IPC3         | 0846  |        |        | _          | _      | _      | C      | MA1IP<2:   | 0>     | _     |        | AD1IP<2:0>  |        | _      | U        | J1TXIP<2:0> |               | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0   | >      | _      |        | CMIP<2:0   | >      | _     | I      | WI2C1IP<2:0 | >      | _      | S        | I2C1IP<2:0> |               | 4444          |

| IPC5         | 084A  |        |        | _          | _      | _      | _      | _          | _      | _     | _      | _           | _      | _      |          | NT1IP<2:0>  |               | 0004          |

| IPC6         | 084C  |        |        | T4IP<2:0>  | >      | _      | (      | C4IP<2:0   | >      | _     |        | OC3IP<2:0>  |        | _      | D        | MA2IP<2:0>  |               | 4444          |

| IPC7         | 084E  |        | ι      | U2TXIP<2:( | )>     | _      | L      | I2RXIP<2:  | 0>     | _     |        | INT2IP<2:0> | •      | _      |          | T5IP<2:0>   |               | 4444          |

| IPC8         | 0850  |        |        | C1IP<2:0>  | >      | _      | C      | 1RXIP<2:   | 0>     | _     |        | SPI2IP<2:0> | •      | _      | S        | PI2EIP<2:0> |               | 4444          |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0  | >      | _     |        | IC3IP<2:0>  |        | _      | D        | MA3IP<2:0>  |               | 0444          |

| IPC11        | 0856  | _      | _      | _          | _      | _      |        | _          | —      | _     | _      | _           | —      | _      | _        | _           | _             | 0000          |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | II2C2IP<2: | 0>     | _     |        | SI2C2IP<2:0 | >      | _      | _        | _           | _             | 0440          |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>     | _      |        | U2EIP<2:0  | >      | _     |        | U1EIP<2:0>  |        | _      | _        | _           | _             | 4440          |

| IPC17        | 0862  | _      | _      | _          | _      | _      | C      | 1TXIP<2:   | )>     | _     | _      | _           | —      | _      | _        | _           | _             | 0400          |

| IPC19        | 0866  | _      | _      | —          | _      | _      |        | _          | —      | _     |        | CTMUIP<2:0  | >      | _      | —        |             |               | 0040          |

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>     | _      |        | ICDIP<2:0  | >      | _     | —      | —           | _      | _      | —        | _           | _             | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:  | 0>     | _      | PT     | GWDTIP<    | 2:0>   | _     | PT     | GSTEPIP<2   | :0>    | _      | _        | _           | _             | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | TG3IP<2:   | )>     | _     |        | PTG2IP<2:0  | >      | _      | Р        | TG1IP<2:0>  |               | 0444          |

#### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/S-0                | U-0                                                                    | U-0                             | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |

|----------------------|------------------------------------------------------------------------|---------------------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|

| FORCE <sup>(1)</sup> |                                                                        | _                               | _                     | —                |                  | _               |         |  |  |

| bit 15               |                                                                        |                                 |                       |                  |                  |                 | bit 8   |  |  |

|                      |                                                                        |                                 |                       |                  |                  |                 |         |  |  |

| R/W-0                | R/W-0                                                                  | R/W-0                           | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |

| IRQSEL7              | IRQSEL6                                                                | IRQSEL5                         | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |

| bit 7                |                                                                        |                                 |                       |                  |                  |                 | bit     |  |  |

| Legend:              |                                                                        | S = Settable b                  | oit                   |                  |                  |                 |         |  |  |

| R = Readable         | bit                                                                    | W = Writable                    | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |

| -n = Value at F      | POR                                                                    | '1' = Bit is set                |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |

|                      |                                                                        |                                 |                       |                  |                  |                 |         |  |  |

| bit 15               | FORCE: Force                                                           | e DMA Transfe                   | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |

|                      | 1 = Forces a                                                           | single DMA tra                  | insfer (Manua         | l mode)          |                  |                 |         |  |  |

|                      | 0 = Automatic DMA transfer initiation by DMA request                   |                                 |                       |                  |                  |                 |         |  |  |

| bit 14-8             | t 14-8 Unimplemented: Read as '0'                                      |                                 |                       |                  |                  |                 |         |  |  |

| bit 7-0              | IRQSEL<7:0>                                                            | -: DMA Periphe                  | eral IRQ Num          | ber Select bits  |                  |                 |         |  |  |

|                      |                                                                        | ECAN1 – TX D                    |                       | 2)               |                  |                 |         |  |  |

|                      |                                                                        | IC4 – Input Ca                  |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | IC3 – Input Ca                  |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | ECAN1 – RX D<br>SPI2 Transfer I | -                     |                  |                  |                 |         |  |  |

|                      |                                                                        | UART2TX – UA                    |                       | itter            |                  |                 |         |  |  |

|                      |                                                                        | UART2RX – U                     |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | TMR5 – Timer5                   |                       |                  |                  |                 |         |  |  |

|                      | 00011011 =                                                             | TMR4 – Timer4                   | 1                     |                  |                  |                 |         |  |  |

|                      |                                                                        | OC4 – Output (                  |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | OC3 – Output (                  |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | ADC1 – ADC1                     |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | UART1TX – UA                    |                       |                  |                  |                 |         |  |  |

|                      | 00001011 = UART1RX – UART1 Receiver<br>00001010 = SPI1 – Transfer Done |                                 |                       |                  |                  |                 |         |  |  |

|                      | 00001010 = TMR3 - Timer3                                               |                                 |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | TMR2 – Timer2                   |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | OC2 – Output (                  |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | IC2 – Input Ca                  |                       |                  |                  |                 |         |  |  |

|                      | 00000010 = OC1 – Output Compare 1                                      |                                 |                       |                  |                  |                 |         |  |  |

|                      |                                                                        | IC1 – Input Ca                  |                       |                  |                  |                 |         |  |  |

|                      | 00000000 =                                                             | INT0 – Externa                  | I Interrupt 0         |                  |                  |                 |         |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

## REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          | -               | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

| R/W-0              | U-0                  | R/W-0                 | U-0                   | U-0 | U-0 | U-0                  | U-0   |

|--------------------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| TON <sup>(1)</sup> | —                    | TSIDL <sup>(2)</sup>  | —                     | —   | —   | —                    | —     |

| bit 15             |                      |                       |                       |     |     |                      | bit 8 |

|                    |                      |                       |                       |     |     |                      |       |

| U-0                | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

| —                  | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> |     | —   | TCS <sup>(1,3)</sup> | —     |

| bit 7              |                      |                       |                       |     |     |                      | bit 0 |

|                    |                      |                       |                       |     |     |                      |       |

#### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| Legend:      |                        |                                                                               |                                         |                                   |

|--------------|------------------------|-------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------|

| R = Readal   | ole bit                | W = Writable bit                                                              | U = Unimplemented bit                   | , read as '0'                     |

| -n = Value a | at POR                 | '1' = Bit is set                                                              | '0' = Bit is cleared                    | x = Bit is unknown                |

| bit 15       | TON: Tin               | nery On bit <sup>(1)</sup>                                                    |                                         |                                   |

|              |                        | s 16-bit Timery<br>s 16-bit Timery                                            |                                         |                                   |

| bit 14       | •                      | mented: Read as '0'                                                           |                                         |                                   |

| bit 13       | -                      | imery Stop in Idle Mode bit <sup>(2</sup>                                     | 2)                                      |                                   |

|              |                        | ontinues module operation winues module operation in Id                       | hen device enters Idle mode<br>lle mode |                                   |

| bit 12-7     | Unimple                | mented: Read as '0'                                                           |                                         |                                   |

| bit 6        | TGATE:                 | Timery Gated Time Accumu                                                      | lation Enable bit <sup>(1)</sup>        |                                   |

|              | When TC<br>This bit is | <u>CS = 1:</u><br>s ignored.                                                  |                                         |                                   |

|              |                        | <u>CS = 0:</u><br>d time accumulation is enab<br>d time accumulation is disab |                                         |                                   |

| bit 5-4      | TCKPS<                 | 1:0>: Timery Input Clock Pre                                                  | escale Select bits <sup>(1)</sup>       |                                   |

|              | 11 <b>= 1:2</b> 5      |                                                                               |                                         |                                   |

|              | 10 = 1:64<br>01 = 1:8  | 1                                                                             |                                         |                                   |

|              | 01 = 1.8               |                                                                               |                                         |                                   |

| bit 3-2      | Unimple                | mented: Read as '0'                                                           |                                         |                                   |

| bit 1        | -                      | nery Clock Source Select bit                                                  | (1,3)                                   |                                   |

|              |                        | nal clock is from pin, TyCK (<br>nal clock (FP)                               | (on the rising edge)                    |                                   |

| bit 0        | Unimple                | mented: Read as '0'                                                           |                                         |                                   |

|              |                        | peration is enabled (T2CON<br>set through TxCON.                              | <3> = 1), these bits have no e          | ffect on Timery operation; all ti |

|              |                        |                                                                               |                                         |                                   |

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

# REGISTER 16-13: IOCONX: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 OSYNC: Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx period boundary

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|       | R/W-0            | R/W-0           | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                | R/W-0                                                                                                    |

|-------|------------------|-----------------|---------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|       |                  | QEIG            | EC<31:24>                             |                                                                  |                                                                                                      |                                                                                                          |

|       |                  |                 |                                       |                                                                  |                                                                                                      | bit 8                                                                                                    |

|       | DAMO             |                 |                                       |                                                                  | DAMO                                                                                                 |                                                                                                          |

| R/W-U | R/W-0            |                 |                                       | R/W-U                                                            | R/W-U                                                                                                | R/W-0                                                                                                    |

|       |                  | QEIGE           | EC<23:16>                             |                                                                  |                                                                                                      |                                                                                                          |

|       |                  |                 |                                       |                                                                  |                                                                                                      | bit (                                                                                                    |

|       |                  |                 |                                       |                                                                  |                                                                                                      |                                                                                                          |

|       | W = Writable bi  | t               | U = Unimplem                          | nented bit, rea                                                  | d as '0'                                                                                             |                                                                                                          |

| २     | '1' = Bit is set |                 | '0' = Bit is clea                     | ared                                                             | x = Bit is unkn                                                                                      | iown                                                                                                     |

|       | R/W-0            | W = Writable bi | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit     U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |

### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

#### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | QEIGE | C<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | QEIG  | EC<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

# 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 23.1 Key Features

# 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

# 23.4 ADC Control Registers

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                        | R/W-0                               | R/W-0               | U-0               | R/W-0            | R/W-0                               | R/W-0               |

|---------------|----------------------------|-------------------------------------|---------------------|-------------------|------------------|-------------------------------------|---------------------|

| ADON          | —                          | ADSIDL                              | ADDMABM             |                   | AD12B            | FORM1                               | FORM0               |

| bit 15        | •                          |                                     |                     |                   |                  |                                     | bit 8               |

| R/W-0         | R/W-0                      | R/W-0                               | R/W-0               | R/W-0             | R/W-0            | R/W-0, HC, HS                       | R/C-0. HC. HS       |

| SSRC2         | SSRC1                      | SSRC0                               | SSRCG               | SIMSAM            | ASAM             | SAMP                                | DONE <sup>(3)</sup> |

| bit 7         |                            |                                     |                     |                   |                  |                                     | bit (               |

| Legend:       |                            | HC - Hardwar                        | e Clearable bit     | HS - Hardwa       | re Settable bit  | C = Clearable bi                    | +                   |

| R = Readable  | a hit                      | W = Writable b                      |                     |                   | nented bit, read |                                     | L                   |

| -n = Value at |                            | '1' = Bit is set                    | nt -                | '0' = Bit is clea |                  | x = Bit is unknov                   | vp.                 |

|               | FUR                        | I - DILIS SEL                       |                     |                   | aieu             |                                     |                     |

| bit 15        | ADON: ADO                  | C1 Operating M                      | ode bit             |                   |                  |                                     |                     |

|               | 1 = ADC mo<br>0 = ADC is 0 | odule is operatir<br>off            | ng                  |                   |                  |                                     |                     |

| bit 14        | Unimpleme                  | nted: Read as                       | <b>'</b> 0 <b>'</b> |                   |                  |                                     |                     |

| bit 13        | ADSIDL: A                  | DC1 Stop in Idle                    | e Mode bit          |                   |                  |                                     |                     |

|               | 1 = Disconti               | nues module oj                      | peration when o     | device enters     | ldle mode        |                                     |                     |

|               | 0 = Continu                | es module oper                      | ation in Idle mo    | ode               |                  |                                     |                     |

| bit 12        |                            | : DMA Buffer B                      |                     |                   |                  |                                     |                     |

|               |                            |                                     |                     |                   |                  | rovides an addre                    | ess to the DM       |

|               |                            |                                     |                     |                   |                  | nd-alone buffer<br>des a Scatter/Ga | ther address t      |

|               |                            |                                     |                     |                   |                  | size of the DMA b                   |                     |

| bit 11        |                            | nted: Read as                       |                     |                   |                  |                                     |                     |

| bit 10        | AD12B: AD                  | C1 10-Bit or 12                     | -Bit Operation I    | Mode bit          |                  |                                     |                     |

|               |                            | -channel ADC                        | -                   |                   |                  |                                     |                     |

|               | 0 = 10-bit, 4              | -channel ADC                        | operation           |                   |                  |                                     |                     |

| bit 9-8       | FORM<1:0>                  | Data Output I                       | Format bits         |                   |                  |                                     |                     |

|               | For 10-Bit C               |                                     |                     |                   |                  |                                     |                     |

|               |                            | l fractional (Dou<br>nal (Dou⊤ = dd |                     |                   | 0, where s = .I  | NOT.d<9>)                           |                     |

|               |                            | l integer (DOUT                     |                     |                   | where $s = .NC$  | (<9>)                               |                     |

|               |                            | r (Dout = 0000                      |                     |                   |                  |                                     |                     |

|               | For 12-Bit C               | peration:                           |                     |                   |                  |                                     |                     |

|               | •                          | fractional (Dou                     |                     |                   | 0, where s = .I  | NOT.d<11>)                          |                     |

|               |                            |                                     |                     |                   |                  |                                     |                     |

|               |                            | nal (Dout = dd<br>I integer (Dout   |                     |                   |                  | (<11>)                              |                     |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 3: Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0

**CH123SA:** Channel 1, 2, 3 Positive Input Select for Sample MUXA bit In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value          |             | ADC Channel |         |  |  |  |  |

|----------------|-------------|-------------|---------|--|--|--|--|

| value          | CH1 CH2 CH3 |             |         |  |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0     | OA3/AN6 |  |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1         | AN2     |  |  |  |  |

**Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                                           | Description                                                | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|-------------------------------------------|------------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 9                  | BTG                  | BTG f,#bit4     |                                           | Bit Toggle f                                               | 1             | 1                             | None                     |

|                    |                      | BTG             | Ws,#bit4                                  | Bit Toggle Ws                                              | 1             | 1                             | None                     |

| 10                 | BTSC                 | BTSC            | f,#bit4                                   | Bit Test f, Skip if Clear                                  | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSC            | Ws,#bit4                                  | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)                 | None                     |

| 11                 | BTSS                 | BTSS            | f,#bit4                                   | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSS            | Ws,#bit4                                  | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)                 | None                     |

| 12                 | BTST                 | BTST            | f,#bit4                                   | Bit Test f                                                 | 1             | 1                             | Z                        |

|                    |                      | BTST.C          | Ws,#bit4                                  | Bit Test Ws to C                                           | 1             | 1                             | С                        |

|                    |                      | BTST.Z          | Ws,#bit4                                  | Bit Test Ws to Z                                           | 1             | 1                             | Z                        |

|                    |                      | BTST.C          | Ws,Wb                                     | Bit Test Ws <wb> to C</wb>                                 | 1             | 1                             | С                        |

|                    |                      | BTST.Z          | Ws,Wb                                     | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1                             | Z                        |

| 13                 | BTSTS                | BTSTS           | f,#bit4                                   | Bit Test then Set f                                        | 1             | 1                             | Z                        |

|                    |                      | BTSTS.C         | Ws,#bit4                                  | Bit Test Ws to C, then Set                                 | 1             | 1                             | С                        |

|                    |                      | BTSTS.Z         | Ws,#bit4                                  | Bit Test Ws to Z, then Set                                 | 1             | 1                             | Z                        |

| 14                 | CALL                 | CALL            | lit23                                     | Call subroutine                                            | 2             | 4                             | SFA                      |

|                    |                      | CALL            | Wn                                        | Call indirect subroutine                                   | 1             | 4                             | SFA                      |

|                    |                      | CALL.L          | Wn                                        | Call indirect subroutine (long address)                    | 1             | 4                             | SFA                      |

| 15                 | CLR                  | CLR             | f                                         | f = 0x0000                                                 | 1             | 1                             | None                     |

|                    |                      | CLR             | WREG                                      | WREG = 0x0000                                              | 1             | 1                             | None                     |

|                    |                      | CLR             | Ws                                        | Ws = 0x0000                                                | 1             | 1                             | None                     |

|                    |                      | CLR             | Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Clear Accumulator                                          | 1             | 1                             | OA,OB,SA,SB              |

| 16                 | CLRWDT               | CLRWDT          |                                           | Clear Watchdog Timer                                       | 1             | 1                             | WDTO,Sleep               |

| 17                 | СОМ                  | COM             | f                                         | f = f                                                      | 1             | 1                             | N,Z                      |

|                    |                      | COM             | f,WREG                                    | WREG = f                                                   | 1             | 1                             | N,Z                      |

|                    |                      | COM             | Ws,Wd                                     | $Wd = \overline{Ws}$                                       | 1             | 1                             | N,Z                      |

| 18                 | CP                   | CP              | f                                         | Compare f with WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CP              | Wb,#lit8                                  | Compare Wb with lit8                                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CP              | Wb,Ws                                     | Compare Wb with Ws (Wb – Ws)                               | 1             | 1                             | C,DC,N,OV,Z              |

| 19                 | CP0                  | CPO             | f                                         | Compare f with 0x0000                                      | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CPO             | Ws                                        | Compare Ws with 0x0000                                     | 1             | 1                             | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB             | f                                         | Compare f with WREG, with Borrow                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CPB             | Wb,#lit8                                  | Compare Wb with lit8, with Borrow                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CPB             | Wb,Ws                                     | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ           | Wb,Wn                                     | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBEQ                | CPBEQ           | Wb,Wn,Expr                                | Compare Wb with Wn, branch if =                            | 1             | 1 (5)                         | None                     |

| 22                 | CPSGT                | CPSGT           | Wb,Wn                                     | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBGT                | CPBGT           | Wb,Wn,Expr                                | Compare Wb with Wn, branch if >                            | 1             | 1 (5)                         | None                     |

| 23                 | CPSLT                | CPSLT           | Wb,Wn                                     | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBLT                | CPBLT           | Wb,Wn,Expr                                | Compare Wb with Wn, branch if <                            | 1             | 1 (5)                         | None                     |

| 24                 | CPSNE                | CPSNE           | Wb,Wn                                     | Compare Wb with Wn, skip if ≠                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBNE                | CPBNE           | Wb,Wn,Expr                                | Compare Wb with Wn, branch if ≠                            | 1             | 1 (5)                         | None                     |

| <b>TABLE 28-2:</b> | <b>INSTRUCTION SET OVERVIEW (</b> | CONTINUED) | ) |

|--------------------|-----------------------------------|------------|---|

|                    |                                   | CONTINUED  | , |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| DC CHARACTERISTICS |        |                                                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |                  |                                                                                                                                                                        |  |

|--------------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------|------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.             | Symbol | Characteristic                                                        | Min.                                                  | Тур. | Max. | Units Conditions |                                                                                                                                                                        |  |

| DO10 V             | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>              |                                                       |      | 0.4  | V                | VDD = 3.3V,<br>$IOL \le 6 \text{ mA}, -40^{\circ}\text{C} \le Ta \le +85^{\circ}\text{C}$<br>$IOL \le 5 \text{ mA}, +85^{\circ}\text{C} < Ta \le +125^{\circ}\text{C}$ |  |

|                    |        | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>              | _                                                     |      | 0.4  | V                |                                                                                                                                                                        |  |

| DO20               | Vон    | Output High Voltage<br>4x Source Driver Pins <sup>(2)</sup>           | 2.4                                                   |      | _    | V                | $IOH \ge -10 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup>           | 2.4                                                   | _    | —    | V                | $IOH \ge -15 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$                                                                                                                  |  |

| DO20A              | Voh1   | H1 <b>Output High Voltage</b><br>4x Source Driver Pins <sup>(2)</sup> | 1.5(1)                                                | _    |      | V                | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |  |

|                    |        |                                                                       | 2.0 <sup>(1)</sup>                                    | _    | _    |                  | $IOH \ge -12 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                   |  |

|                    |        |                                                                       | 3.0(1)                                                |      | —    |                  | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                                                    |  |

|                    |        | Output High Voltage<br>8x Source Driver Pins <sup>(3)</sup>           | 1.5 <sup>(1)</sup>                                    | —    | —    | V                | $IOH \geq -22  mA,  VDD = 3.3  V$                                                                                                                                      |  |

|                    |        |                                                                       | 2.0 <sup>(1)</sup>                                    | _    | —    |                  | IOH $\geq$ -18 mA, VDD = 3.3V                                                                                                                                          |  |

|                    |        |                                                                       | 3.0(1)                                                | _    | —    | 1                | IOH $\geq$ -10 mA, VDD = 3.3V                                                                                                                                          |  |

# TABLE 30-12: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes all I/O pins that are not 8x Sink Driver pins (see below).

Includes the following pins:

For devices with less than 64 pins: RA3, RA4, RA9, RB<7:15> and RC3

For 64-pin devices: RA4, RA9, RB<7:15>, RC3 and RC15

## TABLE 30-13: ELECTRICAL CHARACTERISTICS: BOR