Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

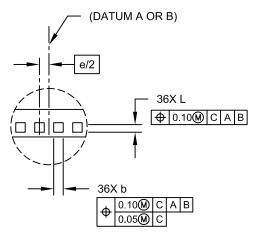

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc202-h-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES

| FA                | MIL                            | ES                            |              |                      |               |                |                                                |                              |        |                    |                  |                                    | _    | _                    | _                            | _                   |      |     | _        | _         |                                |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

|                   | ()                             | es)                           |              |                      |               | Rei            | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |      |                      | -                            |                     |      |     |          |           |                                |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I²C™ | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | PTG | I/O Pins | Pins      | Packages                       |

| PIC24EP32MC202    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC202    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| PIC24EP128MC202   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| PIC24EP256MC202   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512MC202   | 1024                           | 512                           | 48           | 8                    |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP32MC203    | 512                            | 32                            | 4            | -                    |               |                | <u> </u>                                       | ,                            | 6      | 6                  |                  | <u> </u>                           | 6    |                      | _                            | <i></i>             | v    | ~   | 0-       |           | ) (T) A                        |

| PIC24EP64MC203    | 1024                           | 64                            | 8            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| PIC24EP32MC204    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      | 1   |          |           |                                |

| PIC24EP64MC204    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| PIC24EP128MC204   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256MC204   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          | 40        | UQFN                           |

| PIC24EP512MC204   | 1024                           | 512                           | 48           | 48                   |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC206    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP128MC206   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 4                            | 2      | 2                  |                  | 2                                  | 2    | 1                    | 10                           | 2/4                 | Vaa  | Vaa | 50       | 64        | TQFP,                          |

| PIC24EP256MC206   | 1024                           | 256                           | 32           | 32                   | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2 1  | 16                   | 3/4                          | Yes                 | Yes  | 53  | 64       | QFN       |                                |

| PIC24EP512MC206   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC202  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC202  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC202 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3 <b>(1)</b>      | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC202 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC202 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC203  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  |                  | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC203  | 1024                           | 64                            | 8            | э                    | 4             | 4              | 0                                              | -                            | 2      | 2                  |                  | ა                                  | 2    | I                    | 0                            | 3/4                 | res  | tes | 25       | 30        | VILA                           |

| dsPIC33EP32MC204  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC204  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| dsPIC33EP128MC204 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | —                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256MC204 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | UQFN                           |

| dsPIC33EP512MC204 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC206  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP128MC206 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | TQFP,                          |

| dsPIC33EP256MC206 | 1024                           | 256                           | 32           | 5                    | +             | 1              | 0                                              | 1                            | 2      | 2                  |                  | 5                                  | 2    | · ·                  | 10                           | 5/4                 | 165  | 163 | 55       | 04        | QFN                            |

| dsPIC33EP512MC206 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC502  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC502  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,<br>SOIC,                |

| dsPIC33EP128MC502 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC502 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC502 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC503  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC503  | 1024                           | 64                            | 8            | ~                    |               |                |                                                |                              | -      | _                  |                  |                                    | _    |                      | Ĵ                            | <i></i>             |      |     |          |           |                                |

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details. 2: Only SPI2 is remappable.

**3:** INTO is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

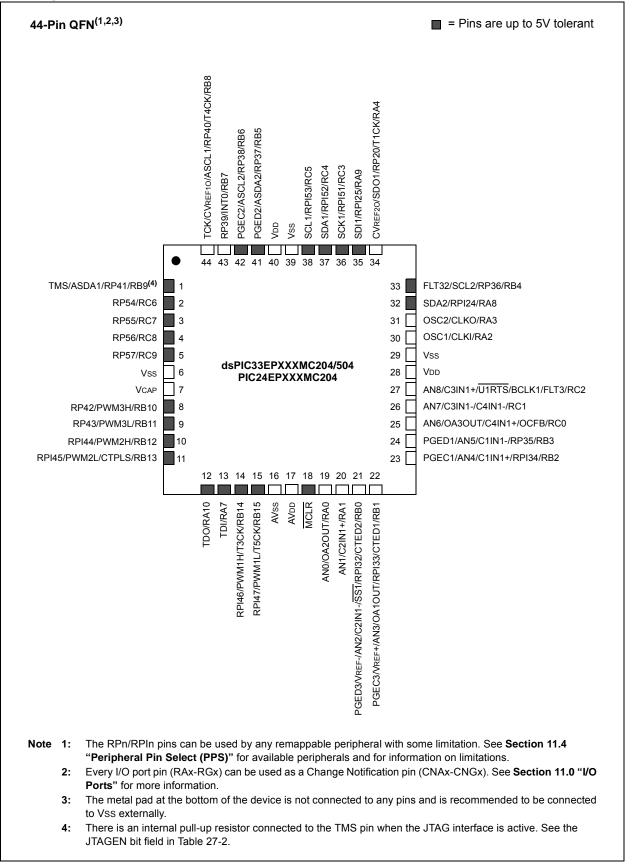

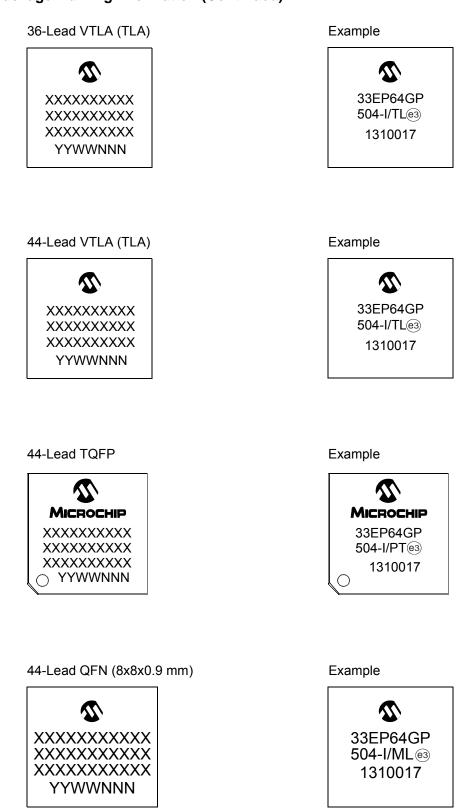

## Pin Diagrams (Continued)

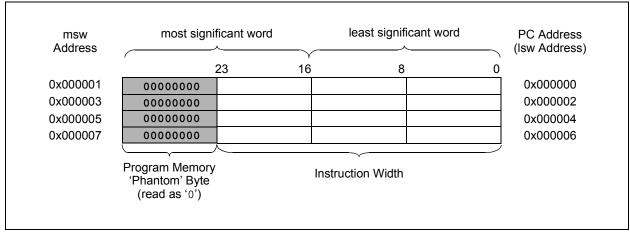

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

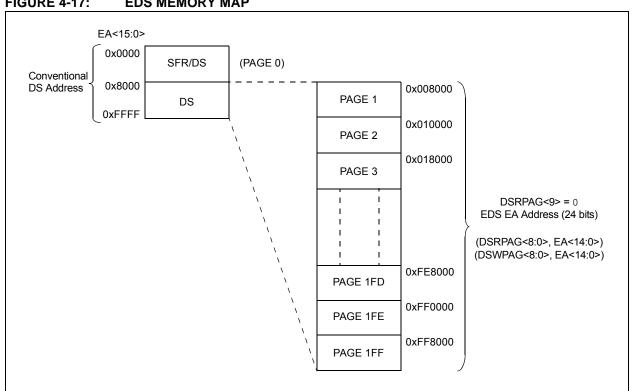

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

| -n = Value at POR '1' = Bit is set |                                   |       |       | '0' = Bit is cleared x = Bit is unknown |                                    |       |       |  |  |  |  |

|------------------------------------|-----------------------------------|-------|-------|-----------------------------------------|------------------------------------|-------|-------|--|--|--|--|

| R = Readable                       | R = Readable bit W = Writable bit |       |       |                                         | U = Unimplemented bit, read as '0' |       |       |  |  |  |  |

| Legend:                            |                                   |       |       |                                         |                                    |       |       |  |  |  |  |

|                                    |                                   |       |       |                                         |                                    |       |       |  |  |  |  |

| bit 7                              |                                   |       |       |                                         |                                    |       | bit C |  |  |  |  |

|                                    |                                   |       | NVMAD | )R<23:16>                               |                                    |       |       |  |  |  |  |

| R/W-x                              | R/W-x                             | R/W-x | R/W-x | R/W-x                                   | R/W-x                              | R/W-x | R/W-x |  |  |  |  |

| bit 15                             |                                   |       |       |                                         |                                    |       | bit 8 |  |  |  |  |

| _                                  | —                                 | —     | —     | —                                       | _                                  | —     | —     |  |  |  |  |

| U-0                                | U-0                               | U-0   | U-0   | U-0                                     | U-0                                | U-0   | U-0   |  |  |  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADR<23:16>:** Nonvolatile Memory Write Address High bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADRL: NONVOLATILE MEMORY ADDRESS REGISTER LOW

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                 | R/W-x | R/W-x | R/W-x |  |  |  |

|-----------------------------------|-------|------------------|-------|---------------------------------------|-------|-------|-------|--|--|--|

|                                   |       |                  | NVMA  | DR<15:8>                              |       |       |       |  |  |  |

| bit 15                            |       |                  |       |                                       |       |       | bit 8 |  |  |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                 | R/W-x | R/W-x | R/W-x |  |  |  |

|                                   |       |                  | NVMA  | DR<7:0>                               |       |       |       |  |  |  |

| bit 7                             |       |                  |       |                                       |       |       | bit 0 |  |  |  |

| Legend:                           |       |                  |       |                                       |       |       |       |  |  |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0'    |       |       |       |  |  |  |

| -n = Value at POR '1' = Bit is se |       | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unkno |       |       |       |  |  |  |

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address Low bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY

| U-0             | U-0 | U-0              | U-0  | U-0              | U-0             | U-0             | U-0   |

|-----------------|-----|------------------|------|------------------|-----------------|-----------------|-------|

| —               | —   | —                | —    | —                | —               | —               | —     |

| bit 15          |     |                  |      |                  |                 |                 | bit 8 |

|                 |     |                  |      |                  |                 |                 |       |

| W-0             | W-0 | W-0              | W-0  | W-0              | W-0             | W-0             | W-0   |

|                 |     |                  | NVMK | EY<7:0>          |                 |                 |       |

| bit 7           |     |                  |      |                  |                 |                 | bit 0 |

|                 |     |                  |      |                  |                 |                 |       |

| Legend:         |     |                  |      |                  |                 |                 |       |

| R = Readable I  | bit | W = Writable     | bit  | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

NOTES:

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | U-0                                                                                                                              | U-0                               | U-0                      | U-0                         | U-0  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|------|

|                                              | _                                                                                                                                                                            | _                                                                                                                                                                                                                            | _                                                                                                                                | _                                 | _                        | _                           | _    |

| bit 15                                       |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |

|                                              |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             |      |

| U-0                                          | U-0                                                                                                                                                                          | U-0                                                                                                                                                                                                                          | R/W-0                                                                                                                            | R/W-0                             | U-0                      | U-0                         | U-0  |

| _                                            | -                                                                                                                                                                            | _                                                                                                                                                                                                                            | DMA0MD <sup>(1)</sup><br>DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup>                                 | PTGMD                             | _                        | _                           | _    |

| bit 7                                        |                                                                                                                                                                              |                                                                                                                                                                                                                              |                                                                                                                                  |                                   |                          |                             | bit  |

| <b>Legend:</b><br>R = Readab<br>-n = Value a |                                                                                                                                                                              | W = Writable<br>'1' = Bit is set                                                                                                                                                                                             |                                                                                                                                  | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkn | iown |

| bit 15-5<br>bit 4                            | DMA0MD: DM<br>1 = DMA0 mo<br>0 = DMA0 mo<br>DMA1MD: DM<br>1 = DMA1 mo<br>0 = DMA1 mo<br>DMA2MD: DM<br>1 = DMA2 mo<br>0 = DMA2 mo<br>DMA3MD: DM<br>1 = DMA3 mo<br>0 = DMA3 mo | ted: Read as '<br>MA0 Module Di<br>odule is disable<br>odule is enable<br>MA1 Module Di<br>odule is disable<br>MA2 Module Di<br>odule is disable<br>odule is enable<br>MA3 Module Di<br>odule is disable<br>odule is disable | sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d<br>sable bit <sup>(1)</sup><br>d |                                   |                          |                             |      |

| bit 3                                        |                                                                                                                                                                              | Module Disat<br>ule is disabled<br>ule is enabled                                                                                                                                                                            | ole bit                                                                                                                          |                                   |                          |                             |      |

| bit 2-0                                      | Unimplement                                                                                                                                                                  | ted: Read as '                                                                                                                                                                                                               | 0'                                                                                                                               |                                   |                          |                             |      |

| Note 1: T                                    | his single bit ena                                                                                                                                                           | ables and disal                                                                                                                                                                                                              | oles all four DM                                                                                                                 | A channels.                       |                          |                             |      |

## REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

#### 11.4.4 INPUT MAPPING

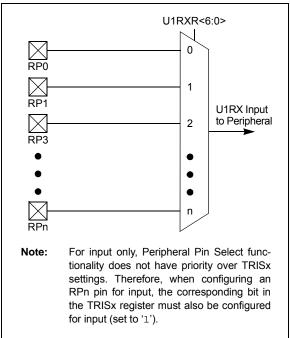

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | _                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | _                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         |     | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         |     | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

## REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|--------------|------------------|----------------------------------------------------------|-------|-------------------|-----------------|--------------------|-------|--|

|              |                  |                                                          |       | DTCMP3R<6:0       | )>              |                    |       |  |

| bit 15       |                  |                                                          |       |                   |                 |                    | bit 8 |  |

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

| 0-0          | R/W-0            | R/W-0                                                    | -     | DTCMP2R<6:0       |                 | R/W-0              | R/W-U |  |

| bit 7        |                  |                                                          |       |                   | 17              |                    | bit 0 |  |

| bit i        |                  |                                                          |       |                   |                 |                    | bit 0 |  |

| Legend:      |                  |                                                          |       |                   |                 |                    |       |  |

| R = Readab   | ole bit          | W = Writable                                             | bit   | U = Unimplem      | nented bit, rea | ad as '0'          |       |  |

| -n = Value a | at POR           | '1' = Bit is set                                         |       | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

|              |                  |                                                          |       |                   |                 |                    |       |  |

|              |                  | nput tied to CMI                                         |       |                   |                 |                    |       |  |

| bit 7        | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |                   |                 |                    |       |  |

| R/W-0         | R/W-0                                                                                                                                                                  | R/W-0                                      | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|--|

| QCAPEN        | FLTREN                                                                                                                                                                 | QFDIV2                                     | QFDIV1            | QFDIV0            | OUTFNC1          | OUTFNC0         | SWPAB |  |  |  |  |  |  |

| bit 15        | ·                                                                                                                                                                      | ·                                          |                   |                   |                  |                 | bit 8 |  |  |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                  | R/W-0                                      | R/W-0             | R-x               | R-x              | R-x             | R-x   |  |  |  |  |  |  |

| HOMPOL        | IDXPOL                                                                                                                                                                 | QEBPOL                                     | QEAPOL            | HOME              | INDEX            | QEB             | QEA   |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                                        |                                            |                   | TIOME             | INDEX            | QLD             | bit ( |  |  |  |  |  |  |

| Legend:       |                                                                                                                                                                        |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                                  | W = Writable                               | bit               | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |  |  |

| -n = Value at |                                                                                                                                                                        | '1' = Bit is set                           |                   | '0' = Bit is cle  |                  | x = Bit is unkn | own   |  |  |  |  |  |  |

|               |                                                                                                                                                                        |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| bit 15        | QCAPEN: Q                                                                                                                                                              | EI Position Cou                            | nter Input Cap    | ture Enable bit   |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                                                        | tch event trigge                           |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                                                        | tch event does                             |                   | -                 |                  |                 |       |  |  |  |  |  |  |

| bit 14        |                                                                                                                                                                        | Ax/QEBx/INDX                               | •                 | tal Filter Enable | e dit            |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                                                        | digital filter is e<br>digital filter is d |                   | sed)              |                  |                 |       |  |  |  |  |  |  |

| bit 13-11     | <ul> <li>0 = Input pin digital filter is disabled (bypassed)</li> <li>QFDIV&lt;2:0&gt;: QEAx/QEBx/INDXx/HOMEx Digital Input Filter Clock Divide Select bits</li> </ul> |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 111 = 1:128                                                                                                                                                            |                                            |                   | 9                 |                  |                 |       |  |  |  |  |  |  |

|               | 110 = 1:64 cl                                                                                                                                                          | lock divide                                |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 101 = 1:32 cl                                                                                                                                                          |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 100 = 1:16 cl                                                                                                                                                          |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 011 = 1:8 clock divide<br>010 = 1:4 clock divide                                                                                                                       |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 010 = 1.4 clock divide<br>001 = 1.2 clock divide                                                                                                                       |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 000 = 1:1 clo                                                                                                                                                          |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| bit 10-9      | OUTFNC<1:0>: QEI Module Output Function Mode Select bits                                                                                                               |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 11 = The CTNCMPx pin goes high when QEI1LEC $\geq$ POS1CNT $\geq$ QEI1GEC                                                                                              |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 10 = The CTNCMPx pin goes high when POS1CNT ≤ QEI1LEC                                                                                                                  |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 01 = The CTNCMPx pin goes high when POS1CNT ≥ QEI1GEC<br>00 = Output is disabled                                                                                       |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| L:1 0         | •                                                                                                                                                                      |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| bit 8         |                                                                                                                                                                        | ap QEA and QE                              | •                 |                   |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                                                                                        | d QEBx are sw<br>d QEBx are not            |                   | quadrature dec    | coder logic      |                 |       |  |  |  |  |  |  |

| bit 7         | HOMPOL: H                                                                                                                                                              | OMEx Input Po                              | larity Select bit |                   |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Input is in                                                                                                                                                        |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| bit 6         | 0 = Input is n                                                                                                                                                         |                                            | ty Soloot hit     |                   |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Input is in                                                                                                                                                        | OXx Input Polari                           | ly Select bit     |                   |                  |                 |       |  |  |  |  |  |  |

|               | 0 = Input is n                                                                                                                                                         |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| bit 5         | -                                                                                                                                                                      | EBx Input Polar                            | itv Select bit    |                   |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Input is i                                                                                                                                                         | •                                          | .,                |                   |                  |                 |       |  |  |  |  |  |  |

|               | 0 = Input is r                                                                                                                                                         |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| bit 4         | QEAPOL: Q                                                                                                                                                              | EAx Input Polar                            | ity Select bit    |                   |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Input is i                                                                                                                                                         |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

|               | 0 = Input is r                                                                                                                                                         | not inverted                               |                   |                   |                  |                 |       |  |  |  |  |  |  |

| bit 3         | HOME: Statu                                                                                                                                                            |                                            |                   |                   |                  |                 |       |  |  |  |  |  |  |

| DIL 3         | <b>HOME</b> . Statu                                                                                                                                                    |                                            | out Pin Alter Po  | olarity Control   |                  |                 |       |  |  |  |  |  |  |

| DIL 3         | 1 = Pin is at<br>0 = Pin is at                                                                                                                                         | logic '1'                                  | out Pin Aiter Po  | bianty Control    |                  |                 |       |  |  |  |  |  |  |

## REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER

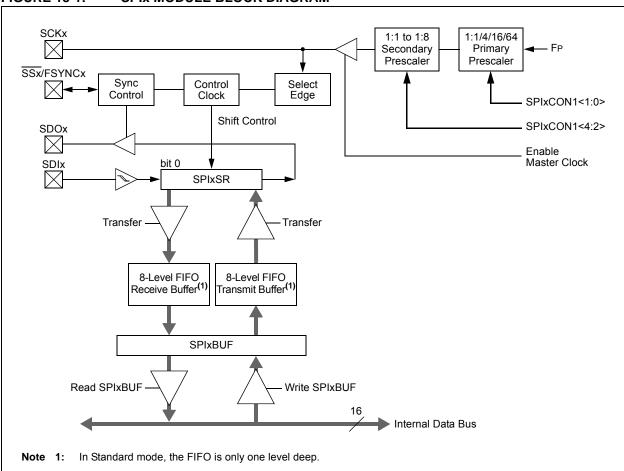

#### FIGURE 18-1: SPIx MODULE BLOCK DIAGRAM

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0    | R/W-0            | U-0             | R/W-0, HC                             | R/W-0                | R-0   | R-1   |

|---------------|----------|------------------|-----------------|---------------------------------------|----------------------|-------|-------|

| UTXISEL1      | UTXINV   | UTXISEL0         | —               | UTXBRK                                | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15        |          |                  |                 |                                       |                      |       | bit 8 |

|               |          |                  |                 |                                       |                      |       |       |

| R/W-0         | R/W-0    | R/W-0            | R-1             | R-0                                   | R-0                  | R/C-0 | R-0   |

| URXISEL1      | URXISEL0 | ADDEN            | RIDLE           | PERR                                  | FERR                 | OERR  | URXDA |

| bit 7         |          |                  |                 |                                       |                      |       | bit C |

|               |          |                  |                 |                                       |                      |       |       |

| Legend:       |          | HC = Hardward    | e Clearable bit | C = Clearable                         | e bit                |       |       |

| R = Readable  | e bit    | W = Writable b   | bit             | U = Unimplemented bit, read as '0'    |                      |       |       |

| -n = Value at | POR      | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is unkno |                      |       | nown  |

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

- $\frac{\text{If IREN = 0:}}{1 = \text{UxTX Idle state is '0'}}$

- 0 = UxTX Idle state is '1'

- If IREN = 1:

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 Unimplemented: Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup> 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled by the PORT

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

| Bit Field             | Description                                                                                                                                                                                   |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| WDTPRE                | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                         |  |

| WDTPOST<3:0>          | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                         |  |

| WDTWIN<1:0>           | Watchdog Window Select bits<br>11 = WDT window is 25% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period |  |

| ALTI2C1               | Alternate I2C1 pin<br>1 = I2C1 is mapped to the SDA1/SCL1 pins<br>0 = I2C1 is mapped to the ASDA1/ASCL1 pins                                                                                  |  |

| ALTI2C2               | Alternate I2C2 pin<br>1 = I2C2 is mapped to the SDA2/SCL2 pins<br>0 = I2C2 is mapped to the ASDA2/ASCL2 pins                                                                                  |  |

| JTAGEN <sup>(2)</sup> | JTAG Enable bit<br>1 = JTAG is enabled<br>0 = JTAG is disabled                                                                                                                                |  |

| ICS<1:0>              | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved, do not use       |  |

## TABLE 27-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

| DC CHARACTERISTICS |                     |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                |       |         |

|--------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|---------|

| Parameter<br>No.   | Тур.                | Max. | Units                                                                                                                                                                                                                                                                                   | its Conditions |       |         |

| Idle Current (III  | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |                |       |         |