Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc202-i-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES

| FA                | MIL                            | ES                            |              |                      |               |                |                                                |                              |        |                    |                  |                                    | _    | _                    | _                            | _                   |      |     | _        | _         |                                |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

|                   | ()                             | es)                           |              |                      |               | Rei            | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |      |                      | -                            |                     |      |     |          |           |                                |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I²C™ | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | PTG | I/O Pins | Pins      | Packages                       |

| PIC24EP32MC202    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC202    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

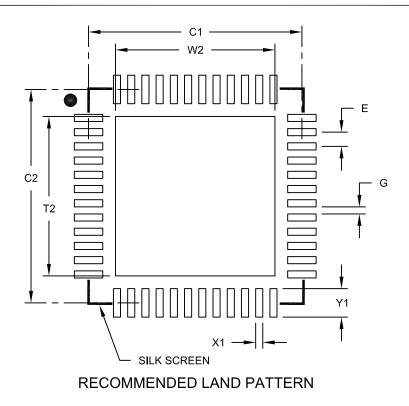

| PIC24EP128MC202   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| PIC24EP256MC202   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512MC202   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP32MC203    | 512                            | 32                            | 4            | -                    |               |                | <u> </u>                                       | ,                            | 6      | 6                  |                  | <u> </u>                           | 6    |                      | _                            |                     | v    | ~   | 0-       |           | ) (T) A                        |

| PIC24EP64MC203    | 1024                           | 64                            | 8            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| PIC24EP32MC204    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      | 1   |          |           |                                |

| PIC24EP64MC204    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| PIC24EP128MC204   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256MC204   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          | 40        | UQFN                           |

| PIC24EP512MC204   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC206    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP128MC206   | 1024                           | 128                           | 16           | F                    | 4             | 4              | 6                                              | 4                            | 2      | 2                  |                  | 2                                  | 2    | 1                    | 10                           | 2/4                 | Vaa  | Vaa | 50       | 64        | TQFP,                          |

| PIC24EP256MC206   | 1024                           | 256                           | 32           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| PIC24EP512MC206   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC202  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC202  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC202 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3 <b>(1)</b>      | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC202 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC202 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC203  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  |                  | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC203  | 1024                           | 64                            | 8            | э                    | 4             | 4              | 0                                              | -                            | 2      | 2                  |                  | ა                                  | 2    | I                    | 0                            | 3/4                 | res  | tes | 25       | 30        | VILA                           |

| dsPIC33EP32MC204  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC204  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| dsPIC33EP128MC204 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | —                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256MC204 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | UQFN                           |

| dsPIC33EP512MC204 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC206  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP128MC206 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | TQFP,                          |

| dsPIC33EP256MC206 | 1024                           | 256                           | 32           | 5                    | +             | 1              | 0                                              | 1                            | 2      | 2                  |                  | 5                                  | 2    | · ·                  | 10                           | 5/4                 | 165  | 163 | 55       | 04        | QFN                            |

| dsPIC33EP512MC206 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC502  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC502  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,<br>SOIC,                |

| dsPIC33EP128MC502 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC502 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC502 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC503  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC503  | 1024                           | 64                            | 8            | ~                    |               |                |                                                |                              | -      | _                  |                  |                                    | _    |                      | Ĵ                            | <i></i>             |      |     |          |           |                                |

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details. 2: Only SPI2 is remappable.

**3:** INTO is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

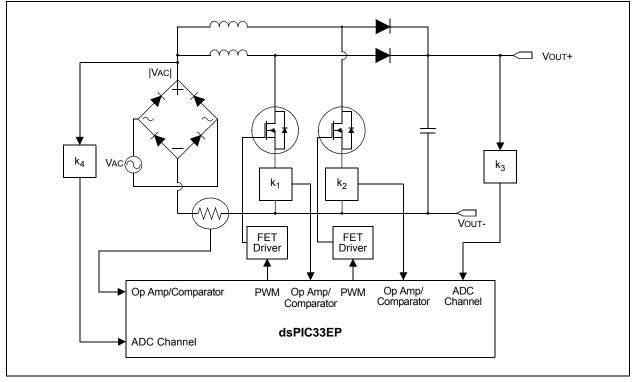

#### FIGURE 2-7: INTERLEAVED PFC

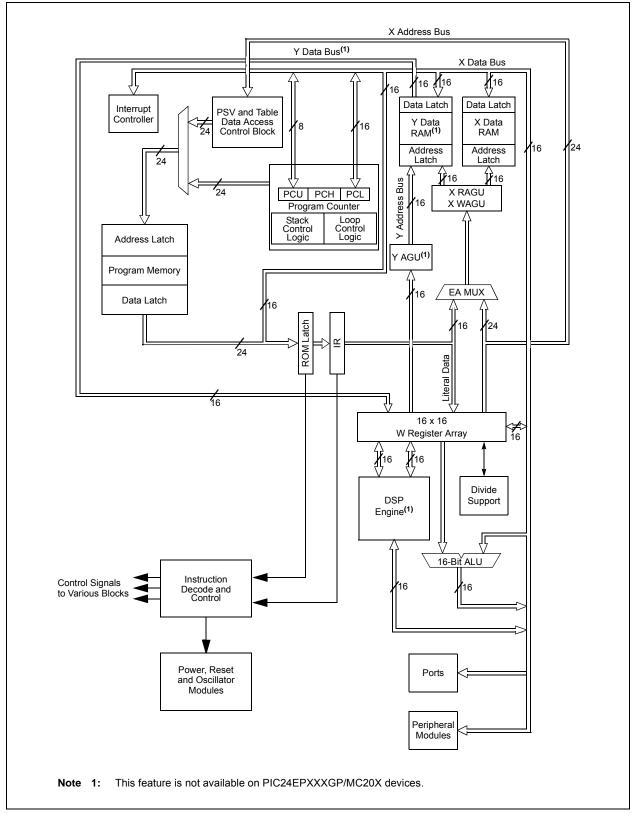

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

#### **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

| IABLE 4-2  | 23: E                     | CAN1 I                                                                                                        | REGIST | ER MA | P WHE | N WIN  | (CICIE | <l1<0></l1<0>                 | •) = 1 FC | OR dsPIC           | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|---------------------------|---------------------------------------------------------------------------------------------------------------|--------|-------|-------|--------|--------|-------------------------------|-----------|--------------------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr                      | Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8 |        |       |       |        |        |                               |           | Bit 7              | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | C1RXF11EID 046E EID<15:8> |                                                                                                               |        |       |       |        |        |                               |           | EID<               | 7:0>     |        |        |        | xxxx   |       |       |               |

| C1RXF12SID | 0470                      |                                                                                                               |        |       | SID<  | :10:3> |        |                               |           | SID<2:0> — EXIDE — |          |        |        |        | EID<1  | 7:16> | xxxx  |               |

| C1RXF12EID | 0472                      | 72 EID<15:8>                                                                                                  |        |       |       |        |        |                               |           | EID<7:0>           |          |        |        |        |        |       | xxxx  |               |

| C1RXF13SID | 0474                      |                                                                                                               |        |       | SID<  | :10:3> |        |                               |           | SID<2:0> — EXIDE   |          |        |        |        | —      | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476                      |                                                                                                               |        |       | EID<  | :15:8> |        |                               |           | EID<7:0>           |          |        |        |        |        | xxxx  |       |               |

| C1RXF14SID | 0478                      |                                                                                                               |        |       | SID<  | :10:3> |        |                               |           |                    | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A                      |                                                                                                               |        |       | EID<  | :15:8> |        |                               |           | EID<7:0>           |          |        |        |        |        | xxxx  |       |               |

| C1RXF15SID | 047C                      | 7C SID<10:3>                                                                                                  |        |       |       |        |        | SID<2:0> — EXIDE — EID<17:16> |           |                    |          |        | 7:16>  | xxxx   |        |       |       |               |

| C1RXF15EID | 047E                      |                                                                                                               |        |       | EID<  | :15:8> |        |                               |           |                    |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

#### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

#### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

#### REGISTER 11-16: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38 (dsPIC33EPXXXMC20X AND PIC24EPXXXMC20X DEVICES ONLY)

|              | -         |                                      |       |                  |                   | -               |                |

|--------------|-----------|--------------------------------------|-------|------------------|-------------------|-----------------|----------------|

| U-0          | R/W-0     | R/W-0                                | R/W-0 | R/W-0            | R/W-0             | R/W-0           | R/W-0          |

|              |           |                                      |       | DTCMP1R<6:       | 0>                |                 |                |

| bit 15       |           |                                      |       |                  |                   |                 | bit 8          |

|              |           |                                      |       |                  |                   |                 |                |

| U-0          | U-0       | U-0                                  | U-0   | U-0              | U-0               | U-0             | U-0            |

| —            | —         | —                                    | _     |                  | _                 | —               | —              |

| bit 7        |           |                                      |       |                  |                   |                 | bit C          |

|              |           |                                      |       |                  |                   |                 |                |

| Legend:      |           |                                      |       |                  |                   |                 |                |

| R = Readal   | ole bit   | W = Writable                         | bit   | U = Unimpler     | mented bit, read  | d as '0'        |                |

| -n = Value a | at POR    | '1' = Bit is set                     | :     | '0' = Bit is cle | ared              | x = Bit is unkr | nown           |

|              |           |                                      |       |                  |                   |                 |                |

| bit 15       | Unimpleme | nted: Read as '                      | 0'    |                  |                   |                 |                |

| bit 14-8     |           | 6:0>: Assign PV<br>1-2 for input pin |       | •                | on Input 1 to the | e Corresponding | g RPn Pin bits |

|              | 1111001 = | Input tied to RP                     | 1121  |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              | •         |                                      |       |                  |                   |                 |                |

|              |           | Input tied to CM                     | P1    |                  |                   |                 |                |

|              |           | Input tied to Vss                    |       |                  |                   |                 |                |

| bit 7-0      |           | nted: Read as '                      |       |                  |                   |                 |                |

|              |           |                                      | -     |                  |                   |                 |                |

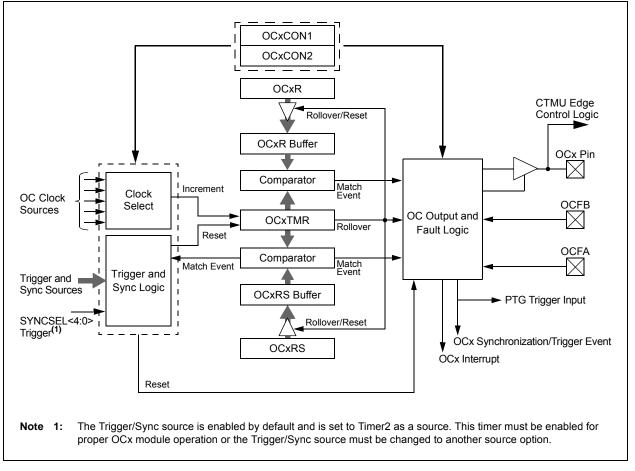

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

#### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

# 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

- 3: There are minimum bit rates of approximately FCY/512. As a result, high processor speeds may not support 100 Kbit/second operation. See timing specifications, IM10 and IM11, and the "Baud Rate Generator" in the "dsPIC33/PIC24 Family Reference Manual".

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two Inter-Integrated Circuit (I<sup>2</sup>C) modules: I2C1 and I2C2.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The  $I^2C$  module has a 2-pin interface:

- · The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

- Intelligent Platform Management Interface (IPMI)

support

- System Management Bus (SMBus) support

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | —   | _   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

|        |     |     |     |          |          |          |          |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 15-12 Unimplemented: Read as '0'

| DIL 15-12 | Unimplemented. Read as 0                                                                                                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                         |

|           | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

|           | 1110 <b>= FLT2</b>                                                                                                                                                                                                                             |

|           | 1101 <b>= PTGO19</b>                                                                                                                                                                                                                           |

|           | 1100 = PTGO18                                                                                                                                                                                                                                  |

|           | 1011 = Reserved                                                                                                                                                                                                                                |

|           | 1010 = Reserved                                                                                                                                                                                                                                |

|           | 1001 = Reserved                                                                                                                                                                                                                                |

|           | 1000 = Reserved                                                                                                                                                                                                                                |

|           | 0111 = Reserved                                                                                                                                                                                                                                |

|           | 0110 = Reserved                                                                                                                                                                                                                                |

|           | 0101 = PWM3H                                                                                                                                                                                                                                   |

|           | 0100 = PWM3L                                                                                                                                                                                                                                   |

|           | 0011 = PWM2H                                                                                                                                                                                                                                   |

|           | 0010 = PWM2L                                                                                                                                                                                                                                   |

|           | 0001 = PWM1H                                                                                                                                                                                                                                   |

|           | 0000 = PWM1L                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                         |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits 1111 = FLT4                                                                                                                                                                                             |

| bit 7-4   | •                                                                                                                                                                                                                                              |

| bit 7-4   | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2                                                                                                                                                                                                                     |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19                                                                                                                                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                          |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                       |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved                                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM1H |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

# 26.3 Programmable CRC Registers

#### REGISTER 26-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0                            | U-0                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R-0                                                                                      | R-0                                                | R-0             | R-0            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------|----------------|

| CRCEN                            | —                                                                                                                                                                                                                                                             | CSIDL                                                                                                                                                                                                                                                                  | VWORD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VWORD3                                                                                   | VWORD2                                             | VWORD1          | VWORD0         |

| bit 15                           | ·                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          |                                                    |                 | bit 8          |

| R-0                              | R-1                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                    | U-0                                                | U-0             | U-0            |

| CRCFUL                           | CRCMPT                                                                                                                                                                                                                                                        | CRCISEL                                                                                                                                                                                                                                                                | CRCGO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LENDIAN                                                                                  | _                                                  | _               | _              |

| bit 7                            | •                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          |                                                    |                 | bit (          |

| Legend:                          |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          |                                                    |                 |                |

| R = Readable                     | e bit                                                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                                           | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U = Unimplen                                                                             | nented bit, read                                   | d as '0'        |                |

| -n = Value at                    | POR                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | '0' = Bit is cle                                                                         | ared                                               | x = Bit is unkr | nown           |

| bit 15                           | 0 = CRC mo                                                                                                                                                                                                                                                    | dule is enabled                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | chines, pointer                                                                          | s and CRCWD                                        | AT/CRCDAT a     | re reset, othe |

| bit 14                           | Unimplemen                                                                                                                                                                                                                                                    | ted: Read as '                                                                                                                                                                                                                                                         | 0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                          |                                                    |                 |                |

| bit 13                           | CSIDL: CRC                                                                                                                                                                                                                                                    | Stop in Idle Mo                                                                                                                                                                                                                                                        | ode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                          |                                                    |                 |                |

|                                  |                                                                                                                                                                                                                                                               | nues module op<br>es module opera                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          | Idle mode                                          |                 |                |

|                                  |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | oue                                                                                      |                                                    |                 |                |

| bit 12-8                         | VWORD<4:0                                                                                                                                                                                                                                                     | >: Pointer Value                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | oue                                                                                      |                                                    |                 |                |