#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

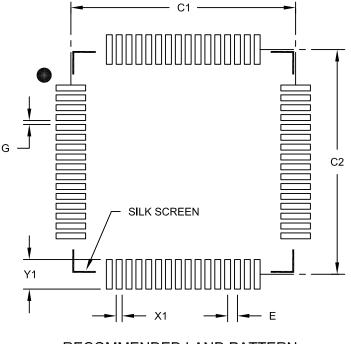

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc202t-e-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

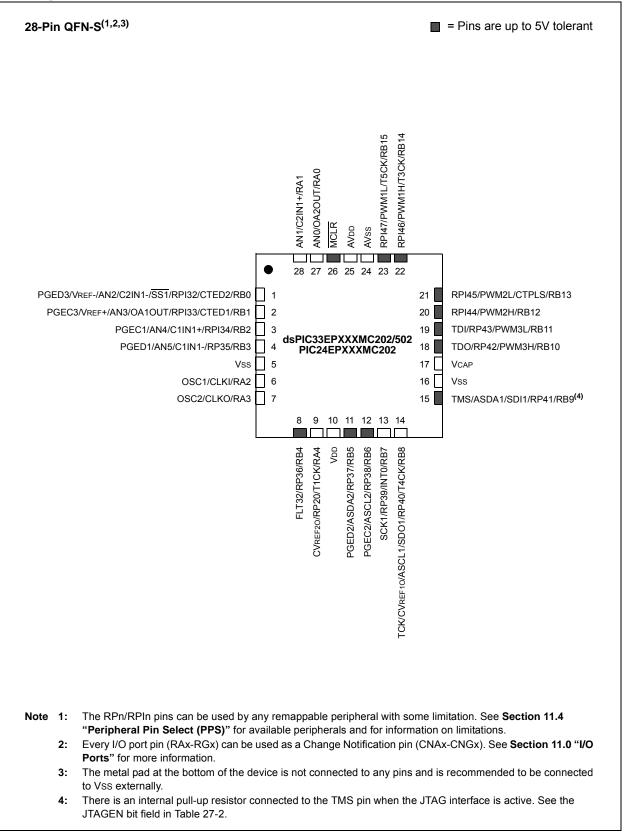

### Pin Diagrams (Continued)

| TABLE 1-1: PINC                           |             | O DESC         | RIPT | IONS (CONTINUED)                                                                 |

|-------------------------------------------|-------------|----------------|------|----------------------------------------------------------------------------------|

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS  | Description                                                                      |

| U2CTS                                     | Ι           | ST             | No   | UART2 Clear-To-Send.                                                             |

| U2RTS                                     | 0           | —              | No   | UART2 Ready-To-Send.                                                             |

| U2RX                                      | Ι           | ST             | Yes  | UART2 receive.                                                                   |

| U2TX                                      | 0           | —              | Yes  | UART2 transmit.                                                                  |

| BCLK2                                     | 0           | ST             | No   | UART2 IrDA <sup>®</sup> baud clock output.                                       |

| SCK1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for SPI1.                                  |

| SDI1                                      | I           | ST             | No   | SPI1 data in.                                                                    |

| SDO1                                      | 0           | —              | No   | SPI1 data out.                                                                   |

| SS1                                       | I/O         | ST             | No   | SPI1 slave synchronization or frame pulse I/O.                                   |

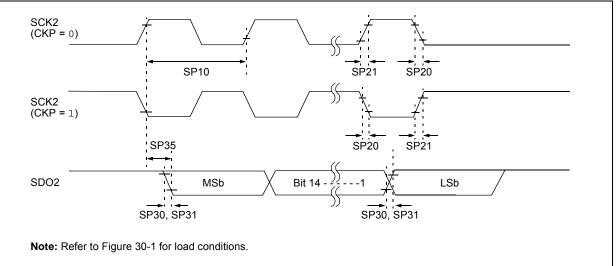

| SCK2                                      | I/O         | ST             | Yes  | Synchronous serial clock input/output for SPI2.                                  |

| SDI2                                      | I           | ST             | Yes  | SPI2 data in.                                                                    |

| SDO2                                      | 0           | _              | Yes  | SPI2 data out.                                                                   |

| SS2                                       | I/O         | ST             | Yes  | SPI2 slave synchronization or frame pulse I/O.                                   |

| SCL1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C1.                                  |

| SDA1                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C1.                                   |

| ASCL1                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C1.                        |

| ASDA1                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C1.                         |

| SCL2                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C2.                                  |

| SDA2                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C2.                                   |

| ASCL2                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C2.                        |

| ASDA2                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C2.                         |

| TMS <sup>(5)</sup>                        | Ι           | ST             | No   | JTAG Test mode select pin.                                                       |

| TCK                                       | Ι           | ST             | No   | JTAG test clock input pin.                                                       |

| TDI                                       | I           | ST             | No   | JTAG test data input pin.                                                        |

| TDO                                       | 0           | _              | No   | JTAG test data output pin.                                                       |

| C1RX <sup>(2)</sup>                       | Ι           | ST             | Yes  | ECAN1 bus receive pin.                                                           |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes  | ECAN1 bus transmit pin.                                                          |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | Ι           | ST             | Yes  | PWM Fault Inputs 1 and 2.                                                        |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | Ι           | ST             | No   | PWM Fault Inputs 3 and 4.                                                        |

| FLT32 <sup>(1,3)</sup>                    | Ι           | ST             | No   | PWM Fault Input 32 (Class B Fault).                                              |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | Ι           | ST             | Yes  | PWM Dead-Time Compensation Inputs 1 through 3.                                   |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | —              | No   | PWM Low Outputs 1 through 3.                                                     |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | —              | No   | PWM High Outputs 1 through 3.                                                    |

| SYNCI1 <sup>(1)</sup>                     | Ι           | ST             |      | PWM Synchronization Input 1.                                                     |

| SYNCO1 <sup>(1)</sup>                     | 0           |                | Yes  | PWM Synchronization Output 1.                                                    |

| INDX1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Index1 pulse input.                                           |

| HOME1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Home1 pulse input.                                            |

| QEA1 <sup>(1)</sup>                       | Ι           | ST             | Yes  | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |

| QEB1 <sup>(1)</sup>                       | ,           | ст             | Vee  | external clock/gate input in Timer mode.                                         |

|                                           | Ι           | ST             | Yes  | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |

| CNTCMP1 <sup>(1)</sup>                    | 0           |                | Yes  | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |

|                                           | 0           | <br>ompatible  | 162  |                                                                                  |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

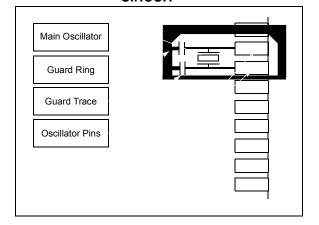

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                   | Bit 7             | Bit 6 | Bit 5     | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|--------|-------------------------|-------------------|-------|-----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —      | _                       |                   |       |           | I2C1 Recei   | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —      | _                       |                   |       |           | I2C1 Transi  | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _      |                         |                   |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                    | GCEN              | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                   | IWCOL             | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |        |                         |                   |       | I2C1 Addr | ess Register | r            |       |       |       | 0000          |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |        |                         |                   |       | I2C1 Add  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _      | _                       |                   |       |           | I2C2 Recei   | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _      | _                       |                   |       |           | I2C2 Transi  | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _      |                         |                   |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                    | GCEN              | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT | ADD10                   | IWCOL             | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      |        | I2C2 Address Register 0 |                   |       |           |              |              |       | 0000  |       |               |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | -      |        |                         | I2C2 Address Mask |       |           |              |              |       |       | 0000  |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                  | Bit 7      | Bit 6    | Bit 5 | Bit 4      | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------|----------|--------|--------|--------|-------|------------------------|------------|----------|-------|------------|----------|-------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN<  | :1:0>                  | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        | _      | _        | _      | _      | _      | _     |                        |            |          | UART1 | Transmit F | Register |       |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _      | _        | _      | _      | _      | _     |                        |            |          | UART  | Receive R  | legister |       |        |       | 0000          |

| U1BRG       | 0228  |          |        |          |        |        |        | Baud  | Rate Gen               | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN<  | :1:0>                  | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                   | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _        | _      | _      | _      | _     |                        |            |          | UART2 | Transmit F | Register |       |        |       | xxxx          |

| U2RXREG     | 0236  | _        | _      | _        | _      | —      | _      | _     | UART2 Receive Register |            |          |       |            |          |       |        |       | 0000          |

| U2BRG       | 0238  |          |        |          |        |        |        | Baud  | Rate Gen               | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-34: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3    | Bit 2 | Bit 1   | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|----------|-------|-------|--------|----------|-------|---------|-------|---------------|

| NVMCON    | 0728  | WR     | WREN   | WRERR  | NVMSIDL | _      | _      | —     | _     | _        | _     | _     | —      |          | NVMC  | )P<3:0> |       | 0000          |

| NVMADRL   | 072A  |        |        |        |         |        |        |       | NVMAD | )R<15:0> |       |       |        |          |       |         |       | 0000          |

| NVMADRH   | 072C  | _      | _      | _      | _       | -      | _      | _     | _     |          |       |       | NVMADF | R<23:16> |       |         |       | 0000          |

| NVMKEY    | 072E  |        |        | _      | —       | _      |        | —     | -     |          |       |       | NVMKE  | Y<7:0>   |       |         |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-35: SYSTEM CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4   | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|--------|--------|-----------|-------|---------|--------|--------|---------|-------|--------|-------|-------|---------------|

| RCON      | 0740  | TRAPR  | IOPUWR | _         | _      | VREGSF | _      | СМ        | VREGS | EXTR    | SWR    | SWDTEN | WDTO    | SLEEP | IDLE   | BOR   | POR   | Note 1        |

| OSCCON    | 0742  | _      | 0      | COSC<2:0> |        | —      |        | NOSC<2:0> |       | CLKLOCK | IOLOCK | LOCK   | _       | CF    | _      | _     | OSWEN | Note 2        |

| CLKDIV    | 0744  | ROI    | [      | OOZE<2:0> |        | DOZEN  | F      | RCDIV<2:0 | >     | PLLPOS  | T<1:0> | _      |         | F     | LLPRE< | 4:0>  |       | 0030          |

| PLLFBD    | 0746  | _      | _      | _         | _      | —      | _      | _         |       |         |        | PLLD   | IV<8:0> |       |        |       |       | 0030          |

| OSCTUN    | 0748  | _      | _      | _         | _      | —      | _      | _         | _     | _       |        |        |         | TUN≤  | <5:0>  |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses.

### TABLE 4-36: REFERENCE CLOCK REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON   | 074E  | ROON   | —      | ROSSLP | ROSEL  |        | RODI   | V<3:0> |       | _     | _     | —     | _     | _     | —     | _     | -     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

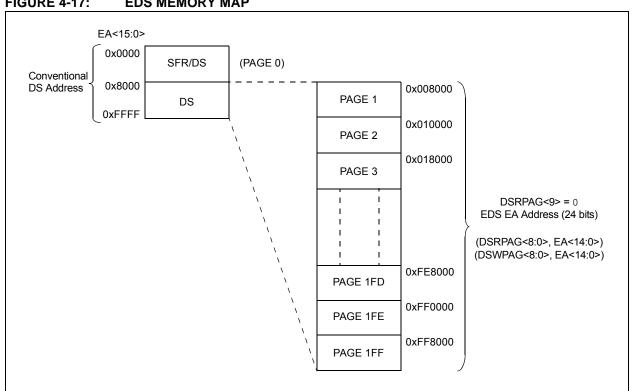

### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

### FIGURE 4-17: EDS MEMORY MAP

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0          | U-0          | U-0             | U-0              | U-0              | U-0              | U-0             | U-0   |

|--------------|--------------|-----------------|------------------|------------------|------------------|-----------------|-------|

|              | —            | _               | —                | —                | —                | —               | _     |

| bit 15       |              |                 |                  |                  |                  | •               | bit 8 |

|              |              |                 |                  |                  |                  |                 |       |

| U-0          | U-0          | R/W-0           | R/W-0            | U-0              | U-0              | U-0             | U-0   |

| —            | —            | DAE             | DOOVR            | —                | —                | —               | —     |

| bit 7        |              |                 |                  |                  |                  |                 | bit 0 |

|              |              |                 |                  |                  |                  |                 |       |

| Legend:      |              |                 |                  |                  |                  |                 |       |

| R = Readab   | le bit       | W = Writable    | bit              | U = Unimplei     | mented bit, read | as '0'          |       |

| -n = Value a | It POR       | '1' = Bit is se | t                | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|              |              |                 |                  |                  |                  |                 |       |

| bit 15-6     | Unimplemen   | ted: Read as    | '0'              |                  |                  |                 |       |

| bit 5        | DAE: DMA A   | ddress Error S  | Soft Trap Status | s bit            |                  |                 |       |

|              | 1 = DMA add  | ress error soft | trap has occur   | red              |                  |                 |       |

|              | 0 = DMA add  | ress error soft | trap has not o   | ccurred          |                  |                 |       |

| bit 4        | DOOVR: DO    | Stack Overflov  | v Soft Trap Sta  | tus bit          |                  |                 |       |

|              | 1 = DO stack | overflow soft t | rap has occurre  | ed               |                  |                 |       |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | _   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0      | U-0   | U-0   | U-0   | U-0       | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|-----------|-------|-------|-------|

| —        | —     | —     | —     | —         | —     | —     | —     |

| bit 15   |       |       |       |           |       |       | bit 8 |

|          |       |       |       |           |       |       |       |

| U-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| —        |       |       |       | SS2R<6:0> |       |       |       |

| bit 7    |       |       |       |           |       |       | bit 0 |

|          |       |       |       |           |       |       |       |

| l egend: |       |       |       |           |       |       |       |

### REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>SS2R&lt;6:0&gt;:</b> Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                            |

|          |                                                                                                                                           |

|          | •                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                               |

### REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      | —     | —     | _     | _          | _     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|        |       |       |       | C1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-0  | <b>C1RXR&lt;6:0&gt;:</b> Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 1111001 = Input tied to RPI121                                                                                                          |

|          | •                                                                                                                                       |

|          |                                                                                                                                         |

|          | 0000001 = Input tied to CMP1<br>0000000 = Input tied to Vss                                                                             |

### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

| R/W-0        | R/W-0                                                                                                    | R/W-0                              | R/W-0          | U-0               | U-0                | U-0              | U-0          |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-------------------|--------------------|------------------|--------------|--|--|

|              | TRGD                                                                                                     | V<3:0>                             |                | —                 |                    | —                | _            |  |  |

| bit 15       |                                                                                                          |                                    |                |                   |                    |                  | bit 8        |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |

| U-0          | U-0                                                                                                      | R/W-0                              | R/W-0          | R/W-0             | R/W-0              | R/W-0            | R/W-0        |  |  |

| _            |                                                                                                          |                                    |                | TRGSTF            | RT<5:0> <b>(1)</b> |                  |              |  |  |

| bit 7        |                                                                                                          |                                    |                |                   |                    |                  | bit          |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |

| Legend:      | 1. 1.4                                                                                                   |                                    |                |                   |                    |                  |              |  |  |

| R = Readab   |                                                                                                          | W = Writable                       |                | •                 | nented bit, read   |                  |              |  |  |

| -n = Value a | t POR                                                                                                    | '1' = Bit is set                   |                | '0' = Bit is clea | ared               | x = Bit is unkn  | own          |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |

| bit 15-12    |                                                                                                          | <b>)&gt;:</b> Trigger # Ou         | -              |                   |                    |                  |              |  |  |

|              | 1111 = Trigger output for every 16th trigger event                                                       |                                    |                |                   |                    |                  |              |  |  |

|              | 1110 = Trigger output for every 15th trigger event                                                       |                                    |                |                   |                    |                  |              |  |  |

|              | 1101 = Trigger output for every 14th trigger event                                                       |                                    |                |                   |                    |                  |              |  |  |

|              | 1100 = Trigger output for every 13th trigger event<br>1011 = Trigger output for every 12th trigger event |                                    |                |                   |                    |                  |              |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                    |                  |              |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                    |                  |              |  |  |

|              |                                                                                                          | per output for ev                  |                |                   |                    |                  |              |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |

|              | 0111 = Trigger output for every 8th trigger event<br>0110 = Trigger output for every 7th trigger event   |                                    |                |                   |                    |                  |              |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                    |                  |              |  |  |

|              | 0100 = Trigg                                                                                             | ger output for ev                  | ery 5th trigge | r event           |                    |                  |              |  |  |

|              | 0011 = Trigger output for every 4th trigger event                                                        |                                    |                |                   |                    |                  |              |  |  |

|              | 0010 = Trigger output for every 3rd trigger event                                                        |                                    |                |                   |                    |                  |              |  |  |

|              |                                                                                                          | ger output for ev                  |                |                   |                    |                  |              |  |  |

|              | 0000 = Trigg                                                                                             | ger output for ev                  | ery trigger ev | ent               |                    |                  |              |  |  |

| bit 11-6     | Unimplemented: Read as '0'                                                                               |                                    |                |                   |                    |                  |              |  |  |

| bit 5-0      | TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits <sup>(1)</sup>                                 |                                    |                |                   |                    |                  |              |  |  |

| 010 5-0      | 111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled       |                                    |                |                   |                    |                  |              |  |  |

|              |                                                                                                          |                                    |                |                   |                    |                  |              |  |  |

|              | •                                                                                                        |                                    |                | ·                 |                    |                  |              |  |  |

|              | •                                                                                                        |                                    |                | -                 |                    |                  |              |  |  |

|              | •                                                                                                        |                                    |                | -                 |                    |                  |              |  |  |

|              | •<br>•<br>•                                                                                              | aits 2 PW/M ava                    | les hefore co  | nerating the fire | t trigger event :  | after the module | a is anabled |  |  |

|              |                                                                                                          | /aits 2 PWM cyc<br>/aits 1 PWM cyc |                |                   |                    |                  |              |  |  |

## REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

# 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                                | U-0                                                                                                    | U-0                         | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|----------------------------------------|----------------------|----------------------|----------------------|--|--|

| _                                  | —                                                                                                      | _                           | DISSCK               | DISSDO                                 | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |

| bit 15                             |                                                                                                        |                             |                      |                                        |                      |                      | bit                  |  |  |

| <b>D M M A</b>                     | <b>D</b> 444 0                                                                                         | DAMA                        | <b>D M / 0</b>       | <b>D</b> 444 0                         | Dates                | Dates                | <b>D</b> 444 0       |  |  |

| R/W-0                              | R/W-0                                                                                                  | R/W-0                       | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |  |

| SSEN <sup>(2)</sup>                | CKP                                                                                                    | MSTEN                       | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3</sup>  |  |  |

| bit 7                              |                                                                                                        |                             |                      |                                        |                      |                      | bit                  |  |  |

| Legend:                            |                                                                                                        |                             |                      |                                        |                      |                      |                      |  |  |

| R = Readabl                        | e bit                                                                                                  | W = Writable                | bit                  | U = Unimpler                           | mented bit, read     | l as '0'             |                      |  |  |

| -n = Value at                      | POR                                                                                                    | '1' = Bit is se             | t                    | '0' = Bit is cle                       |                      | x = Bit is unkr      | nown                 |  |  |

|                                    |                                                                                                        |                             |                      |                                        |                      |                      |                      |  |  |

| bit 15-13                          | Unimplemen                                                                                             | ted: Read as                | 0'                   |                                        |                      |                      |                      |  |  |

| bit 12                             | DISSCK: Disa                                                                                           | able SCKx Pin               | bit (SPIx Mas        | ter modes only                         | /)                   |                      |                      |  |  |

|                                    | 1 = Internal S                                                                                         | Plx clock is di             | sabled, pin fun      | -                                      |                      |                      |                      |  |  |

|                                    | 0 = Internal S                                                                                         | PIx clock is er             | abled                |                                        |                      |                      |                      |  |  |

| it 11 DISSDO: Disable SDOx Pin bit |                                                                                                        |                             |                      |                                        |                      |                      |                      |  |  |

|                                    | 1 = SDOx pin is not used by the module; pin functions as I/O                                           |                             |                      |                                        |                      |                      |                      |  |  |

|                                    | 0 = SDOx pin is controlled by the module                                                               |                             |                      |                                        |                      |                      |                      |  |  |

| bit 10                             | MODE16: Word/Byte Communication Select bit                                                             |                             |                      |                                        |                      |                      |                      |  |  |

|                                    | <ol> <li>Communication is word-wide (16 bits)</li> <li>Communication is byte-wide (8 bits)</li> </ol>  |                             |                      |                                        |                      |                      |                      |  |  |

| bit 9                              |                                                                                                        | ata Input Sam               | . ,                  |                                        |                      |                      |                      |  |  |

| bit 5                              | Master mode                                                                                            |                             |                      |                                        |                      |                      |                      |  |  |

|                                    |                                                                                                        | <u>.</u><br>a is sampled at | end of data o        | utput time                             |                      |                      |                      |  |  |

|                                    |                                                                                                        | a is sampled at             |                      |                                        |                      |                      |                      |  |  |

|                                    | Slave mode:                                                                                            |                             |                      |                                        |                      |                      |                      |  |  |

|                                    |                                                                                                        |                             |                      | n Slave mode.                          |                      |                      |                      |  |  |

| bit 8                              |                                                                                                        | lock Edge Sele              |                      |                                        |                      |                      |                      |  |  |

|                                    |                                                                                                        |                             |                      |                                        | clock state to Id    |                      |                      |  |  |

| bit 7                              |                                                                                                        |                             |                      |                                        | ock state to activ   |                      |                      |  |  |

|                                    | <b>SSEN:</b> Slave Select Enable bit (Slave mode) <sup>(2)</sup><br>1 = SSx pin is used for Slave mode |                             |                      |                                        |                      |                      |                      |  |  |

|                                    |                                                                                                        |                             |                      | is controlled b                        | by port function     |                      |                      |  |  |

| bit 6                              |                                                                                                        | Polarity Select             |                      |                                        | 51                   |                      |                      |  |  |

|                                    | 1 = Idle state                                                                                         | for clock is a h            | nigh level; activ    | ve state is a lov<br>e state is a higl |                      |                      |                      |  |  |

| bit 5                              |                                                                                                        | ter Mode Enat               |                      | Ū                                      |                      |                      |                      |  |  |

|                                    | 1 = Master m                                                                                           |                             |                      |                                        |                      |                      |                      |  |  |

|                                    | 0 = Slave mo                                                                                           | de                          |                      |                                        |                      |                      |                      |  |  |

| <b>Note 1:</b> ⊺h                  | he CKE bit is not                                                                                      | used in Frame               | d SPI modes I        | Program this hi                        | it to '0' for Fram   | ed SPI modes (       | FRMEN = <sup>-</sup> |  |  |

|                                    | his bit must be cl                                                                                     |                             |                      |                                        |                      |                      |                      |  |  |

| <b>2</b> . 11                      |                                                                                                        |                             | · · ·                |                                        |                      |                      |                      |  |  |

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                           | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0   |  |

|---------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------|-----------------|---------|--|

|                                 | F15B                         | P<3:0>                                                                                                                     |                                                |                                    | F14BI          | P<3:0>          |         |  |

| bit 15                          |                              |                                                                                                                            |                                                |                                    |                |                 | bit 8   |  |

| R/W-0                           | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0   |  |

| 1010 0                          |                              | P<3:0>                                                                                                                     | 10110                                          |                                    |                | P<3:0>          | 1010 0  |  |

| bit 7                           |                              |                                                                                                                            |                                                |                                    |                |                 | bit 0   |  |

| Legend:                         |                              |                                                                                                                            |                                                |                                    |                |                 |         |  |

| R = Readable bit W = Writable b |                              |                                                                                                                            | bit                                            | U = Unimplemented bit, read as '0' |                |                 |         |  |

| -n = Value at POR               |                              | '1' = Bit is set                                                                                                           | :                                              | '0' = Bit is cleared x = Bit is    |                | x = Bit is unkr | unknown |  |

| bit 15-12                       | 1111 = Filte<br>1110 = Filte | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | differ<br>4                        |                |                 |         |  |

| bit 11-8                        | F14BP<3:0:                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val                   | ues as bits<15 | :12>)           |         |  |

| bit 7-4                         | F13BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val                   | ues as bits<15 | :12>)           |         |  |

| bit 3-0                         | F12BP<3:0:                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 2 bits (same val                   | ues as bits<15 | :12>)           |         |  |

### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                             |

|---------|------------------------|-------------|----------------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                                      |

|         |                        | 0001        | Reserved.                                                                                                      |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                              |

|         |                        | 0011        | Reserved.                                                                                                      |

|         |                        | 0100        | Reserved.                                                                                                      |

|         |                        | 0101        | Reserved.                                                                                                      |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                               |

|         |                        | 0111        | Reserved.                                                                                                      |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                          |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                          |

|         |                        | 1010        | Reserved.                                                                                                      |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing $(PTGSWT = 0 \text{ to } 1)$ . |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                               |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                               |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                               |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                                 |

|         | PTGADD <sup>(1)</sup>  | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                                |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                                |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                                   |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                                   |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                                |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                         |

|         |                        | 0110        | Reserved.                                                                                                      |

|         |                        | 0111        | Reserved.                                                                                                      |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                              |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                              |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                                 |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                                 |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                             |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                       |

|         |                        | 1110        | Reserved.                                                                                                      |

|         |                        | 1111        | Reserved.                                                                                                      |

### TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax                     | Description                              | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|-------|-------------------------------------|------------------------------------------|---------------|-------------------------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc <sup>(1)</sup>                  | Add Accumulators                         | 1             | 1                             | OA,OB,SA,SB              |

|                    |                      | ADD   | f                                   | f = f + WREG                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG                              | WREG = f + WREG                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn                           | Wd = lit10 + Wd                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd                            | Wd = Wb + Ws                             | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd                         | Wd = Wb + lit5                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc                      | 16-bit Signed Add to Accumulator         | 1             | 1                             | OA,OB,SA,SE              |

| 2                  | ADDC                 | ADDC  | f                                   | f = f + WREG + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG                              | WREG = $f + WREG + (C)$                  | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn                           | Wd = lit10 + Wd + (C)                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd                            | Wd = Wb + Ws + (C)                       | 1             | 1                             | C,DC,N,OV,Z              |