#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc202t-i-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4   | 4-9:  | INPUT CAPTURE 1 THROUGH INPUT CAPTURE 4 REGISTER MAP |                                                        |        |        |           |        |       |              |              |          |       |       |       |          |          |       |               |

|-----------|-------|------------------------------------------------------|--------------------------------------------------------|--------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15                                               | Bit 14                                                 | Bit 13 | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _                                                    | —                                                      | ICSIDL | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142  | _                                                    | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> 000                |        |        |           |        |       |              |              |          |       |       |       | 000D     |          |       |               |

| IC1BUF    | 0144  |                                                      | Input Capture 1 Buffer Register xxx                    |        |        |           |        |       |              |              |          |       |       |       | xxxx     |          |       |               |

| IC1TMR    | 0146  |                                                      | Input Capture 1 Timer 0000                             |        |        |           |        |       |              |              |          |       |       |       | 0000     |          |       |               |

| IC2CON1   | 0148  |                                                      | - ICSIDL ICTSEL<2:0> ICI<1:0> ICOV ICBNE ICM<2:0> 0000 |        |        |           |        |       |              |              |          |       |       |       | 0000     |          |       |               |

| IC2CON2   | 014A  |                                                      | —                                                      |        |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC2BUF    | 014C  |                                                      |                                                        |        |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |                                                      |                                                        |        |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |                                                      | —                                                      | ICSIDL | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |                                                      | —                                                      |        |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |                                                      |                                                        |        |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |                                                      |                                                        |        |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |                                                      | —                                                      | ICSIDL | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _                                                    | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> 000                |        |        |           |        |       |              |              |          |       |       | 000D  |          |          |       |               |

| IC4BUF    | 015C  |                                                      | Input Capture 4 Buffer Register                        |        |        |           |        |       |              |              |          |       |       | xxxx  |          |          |       |               |

| IC4TMR    | 015E  |                                                      | Input Capture 4 Timer 0000                             |        |        |           |        |       |              |              |          |       |       |       |          |          |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|--------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN  | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |        |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN  | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  |        |        |         |        |        |        | SPI2 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | —      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | —      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | _      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

|-----------------|----------------------------------------------------------------------|------------------|-------|-------------------|-------|-----------------|-------|--|--|--|--|

|                 |                                                                      |                  | PAD   | <15:8>            |       |                 |       |  |  |  |  |

| bit 15          |                                                                      |                  |       |                   |       |                 | bit 8 |  |  |  |  |

|                 |                                                                      |                  |       |                   |       |                 |       |  |  |  |  |

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

|                 |                                                                      |                  | PAE   | )<7:0>            |       |                 |       |  |  |  |  |

| bit 7           |                                                                      |                  |       |                   |       |                 | bit 0 |  |  |  |  |

|                 |                                                                      |                  |       |                   |       |                 |       |  |  |  |  |

| Legend:         |                                                                      |                  |       |                   |       |                 |       |  |  |  |  |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       |                   |       |                 |       |  |  |  |  |

| -n = Value at P | POR                                                                  | '1' = Bit is set |       | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |  |  |  |  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

| —               |       |                  |       | CNT<              | 13:8> <b>(2)</b> |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | CNT<  | <7:0> <b>(2)</b>  |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable b  | oit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea  | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

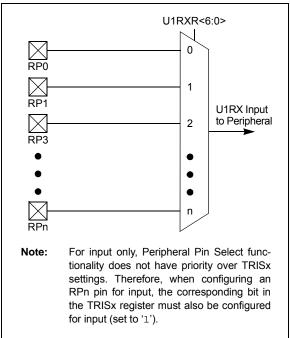

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/ comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

# EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

| RPINR15 = 0x2500; | /* Connect the QEI1 HOME1 input to RP37 (pin 43) */                   |

|-------------------|-----------------------------------------------------------------------|

| RPINR7 = 0x009;   | /* Connect the IC1 input to the digital filter on the FHOME1 input */ |

| QEI1IOC = 0x4000; | /* Enable the QEI digital filter */                                   |

| QEI1CON = 0x8000; | /* Enable the QEI module */                                           |

### REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|------------------|----------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|

|              |                  |                                                          |       | DTCMP3R<6:0       | )>              |                 |       |

| bit 15       |                  |                                                          |       |                   |                 |                 | bit 8 |

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| 0-0          | R/W-0            | R/W-0                                                    | -     | DTCMP2R<6:0       |                 | R/W-0           | R/W-U |

| bit 7        |                  |                                                          |       |                   | 17              |                 | bit 0 |

| bit i        |                  |                                                          |       |                   |                 |                 | bit 0 |

| Legend:      |                  |                                                          |       |                   |                 |                 |       |

| R = Readab   | ole bit          | W = Writable                                             | bit   | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR           | '1' = Bit is set                                         |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                  |                                                          |       |                   |                 |                 |       |

|              |                  | nput tied to CMI                                         |       |                   |                 |                 |       |

| bit 7        | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |                   |                 |                 |       |

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|------------|------------------|----------------|-------------------|------------------|-----------------|-------|

| _             | —          |                  |                | RP39              | R<5:0>           |                 |       |

| bit 15        |            |                  |                |                   |                  |                 | bit 8 |

|               |            |                  |                |                   |                  |                 |       |

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| —             | —          |                  |                | RP38              | R<5:0>           |                 |       |

| bit 7         |            |                  |                |                   |                  |                 | bit 0 |

|               |            |                  |                |                   |                  |                 |       |

| Legend:       |            |                  |                |                   |                  |                 |       |

| R = Readable  | e bit      | W = Writable     | bit            | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at | POR        | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|               |            |                  |                |                   |                  |                 |       |

| bit 15-14     | Unimplemer | nted: Read as '  | 0'             |                   |                  |                 |       |

| bit 13-8      | RP39R<5:0> | : Peripheral Ou  | Itput Function | n is Assigned to  | RP39 Output F    | Pin bits        |       |

#### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits  |

|---------|--------------------------------------------------------------|

|         | 11111 = OCxRS compare event is used for synchronization      |

|         | 11110 = INT2 pin synchronizes or triggers OCx                |

|         | 11101 = INT1 pin synchronizes or triggers OCx                |

|         | 11100 = CTMU module synchronizes or triggers OCx             |

|         | 11011 = ADC1 module synchronizes or triggers OCx             |

|         | 11010 = CMP3 module synchronizes or triggers OCx             |

|         | 11001 = CMP2 module synchronizes or triggers OCx             |

|         | 11000 = CMP1 module synchronizes or triggers OCx             |

|         | 10111 = Reserved                                             |

|         | 10110 = Reserved                                             |

|         | 10101 = Reserved                                             |

|         | 10100 = Reserved                                             |

|         | 10011 = IC4 input capture event synchronizes or triggers OCx |

|         | 10010 = IC3 input capture event synchronizes or triggers OCx |

|         | 10001 = IC2 input capture event synchronizes or triggers OCx |

|         | 10000 = IC1 input capture event synchronizes or triggers OCx |

|         | 01111 = Timer5 synchronizes or triggers OCx                  |

|         | 01110 = Timer4 synchronizes or triggers OCx                  |

|         | 01101 = Timer3 synchronizes or triggers OCx                  |

|         | 01100 = Timer2 synchronizes or triggers OCx (default)        |

|         | 01011 = Timer1 synchronizes or triggers OCx $(2)$            |

|         | 01010 = PTGOx synchronizes or triggers $OCx^{(3)}$           |

|         | 01001 = Reserved                                             |

|         | 01000 = Reserved                                             |

|         | 00111 = Reserved                                             |

|         | 00110 = Reserved                                             |

|         | 00101 = Reserved                                             |

|         | 00100 = OC4 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00011 = OC3 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00010 = OC2 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00001 = OC1 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00000 = No Sync or Trigger source for OCx                    |

- **Note 1:** Do not use the OCx module as its own Synchronization or Trigger source.

- 2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

- Each Output Compare x module (OCx) has one PTG Trigger/Synchronization source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information. PTGO0 = OC1

PTGO0 = OC1 PTGO1 = OC2 PTGO2 = OC3PTGO3 = OC4

| R-0, HSC                                                                   | R-0, HSC  | U-0      | U-0              | U-0             | R/C-0, HS                             | R-0, HSC | R-0, HSC |

|----------------------------------------------------------------------------|-----------|----------|------------------|-----------------|---------------------------------------|----------|----------|

| ACKSTAT                                                                    | TRSTAT    | _        | _                | —               | BCL                                   | GCSTAT   | ADD10    |

| bit 15                                                                     |           |          |                  |                 |                                       | bit 8    |          |

|                                                                            |           |          |                  |                 |                                       |          |          |

| R/C-0, HS                                                                  | R/C-0, HS | R-0, HSC | R/C-0, HSC       | R/C-0, HSC      | R-0, HSC                              | R-0, HSC | R-0, HSC |

| IWCOL                                                                      | I2COV     | D_A      | Р                | S               | R_W                                   | RBF      | TBF      |

| bit 7                                                                      |           |          |                  |                 |                                       |          | bit 0    |

|                                                                            |           |          |                  |                 |                                       |          |          |

| Legend: C = Clearable bit                                                  |           | le bit   | HS = Hardwa      | re Settable bit | HSC = Hardware Settable/Clearable bit |          |          |

| R = Readable bit W = Writable bit U = Unimplemented bit, r                 |           |          | nented bit, read | as '0'          |                                       |          |          |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |           |          |                  |                 |                                       |          |          |

### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

#### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0                             | R/W-0    | R/W-0            | U-0             | R/W-0, HC                          | R/W-0                | R-0             | R-1   |

|-----------------------------------|----------|------------------|-----------------|------------------------------------|----------------------|-----------------|-------|

| UTXISEL1                          | UTXINV   | UTXISEL0         | —               | UTXBRK                             | UTXEN <sup>(1)</sup> | UTXBF           | TRMT  |

| bit 15                            |          |                  |                 |                                    |                      |                 | bit 8 |

|                                   |          |                  |                 |                                    |                      |                 |       |

| R/W-0                             | R/W-0    | R/W-0            | R-1             | R-0                                | R-0                  | R/C-0           | R-0   |

| URXISEL1                          | URXISEL0 | ADDEN            | RIDLE           | PERR                               | FERR                 | OERR            | URXDA |

| bit 7                             |          |                  |                 |                                    |                      |                 | bit C |

|                                   |          |                  |                 |                                    |                      |                 |       |

| Legend:                           |          | HC = Hardward    | e Clearable bit | C = Clearable bit                  |                      |                 |       |

| R = Readable bit W = Writable bit |          |                  | bit             | U = Unimplemented bit, read as '0' |                      |                 |       |

| -n = Value at POR                 |          | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is    |                      | x = Bit is unki | nown  |

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

- <u>If IREN = 0:</u> 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

- If IREN = 1:

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 Unimplemented: Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup> 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled by the PORT

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | (                                                                                                                                                   | ,_, ., ., ., .,                                                           | -,-,-,                |                  |                  |                 |                 |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------|------------------|------------------|-----------------|-----------------|--|--|--|

| R/W-0         | R-0                                                                                                                                                 | R-0                                                                       | R-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |

| TXENn         | TXABTn                                                                                                                                              | TXLARBn                                                                   | TXERRn                | TXREQn           | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |

| bit 15        |                                                                                                                                                     |                                                                           |                       |                  |                  |                 | bit 8           |  |  |  |

| R/W-0         | R-0                                                                                                                                                 | R-0                                                                       | R-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |

| TXENm         | TXABTm <sup>(1)</sup>                                                                                                                               | TXLARBm <sup>(1)</sup>                                                    | TXERRm <sup>(1)</sup> | TXREQm           | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |

| bit 7         |                                                                                                                                                     |                                                                           |                       |                  |                  |                 | bit C           |  |  |  |

| Legend:       |                                                                                                                                                     |                                                                           |                       |                  |                  |                 |                 |  |  |  |

| R = Readabl   | le bit                                                                                                                                              | W = Writable                                                              | bit                   | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |

| -n = Value at | t POR                                                                                                                                               | '1' = Bit is set                                                          |                       | '0' = Bit is cle | ared             | x = Bit is unki | nown            |  |  |  |

| bit 15-8      | See Definitio                                                                                                                                       | n for bits<7:0>,                                                          | Controls Buffe        | <u>er n</u>      |                  |                 |                 |  |  |  |

| bit 7         |                                                                                                                                                     |                                                                           |                       |                  |                  |                 |                 |  |  |  |

|               |                                                                                                                                                     | TXENm: TX/RX Buffer Selection bit<br>1 = Buffer TRBn is a transmit buffer |                       |                  |                  |                 |                 |  |  |  |

|               | 0 = Buffer TRBn is a receive buffer                                                                                                                 |                                                                           |                       |                  |                  |                 |                 |  |  |  |

| bit 6         | TXABTm: Message Aborted bit <sup>(1)</sup>                                                                                                          |                                                                           |                       |                  |                  |                 |                 |  |  |  |

|               | 1 = Message was aborted                                                                                                                             |                                                                           |                       |                  |                  |                 |                 |  |  |  |

|               |                                                                                                                                                     | completed tran                                                            |                       |                  |                  |                 |                 |  |  |  |

| bit 5         |                                                                                                                                                     | TXLARBm: Message Lost Arbitration bit <sup>(1)</sup>                      |                       |                  |                  |                 |                 |  |  |  |

|               |                                                                                                                                                     | lost arbitration did not lose ar                                          |                       |                  |                  |                 |                 |  |  |  |

| bit 4         | TXERRm: Er                                                                                                                                          | <b>TXERRm:</b> Error Detected During Transmission bit <sup>(1)</sup>      |                       |                  |                  |                 |                 |  |  |  |

|               |                                                                                                                                                     | or occurred wh<br>or did not occu                                         |                       |                  |                  |                 |                 |  |  |  |

| bit 3         |                                                                                                                                                     | essage Send F                                                             |                       |                  |                  |                 |                 |  |  |  |

|               |                                                                                                                                                     | 0                                                                         | •                     | bit automatic    | ally clears wher | n the message   | is successfully |  |  |  |

|               | 0 = Clearing                                                                                                                                        | the bit to '0' wh                                                         | nile set reques       | ts a message     | abort            |                 |                 |  |  |  |

| bit 2         | RTRENm: Auto-Remote Transmit Enable bit                                                                                                             |                                                                           |                       |                  |                  |                 |                 |  |  |  |

|               |                                                                                                                                                     | emote transmit<br>emote transmit                                          |                       |                  |                  |                 |                 |  |  |  |

| bit 1-0       | <ul> <li>0 = When a remote transmit is received, TXREQ will be unaffected</li> <li>TXmPRI&lt;1:0&gt;: Message Transmission Priority bits</li> </ul> |                                                                           |                       |                  |                  |                 |                 |  |  |  |

|               | 11 = Highest                                                                                                                                        | message prior                                                             | ity                   |                  |                  |                 |                 |  |  |  |

|               | 0                                                                                                                                                   | ermediate mes                                                             |                       |                  |                  |                 |                 |  |  |  |

|               |                                                                                                                                                     | ermediate mess<br>message priori                                          |                       |                  |                  |                 |                 |  |  |  |

|               |                                                                                                                                                     |                                                                           | -                     |                  |                  |                 |                 |  |  |  |

| Note 1: ⊤     | his bit is cleared                                                                                                                                  | when TXREQ                                                                | s set.                |                  |                  |                 |                 |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

## 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

NOTES:

## **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|       |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

#### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)                                                                                                                             |

|         | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                       |

|         | 00 = Trigger/event/interrupt generation is disabled                                                                                                                                                                                                           |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 4   | <b>CREF:</b> Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                                      |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage<sup>(2)</sup></li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                          |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                                                |

|         | <ul> <li>11 = Unimplemented</li> <li>10 = Unimplemented</li> <li>01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup></li> <li>00 = Inverting input of the op amp/comparator connects to the CxIN1- pin</li> </ul>                 |

|         |                                                                                                                                                                                                                                                               |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

| U-0          | U-0                                   | U-0                                                                                 | U-0              | U-0              | U-0              | U-0            | U-0    |  |  |  |

|--------------|---------------------------------------|-------------------------------------------------------------------------------------|------------------|------------------|------------------|----------------|--------|--|--|--|

|              | —                                     | —                                                                                   | _                | —                |                  | —              | _      |  |  |  |

| bit 15       |                                       |                                                                                     |                  |                  |                  |                | bit    |  |  |  |

|              |                                       |                                                                                     |                  |                  |                  |                |        |  |  |  |

| U-0          | R/W-0                                 | R/W-0                                                                               | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0  |  |  |  |

|              | CFSEL2                                | CFSEL1                                                                              | CFSEL0           | CFLTREN          | CFDIV2           | CFDIV1         | CFDIV0 |  |  |  |

| bit 7        |                                       |                                                                                     |                  |                  |                  |                | bit    |  |  |  |

| Legend:      |                                       |                                                                                     |                  |                  |                  |                |        |  |  |  |

| R = Readab   | le bit                                | W = Writable                                                                        | bit              | U = Unimpler     | mented bit, read | as '0'         |        |  |  |  |

| -n = Value a |                                       | '1' = Bit is set                                                                    |                  | '0' = Bit is cle |                  | x = Bit is unk | nown   |  |  |  |

|              |                                       |                                                                                     |                  |                  |                  |                | -      |  |  |  |

| bit 15-7     | Unimplemen                            | ted: Read as                                                                        | ʻ0'              |                  |                  |                |        |  |  |  |

| oit 6-4      | CFSEL<2:0>                            | : Comparator                                                                        | Filter Input Clo | ock Select bits  |                  |                |        |  |  |  |

|              |                                       | CFSEL<2:0>: Comparator Filter Input Clock Select bits<br>111 = T5CLK <sup>(1)</sup> |                  |                  |                  |                |        |  |  |  |

|              |                                       | $110 = T4CLK^{(2)}$                                                                 |                  |                  |                  |                |        |  |  |  |

|              | 101 = T3CLK                           | $101 = T3CLK^{(1)}$                                                                 |                  |                  |                  |                |        |  |  |  |

|              | 100 = T2CLK                           | $100 = T2CLK^{(2)}$                                                                 |                  |                  |                  |                |        |  |  |  |

|              |                                       | 011 = Reserved                                                                      |                  |                  |                  |                |        |  |  |  |

|              | 010 = SYNC                            | 01 <sup>(3)</sup>                                                                   |                  |                  |                  |                |        |  |  |  |

|              | 001 = Fosc <sup>(4</sup>              | 1)                                                                                  |                  |                  |                  |                |        |  |  |  |

|              | $000 = FP^{(4)}$                      |                                                                                     |                  |                  |                  |                |        |  |  |  |

| bit 3        | CFLTREN: Comparator Filter Enable bit |                                                                                     |                  |                  |                  |                |        |  |  |  |

|              | 1 = Digital filter is enabled         |                                                                                     |                  |                  |                  |                |        |  |  |  |

|              | •                                     | er is disabled                                                                      |                  |                  |                  |                |        |  |  |  |

| bit 2-0      | CFDIV<2:0>:                           | CFDIV<2:0>: Comparator Filter Clock Divide Select bits                              |                  |                  |                  |                |        |  |  |  |

|              | 111 = Clock Divide 1:128              |                                                                                     |                  |                  |                  |                |        |  |  |  |

|              | 110 = Clock                           | 110 = Clock Divide 1:64                                                             |                  |                  |                  |                |        |  |  |  |

|              | 101 = Clock                           | 101 = Clock Divide 1:32                                                             |                  |                  |                  |                |        |  |  |  |

|              | 100 = Clock                           | 100 = Clock Divide 1:16                                                             |                  |                  |                  |                |        |  |  |  |

|              |                                       | 011 = Clock Divide 1:8                                                              |                  |                  |                  |                |        |  |  |  |

|              |                                       | 010 = Clock Divide 1:4                                                              |                  |                  |                  |                |        |  |  |  |

|              | 001 = Clock                           |                                                                                     |                  |                  |                  |                |        |  |  |  |

|              | 000 = Clock                           | Divide 1:1                                                                          |                  |                  |                  |                |        |  |  |  |

| Note 1: S    | See the Type C Ti                     | mer Block Diag                                                                      | gram (Figure 1   | 3-2).            |                  |                |        |  |  |  |

|              | See the Type B Tir                    |                                                                                     |                  |                  |                  |                |        |  |  |  |

| •            |                                       |                                                                                     |                  |                  |                  |                |        |  |  |  |

## REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 16-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

## TABLE 30-37:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS