Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 60 MIPs                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| lumber of I/O             | 35                                                                               |

| Program Memory Size       | 128KB (43K x 24)                                                                 |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 8K x 16                                                                          |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| ata Converters            | A/D 9x10b/12b                                                                    |

| scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C (TA)                                                               |

| lounting Type             | Surface Mount                                                                    |

| ackage / Case             | 44-VQFN Exposed Pad                                                              |

| upplier Device Package    | 44-QFN (8x8)                                                                     |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc204-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB® PICkit™ 3, MPLAB ICD 3, or MPLAB RFALICE™.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB® ICD 3" (poster) DS51765

- "MPLAB® ICD 3 Design Advisory" DS51764

- "MPLAB® REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

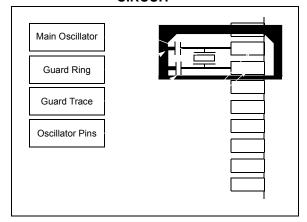

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0** "Oscillator Configuration" for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

FIGURE 2-3: SUGGESTED PLACEMENT

OF THE OSCILLATOR

CIRCUIT

TABLE 4-41: PMD REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | 1      | 1      | -      | CMPMD  | _      | _      | CRCMD  | _     | _     | -      | -      | -      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | 1      | 1      | -      | _      | _      | _      | 1      | _     | _     | -      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | _      | 1      | 1      | -      | PWM3MD | PWM2MD | PWM1MD | 1      | _     | _     | -      | -      | -      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| PIVIDI       | 0760  | _      | _      | _      | _      |        | _      |        | _      | _      | _     | _     | DMA2MD | PIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

| R/W-1  | R/W-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-------|--------|-----|-----|-----|-----|-------|

| GIE    | DISI  | SWTRAP | _   | _   | _   | _   | _     |

| bit 15 | •     |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   | _   | _   | _   | INT2EP | INT1EP | INT0EP |

| bit 7 |     |     |     |     |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 GIE: Global Interrupt Enable bit

1 = Interrupts and associated IE bits are enabled

0 = Interrupts are disabled, but traps are still enabled

bit 14 DISI: DISI Instruction Status bit

1 = DISI instruction is active 0 = DISI instruction is not active

bit 13 **SWTRAP:** Software Trap Status bit

1 = Software trap is enabled0 = Software trap is disabled

bit 12-3 **Unimplemented:** Read as '0'

bit 2 INT2EP: External Interrupt 2 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 1 INT1EP: External Interrupt 1 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

bit 0 INT0EP: External Interrupt 0 Edge Detect Polarity Select bit

1 = Interrupt on negative edge0 = Interrupt on positive edge

#### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

|--------|-----|-----|-----|-----|-----|-----|---------|

| _      | _   | _   | _   | _   | _   | _   | PLLDIV8 |

| bit 15 |     |     |     |     |     |     | bit 8   |

| R/W-0   | R/W-0   | R/W-1   | R/W-1   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PLLDIV7 | PLLDIV6 | PLLDIV5 | PLLDIV4 | PLLDIV3 | PLLDIV2 | PLLDIV1 | PLLDIV0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 **Unimplemented:** Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

111111111 **= 513**

Ť

000110000 = 50 (default)

•

•

•

000000010 = 4

00000001 = 3

000000000 = 2

# REGISTER 11-13: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------|-------|-------|-------|

| _     |       |       |       | SS2R<6:0> |       |       |       |

| bit 7 |       |       |       |           |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 Unimplemented: Read as '0'

bit 6-0 **SS2R<6:0>:** Assign SPI2 Slave Select (SS2) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

# REGISTER 11-14: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26 (dsPIC33EPXXXGP/MC50X DEVICES ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | C1RXR<6:0> | •     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 Unimplemented: Read as '0'

bit 6-0 C1RXR<6:0>: Assign CAN1 RX Input (CRX1) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

•

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

# REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP35  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP35R<5:0>: Peripheral Output Function is Assigned to RP35 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP20R<5:0>: Peripheral Output Function is Assigned to RP20 Output Pin bits

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP37  | R<5:0> |       |       |

| bit 15 | _   |       | _     | _     | _      |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| _     | _   |       | RP36R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP37R<5:0>: Peripheral Output Function is Assigned to RP37 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP36R<5:0>: Peripheral Output Function is Assigned to RP36 Output Pin bits

(see Table 11-3 for peripheral function numbers)

# REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|

| _      | _   |       | RP43R<5:0> |       |       |       |       |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| _     | _   |       | RP42R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP43R<5:0>: Peripheral Output Function is Assigned to RP43 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP42R<5:0>: Peripheral Output Function is Assigned to RP42 Output Pin bits

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|

| _      | _   |       | RP55R<5:0> |       |       |       |       |  |

| bit 15 | _   |       | _          | _     |       | _     | bit 8 |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| _     | _   |       | RP54R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP55R<5:0>:** Peripheral Output Function is Assigned to RP55 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP54R<5:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits

(see Table 11-3 for peripheral function numbers)

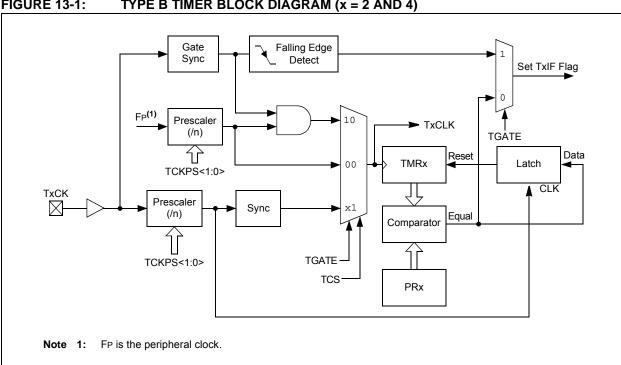

**FIGURE 13-1:** TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

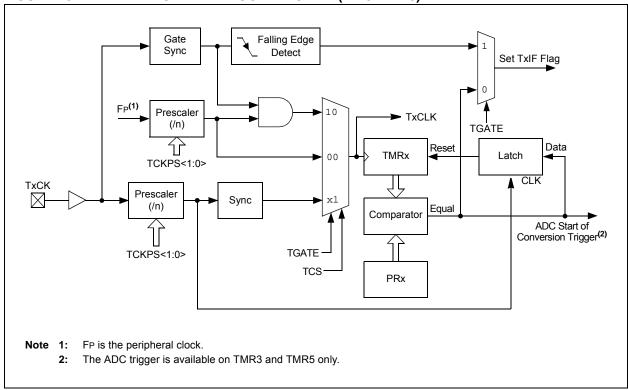

#### **FIGURE 13-2:** TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

## REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

bit 7-6 **DTC<1:0>:** Dead-Time Control bits

11 = Dead-Time Compensation mode

10 = Dead-time function is disabled

01 = Negative dead time is actively applied for Complementary Output mode

00 = Positive dead time is actively applied for all output modes

bit 5 DTCP: Dead-Time Compensation Polarity bit (3)

When Set to '1':

If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened. If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.

When Set to '0':

If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened. If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.

bit 4 Unimplemented: Read as '0'

bit 3 MTBS: Master Time Base Select bit

- 1 = PWM generator uses the secondary master time base for synchronization and as the clock source for the PWM generation logic (if secondary time base is available)

- 0 = PWM generator uses the primary master time base for synchronization and as the clock source for the PWM generation logic

bit 2 **CAM:** Center-Aligned Mode Enable bit<sup>(2,4)</sup>

1 = Center-Aligned mode is enabled

0 = Edge-Aligned mode is enabled

bit 1 XPRES: External PWMx Reset Control bit (5)

- 1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base mode

- 0 = External pins do not affect PWMx time base

bit 0 **IUE:** Immediate Update Enable bit<sup>(2)</sup>

- 1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate

- 0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary

- Note 1: Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.

- 2: These bits should not be changed after the PWMx is enabled (PTEN = 1).

- 3: DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.

- 4: The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- 5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| R/W-0    | R/W-0  | R/W-0    | U-0 | R/W-0, HC | R/W-0                | R-0   | R-1   |

|----------|--------|----------|-----|-----------|----------------------|-------|-------|

| UTXISEL1 | UTXINV | UTXISEL0 | _   | UTXBRK    | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15   |        |          |     |           |                      |       | bit 8 |

| R/W-0    | R/W-0    | R/W-0 | R-1   | R-0       | R-0 | R/C-0 | R-0   |

|----------|----------|-------|-------|-----------|-----|-------|-------|

| URXISEL1 | URXISEL0 | ADDEN | RIDLE | PERR FERR |     | OERR  | URXDA |

| bit 7    |          |       |       |           |     |       | bit 0 |

Legend:

HC = Hardware Clearable bit

C = Clearable bit

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

- bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

#### If IREN = 0:

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

#### If IREN = 1:

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 **Unimplemented:** Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit(1)

- 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled by the PORT

- bit 9 **UTXBF:** UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 **TRMT:** Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UARTx module for transmit operation.

| dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |  |

|-----------------------------------------------------------------|--|

| NOTES:                                                          |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

|                                                                 |  |

## 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

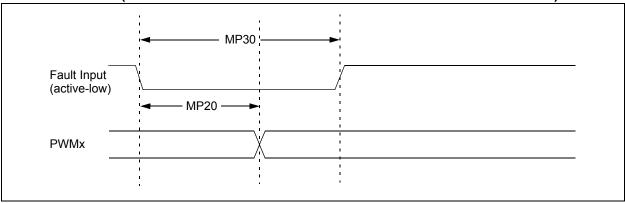

FIGURE 30-9: HIGH-SPEED PWMx MODULE FAULT TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

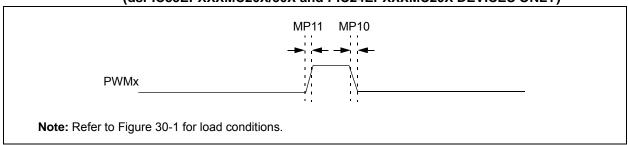

FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                  |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |      |       |                    |

|--------------------|--------|----------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>    | Min. | Тур.                                                                                                                                                                                                                                             | Max. | Units | Conditions         |

| MP10               | TFPWM  | PWMx Output Fall Time            | _    | _                                                                                                                                                                                                                                                | _    | ns    | See Parameter DO32 |

| MP11               | TRPWM  | PWMx Output Rise Time            | _    | _                                                                                                                                                                                                                                                | _    | ns    | See Parameter DO31 |

| MP20               | TFD    | Fault Input ↓ to PWMx I/O Change |      | _                                                                                                                                                                                                                                                | 15   | ns    |                    |

| MP30               | TFH    | Fault Input Pulse Width          | 15   | _                                                                                                                                                                                                                                                | _    | ns    |                    |

Note 1: These parameters are characterized but not tested in manufacturing.

TABLE 30-58: ADC MODULE SPECIFICATIONS (12-BIT MODE)

| AC CHA       | AC CHARACTERISTICS |                                               |                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |         |            |                                                                              |  |  |

|--------------|--------------------|-----------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol             | Characteristic                                | Min. Typ. Max. Units |                                                                                                                                                                                                                                                                 |         | Conditions |                                                                              |  |  |

|              |                    | ADC A                                         | Accuracy             | (12-Bit                                                                                                                                                                                                                                                         | Mode)   |            |                                                                              |  |  |

| AD20a        | Nr                 | Resolution                                    | 12                   | 2 Data Bi                                                                                                                                                                                                                                                       | ts      | bits       |                                                                              |  |  |

| AD21a        | INL                | Integral Nonlinearity                         | -2.5                 |                                                                                                                                                                                                                                                                 | 2.5     | LSb        | $-40^{\circ}C \le TA \le +85^{\circ}C \text{ (Note 2)}$                      |  |  |

|              |                    |                                               | -5.5                 | _                                                                                                                                                                                                                                                               | 5.5     | LSb        | $+85^{\circ}C < TA \le +125^{\circ}C$ (Note 2)                               |  |  |

| AD22a        | DNL                | Differential Nonlinearity                     | -1                   | _                                                                                                                                                                                                                                                               | 1       | LSb        | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C} \text{ (Note 2)}$ |  |  |

|              |                    |                                               | -1                   | _                                                                                                                                                                                                                                                               | 1       | LSb        | $+85^{\circ}C < TA \le +125^{\circ}C$ (Note 2)                               |  |  |

| AD23a        | GERR               | Gain Error <sup>(3)</sup>                     | -10                  | _                                                                                                                                                                                                                                                               | 10      | LSb        | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C} \text{ (Note 2)}$ |  |  |

|              |                    |                                               | -10                  | _                                                                                                                                                                                                                                                               | 10      | LSb        | $+85^{\circ}C < TA \le +125^{\circ}C$ (Note 2)                               |  |  |

| AD24a        | Eoff               | Offset Error                                  | -5                   | _                                                                                                                                                                                                                                                               | 5       | LSb        | $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C} \text{ (Note 2)}$ |  |  |

|              |                    |                                               | -5                   |                                                                                                                                                                                                                                                                 | 5       | LSb        | $+85^{\circ}C < TA \le +125^{\circ}C$ (Note 2)                               |  |  |

| AD25a        |                    | Monotonicity                                  | _                    | _                                                                                                                                                                                                                                                               | _       |            | Guaranteed                                                                   |  |  |

|              |                    | Dynamic                                       | Performa             | nce (12                                                                                                                                                                                                                                                         | Bit Mod | e)         |                                                                              |  |  |

| AD30a        | THD                | Total Harmonic Distortion <sup>(3)</sup>      | _                    | 75                                                                                                                                                                                                                                                              | _       | dB         |                                                                              |  |  |

| AD31a        | SINAD              | Signal to Noise and Distortion <sup>(3)</sup> | _                    | 68                                                                                                                                                                                                                                                              | 1       | dB         |                                                                              |  |  |

| AD32a        | SFDR               | Spurious Free Dynamic<br>Range <sup>(3)</sup> | _                    | 80                                                                                                                                                                                                                                                              | _       | dB         |                                                                              |  |  |

| AD33a        | FNYQ               | Input Signal Bandwidth <sup>(3)</sup>         | _                    | 250                                                                                                                                                                                                                                                             |         | kHz        |                                                                              |  |  |

| AD34a        | ENOB               | Effective Number of Bits <sup>(3)</sup>       | 11.09                | 11.3                                                                                                                                                                                                                                                            | _       | bits       |                                                                              |  |  |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

- 2: For all accuracy specifications, VINL = AVSS = VREFL = 0V and AVDD = VREFH = 3.6V.

- 3: Parameters are characterized but not tested in manufacturing.

| dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |

|-----------------------------------------------------------------|

| NOTES:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

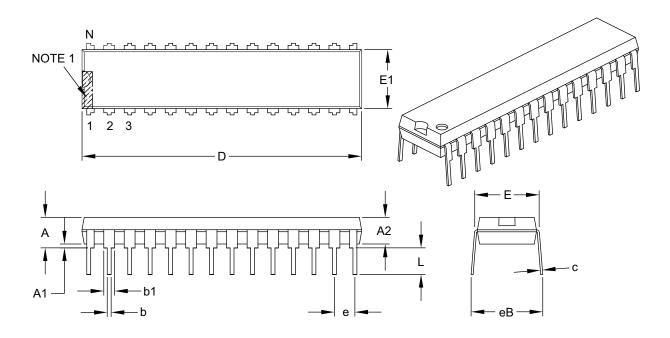

# 33.2 Package Details

# 28-Lead Skinny Plastic Dual In-Line (SP) - 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          | INCHES |       |  |

|----------------------------|------------------|----------|--------|-------|--|

| Dimension                  | Dimension Limits |          | NOM    | MAX   |  |

| Number of Pins             | N                |          | 28     |       |  |

| Pitch                      | е                | .100 BSC |        |       |  |

| Top to Seating Plane       | Α                | _        | _      | .200  |  |

| Molded Package Thickness   | A2               | .120     | .135   | .150  |  |

| Base to Seating Plane      | A1               | .015     | _      | _     |  |

| Shoulder to Shoulder Width | Е                | .290     | .310   | .335  |  |

| Molded Package Width       | E1               | .240     | .285   | .295  |  |

| Overall Length             | D                | 1.345    | 1.365  | 1.400 |  |

| Tip to Seating Plane       | L                | .110     | .130   | .150  |  |

| Lead Thickness             | С                | .008     | .010   | .015  |  |

| Upper Lead Width           | b1               | .040     | .050   | .070  |  |

| Lower Lead Width           | b                | .014     | .018   | .022  |  |

| Overall Row Spacing §      | eВ               | _        | _      | .430  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

# APPENDIX A: REVISION HISTORY

# Revision A (April 2011)

This is the initial released version of the document.

# Revision B (July 2011)

This revision includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-1.

TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                     | Update Description                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Digital Signal Controllers<br>and Microcontrollers" | Changed all pin diagrams references of VLAP to TLA.                                                                                                                                                                                                                                                                     |

| Section 4.0 "Memory Organization"                                                | Updated the All Resets values for CLKDIV and PLLFBD in the System Control Register Map (see Table 4-35).                                                                                                                                                                                                                |

| Section 5.0 "Flash Program Memory"                                               | Updated "one word" to "two words" in the first paragraph of Section 5.2 "RTSP Operation".                                                                                                                                                                                                                               |

| Section 9.0 "Oscillator Configuration"                                           | Updated the PLL Block Diagram (see Figure 9-2).  Updated the Oscillator Mode, Fast RC Oscillator (FRC) with divide-by-N and PLL (FRCPLL), by changing (FRCDIVN + PLL) to (FRCPLL).                                                                                                                                      |

|                                                                                  | Changed (FRCDIVN + PLL) to (FRCPLL) for COSC<2:0> = 001 and NOSC<2:0> = 001 in the Oscillator Control Register (see Register 9-1).                                                                                                                                                                                      |

|                                                                                  | Changed the POR value from 0 to 1 for the DOZE<1:0> bits, from 1 to 0 for the FRCDIV<0> bit, and from 0 to 1 for the PLLPOST<0> bit; Updated the default definitions for the DOZE<2:0> and FRCDIV<2:0> bits and updated all bit definitions for the PLLPOST<1:0> bits in the Clock Divisor Register (see Register 9-2). |

|                                                                                  | Changed the POR value from 0 to 1 for the PLLDIV<5:4> bits and updated the default definitions for all PLLDIV<8:0> bits in the PLL Feedback Division Register (see Register 9-2).                                                                                                                                       |

| Section 22.0 "Charge Time Measurement Unit (CTMU)"                               | Updated the bit definitions for the IRNG<1:0> bits in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                            |

| Section 25.0 "Op amp/<br>Comparator Module"                                      | Updated the voltage reference block diagrams (see Figure 25-1 and Figure 25-2).                                                                                                                                                                                                                                         |

TABLE A-5: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                      | Update Description                                                                                                                                                             |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 30.0 "Electrical                          | Throughout: qualifies all footnotes relating to the operation of analog modules below                                                                                          |

| Characteristics"                                  | VDDMIN (replaces "will have" with "may have")                                                                                                                                  |

|                                                   | Throughout: changes all references of SPI timing parameter symbol "TscP" to "FscP"                                                                                             |

|                                                   | Table 30-1: changes VDD range to 3.0V to 3.6V                                                                                                                                  |

|                                                   | Table 30-4: removes Parameter DC12 (RAM Retention Voltage)                                                                                                                     |

|                                                   | <ul> <li>Table 30-7: updates Maximum values at 10 and 20 MIPS</li> </ul>                                                                                                       |

|                                                   | <ul> <li>Table 30-8: adds Maximum IPD values, and removes all ∆IWDT entries</li> </ul>                                                                                         |

|                                                   | <ul> <li>Adds new Table 30-9 (Watchdog Timer Delta Current) with consolidated values<br/>removed from Table 30-8. All subsequent tables are renumbered accordingly.</li> </ul> |

|                                                   | <ul> <li>Table 30-10: adds footnote for all parameters for 1:2 Doze ratio</li> <li>Table 30-11:</li> </ul>                                                                     |

|                                                   | - changes Minimum and Maximum values for D120 and D130                                                                                                                         |

|                                                   | - adds Minimum and Maximum values for D131                                                                                                                                     |

|                                                   | <ul> <li>adds Minimum and Maximum values for D150 through D156, and removes</li> <li>Typical values</li> </ul>                                                                 |

|                                                   | • Table 30-12:                                                                                                                                                                 |

|                                                   | - reformats table for readability                                                                                                                                              |

|                                                   | - changes IoL conditions for DO10                                                                                                                                              |

|                                                   | Table 30-14: adds footnote to D135                                                                                                                                             |

|                                                   | Table 30-17: changes Minimum and Maximum values for OS30                                                                                                                       |

|                                                   | • Table 30-19:                                                                                                                                                                 |

|                                                   | - splits temperature range and adds new values for F20a                                                                                                                        |

|                                                   | <ul> <li>reduces temperature range for F20b to extended temperatures only</li> <li>Table 30-20:</li> </ul>                                                                     |

|                                                   | - splits temperature range and adds new values for F21a                                                                                                                        |

|                                                   | reduces temperature range for F20b to extended temperatures only                                                                                                               |

|                                                   | • Table 30-53:                                                                                                                                                                 |

|                                                   | - adds Maximum value to CM30                                                                                                                                                   |

|                                                   | - adds footnote ("Parameter characterized") to multiple parameters                                                                                                             |

|                                                   | Table 30-55: adds Minimum and Maximum values for all CTMUI specifications, and                                                                                                 |

|                                                   | removes Typical values                                                                                                                                                         |

|                                                   | Table 30-57: adds new footnote to AD09  Table 30-50:                                                                                                                           |

|                                                   | • Table 30-58:                                                                                                                                                                 |

|                                                   | <ul> <li>removes all specifications for accuracy with external voltage references</li> <li>removes Typical values for AD23a and AD24a</li> </ul>                               |

|                                                   | <ul> <li>replaces Minimum and Maximum values for AD21a, AD22a, AD23a and AD24a</li> <li>with new values, split by Industrial and Extended temperatures</li> </ul>              |

|                                                   | - removes Maximum value of AD30                                                                                                                                                |

|                                                   | - removes Minimum values from AD31a and AD32a                                                                                                                                  |

|                                                   | <ul> <li>adds or changes Typical values for AD30, AD31a, AD32a and AD33a</li> <li>Table 30-59:</li> </ul>                                                                      |

|                                                   | - removes all specifications for accuracy with external voltage references - removes Maximum value of AD30                                                                     |

|                                                   | - removes Typical values for AD23b and AD24b                                                                                                                                   |

|                                                   | - replaces Minimum and Maximum values for AD21b, AD22b, AD23b and AD24b                                                                                                        |

|                                                   | with new values, split by Industrial and Extended temperatures                                                                                                                 |

|                                                   | - removes Minimum and Maximum values from AD31b, AD32b, AD33b and AD34b                                                                                                        |

|                                                   | - adds or changes Typical values for AD30, AD31a, AD32a and AD33a                                                                                                              |

|                                                   | Table 30-61: Adds footnote to AD51                                                                                                                                             |

| Section 32.0 "DC and AC<br>Device Characteristics | <ul> <li>Updates Figure 32-6 (Typical IDD @ 3.3V) with individual current vs. processor speed<br/>curves for the different program memory sizes</li> </ul>                     |

| Graphs"                                           |                                                                                                                                                                                |

| Section 33.0 "Packaging Information"              | <ul> <li>Replaces drawing C04-149C (64-pin QFN, 7.15 x 7.15 exposed pad) with C04-154A<br/>(64-pin QFN, 5.4 x 5.4 exposed pad)</li> </ul>                                      |

| Remappable Input for U1RX                         | 176      | Memory Map for PIC24EP256GP/MC20X/50X                                 |       |          |

|---------------------------------------------------|----------|-----------------------------------------------------------------------|-------|----------|

| Reset System                                      |          | Devices6                                                              |       |          |

| Shared Port Structure                             |          | Memory Map for PIC24EP32GP/MC20X/50X                                  |       | 00       |

| Single-Phase Synchronous Buck Converter           |          | Devices                                                               |       | 57       |

|                                                   |          | Memory Map for PIC24EP512GP/MC20X/50X                                 |       | 51       |

| SPIx ModuleSuggested Oscillator Circuit Placement |          |                                                                       |       | 61       |

| Type B Timer (Timer2 and Timer4)                  |          | Devices Memory Map for PIC24EP64GP/MC20X/50X                          |       | 0 1      |

|                                                   |          | •                                                                     |       | E0       |

| Type B/Type C Timer Pair (32-Bit Timer)           |          | Devices                                                               |       |          |

| Type C Timer (Timer3 and Timer5)                  |          | Near Data Space                                                       |       |          |

| UARTx Module                                      |          | Organization, Alignment                                               |       |          |

| User-Programmable Blanking Function               |          | SFR Space                                                             |       |          |

| Watchdog Timer (WDT)                              |          | Width                                                                 | ••••• | 51       |

| Brown-out Reset (BOR)                             | 384      | Data Memory                                                           |       |          |

| С                                                 |          | Arbitration and Bus Master Priority                                   |       | 110      |

|                                                   |          | Data Space                                                            |       |          |

| C Compilers                                       | 000      | Extended X                                                            |       |          |

| MPLAB XC Compilers                                | 398      | Paged Memory Scheme                                                   |       | 105      |

| Charge Time Measurement Unit. See CTMU.           |          | DC and AC Characteristics                                             |       |          |

| Code Examples                                     |          | Graphs                                                                |       | 475      |

| IC1 Connection to QEI1 Input on                   |          | DC Characteristics                                                    |       |          |

| Pin 43 of dsPIC33EPXXXMC206                       |          | BOR                                                                   |       |          |

| Port Write/Read                                   | 174      | CTMU Current Source Requirements                                      |       | 458      |

| PWMx Write-Protected Register                     |          | Doze Current (IDOZE)                                                  | 407,  | 469      |

| Unlock Sequence                                   |          | High Temperature                                                      |       | 468      |

| PWRSAV Instruction Syntax                         | 163      | I/O Pin Input Specifications                                          |       | 408      |

| Code Protection                                   | 379, 386 | I/O Pin Output Specifications                                         | 411,  | 470      |

| CodeGuard Security                                | 379, 386 | Idle Current (IIDLE)                                                  | 405,  | 469      |

| Configuration Bits                                | 379      | Op Amp/Comparator Requirements                                        |       | 455      |

| Description                                       | 381      | Op Amp/Comparator Voltage Reference                                   |       |          |

| Configuration Byte Register Map                   | 380      | Requirements                                                          |       | 457      |

| Configuring Analog and Digital Port Pins          |          | Operating Current (IDD)                                               |       |          |

| CPU                                               |          | Operating MIPS vs. Voltage                                            |       |          |

| Addressing Modes                                  | 35       | Power-Down Current (IPD)                                              |       |          |

| Clocking System Options                           |          | Program Memory                                                        |       |          |

| Fast RC (FRC) Oscillator                          |          | Temperature and Voltage                                               |       |          |

| FRC Oscillator with PLL                           |          | Temperature and Voltage Specifications                                |       |          |

| FRC Oscillator with Postscaler                    |          | Thermal Operating Conditions                                          |       |          |

| Low-Power RC (LPRC) Oscillator                    |          |                                                                       |       |          |

| Primary (XT, HS, EC) Oscillator                   |          | Watchdog Timer Delta Current  Demo/Development Boards, Evaluation and |       | 407      |

| Primary Oscillator with PLL                       |          | •                                                                     |       | 400      |

|                                                   |          | Starter Kits                                                          |       |          |

| Control Registers                                 |          | Development Support                                                   |       |          |

| Data Space Addressing                             |          | Third-Party Tools                                                     |       | 400      |

| Instruction Set                                   |          | DMA Controller                                                        |       | 4.40     |

| Resources                                         | 39       | Channel to Peripheral Associations                                    |       |          |

| CTMU                                              | 0.47     | Control Registers                                                     |       |          |

| Control Registers                                 |          | DMAxCNT                                                               |       |          |

| Resources                                         |          | DMAxCON                                                               |       |          |

| Customer Change Notification Service              |          | DMAxPAD                                                               |       |          |

| Customer Notification Service                     |          | DMAxREQ                                                               |       |          |

| Customer Support                                  | 524      | DMAxSTA                                                               |       |          |

| D                                                 |          | DMAxSTB                                                               |       | 141      |

|                                                   |          | Resources                                                             |       | 141      |

| Data Address Space                                |          | Supported Peripherals                                                 |       | 139      |

| Memory Map for dsPIC33EP128MC20X/50X,             |          | Doze Mode                                                             |       | 165      |

| dsPIC33EP128GP50X Devices                         | 54       | DSP Engine                                                            |       | 44       |

| Memory Map for dsPIC33EP256MC20X/50X,             |          | _                                                                     |       |          |

| dsPIC33EP256GP50X Devices                         | 55       | E                                                                     |       |          |

| Memory Map for dsPIC33EP32MC20X/50X,              |          | ECAN Message Buffers                                                  |       |          |

| dsPIC33EP32GP50X Devices                          | 52       | Word 0                                                                |       | 310      |

| Memory Map for dsPIC33EP512MC20X/50X,             |          | Word 1                                                                |       |          |

| dsPIC33EP512GP50X Devices                         |          | Word 2                                                                |       |          |

| Memory Map for dsPIC33EP64MC20X/50X,              |          | Word 3                                                                |       |          |

| dsPIC33EP64GP50X Devices                          | 53       | Word 4                                                                |       |          |

| Memory Map for PIC24EP128GP/MC20X/50X             |          | Word 5                                                                |       |          |

| Devices                                           |          | Word 6                                                                |       |          |

| DCV1003                                           |          | Word 7                                                                |       | 313      |

|                                                   |          | VVCICI /                                                              |       | - 3 1 .3 |