Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 48-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc204-e-mv |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

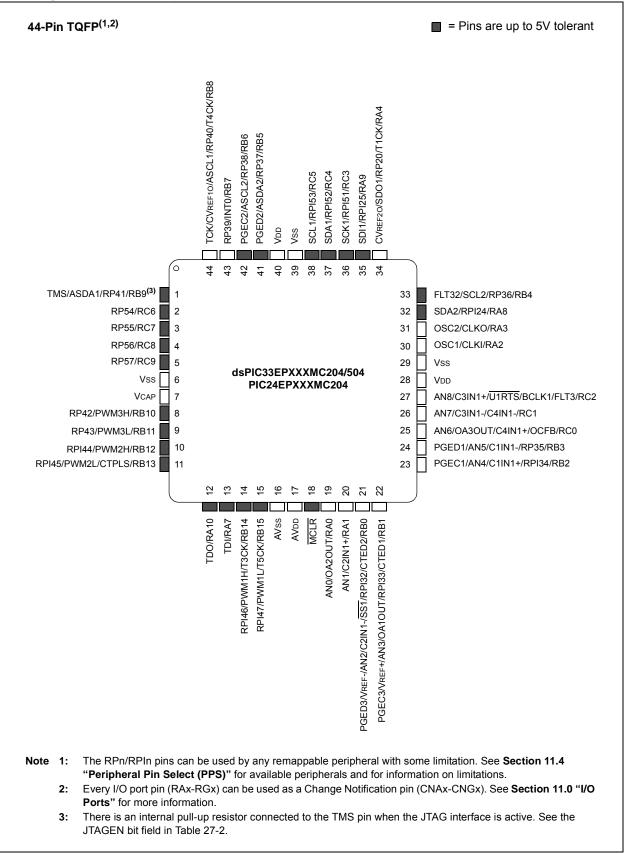

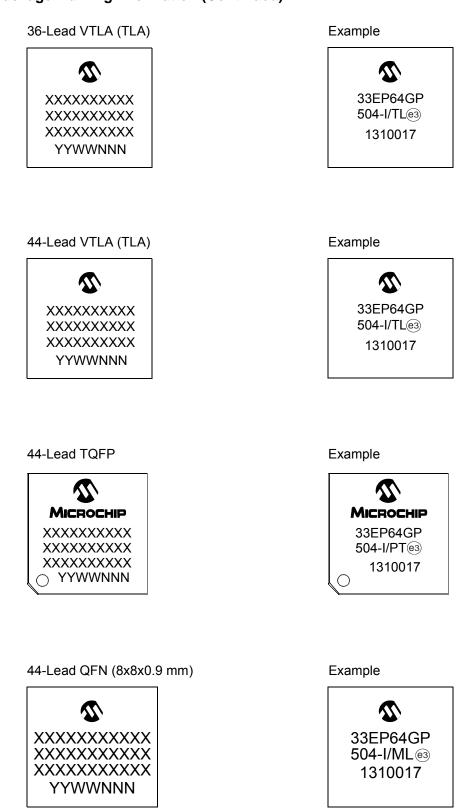

## Pin Diagrams (Continued)

| R/W-0               | U-0                                                                                                           | R/W-0                                                                                                                                                                                | R/W-0                   | R/W-0                       | R-0                | R-0                | R-0                |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------|--------------------|--------------------|--------------------|--|--|--|--|

| VAR                 | —                                                                                                             | US1 <sup>(1)</sup>                                                                                                                                                                   | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup> | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |  |  |  |  |

| bit 15              |                                                                                                               |                                                                                                                                                                                      |                         |                             |                    |                    | bit                |  |  |  |  |

| R/W-0               | R/W-0                                                                                                         | R/W-1                                                                                                                                                                                | R/W-0                   | R/C-0                       | R-0                | R/W-0              | R/W-0              |  |  |  |  |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>                                                                                           | SATDW <sup>(1)</sup>                                                                                                                                                                 | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                | RND <sup>(1)</sup> | IF(1)              |  |  |  |  |

| bit 7               | I                                                                                                             |                                                                                                                                                                                      |                         |                             | 1                  | 1                  | bit                |  |  |  |  |

| Legend:             |                                                                                                               | C = Clearable                                                                                                                                                                        | e bit                   |                             |                    |                    |                    |  |  |  |  |

| R = Readabl         | e bit                                                                                                         | W = Writable                                                                                                                                                                         | bit                     | U = Unimpler                | mented bit, read   | d as '0'           |                    |  |  |  |  |

| -n = Value at       | POR                                                                                                           | '1' = Bit is set                                                                                                                                                                     | t                       | '0' = Bit is cle            | ared               | x = Bit is unkr    | nown               |  |  |  |  |

| bit 15              | 1 = Variable                                                                                                  | le Exception Pro<br>exception proce                                                                                                                                                  | essing latency          | is enabled                  |                    |                    |                    |  |  |  |  |

| bit 14              |                                                                                                               | nted: Read as '                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

| bit 13-12           | -                                                                                                             | SP Multiply Uns                                                                                                                                                                      |                         | Control bits <sup>(1)</sup> |                    |                    |                    |  |  |  |  |

|                     | 10 = DSP er<br>01 = DSP er<br>00 = DSP er                                                                     | <ul> <li>11 = Reserved</li> <li>10 = DSP engine multiplies are mixed-sign</li> <li>01 = DSP engine multiplies are unsigned</li> <li>00 = DSP engine multiplies are signed</li> </ul> |                         |                             |                    |                    |                    |  |  |  |  |

| bit 11              | •                                                                                                             | O Loop Terminatives executing Dot<br>t                                                                                                                                               |                         |                             | iteration          |                    |                    |  |  |  |  |

| bit 10-8            | DL<2:0>: DO Loop Nesting Level Status bits <sup>(1)</sup><br>111 = 7 DO loops are active                      |                                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

|                     | •                                                                                                             |                                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

|                     | •                                                                                                             |                                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

|                     | 001 = 1 DO loop is active<br>000 = 0 DO loops are active                                                      |                                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

| bit 7               | SATA: ACCA                                                                                                    | A Saturation En                                                                                                                                                                      | able bit <sup>(1)</sup> |                             |                    |                    |                    |  |  |  |  |

|                     | <ul> <li>1 = Accumulator A saturation is enabled</li> <li>0 = Accumulator A saturation is disabled</li> </ul> |                                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

| bit 6               | SATB: ACCE                                                                                                    | B Saturation En                                                                                                                                                                      | able bit <sup>(1)</sup> |                             |                    |                    |                    |  |  |  |  |

|                     |                                                                                                               | ator B saturatio<br>ator B saturatio                                                                                                                                                 |                         |                             |                    |                    |                    |  |  |  |  |

| bit 5               | SATDW: Data Space Write from DSP Engine Saturation Enable bit <sup>(1)</sup>                                  |                                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

|                     |                                                                                                               | ace write satura<br>ace write satura                                                                                                                                                 |                         | I                           |                    |                    |                    |  |  |  |  |

| bit 4               | ACCSAT: Accumulator Saturation Mode Select bit <sup>(1)</sup>                                                 |                                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

|                     | <ul><li>1 = 9.31 saturation (super saturation)</li><li>0 = 1.31 saturation (normal saturation)</li></ul>      |                                                                                                                                                                                      |                         |                             |                    |                    |                    |  |  |  |  |

| bit 3               |                                                                                                               | nterrupt Priority                                                                                                                                                                    |                         |                             |                    |                    |                    |  |  |  |  |

|                     |                                                                                                               | errupt Priority Le<br>errupt Priority Le                                                                                                                                             |                         |                             |                    |                    |                    |  |  |  |  |

|                     | nis bit is availabl                                                                                           |                                                                                                                                                                                      | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP         | 50X devices on     | ly.                |  |  |  |  |

| 2: Th               | nis bit is always                                                                                             | reau as 0.                                                                                                                                                                           |                         |                             |                    |                    |                    |  |  |  |  |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

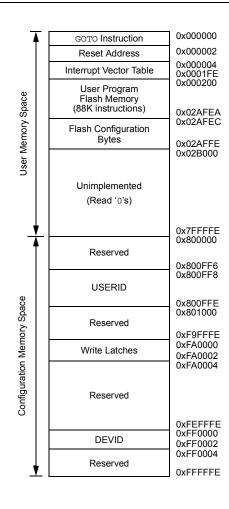

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>            |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PAE   | )<7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0                                | U-0   | R/W-0 | R/W-0 | R/W-0                              | R/W-0            | R/W-0           | R/W-0 |

|------------------------------------|-------|-------|-------|------------------------------------|------------------|-----------------|-------|

| —                                  |       |       |       | CNT<                               | 13:8> <b>(2)</b> |                 |       |

| bit 15                             |       |       |       |                                    |                  |                 | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0            | R/W-0           | R/W-0 |

|                                    |       |       | CNT<  | <7:0> <b>(2)</b>                   |                  |                 |       |

| bit 7                              |       |       |       |                                    |                  |                 | bit 0 |

| Legend:                            |       |       |       |                                    |                  |                 |       |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0' |                  |                 |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is clea                  | ared             | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                             | R/W-0           | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|

| ROON          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ROSSLP                                                            | ROSEL           | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                   |                 |                       |                       | •                     | bit                   |  |  |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                               | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |

|               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                 |                 | _                     |                       | _                     |                       |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                   |                 |                       |                       |                       | bit                   |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                   |                 |                       |                       |                       |                       |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable                                                      | bit             | U = Unimpler          | nented bit, read      | l as '0'              |                       |  |  |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | '1' = Bit is set                                                  |                 | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as ' | out is disabled |                       | .K pin <sup>(2)</sup> |                       |                       |  |  |

| bit 13        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ference Oscilla                                                   |                 | en hit                |                       |                       |                       |  |  |

|               | 1 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | e oscillator out<br>e oscillator out                              | out continues   | to run in Sleep       |                       |                       |                       |  |  |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | erence Oscillato<br>crystal is used<br>lock is used as            | as the refere   | nce clock             |                       |                       |                       |  |  |

| bit 11-8      | <ul> <li>0 = System clock is used as the reference clock</li> <li>RODIV&lt;3:0&gt;: Reference Oscillator Divider bits<sup>(1)</sup></li> <li>1111 = Reference clock divided by 32,768</li> <li>1100 = Reference clock divided by 16,384</li> <li>1101 = Reference clock divided by 4,096</li> <li>1011 = Reference clock divided by 2,048</li> <li>1010 = Reference clock divided by 1,024</li> <li>1001 = Reference clock divided by 512</li> <li>1000 = Reference clock divided by 256</li> <li>0111 = Reference clock divided by 128</li> <li>0110 = Reference clock divided by 128</li> <li>0110 = Reference clock divided by 4</li> <li>011 = Reference clock divided by 4</li> <li>001 = Reference clock divided by 4</li> <li>001 = Reference clock divided by 32</li> <li>0100 = Reference clock divided by 4</li> <li>001 = Reference clock divided by 4</li> </ul> |                                                                   |                 |                       |                       |                       |                       |  |  |

|               | 0000 = Refer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ence clock                                                        | -               |                       |                       |                       |                       |  |  |

### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

## REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                     | U-0                                  | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

|-------------------------|--------------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|

| _                       | _                                    |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |

| bit 15                  | <b>I</b>                             | •                                  |         |                  |                 |                 | bit 8   |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |

| U-0                     | R-1                                  | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

| _                       | ICODE6                               | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |

| bit 7                   |                                      |                                    |         |                  |                 |                 | bit     |  |  |  |

| Logondi                 |                                      |                                    |         |                  |                 |                 |         |  |  |  |

| Legend:<br>R = Readable | - hit                                |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |

| -n = Value at           |                                      | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |

| -n = value at           | POR                                  | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |

| bit 15-13               | Unimplemen                           | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 12-8                | =                                    | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |

|                         | 01111 <b>= Filte</b>                 | r 15                               |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 00001 = Filter 1<br>00000 = Filter 0 |                                    |         |                  |                 |                 |         |  |  |  |

| bit 7                   |                                      | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         |                                      | IFO almost full                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |

|                         | 1000010 = K<br>1000001 = E           | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |

|                         | 1000000 = N                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         | •                                    | B15 buffer inte                    | inupt   |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 0001001 <b>= R</b>                   | B9 buffer inter                    | rupt    |                  |                 |                 |         |  |  |  |

|                         |                                      | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         | 0000011 <b>= T</b>                   | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                                      | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |

## REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

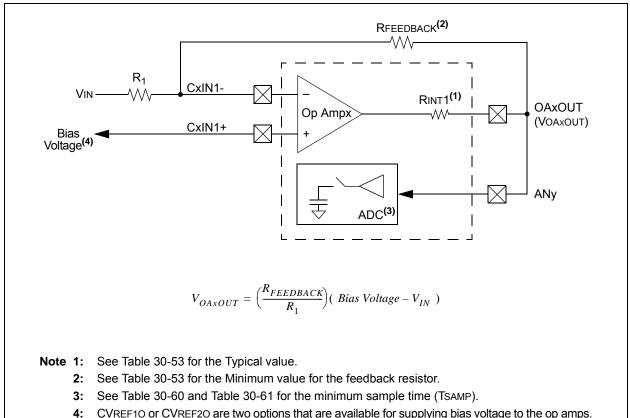

### 25.1.2 OP AMP CONFIGURATION B

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

## 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

NOTES:

## 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

# 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

## 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

## 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax    | Description                        | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------|------------------------------------|---------------|-------------------------------|--------------------------|

| 72                 | SL                   | SL     | f                  | f = Left Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG             | WREG = Left Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd              | Wd = Left Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Wb,Wns,Wnd         | Wnd = Left Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd       | Wnd = Left Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 73                 | SUB                  | SUB    | Acc <sup>(1)</sup> | Subtract Accumulators              | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SUB    | f                  | f = f – WREG                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | f,WREG             | WREG = f – WREG                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | #lit10,Wn          | Wn = Wn - lit10                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,Ws,Wd           | Wd = Wb – Ws                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,#lit5,Wd        | Wd = Wb - lit5                     | 1             | 1                             | C,DC,N,OV,Z              |

| 74                 | SUBB                 | SUBB   | f                  | $f = f - WREG - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | f,WREG             | WREG = f – WREG – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | #lit10,Wn          | $Wn = Wn - lit10 - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,Ws,Wd           | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,#lit5,Wd        | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 75                 | SUBR                 | SUBR   | f                  | f = WREG – f                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | f,WREG             | WREG = WREG – f                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,Ws,Wd           | Wd = Ws – Wb                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,#lit5,Wd        | Wd = lit5 – Wb                     | 1             | 1                             | C,DC,N,OV,Z              |

| 76                 | SUBBR                | SUBBR  | f                  | $f = WREG - f - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | f,WREG             | WREG = WREG – f – $(\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,Ws,Wd           | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,#lit5,Wd        | $Wd = lit5 - Wb - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 77                 | SWAP                 | SWAP.b | Wn                 | Wn = nibble swap Wn                | 1             | 1                             | None                     |

|                    |                      | SWAP   | Wn                 | Wn = byte swap Wn                  | 1             | 1                             | None                     |

| 78                 | TBLRDH               | TBLRDH | Ws,Wd              | Read Prog<23:16> to Wd<7:0>        | 1             | 5                             | None                     |

| 79                 | TBLRDL               | TBLRDL | Ws,Wd              | Read Prog<15:0> to Wd              | 1             | 5                             | None                     |

| 80                 | TBLWTH               | TBLWTH | Ws,Wd              | Write Ws<7:0> to Prog<23:16>       | 1             | 2                             | None                     |

| 81                 | TBLWTL               | TBLWTL | Ws,Wd              | Write Ws to Prog<15:0>             | 1             | 2                             | None                     |

| 82                 | ULNK                 | ULNK   |                    | Unlink Frame Pointer               | 1             | 1                             | SFA                      |

| 83                 | XOR                  | XOR    | f                  | f = f .XOR. WREG                   | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | f,WREG             | WREG = f.XOR. WREG                 | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | #lit10,Wn          | Wd = lit10 .XOR. Wd                | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd           | Wd = Wb .XOR. Ws                   | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd        | Wd = Wb .XOR. lit5                 | 1             | 1                             | N,Z                      |

| 84                 | ZE                   | ZE     | Ws,Wnd             | Wnd = Zero-extend Ws               | 1             | 1                             | C,Z,N                    |

## TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTE      | RISTICS                       |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                       |                 |  |  |  |

|------------------|-------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|--|--|--|

| Parameter<br>No. | Тур.                          | Max.          | Units                                                                                                                                                                                                                                                                                 | Condi                 | tions           |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                       | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |  |  |

| DC60d            | 30                            | 100           | μA                                                                                                                                                                                                                                                                                    | -40°C                 |                 |  |  |  |

| DC60a            | 35                            | 100           | μA                                                                                                                                                                                                                                                                                    | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 150                           | 200           | μA                                                                                                                                                                                                                                                                                    | +85°C                 | 3.3V            |  |  |  |

| DC60c            | 250                           | 500           | μA                                                                                                                                                                                                                                                                                    | +125°C                |                 |  |  |  |

| Power-Down Cu    | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF                                                                                                                                                                                                                                                                       | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |  |  |

| DC60d            | 25                            | 100           | μA                                                                                                                                                                                                                                                                                    | -40°C                 |                 |  |  |  |

| DC60a            | 30                            | 100           | μΑ                                                                                                                                                                                                                                                                                    | +25°C                 | 3.3V            |  |  |  |

| DC60b            | 150                           | 350           | μΑ                                                                                                                                                                                                                                                                                    | +85°C                 |                 |  |  |  |

| DC60c            | 350                           | 800           | μΑ                                                                                                                                                                                                                                                                                    | +125°C                |                 |  |  |  |