Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Betuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc204-h-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

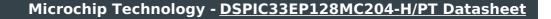

## Pin Diagrams (Continued)

# TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>      | —       |        | ICDIP<2:0  | >     | _        | —       | —           | _       | —       | _      | -           |        | 4400          |

| IPC36        | 0888  | -      | l      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<    | 2:0>  | _        | P       | TGSTEPIP<2  | :0>     | —       | —      |             |        | 4440          |

| IPC37        | 088A  |        | _      | _          | _       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | >       | _       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | —       | _      |            |       | —        | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | —          | —       | —       | _      |            |       | —        | _       | DAE         | DOOVR   | _       | —      |             |        | 0000          |

| INTCON4      | 08C6  | -      | _      | —          | _       | _       | _      |            | _     | _        | _       | —           | —       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | -      | —      | —          | _       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | M<7:0>  |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

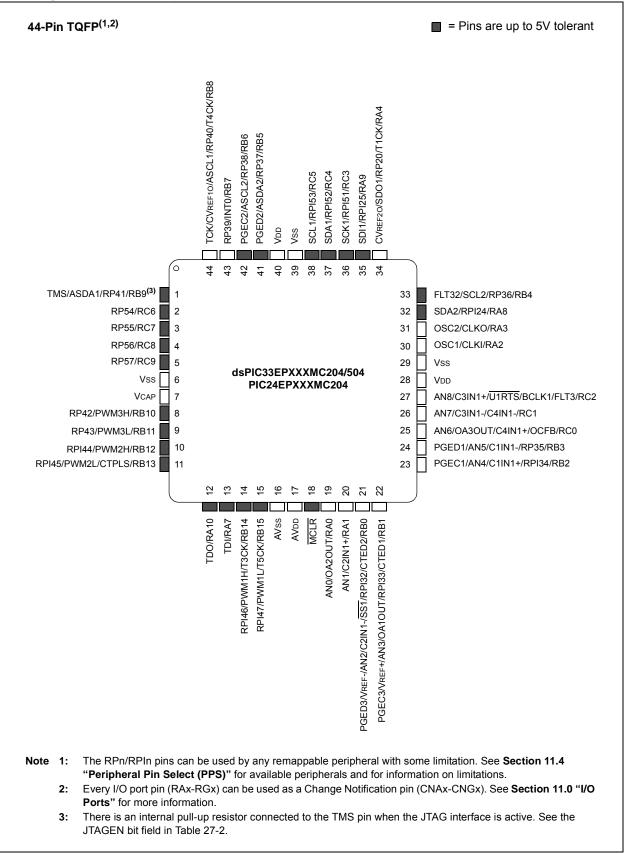

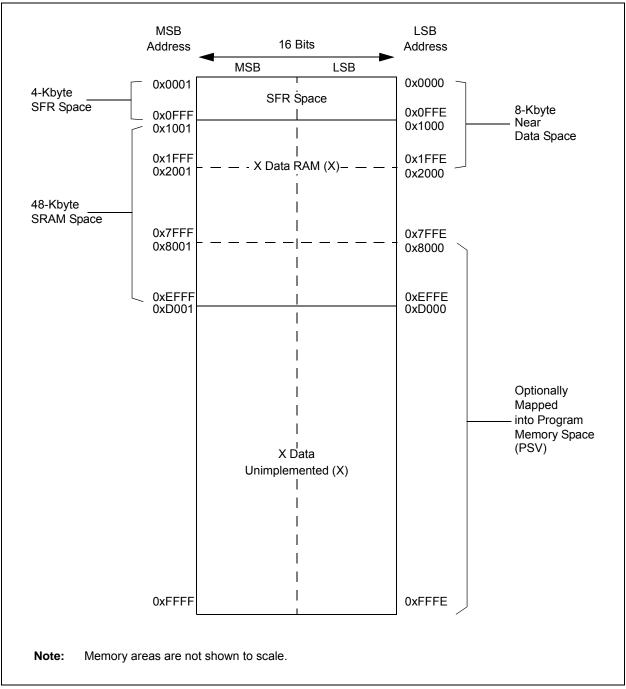

## 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

## TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

| A T                    | Access        | Program Space Address        |                    |          |        |     |  |  |

|------------------------|---------------|------------------------------|--------------------|----------|--------|-----|--|--|

| Access Type            | Space         | <23>                         | <22:16>            | <15>     | <14:1> | <0> |  |  |

| Instruction Access     | User          | 0                            | 0 PC<22:1>         |          |        |     |  |  |

| (Code Execution)       |               | 0xx xxxx xxxx xxxx xxxx xxxx |                    |          |        |     |  |  |

| TBLRD/TBLWT            | User          | TBLPAG<7:0> Data EA<15:0>    |                    |          |        |     |  |  |

| (Byte/Word Read/Write) |               | 0                            | xxx xxxx           | XXXX XXX | ***    |     |  |  |

|                        | Configuration | TB                           | TBLPAG<7:0> Data E |          |        |     |  |  |

|                        |               | 1                            | xxx xxxx           | XXXX XX  | ***    |     |  |  |

## FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

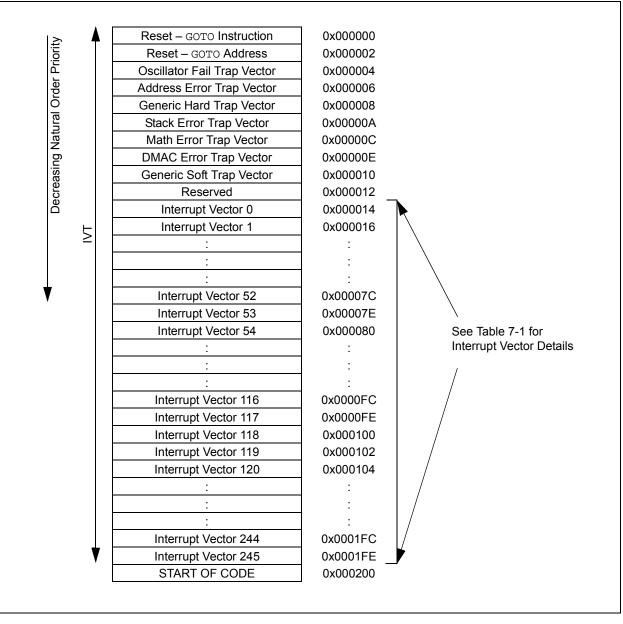

#### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

## 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP43  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| —      | —   |       |       | RP42  | R<5:0> |       |       |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|

| —      | —   |       | RP55R<5:0> |       |       |       |       |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0   | U-0              | U-0   | U-0                                | U-0   | R/W-0              | R/W-0   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|---------|--|

| CHPCLKEN                                                                                                                                                                                                                                                                                                                                                                                                                             | —     | —                | —     | —                                  | —     | CHOPC              | LK<9:8> |  |

| bit 15                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                  |       |                                    |       |                    | bit 8   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                  |       |                                    |       |                    |         |  |

| R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                  | CHOPC | LK<7:0>                            |       |                    |         |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                  |       |                                    |       |                    | bit 0   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                  |       |                                    |       |                    |         |  |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                  |       |                                    |       |                    |         |  |

| R = Readable I                                                                                                                                                                                                                                                                                                                                                                                                                       | bit   | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                    |         |  |

| -n = Value at P                                                                                                                                                                                                                                                                                                                                                                                                                      | OR    | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |         |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown   bit 15 CHPCLKEN: Enable Chop Clock Generator bit 1 = Chop clock generator is enabled 0 = Chop clock generator is disabled   bit 14-10 Unimplemented: Read as '0' 0'   bit 9-0 CHOPCLK<9:0>: Chop Clock Divider bits   The frequency of the chop clock signal is given by the following expression: Chop Frequency = (FP/PCLKDIV<2:0)/(CHOPCLK<9:0> + 1) |       |                  |       |                                    |       |                    |         |  |

## REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

#### REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|

|                                    |       |       | MDC   | <15:8>                                  |       |       |       |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |

|                                    |       |       |       |                                         |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | MD    | C<7:0>                                  |       |       |       |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |

|                                    |       |       |       |                                         |       |       |       |

| Legend:                            |       |       |       |                                         |       |       |       |

| R = Readable bit W = Writable bit  |       |       | bit   | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

## 21.2 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3 ECAN Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 21.3.1 KEY RESOURCES

- "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| 11.0   | 11.0 | 11.0 | 11.0 | 11.0 |          |          |         |

|--------|------|------|------|------|----------|----------|---------|

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| —      | _    |      |      |      | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |      |      |      |      |          |          | bit 8   |

|        |      |      |      |      |          |          |         |

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| 0-0   | 0-0 | 0-0 | 0-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | _   |     | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

# Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample MUXB bits

In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|

| value           | CH1         | CH2   | CH3   |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |

| 0x              | Vrefl       | Vrefl | VREFL |  |  |  |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |  |

|----------------|-------------|---------|---------|--|--|--|

| value          | CH1         | CH2     | CH3     |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '<u>0</u>':

| Value           | ADC Channel |       |       |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|

|                 | CH1         | CH2   | CH3   |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |

| 0x              | VREFL       | VREFL | Vrefl |  |  |  |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

# 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

# 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a То comprehensive reference source. complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

# 27.1 Configuration Bits

In dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored in at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to make certain that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

**Note:** Performing a page erase operation on the last page of program memory clears the Flash Configuration bytes, enabling code protection as a result. Therefore, users should avoid performing page erase operations on the last page of program memory.

The Configuration Flash bytes map is shown in Table 27-1.

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                                                                | Description                                       | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected        |

|--------------------|----------------------|-----------------|----------------------------------------------------------------|---------------------------------------------------|---------------|-------------------------------|---------------------------------|

| 53                 | NEG                  | NEG             | <sub>Acc</sub> (1)                                             | Negate Accumulator                                | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

|                    |                      | NEG             | f                                                              | $f = \overline{f} + 1$                            | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG             | f,WREG                                                         | WREG = $\overline{f}$ + 1                         | 1             | 1                             | C,DC,N,OV,Z                     |

|                    |                      | NEG             | Ws,Wd                                                          | $Wd = \overline{Ws} + 1$                          | 1             | 1                             | C,DC,N,OV,Z                     |

| 54                 | NOP                  | NOP             | · · · · · · · · · · · · · · · · · · ·                          | No Operation                                      | 1             | 1                             | None                            |

|                    |                      | NOPR            |                                                                | No Operation                                      | 1             | 1                             | None                            |

| 55                 | POP                  | POP             | f                                                              | Pop f from Top-of-Stack (TOS)                     | 1             | 1                             | None                            |

|                    |                      | POP             | Wdo                                                            | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1                             | None                            |

|                    |                      | POP.D           | Wnd                                                            | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2                             | None                            |

|                    |                      | POP.S           |                                                                | Pop Shadow Registers                              | 1             | 1                             | All                             |

| 56                 | PUSH                 | PUSH            | f                                                              | Push f to Top-of-Stack (TOS)                      | 1             | 1                             | None                            |

|                    |                      | PUSH            | Wso                                                            | Push Wso to Top-of-Stack (TOS)                    | 1             | 1                             | None                            |

|                    |                      | PUSH.D          | Wns                                                            | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2                             | None                            |

|                    |                      | PUSH.S          |                                                                | Push Shadow Registers                             | 1             | 1                             | None                            |

| 57                 | PWRSAV               | PWRSAV          | #lit1                                                          | Go into Sleep or Idle mode                        | 1             | 1                             | WDTO,Sleep                      |

| 58                 | RCALL                | RCALL           | Expr                                                           | Relative Call                                     | 1             | 4                             | SFA                             |

|                    |                      | RCALL           | Wn                                                             | Computed Call                                     | 1             | 4                             | SFA                             |

| 59                 | REPEAT               | REPEAT          | #lit15                                                         | Repeat Next Instruction lit15 + 1 times           | 1             | 1                             | None                            |

|                    |                      | REPEAT          | Wn                                                             | Repeat Next Instruction (Wn) + 1 times            | 1             | 1                             | None                            |

| 60                 | RESET                | RESET           |                                                                | Software device Reset                             | 1             | 1                             | None                            |

| 61                 | RETFIE               | RETFIE          |                                                                | Return from interrupt                             | 1             | 6 (5)                         | SFA                             |

| 62                 | RETLW                | RETLW           | #lit10,Wn                                                      | Return with literal in Wn                         | 1             | 6 (5)                         | SFA                             |

| 63                 | RETURN               | RETURN          |                                                                | Return from Subroutine                            | 1             | 6 (5)                         | SFA                             |

| 64                 | RLC                  | RLC             | f                                                              | f = Rotate Left through Carry f                   | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC             | f,WREG                                                         | WREG = Rotate Left through Carry f                | 1             | 1                             | C,N,Z                           |

|                    |                      | RLC             | Ws,Wd                                                          | Wd = Rotate Left through Carry Ws                 | 1             | 1                             | C,N,Z                           |

| 65                 | RLNC                 | RLNC            | f                                                              | f = Rotate Left (No Carry) f                      | 1             | 1                             | N,Z                             |

|                    |                      | RLNC            | f,WREG                                                         | WREG = Rotate Left (No Carry) f                   | 1             | 1                             | N,Z                             |

|                    |                      | RLNC            | Ws,Wd                                                          | Wd = Rotate Left (No Carry) Ws                    | 1             | 1                             | N,Z                             |

| 66                 | RRC                  | RRC             | f                                                              | f = Rotate Right through Carry f                  | 1             | 1                             | C,N,Z                           |

|                    |                      | RRC             | f,WREG                                                         | WREG = Rotate Right through Carry f               | 1             | 1                             | C,N,Z                           |

| 07                 |                      | RRC             | Ws,Wd                                                          | Wd = Rotate Right through Carry Ws                | 1             | 1                             | C,N,Z                           |

| 67                 | RRNC                 | RRNC            | f                                                              | f = Rotate Right (No Carry) f                     | 1             | 1                             | N,Z                             |

|                    |                      | RRNC            | f,WREG                                                         | WREG = Rotate Right (No Carry) f                  | 1             | 1                             | N,Z                             |

| <u></u>            | ~~~                  | RRNC            | Ws,Wd                                                          | Wd = Rotate Right (No Carry) Ws                   | 1             | 1                             | N,Z                             |

| 68                 | SAC                  | SAC             | Acc,#Slit4,Wdo <sup>(1)</sup><br>Acc,#Slit4,Wdo <sup>(1)</sup> | Store Accumulator                                 | 1             | 1                             | None                            |

| 60                 | CE                   | SAC.R           |                                                                | Store Rounded Accumulator                         | 1             | 1                             | None                            |

| 69<br>70           | SE                   | SE              | Ws,Wnd                                                         | Wnd = sign-extended Ws<br>f = 0xFFFF              | 1             | 1                             | C,N,Z<br>None                   |

| 10                 | SETM                 | SETM            | f                                                              |                                                   | -             | 1                             |                                 |

|                    |                      | SETM            | WREG                                                           | WREG = 0xFFFF<br>Ws = 0xFFFF                      | 1             | 1                             | None                            |

| 71                 | SFTAC                | SETM            | Ws<br>Acc, Wn <sup>(1)</sup>                                   | Arithmetic Shift Accumulator by (Wn)              | 1             | 1                             | None<br>OA,OB,OAB,<br>SA,SB,SAB |

|                    |                      | SFTAC           | Acc,#Slit6 <sup>(1)</sup>                                      | Arithmetic Shift Accumulator by Slit6             | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB         |

## TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

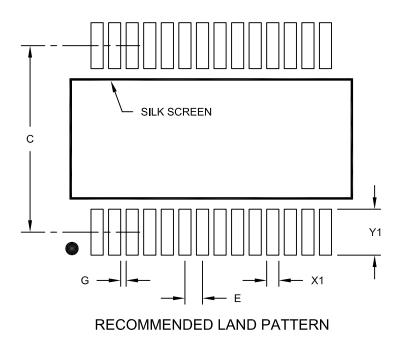

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Ν   |      | S        |      |

|--------------------------|-----|------|----------|------|

| Dimensior                | MIN | NOM  | MAX      |      |

| Contact Pitch            |     |      | 0.65 BSC |      |

| Contact Pad Spacing      | С   |      | 7.20     |      |

| Contact Pad Width (X28)  | X1  |      |          | 0.45 |

| Contact Pad Length (X28) | Y1  |      |          | 1.75 |

| Distance Between Pads    | G   | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

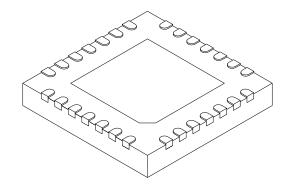

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units | MILLIMETERS |      |      |

|-------------------------|-------|-------------|------|------|

| Dimension Limits        |       | MIN         | NOM  | MAX  |

| Number of Pins          | Ν     | 28          |      |      |

| Pitch                   | е     | 0.65 BSC    |      |      |

| Overall Height          | А     | 0.80        | 0.90 | 1.00 |

| Standoff                | A1    | 0.00        | 0.02 | 0.05 |

| Terminal Thickness      | A3    | 0.20 REF    |      |      |

| Overall Width           | Е     | 6.00 BSC    |      |      |

| Exposed Pad Width       | E2    | 3.65        | 3.70 | 4.70 |

| Overall Length          | D     | 6.00 BSC    |      |      |

| Exposed Pad Length      | D2    | 3.65        | 3.70 | 4.70 |

| Terminal Width          | b     | 0.23        | 0.30 | 0.35 |

| Terminal Length         | L     | 0.30        | 0.40 | 0.50 |

| Terminal-to-Exposed Pad | К     | 0.20        | -    | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

$\label{eq:REF:Reference} \ensuremath{\mathsf{REF:}} \ensuremath{\mathsf{Reference}}\xspace \ensuremath{\mathsf{Dimension}}, \ensuremath{\mathsf{usually}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace, \ensuremath{\mathsf{for}}\xspace \ensuremath{\mathsf{oterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{rescale}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{$

Microchip Technology Drawing C04-124C Sheet 2 of 2

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |           | MILLIMETERS |      |  |

|--------------------------|-------|-----------|-------------|------|--|

| Dimension Limits         |       | MIN       | NOM         | MAX  |  |

| Number of Leads          | N     | 64        |             |      |  |

| Lead Pitch               | е     | 0.50 BSC  |             |      |  |

| Overall Height           | А     | -         | -           | 1.20 |  |

| Molded Package Thickness | A2    | 0.95      | 1.00        | 1.05 |  |

| Standoff                 | A1    | 0.05      | -           | 0.15 |  |

| Foot Length              | L     | 0.45      | 0.60        | 0.75 |  |

| Footprint                | L1    | 1.00 REF  |             |      |  |

| Foot Angle               | φ     | 0°        | 3.5°        | 7°   |  |

| Overall Width            | E     | 12.00 BSC |             |      |  |

| Overall Length           | D     | 12.00 BSC |             |      |  |

| Molded Package Width     | E1    | 10.00 BSC |             |      |  |

| Molded Package Length    | D1    | 10.00 BSC |             |      |  |

| Lead Thickness           | С     | 0.09      | -           | 0.20 |  |

| Lead Width               | b     | 0.17      | 0.22        | 0.27 |  |

| Mold Draft Angle Top     | α     | 11°       | 12°         | 13°  |  |

| Mold Draft Angle Bottom  | β     | 11°       | 12°         | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

NOTES: