Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

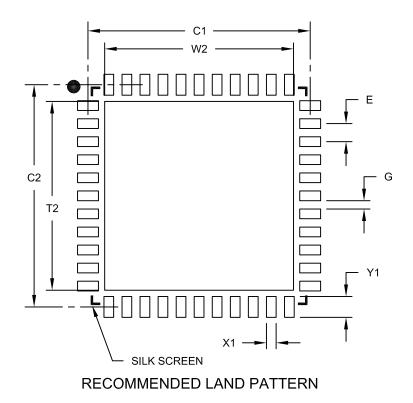

| Package / Case             | 48-UFQFN Exposed Pad                                                              |

| Supplier Device Package    | 48-UQFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc204t-i-mv |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

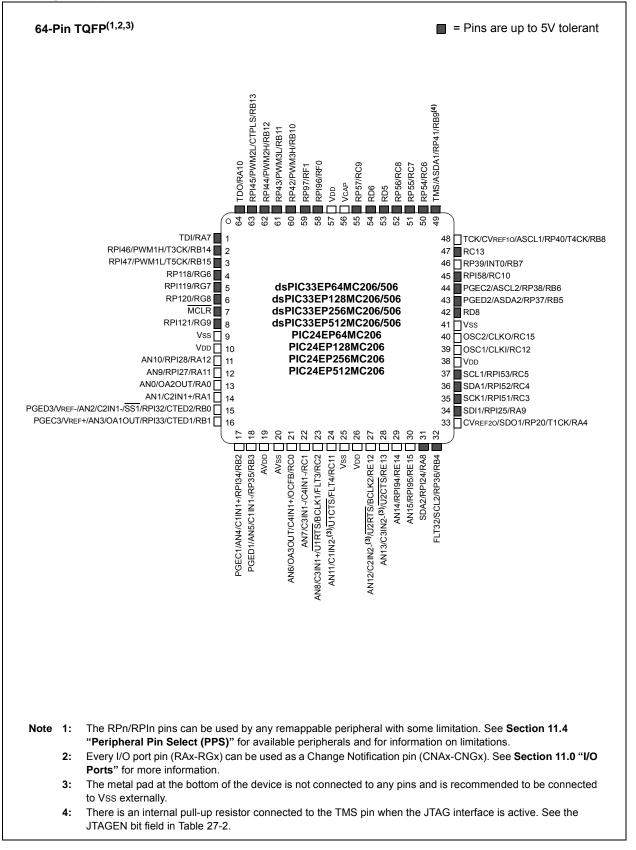

# Pin Diagrams (Continued)

# 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

# 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

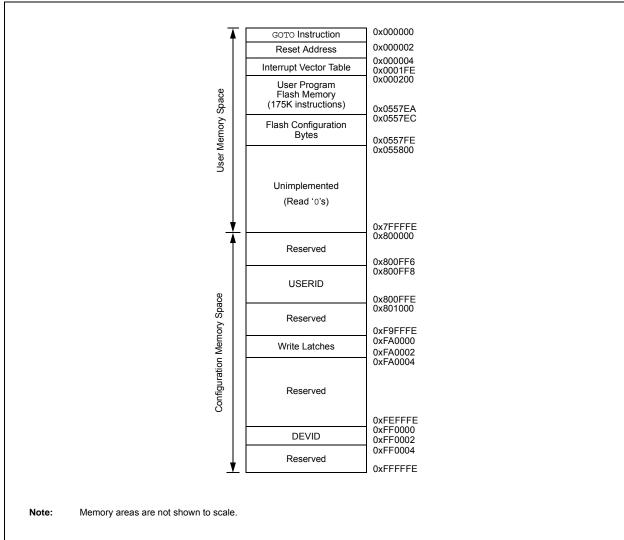

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            | VELEN  |        |        |            |        |       |         | DEVICE      |         |         |          |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|---------|-------------|---------|---------|----------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF   | IC2IF       | DMA0IF  | T1IF    | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _       | —           | INT1IF  | CNIF    | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —          | _      | _     | IC4IF   | IC3IF       | DMA3IF  | _       | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIF   | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  |            | _      | _      | _      | _          | —      | _     | _       | _           | _       | _       | —        | —            | —       | 0000          |

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | _          | —      | _     | PTG3IF  | PTG2IF      | PTG1IF  | PTG0IF  | PTGWDTIF | PTGSTEPIF    | —       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE   | IC2IE       | DMA0IE  | T1IE    | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _       | _           | INT1IE  | CNIE    | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _          | _      | _     | IC4IE   | IC3IE       | DMA3IE  | _       | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | _          | —      | _     | _       | _           | _       | _       | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIE   | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | _        | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | _          | —      | _     | PTG3IE  | PTG2IE      | PTG1IE  | PTG0IE  | PTGWDTIE | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     |         | IC1IP<2:0>  |         | —       |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |         | IC2IP<2:0>  |         | _       | C        | 0MA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |         | SPI1EIP<2:0 | >       | _       |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _     |         | AD1IP<2:0>  |         | _       | ι        | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _     |         | MI2C1IP<2:0 | >       | _       | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | —           | _       | _       | I        | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |         | OC3IP<2:0>  |         | _       | C        | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |        | 1      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _     |         | INT2IP<2:0> |         | _       |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —          | —      | _     |         | SPI2IP<2:0> |         | _       | S        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          |        |        |        | IC4IP<2:0  | >      | _     |         | IC3IP<2:0>  |         | _       | C        | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          |        |        | N      | 112C2IP<2: | 0>     | _     |         | SI2C2IP<2:0 | >       | _       | _        | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _     |         | U1EIP<2:0>  |         | _       | _        | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _          | _      | _     |         | CTMUIP<2:0  | >       | _       | _        | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _     | _       | _           | _       | _       | _        | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P       | TGSTEPIP<2  | :0>     | _       | _        | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _     |         | PTG2IP<2:0  | >       | _       | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            | —      | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR   | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |            | _      | _     |         | —           | —       | _       | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      |            | _      |        |        | _          | _      | _     | _       | DAE         | DOOVR   | _       | _        | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —          | _      | _     | _       | _           | _       | _       | _        |              | SGHT    | 0000          |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>       |        |       |         |             | VECN    | UM<7:0> |          |              |         | 0000          |

|              |       |        |        |            |        |        |        |            |        |       |         |             |         |         |          |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

## TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | _      | _      | _      | —      | —     | —      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | —      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | _      | _      | _      | —      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | —      | _      | _      |        | —      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _      | —      | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

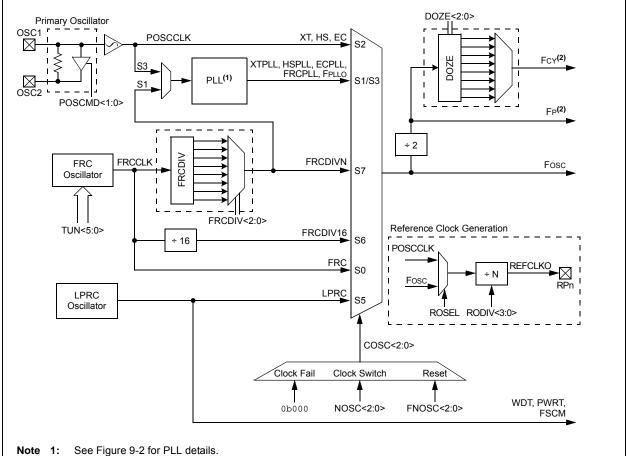

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

# FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nown                                                                                                                                                                                                                                                                                                                                                                                                |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Unimplemer                   | nted: Read as '0                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| (see Table 11<br>1111001 = I | I-2 for input pin's nput tied to RPI1                                                                                                                                  | election num<br>21                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          | onding RPn Pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | e bit<br>POR<br>Unimplemen<br>IC2R<6:0>: /<br>(see Table 11<br>1111001 = I<br>0000001 = I<br>0000000 = I<br>Unimplemen<br>IC1R<6:0>: /<br>(see Table 11<br>1111001 = I | e bit W = Writable b<br>POR '1' = Bit is set<br>Unimplemented: Read as '0<br>IC2R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s<br>1111001 = Input tied to RPI1<br>0000001 = Input tied to CMP<br>0000000 = Input tied to Vss<br>Unimplemented: Read as '0<br>IC1R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s | e bit W = Writable bit<br>POR '1' = Bit is set<br>Unimplemented: Read as '0'<br>IC2R<6:0>: Assign Input Capture 2 (IC2)<br>(see Table 11-2 for input pin selection num<br>1111001 = Input tied to RPI121 | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>       IC1R<6:0>         e bit       W = Writable bit       U = Unimplem         POR       '1' = Bit is set       '0' = Bit is clear         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>         e bit       W = Writable bit       U = Unimplemented bit, real         POR       '1' = Bit is set       '0' = Bit is cleared         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>    e bit W = Writable bit U = Unimplemented bit, read as '0' POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkr Unimplemented: Read as '0' IC2R<6:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 <p< td=""></p<> |

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

# 15.2 Output Compare Control Registers

# REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                                                                                                                                   | R/W-0                                         | R/W-0             | R/W-0             | R/W-0                  | U-0              | R/W-0         |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------|-------------------|------------------------|------------------|---------------|--|--|--|--|

|               | 0-0                                                                                                                                   | OCSIDL                                        | OCTSEL2           | OCTSEL1           | OCTSEL0                |                  | ENFLTB        |  |  |  |  |

| <br>bit 15    |                                                                                                                                       | COOIDE                                        |                   | OUTOLLI           | OUTOLLU                |                  | bit 8         |  |  |  |  |

| Sit 10        |                                                                                                                                       |                                               |                   |                   |                        |                  | bit 0         |  |  |  |  |

| R/W-0         | U-0                                                                                                                                   | R/W-0, HSC                                    | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0            | R/W-0         |  |  |  |  |

| ENFLT         |                                                                                                                                       | OCFLTB                                        | OCFLTA            | TRIGMODE          | OCM2                   | OCM1             | OCM0          |  |  |  |  |

| bit 7         |                                                                                                                                       |                                               |                   |                   |                        |                  | bit 0         |  |  |  |  |

|               |                                                                                                                                       |                                               |                   |                   |                        |                  |               |  |  |  |  |

| Legend:       |                                                                                                                                       | HSC = Hardw                                   | are Settable/Cl   | earable bit       |                        |                  |               |  |  |  |  |

| R = Read      | able bit                                                                                                                              | W = Writable I                                | oit               | U = Unimplem      | nented bit, read       | as '0'           |               |  |  |  |  |

| -n = Value    | e at POR                                                                                                                              | '1' = Bit is set                              |                   | '0' = Bit is clea | ared                   | x = Bit is unkn  | own           |  |  |  |  |

|               |                                                                                                                                       |                                               |                   |                   |                        |                  |               |  |  |  |  |

| bit 15-14     | Unimplemen                                                                                                                            | ted: Read as '0                               | )'                |                   |                        |                  |               |  |  |  |  |

| bit 13        | OCSIDL: Out                                                                                                                           | tput Compare x                                | Stop in Idle Mo   | de Control bit    |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | ompare x Halts                                |                   |                   |                        |                  |               |  |  |  |  |

|               | •                                                                                                                                     | compare x conti                               | •                 |                   | ode                    |                  |               |  |  |  |  |

| bit 12-10     |                                                                                                                                       | )>: Output Com                                | pare x Clock S    | elect bits        |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | 111 = Peripheral clock (FP)<br>110 = Reserved |                   |                   |                        |                  |               |  |  |  |  |

|               | 101 = PTGOx clock(2)                                                                                                                  |                                               |                   |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | is the clock so                               |                   |                   | hronous clock          | is supported)    |               |  |  |  |  |

|               |                                                                                                                                       | is the clock so                               |                   |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | ( is the clock so<br>( is the clock so        |                   |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | is the clock so                               |                   |                   |                        |                  |               |  |  |  |  |

| bit 9         | Unimplemen                                                                                                                            | ted: Read as '0                               | )'                |                   |                        |                  |               |  |  |  |  |

| bit 8         | ENFLTB: Fau                                                                                                                           | ult B Input Enab                              | le bit            |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | compare Fault B<br>compare Fault B            |                   |                   |                        |                  |               |  |  |  |  |

| bit 7         | -                                                                                                                                     | ult A Input Enab                              |                   |                   |                        |                  |               |  |  |  |  |

|               | 1 = Output C                                                                                                                          | ompare Fault A<br>compare Fault A             | input (OCFA)      |                   |                        |                  |               |  |  |  |  |

| bit 6         | •                                                                                                                                     | ted: Read as '0                               | • • •             |                   |                        |                  |               |  |  |  |  |

| bit 5         | OCFLTB: PW                                                                                                                            | M Fault B Con                                 | dition Status bit |                   |                        |                  |               |  |  |  |  |

|               |                                                                                                                                       | ult B condition of Fault B condition          |                   |                   |                        |                  |               |  |  |  |  |

| bit 4         |                                                                                                                                       | /M Fault A Cond                               | •                 |                   |                        |                  |               |  |  |  |  |

|               | <ul> <li>1 = PWM Fault A condition on OCFA pin has occurred</li> <li>0 = No PWM Fault A condition on OCFA pin has occurred</li> </ul> |                                               |                   |                   |                        |                  |               |  |  |  |  |

| Note 1:       | OCxR and OCxF                                                                                                                         | 29 are double h                               | uffered in D\\//  | / mode only       |                        |                  |               |  |  |  |  |

| Note 1.<br>2: | Each Output Cor                                                                                                                       |                                               |                   | -                 | irce. See <b>Secti</b> | on 24.0 "Perin   | heral Trigger |  |  |  |  |

| 2.            | Generator (PTG                                                                                                                        |                                               |                   |                   |                        | 5.1 2 7.0 1 611p |               |  |  |  |  |

|               | PTGO4 = OC1                                                                                                                           | -                                             |                   |                   |                        |                  |               |  |  |  |  |