Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Dectano                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc204t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

#### TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

### TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |       | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |       | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |       |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |       | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |       | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _     | _       | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | —                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | —                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         |     | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         |     | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

- g) The TRISx registers control only the digital I/O output buffer. Any other dedicated or remappable active "output" will automatically override the TRIS setting. The TRISx register does not control the digital logic "input" buffer. Remappable digital "inputs" do not automatically override TRIS settings, which means that the TRISx bit must be set to input for pins with only remappable input function(s) assigned

- h) All analog pins are enabled by default after any Reset and the corresponding digital input buffer on the pin has been disabled. Only the Analog Pin Select registers control the digital input buffer, *not* the TRISx register. The user must disable the analog function on a pin using the Analog Pin Select registers in order to use any "digital input(s)" on a corresponding pin, no exceptions.

#### 11.6 I/O Ports Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 11.6.1 KEY RESOURCES

- "I/O Ports" (DS70598) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 12.2 Timer1 Control Register

| R/W-0              | U-0                                                            | R/W-0                                 | U-0                       | U-0              | U-0                      | U-0                | U-0                |  |  |  |  |

|--------------------|----------------------------------------------------------------|---------------------------------------|---------------------------|------------------|--------------------------|--------------------|--------------------|--|--|--|--|

| TON <sup>(1)</sup> | —                                                              | TSIDL                                 | —                         | _                | —                        | _                  | _                  |  |  |  |  |

| bit 15             |                                                                |                                       |                           |                  |                          |                    | bit 8              |  |  |  |  |

|                    |                                                                |                                       |                           |                  |                          |                    |                    |  |  |  |  |

| U-0                | R/W-0                                                          | R/W-0                                 | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0                |  |  |  |  |

|                    | TGATE                                                          | TCKPS1                                | TCKPS0                    | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> |                    |  |  |  |  |

| bit 7              |                                                                |                                       |                           |                  |                          |                    | bit (              |  |  |  |  |

| Legend:            |                                                                |                                       |                           |                  |                          |                    |                    |  |  |  |  |

| R = Readable       | e bit                                                          | W = Writable                          | bit                       | U = Unimplei     | mented bit, read         | l as '0'           |                    |  |  |  |  |

| -n = Value at      | POR                                                            | '1' = Bit is set                      |                           | '0' = Bit is cle | ared                     | x = Bit is unkno   | own                |  |  |  |  |

|                    |                                                                | o                                     |                           |                  |                          |                    |                    |  |  |  |  |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16-                           |                                       |                           |                  |                          |                    |                    |  |  |  |  |

|                    | 0 = Stops 16-                                                  |                                       |                           |                  |                          |                    |                    |  |  |  |  |

| bit 14             | Unimplemen                                                     | ted: Read as '                        | 0'                        |                  |                          |                    |                    |  |  |  |  |

| bit 13             | TSIDL: Timer                                                   | 1 Stop in Idle N                      | /lode bit                 |                  |                          |                    |                    |  |  |  |  |

|                    |                                                                | ues module op                         |                           |                  | ldle mode                |                    |                    |  |  |  |  |

|                    |                                                                | s module opera                        |                           | ode              |                          |                    |                    |  |  |  |  |

| bit 12-7           | Unimplemented: Read as '0'                                     |                                       |                           |                  |                          |                    |                    |  |  |  |  |

| bit 6              | TGATE: Timer1 Gated Time Accumulation Enable bit               |                                       |                           |                  |                          |                    |                    |  |  |  |  |

|                    | When TCS =<br>This bit is igno                                 |                                       |                           |                  |                          |                    |                    |  |  |  |  |

|                    | When TCS =                                                     |                                       |                           |                  |                          |                    |                    |  |  |  |  |

|                    |                                                                | e accumulatio                         |                           |                  |                          |                    |                    |  |  |  |  |

|                    |                                                                | e accumulatio                         |                           | 0.1.1.1.1.1      |                          |                    |                    |  |  |  |  |

| bit 5-4            |                                                                | : Timer1 Input                        | Clock Prescal             | e Select bits    |                          |                    |                    |  |  |  |  |

|                    | 11 = 1:256<br>10 = 1:64                                        |                                       |                           |                  |                          |                    |                    |  |  |  |  |

|                    | 01 = 1:8                                                       |                                       |                           |                  |                          |                    |                    |  |  |  |  |

|                    | 00 = 1:1                                                       |                                       |                           |                  |                          |                    |                    |  |  |  |  |

| bit 3              | -                                                              | ted: Read as '                        |                           |                  |                          |                    |                    |  |  |  |  |

| bit 2              |                                                                | er1 External Clo                      | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                    |                    |  |  |  |  |

|                    | When TCS = 1:                                                  |                                       |                           |                  |                          |                    |                    |  |  |  |  |

|                    |                                                                | 1 = Synchronizes external clock input |                           |                  |                          |                    |                    |  |  |  |  |

|                    | 0 = Does not synchronize external clock input<br>When TCS = 0: |                                       |                           |                  |                          |                    |                    |  |  |  |  |

|                    | This bit is igno                                               |                                       |                           |                  |                          |                    |                    |  |  |  |  |

| bit 1              | TCS: Timer1                                                    | Clock Source S                        | Select bit <sup>(1)</sup> |                  |                          |                    |                    |  |  |  |  |

|                    | 1 = External c<br>0 = Internal cl                              | clock is from pi<br>ock (FP)          | n, T1CK (on th            | ne rising edge)  | •                        |                    |                    |  |  |  |  |

| bit 0              | Unimplemen                                                     | ted: Read as '                        | 0'                        |                  |                          |                    |                    |  |  |  |  |

|                    | nen Timer1 is er<br>empts by user s                            |                                       |                           |                  |                          | SYNC = 1, TON      | <b>\ =</b> 1), any |  |  |  |  |

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

#### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7- | 6  | DTC<1:0>: Dead-Time Control bits                                                                                                    |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------|

|        |    | 11 = Dead-Time Compensation mode                                                                                                    |

|        |    | 10 = Dead-time function is disabled                                                                                                 |

|        |    | 01 = Negative dead time is actively applied for Complementary Output mode                                                           |

|        |    | 00 = Positive dead time is actively applied for all output modes                                                                    |

| bit 5  |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                     |

|        |    | When Set to '1':                                                                                                                    |

|        |    | If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.                                                                          |

|        |    | If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                          |

|        |    | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.                                               |

|        |    | If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                          |

| bit 4  |    | Unimplemented: Read as '0'                                                                                                          |

| bit 3  |    | MTBS: Master Time Base Select bit                                                                                                   |

|        |    | 1 = PWM generator uses the secondary master time base for synchronization and as the clock source                                   |

|        |    | for the PWM generation logic (if secondary time base is available)                                                                  |

|        |    | 0 = PWM generator uses the primary master time base for synchronization and as the clock source                                     |

|        |    | for the PWM generation logic                                                                                                        |

| bit 2  |    | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                |

|        |    | 1 = Center-Aligned mode is enabled                                                                                                  |

|        |    | 0 = Edge-Aligned mode is enabled                                                                                                    |

| bit 1  |    | <b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                        |

|        |    | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base<br/>mode</li> </ul> |

|        |    | 0 = External pins do not affect PWMx time base                                                                                      |

| bit 0  |    | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                     |

|        |    | 1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate                                                      |

|        |    | <ul> <li>Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the<br/>PWMx period boundary</li> </ul>   |

| Note   | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                        |

|        | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                              |

|        | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                 |

|        | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.            |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

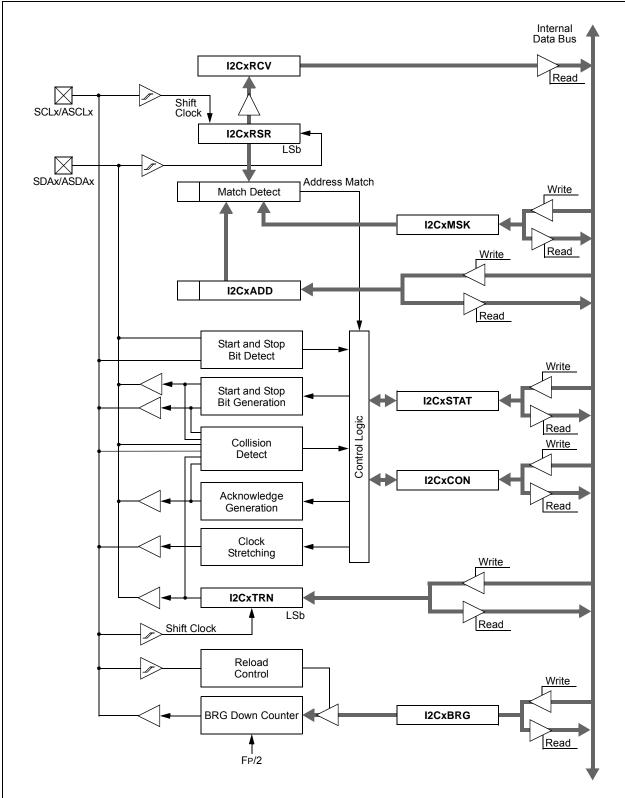

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

| U-0                     | U-0                        | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

|-------------------------|----------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|

| _                       | _                          |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |

| bit 15                  | <b>I</b>                   | •                                  |         |                  |                 |                 | bit 8   |  |  |  |

|                         |                            |                                    |         |                  |                 |                 |         |  |  |  |

| U-0                     | R-1                        | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |

| _                       | ICODE6                     | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |

| bit 7                   |                            |                                    |         |                  |                 |                 | bit     |  |  |  |

| Logondi                 |                            |                                    |         |                  |                 |                 |         |  |  |  |

| Legend:<br>R = Readable | - hit                      |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |

| -n = Value at           |                            | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |

| -n = value at           | POR                        | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |

| bit 15-13               | Unimplemen                 | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 12-8                | =                          | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |

|                         |                            | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |

|                         | 01111 <b>= Filte</b>       | r 15                               |         |                  |                 |                 |         |  |  |  |

|                         | •                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                            | •<br>00001 = Filter 1              |         |                  |                 |                 |         |  |  |  |

|                         | 00001 = Filte              |                                    |         |                  |                 |                 |         |  |  |  |

| bit 7                   |                            | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |

| bit 6-0                 | -                          | Interrupt Flag                     |         |                  |                 |                 |         |  |  |  |

|                         | 1000101-1111111 = Reserved |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                            | IFO almost full                    |         |                  |                 |                 |         |  |  |  |

|                         |                            | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |

|                         | 1000010 = K<br>1000001 = E | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |

|                         | 1000000 = N                |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                            | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |

|                         | • • •                      |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | •                          |                                    |         |                  |                 |                 |         |  |  |  |

|                         | 0001001 <b>= R</b>         | B9 buffer inter                    | rupt    |                  |                 |                 |         |  |  |  |

|                         |                            | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |

|                         |                            | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |

|                         |                            | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         |                            | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |

|                         | 0000011 <b>= T</b>         | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |

|                         |                            |                                    |         |                  |                 |                 |         |  |  |  |

|                         |                            | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |

#### REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0          | R/W-x                                                                    | U-0                           | U-0              | U-0              | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

|--------------|--------------------------------------------------------------------------|-------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| —            | WAKFIL                                                                   |                               | —                |                  | SEG2PH2          | SEG2PH1         | SEG2PH0 |  |  |  |  |

| bit 15       |                                                                          |                               |                  |                  |                  |                 | bit     |  |  |  |  |

|              |                                                                          |                               |                  |                  |                  |                 |         |  |  |  |  |

| R/W-x        | R/W-x                                                                    | R/W-x                         | R/W-x            | R/W-x            | R/W-x            | R/W-x           | R/W-x   |  |  |  |  |

| SEG2PHTS     | S SAM                                                                    | SEG1PH2                       | SEG1PH1          | SEG1PH0          | PRSEG2           | PRSEG1          | PRSEG0  |  |  |  |  |

| bit 7        |                                                                          |                               |                  |                  |                  |                 | bit     |  |  |  |  |

| Legend:      |                                                                          |                               |                  |                  |                  |                 |         |  |  |  |  |

| R = Readab   | le bit                                                                   | W = Writable                  | bit              | U = Unimpler     | nented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value a |                                                                          | '1' = Bit is set              |                  | '0' = Bit is cle |                  | x = Bit is unkr | nown    |  |  |  |  |

|              |                                                                          |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 15       | Unimplemen                                                               | nted: Read as '               | 0'               |                  |                  |                 |         |  |  |  |  |

| bit 14       | WAKFIL: Sel                                                              | lect CAN Bus L                | ine Filter for V | Vake-up bit      |                  |                 |         |  |  |  |  |

|              |                                                                          | N bus line filter             |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                          | line filter is not            |                  | e-up             |                  |                 |         |  |  |  |  |

| bit 13-11    | -                                                                        | Unimplemented: Read as '0'    |                  |                  |                  |                 |         |  |  |  |  |

| bit 10-8     | <b>SEG2PH&lt;2:0&gt;:</b> Phase Segment 2 bits<br>111 = Length is 8 x TQ |                               |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                          |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                          |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 000 = Length                                                             | n is 1 x To                   |                  |                  |                  |                 |         |  |  |  |  |

| bit 7        | SEG2PHTS: Phase Segment 2 Time Select bit                                |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | 1 = Freely programmable                                                  |                               |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                          | n of SEG1PHx I                | bits or Informa  | tion Processin   | g Time (IPT), w  | hichever is gre | ater    |  |  |  |  |

| bit 6        | SAM: Sample                                                              | e of the CAN B                | us Line bit      |                  |                  |                 |         |  |  |  |  |

|              |                                                                          | s sampled threes sampled once |                  |                  |                  |                 |         |  |  |  |  |

| bit 5-3      | SEG1PH<2:0                                                               | <b>0&gt;:</b> Phase Segr      | nent 1 bits      |                  |                  |                 |         |  |  |  |  |

|              | 111 = Length is 8 x TQ                                                   |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                        | •                             |                  |                  |                  |                 |         |  |  |  |  |

|              | 000 = Length                                                             |                               |                  |                  |                  |                 |         |  |  |  |  |

| bit 2-0      |                                                                          | >: Propagation                | Time Segmen      | t bits           |                  |                 |         |  |  |  |  |

|              | 111 = Length                                                             | IIS8XIQ                       |                  |                  |                  |                 |         |  |  |  |  |

|              |                                                                          |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

|              | •                                                                        |                               |                  |                  |                  |                 |         |  |  |  |  |

#### REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x                                                                               | R/W-x                                        | R/W-x                                    | R/W-x            | R/W-x                              | R/W-x           | R/W-x  | R/W-x |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------|------------------|------------------------------------|-----------------|--------|-------|--|--|--|

| EID5                                                                                | EID4                                         | EID3                                     | EID2             | EID1                               | EID0            | RTR    | RB1   |  |  |  |

| bit 15                                                                              |                                              |                                          |                  |                                    |                 |        | bit 8 |  |  |  |

|                                                                                     |                                              |                                          |                  |                                    |                 |        |       |  |  |  |

| U-x                                                                                 | U-x                                          | U-x                                      | R/W-x            | R/W-x                              | R/W-x           | R/W-x  | R/W-x |  |  |  |

| —                                                                                   | —                                            | —                                        | RB0              | DLC3                               | DLC2            | DLC1   | DLC0  |  |  |  |

| bit 7                                                                               |                                              |                                          |                  |                                    |                 |        | bit 0 |  |  |  |

| Lonondi                                                                             |                                              |                                          |                  |                                    |                 |        |       |  |  |  |

| Legend:                                                                             |                                              |                                          |                  |                                    |                 | -l (O) |       |  |  |  |

| R = Readable bit W = Writable bit                                                   |                                              |                                          |                  | U = Unimplemented bit, read as '0' |                 |        |       |  |  |  |

| -n = Value at POR '1' = Bit is set                                                  |                                              |                                          | '0' = Bit is cle | ared                               | x = Bit is unkr | iown   |       |  |  |  |

|                                                                                     |                                              |                                          |                  |                                    |                 |        |       |  |  |  |

| bit 15-10                                                                           | EID<5:0>: E                                  | xtended Identifi                         | er bits          |                                    |                 |        |       |  |  |  |

| bit 9                                                                               | RTR: Remot                                   | R: Remote Transmission Request bit       |                  |                                    |                 |        |       |  |  |  |

|                                                                                     | When IDE = 1:                                |                                          |                  |                                    |                 |        |       |  |  |  |

|                                                                                     | 1 = Message will request remote transmission |                                          |                  |                                    |                 |        |       |  |  |  |

|                                                                                     |                                              | 0 = Normal message                       |                  |                                    |                 |        |       |  |  |  |

|                                                                                     |                                              | When IDE = 0:<br>The RTR bit is ignored. |                  |                                    |                 |        |       |  |  |  |

| <b>h</b> :+ 0                                                                       |                                              |                                          |                  |                                    |                 |        |       |  |  |  |

| bit 8 <b>RB1:</b> Reserved Bit 1<br>User must set this bit to '0' per CAN protocol. |                                              |                                          |                  |                                    |                 |        |       |  |  |  |

|                                                                                     |                                              |                                          | •                | 0001.                              |                 |        |       |  |  |  |

| bit 7-5                                                                             | •                                            | nted: Read as '                          | 0                |                                    |                 |        |       |  |  |  |

| bit 4                                                                               | RB0: Reserv                                  |                                          | <b></b>          |                                    |                 |        |       |  |  |  |

|                                                                                     | User must se                                 | et this bit to '0' p                     | per CAN proto    | ocol.                              |                 |        |       |  |  |  |

| hit 2 0                                                                             |                                              | Jota Longth Co.                          | da hita          |                                    |                 |        |       |  |  |  |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

#### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x                     | R/W-x | R/W-x            | R/W-x            | R/W-x | R/W-x                              | R/W-x              | R/W-x |  |

|---------------------------|-------|------------------|------------------|-------|------------------------------------|--------------------|-------|--|

|                           |       |                  | Ву               | /te 1 |                                    |                    |       |  |

| bit 15                    |       |                  |                  |       |                                    |                    | bit 8 |  |

| R/W-x                     | R/W-x | R/W-x            | R/W-x            | R/W-x | R/W-x                              | R/W-x              | R/W-x |  |

|                           |       |                  | Ву               | rte 0 |                                    |                    |       |  |

| bit 7                     |       |                  |                  |       |                                    |                    | bit 0 |  |

| Legend:                   |       |                  |                  |       |                                    |                    |       |  |

| R = Readable              | bit   | W = Writable     | W = Writable bit |       | U = Unimplemented bit, read as '0' |                    |       |  |

| -n = Value at POR '1' = B |       | '1' = Bit is set | 1' = Bit is set  |       | ared                               | x = Bit is unknown |       |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

#### REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt</li> <li>0 = Always starts filling the buffer from the start address.</li> </ul> |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                                                                    |

1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample 0 = Always uses channel input selects for Sample MUXA

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

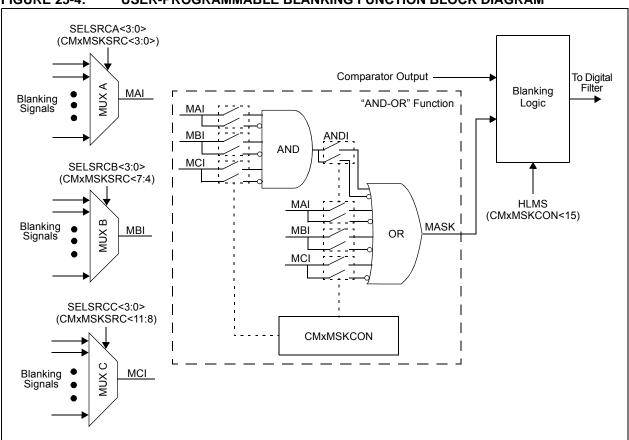

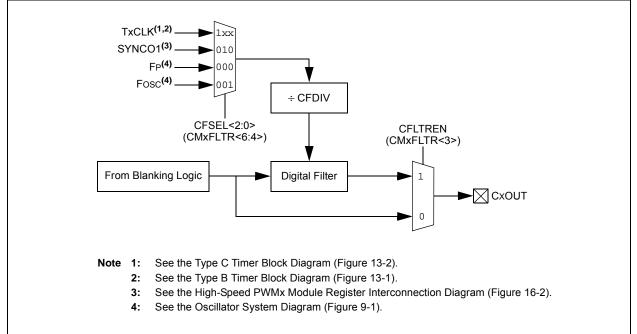

#### DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |  |  |  |  |  |  |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |  |  |  |  |  |  |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |  |  |  |  |  |  |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |  |  |  |  |  |  |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

#### TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

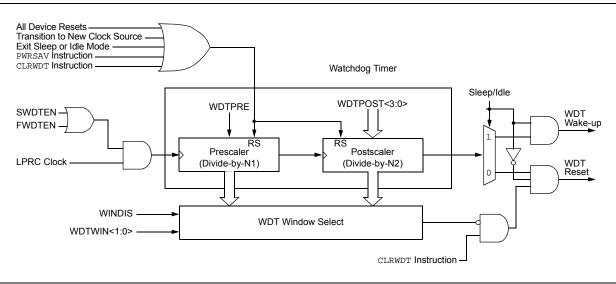

#### 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### FIGURE 27-2: WDT BLOCK DIAGRAM

## 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

### 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 27.5.4 WDT WINDOW