Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

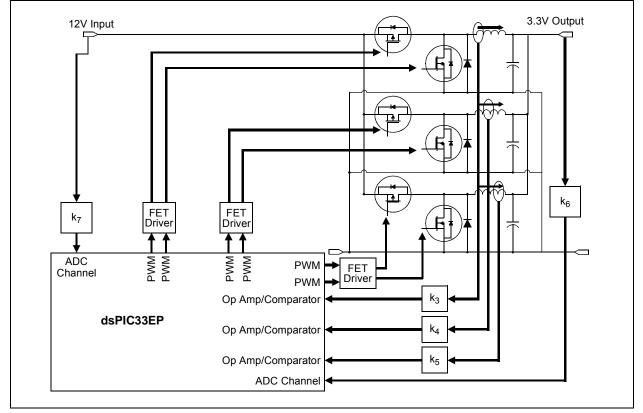

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-VFTLA Exposed Pad                                                              |

| Supplier Device Package    | 44-VTLA (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc204t-i-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

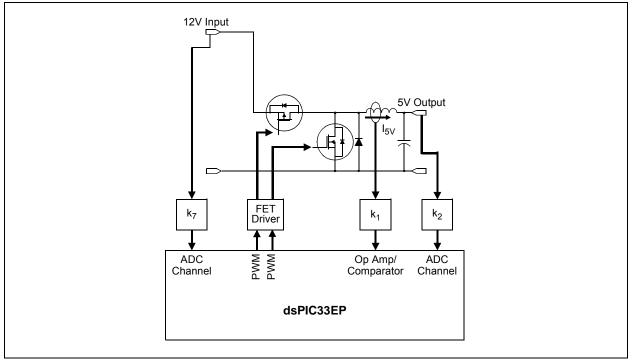

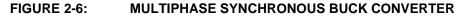

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

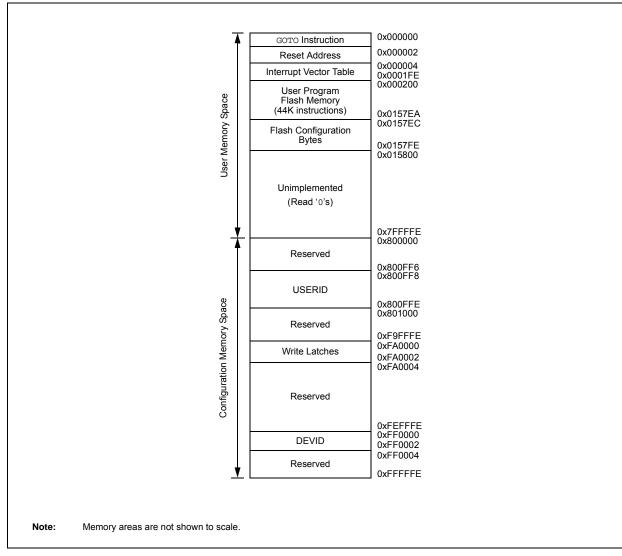

#### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP128GP50X, dsPIC33EP128MC20X/50X AND PIC24EP128GP/MC20X DEVICES

# TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

# REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                 |       |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                 | bit 8 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                 |       |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                 | bit 0 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                 |       |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                 |       |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                 |       |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                 |       |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

# REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

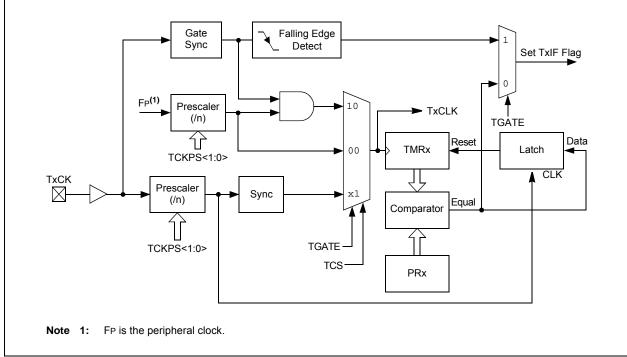

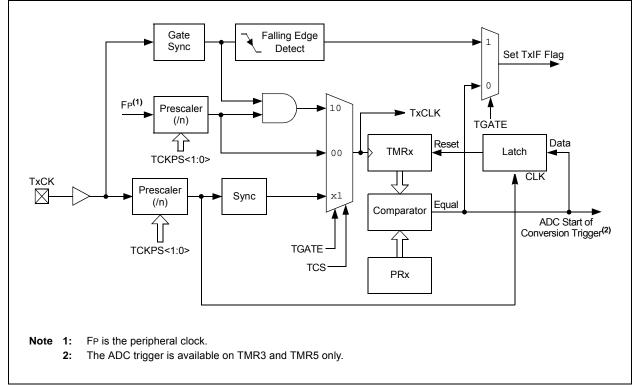

## FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

# FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

# 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

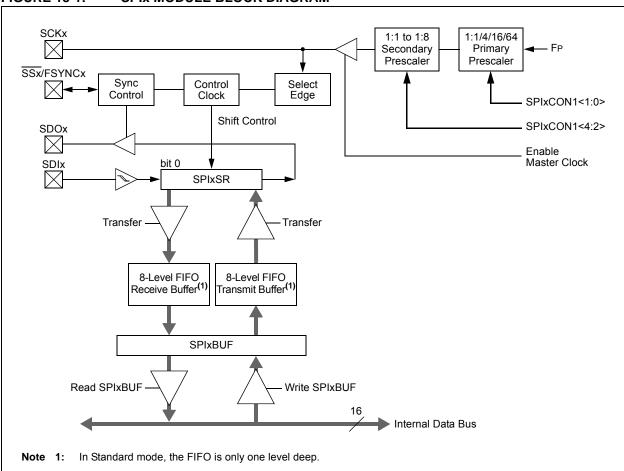

#### FIGURE 18-1: SPIX MODULE BLOCK DIAGRAM

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

# REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

RXOVF4

| bit 7            |                          |                                         | bit 0 |

|------------------|--------------------------|-----------------------------------------|-------|

|                  |                          |                                         |       |

| Legend:          | C = Writable bit, but or | nly '0' can be written to clear the bit |       |

| R = Readable bit | W = Writable bit         | U = Unimplemented bit, read as '0'      |       |

RXOVF3

RXOVF2

| R = Readable bit  | vv = vvritable bit | U = Unimplemented bit, read | d as 0             |

|-------------------|--------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

RXOVF6

RXOVF7

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

RXOVF5

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but or | nly '0' can be written to clear t | the bit            |

|-------------------|--------------------------|-----------------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit             | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared              | x = Bit is unknown |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

RXOVF0

RXOVF1

# BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

|                                   |       |                  | Ву    | /te 3                              |       |                 |       |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |

|                                   |       |                  |       |                                    |       |                 |       |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x           | R/W-x |

|                                   |       |                  | Ву    | /te 2                              |       |                 |       |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |

| Legend:                           |       |                  |       |                                    |       |                 |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0' |       |                 |       |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|-----------------------------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|

|                                   |       |                  | B     | yte 5                                   |       |       |       |  |

| bit 15                            |       |                  |       |                                         |       |       | bit 8 |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|                                   |       |                  |       | yte 4                                   |       |       |       |  |

| bit 7                             |       |                  |       |                                         |       |       | bit 0 |  |

|                                   |       |                  |       |                                         |       |       |       |  |

| Legend:                           |       |                  |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

# FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

# 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# 22.2 CTMU Control Registers

| REGISTER                                                                                                                                                            | 22-1: CTM                         | UCON1: CTMU      | J CONTROL | . REGISTER        | 1                |                        |        |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|-----------|-------------------|------------------|------------------------|--------|--|

| R/W-0                                                                                                                                                               | U-0                               | R/W-0            | R/W-0     | R/W-0             | R/W-0            | R/W-0                  | R/W-0  |  |

| CTMUEN                                                                                                                                                              | _                                 | CTMUSIDL         | TGEN      | EDGEN             | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |  |

| bit 15                                                                                                                                                              |                                   |                  |           |                   |                  |                        | bit 8  |  |

|                                                                                                                                                                     |                                   |                  |           |                   |                  |                        |        |  |

| U-0                                                                                                                                                                 | U-0                               | U-0              | U-0       | U-0               | U-0              | U-0                    | U-0    |  |

| _                                                                                                                                                                   |                                   | —                | _         |                   | <u> </u>         |                        | _      |  |

| bit 7                                                                                                                                                               |                                   |                  |           |                   |                  |                        | bit 0  |  |

|                                                                                                                                                                     |                                   |                  |           |                   |                  |                        |        |  |

| Legend:                                                                                                                                                             |                                   |                  |           |                   |                  |                        |        |  |

| R = Readable                                                                                                                                                        | e bit                             | W = Writable b   | oit       | U = Unimplen      | nented bit, read | l as '0'               |        |  |

| -n = Value at                                                                                                                                                       | POR                               | '1' = Bit is set |           | '0' = Bit is clea | ared             | x = Bit is unkn        | own    |  |

| bit 15 <b>CTMUEN:</b> CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled                                                                            |                                   |                  |           |                   |                  |                        |        |  |

| bit 14                                                                                                                                                              | bit 14 Unimplemented: Read as '0' |                  |           |                   |                  |                        |        |  |

| bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                                   |                  |           |                   |                  |                        |        |  |

| bit 12                                                                                                                                                              | TGEN: Time                        | Generation Ena   | ble bit   |                   |                  |                        |        |  |

#### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

| R/W-0         | R/W-0                                                                                       | R/W-0                                                                                                                                                                                  | R/W-0                                                                                                                                    | R/W-0                                                                                    | R/W-0                                 | R/W-0           | R/W-0 |

|---------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------|

| ITRIM5        | ITRIM4                                                                                      | ITRIM3                                                                                                                                                                                 | ITRIM2                                                                                                                                   | ITRIM1                                                                                   | ITRIM0                                | IRNG1           | IRNG0 |

| bit 15        |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 | bit   |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

| U-0           | U-0                                                                                         | U-0                                                                                                                                                                                    | U-0                                                                                                                                      | U-0                                                                                      | U-0                                   | U-0             | U-0   |

|               |                                                                                             | _                                                                                                                                                                                      | _                                                                                                                                        |                                                                                          | _                                     | _               | _     |

| bit 7         |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 | bit   |

| Legend:       |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

| R = Readabl   | e bit                                                                                       | W = Writable                                                                                                                                                                           | bit                                                                                                                                      | U = Unimplem                                                                             | nented bit, read                      | 1 as '0'        |       |

| -n = Value at | POR                                                                                         | '1' = Bit is set                                                                                                                                                                       |                                                                                                                                          | '0' = Bit is clea                                                                        |                                       | x = Bit is unkr | nown  |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

|               | 011110 = Ma<br>•                                                                            |                                                                                                                                                                                        | e change nom                                                                                                                             |                                                                                          | 1 00 /0                               |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nimum positive<br>nimum positive<br>minal current c<br>nimum negative                                                                                                                  | change from r<br>change from r<br>output specified<br>e change from                                                                      | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>t – 2%                |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative                                                                              | change from r<br>change from r<br>output specified<br>e change from<br>e change from<br>re change from                                   | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren                   | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

| bit 9-8       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative<br>current Source<br>ase Current <sup>(2)</sup><br>se Current <sup>(2)</sup> | change from r<br>change from r<br>output specified<br>e change from<br>e change from<br>re change from<br>re change from<br>Range Select | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

## REGISTER 22-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

2: Refer to the CTMU Current Source Specifications (Table 30-56) in Section 30.0 "Electrical Characteristics" for the current range selection values.

# REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

| bit 1 | BUFM: Buffer Fill Mode Select bit                                                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt</li> <li>0 = Always starts filling the buffer from the start address.</li> </ul> |

| bit 0 | ALTS: Alternate Input Sample Mode Select bit                                                                                                                                                                                    |

1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample 0 = Always uses channel input selects for Sample MUXA

# REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

| bit 4-0 | CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits <sup>(1)</sup>                     |

|---------|-----------------------------------------------------------------------------------------------------|

|         | 11111 = Open; use this selection with CTMU capacitive and time measurement                          |

|         | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP) |

|         | 11101 = Reserved                                                                                    |

|         | 11100 = Reserved                                                                                    |

|         | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>      |

|         | 11010 =  Channel 0 positive input is the output of OA3/AN0 <sup>(2)</sup>                           |

|         | 11000 = Channel 0 positive input is the output of OA1/AN3 <sup>(2)</sup>                            |

|         | 10110 = Reserved                                                                                    |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 10000 = Reserved                                                                                    |

|         | 01111 = Channel 0 positive input is AN15 <sup>(1,3)</sup>                                           |

|         | 01110 = Channel 0 positive input is AN14 <sup>(1,3)</sup>                                           |

|         | 01101 = Channel 0 positive input is AN13 <sup>(1,3)</sup>                                           |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         | 00010 = Channel 0 positive input is $AN2^{(1,3)}$                                                   |

|         | 00001 = Channel 0 positive input is $AN1^{(1,3)}$                                                   |

|         | 00000 = Channel 0 positive input is AN0 <sup>(1,3)</sup>                                            |

|         |                                                                                                     |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | R/W-0                        | U-0              | U-0                                    | U-0              | R/W-0                        | U-0              | U-0            |

|-----------------|------------------------------|------------------|----------------------------------------|------------------|------------------------------|------------------|----------------|

|                 | CVR2OE <sup>(1)</sup>        | _                |                                        | _                | VREFSEL                      |                  | _              |

| bit 15          |                              |                  |                                        |                  |                              |                  | bit            |

| <b>D</b> 444 0  | DANIO                        |                  | <b>D</b> 444.0                         | <b>D</b> 444 0   | DAALO                        | DAMA             | <b>D</b> 444 0 |

| R/W-0           | R/W-0                        | R/W-0            | R/W-0                                  | R/W-0            | R/W-0                        | R/W-0            | R/W-0          |

| CVREN           | CVR10E <sup>(1)</sup>        | CVRR             | CVRSS <sup>(2)</sup>                   | CVR3             | CVR2                         | CVR1             | CVR0           |

| bit 7           |                              |                  |                                        |                  |                              |                  | bit            |

| Legend:         |                              |                  |                                        |                  |                              |                  |                |

| R = Readable    | bit                          | W = Writable     | bit                                    | U = Unimple      | mented bit, read             | as '0'           |                |

| -n = Value at F | POR                          | '1' = Bit is set | t                                      | '0' = Bit is cle | eared                        | x = Bit is unkn  | iown           |

|                 |                              |                  |                                        |                  |                              |                  |                |

| bit 15          | Unimplement                  |                  |                                        |                  |                              |                  |                |

| bit 14          |                              | •                | ige Reference                          | •                | ble bit <sup>(1)</sup>       |                  |                |

|                 |                              |                  | nected to the C<br>onnected from       |                  | nin                          |                  |                |

| bit 13-11       | Unimplement                  |                  |                                        |                  | <b>F</b>                     |                  |                |

| bit 10          | -                            |                  | age Reference                          | e Select bit     |                              |                  |                |

|                 | 1 = CVREFIN =                | -                | U                                      |                  |                              |                  |                |

|                 | 0 = CVREFIN is               | s generated by   | y the resistor ne                      | etwork           |                              |                  |                |

| bit 9-8         | Unimplement                  | ed: Read as '    | 0'                                     |                  |                              |                  |                |

| bit 7           |                              |                  | e Reference E                          |                  |                              |                  |                |

|                 |                              |                  | erence circuit is<br>erence circuit is |                  | wn                           |                  |                |

| bit 6           | CVR1OE: Co                   | mparator Volta   | ige Reference                          | 1 Output Ena     | ble bit <sup>(1)</sup>       |                  |                |

|                 |                              |                  | n the CVREF1C                          |                  | n                            |                  |                |

| bit 5           | CVRR: Comp                   | arator Voltage   | Reference Ra                           | nge Selection    | n bit                        |                  |                |

|                 | 1 = CVRSRC/2<br>0 = CVRSRC/3 | •                |                                        |                  |                              |                  |                |

| bit 4           | CVRSS: Com                   | parator Voltag   | e Reference S                          | ource Selecti    | on bit <sup>(2)</sup>        |                  |                |

|                 |                              | 0                | erence source,<br>erence source,       | · ·              | ref+) – (AVss)<br>/dd – AVss |                  |                |

| bit 3-0         | CVR<3:0> Co                  | mparator Volt    | age Reference                          | Value Select     | ion $0 \leq CVR < 3$ :       | $0> \le 15$ bits |                |

|                 | When CVRR =                  |                  | (CVRSRC)                               |                  |                              |                  |                |

|                 | When CVRR = CVREFIN = (CV    | = 0:             |                                        | $(\mathbf{C})$   |                              |                  |                |

### REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

- 2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

| DC CH        | ARACTE | RISTICS                                 | (unless | d Operating<br>otherwise<br>g temperat | <b>stated)</b><br>ure -40° | C ≤ TA ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended                                                                               |

|--------------|--------|-----------------------------------------|---------|----------------------------------------|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                          | Min.    | Тур.                                   | Max.                       | Units    | Conditions                                                                                                                                    |

|              | liL    | Input Leakage Current <sup>(1,2)</sup>  |         |                                        |                            |          |                                                                                                                                               |

| DI50         |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1      | —                                      | +1                         | μA       | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in at high-impedance} \end{split}$                         |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1      | _                                      | +1                         | μA       | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1      | _                                      | +1                         | μA       | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1      | _                                      | +1                         | μA       | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                      |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1      | _                                      | +1                         | μA       | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |

| DI55         |        | MCLR                                    | -5      | —                                      | +5                         | μA       | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |

| DI56         |        | OSC1                                    | -5      | —                                      | +5                         | μΑ       | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                     |

# TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.