Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

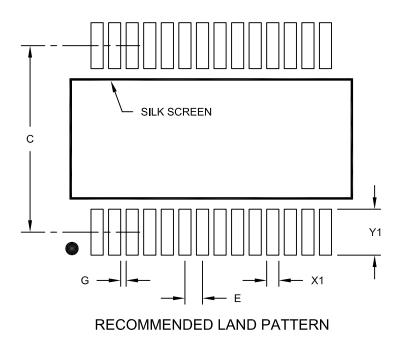

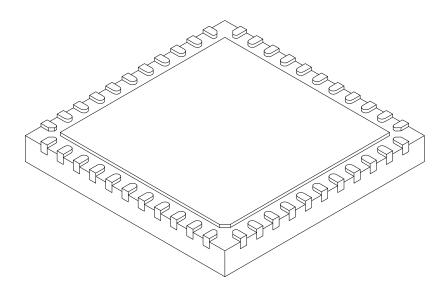

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc206-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

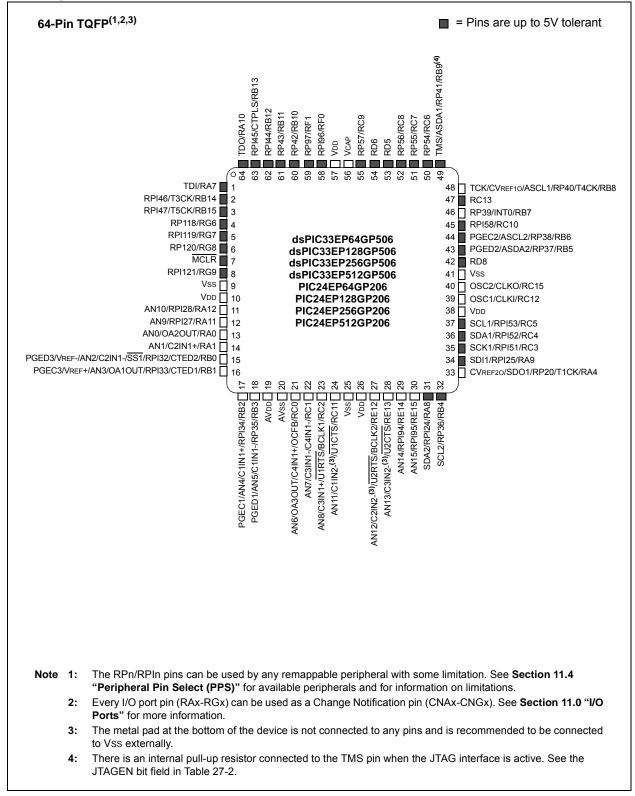

# **Pin Diagrams (Continued)**

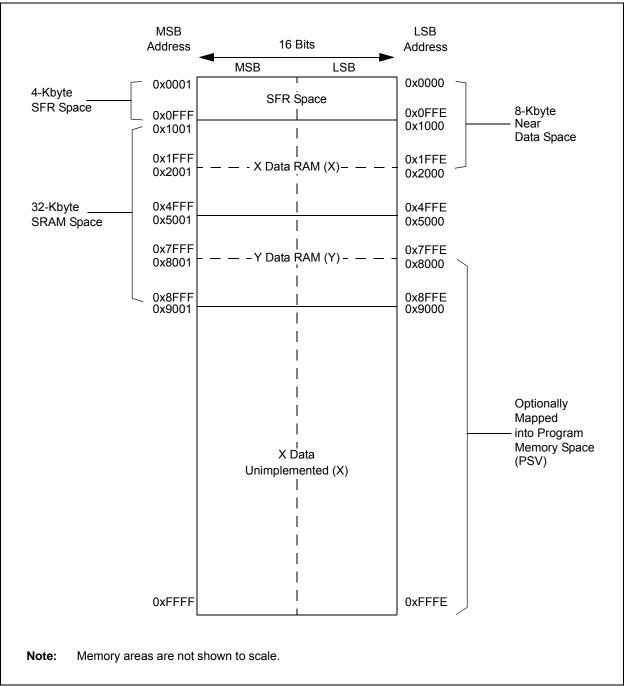

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

# TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8                 | Bit 7 | Bit 6 | Bit 5    | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|-----------------------|-----------------------|-------|-------|----------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —                     | _                     |       |       |          | I2C1 Recei  | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —                     | _                     |       |       |          | I2C1 Transi | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _                     |                       |       |       | Bau      | d Rate Gene | erator       |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN                  | GCEN  | STREN | ACKDT    | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                | ADD10                 | IWCOL | I2COV | D_A      | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |                       | I2C1 Address Register |       |       |          |             | 0000         |       |       |       |               |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |                       |                       |       |       | I2C1 Add | dress Mask  |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _                     | _                     |       |       |          | I2C2 Recei  | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _                     | _                     |       |       |          | I2C2 Transi | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _                     |                       |       |       | Bau      | d Rate Gene | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN                  | GCEN  | STREN | ACKDT    | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT                | ADD10                 | IWCOL | I2COV | D_A      | Р           | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      | I2C2 Address Register |                       |       |       |          | 0000        |              |       |       |       |               |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | -      |                       |                       |       |       |          |             | 0000         |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                           | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                      | Bit 7      | Bit 6    | Bit 5 | Bit 4      | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------------------------------|--------|----------|--------|--------|--------|-------|----------------------------|------------|----------|-------|------------|----------|-------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN                           | —      | USIDL    | IREN   | RTSMD  | _      | UEN<  | :1:0>                      | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1                         | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                       | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _                                | _      | _        | _      | _      | _      | _     | UART1 Transmit Register xx |            |          |       |            |          | xxxx  |        |       |               |

| U1RXREG     | 0226  | _                                | _      | _        | _      | _      | _      | _     | - UART1 Receive Register 0 |            |          |       |            | 0000     |       |        |       |               |

| U1BRG       | 0228  |                                  |        |          |        |        |        | Baud  | Rate Gen                   | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

| U2MODE      | 0230  | UARTEN                           | _      | USIDL    | IREN   | RTSMD  | _      | UEN<  | :1:0>                      | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1                         | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT                       | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _                                | _      | _        | _      | _      | _      | _     |                            |            |          | UART2 | Transmit F | Register |       |        |       | xxxx          |

| U2RXREG     | 0236  | _                                | _      | _        | _      | —      | _      | _     | UART2 Receive Register     |            |          |       |            | 0000     |       |        |       |               |

| U2BRG       | 0238  | Baud Rate Generator Prescaler 00 |        |          |        |        |        | 0000  |                            |            |          |       |            |          |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4-2  | 23: E | CAN1 I       | REGIST | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC                     | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|--------------|--------|--------|--------|--------|--------|---------------|-------------------------------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15       | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8                         | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  | 6E EID<15:8> |        |        |        |        |        |               | EID<7:0>                      |          |          |        |        |        | xxxx   |       |       |               |

| C1RXF12SID | 0470  | SID<10:3>    |        |        |        |        |        |               | SID<2:0> — EXIDE — EID<17:16> |          |          |        |        | 7:16>  | xxxx   |       |       |               |

| C1RXF12EID | 0472  | EID<15:8>    |        |        |        |        |        |               | EID<7:0>                      |          |          |        |        |        |        | xxxx  |       |               |

| C1RXF13SID | 0474  |              |        |        | SID<   | :10:3> |        |               |                               |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476  |              |        |        | EID<   | :15:8> |        |               |                               | EID<7:0> |          |        |        |        |        | xxxx  |       |               |

| C1RXF14SID | 0478  |              |        |        | SID<   | :10:3> |        |               |                               |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A  | EID<15:8>    |        |        |        |        |        | EID<7:0>      |                               |          |          |        |        | xxxx   |        |       |       |               |

| C1RXF15SID | 047C  | SID<10:3>    |        |        |        |        |        |               | SID<2:0>                      |          | _        | EXIDE  | _      | EID<1  | 7:16>  | xxxx  |       |               |

| C1RXF15EID | 047E  |              |        |        |        |        |        |               |                               |          |          | EID<   | 7:0>   |        |        |       | xxxx  |               |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

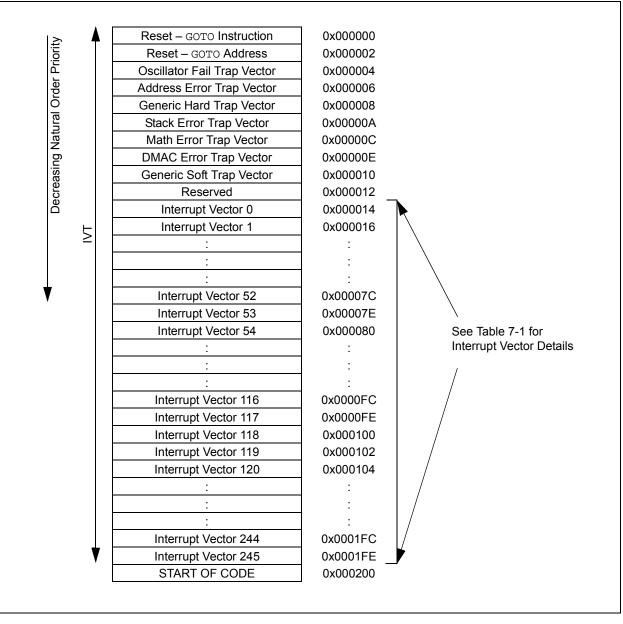

### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

# bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                 | R/W-0           | R/W-0     | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|---------------------------------------|-----------------|-----------|-------|-------|

|                                    |       |       | STA                                   | <15:8>          |           |       |       |

| bit 15                             |       |       |                                       |                 |           |       | bit 8 |

|                                    |       |       |                                       |                 |           |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                 | R/W-0           | R/W-0     | R/W-0 | R/W-0 |

|                                    |       |       | STA                                   | A<7:0>          |           |       |       |

| bit 7                              |       |       |                                       |                 |           |       | bit 0 |

|                                    |       |       |                                       |                 |           |       |       |

| Legend:                            |       |       |                                       |                 |           |       |       |

| R = Readable bit W = Writable bit  |       | oit   | U = Unimpler                          | mented bit, rea | ad as '0' |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unkno |                 |           |       |       |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                                                       | U-0                                   | U-0                                                                                          | U-0           | U-0                                     | U-0              | U-0    | U-0    |  |  |  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------|---------------|-----------------------------------------|------------------|--------|--------|--|--|--|

| —                                                                                                         | —                                     | —                                                                                            | —             | —                                       | —                | —      | —      |  |  |  |

| bit 15                                                                                                    |                                       |                                                                                              |               |                                         |                  |        | bit 8  |  |  |  |

|                                                                                                           |                                       |                                                                                              |               |                                         |                  |        |        |  |  |  |

| U-0                                                                                                       | U-0                                   | U-0                                                                                          | U-0           | R-0                                     | R-0              | R-0    | R-0    |  |  |  |

|                                                                                                           |                                       | <u> </u>                                                                                     | _             | PWCOL3                                  | PWCOL2           | PWCOL1 | PWCOL0 |  |  |  |

| bit 7                                                                                                     |                                       |                                                                                              |               |                                         |                  |        | bit 0  |  |  |  |

|                                                                                                           |                                       |                                                                                              |               |                                         |                  |        |        |  |  |  |

| Legend:                                                                                                   |                                       |                                                                                              |               |                                         |                  |        |        |  |  |  |

| R = Readab                                                                                                | R = Readable bit     W = Writable bit |                                                                                              |               |                                         | mented bit, read | as '0' |        |  |  |  |

| -n = Value a                                                                                              | n = Value at POR '1' = Bit is set     |                                                                                              |               | '0' = Bit is cleared x = Bit is unknown |                  |        |        |  |  |  |

|                                                                                                           |                                       |                                                                                              |               |                                         |                  |        |        |  |  |  |

| bit 15-4                                                                                                  | Unimplemen                            | ted: Read as '                                                                               | 0'            |                                         |                  |        |        |  |  |  |

| bit 3                                                                                                     | PWCOL3: DI                            | MA Channel 3 F                                                                               | Peripheral Wi | rite Collision Fla                      | ag bit           |        |        |  |  |  |

|                                                                                                           |                                       | lision is detecte                                                                            |               |                                         |                  |        |        |  |  |  |

|                                                                                                           |                                       | collision is dete                                                                            |               |                                         |                  |        |        |  |  |  |

| bit 2                                                                                                     |                                       |                                                                                              | •             | rite Collision Fla                      | ag bit           |        |        |  |  |  |

|                                                                                                           |                                       | lision is detecte<br>collision is dete                                                       |               |                                         |                  |        |        |  |  |  |

| bit 1                                                                                                     |                                       |                                                                                              |               | rito Collision Els                      | a hit            |        |        |  |  |  |

| bit 1 <b>PWCOL1:</b> DMA Channel 1 Peripheral Write Collision Flag bit<br>1 = Write collision is detected |                                       |                                                                                              |               |                                         |                  |        |        |  |  |  |

|                                                                                                           | 0 = No write collision is detected    |                                                                                              |               |                                         |                  |        |        |  |  |  |

| bit 0                                                                                                     | PWCOL0: DI                            | MA Channel 0 F                                                                               | Peripheral Wi | rite Collision Fla                      | ag bit           |        |        |  |  |  |

|                                                                                                           |                                       | PWCOL0: DMA Channel 0 Peripheral Write Collision Flag bit<br>1 = Write collision is detected |               |                                         |                  |        |        |  |  |  |

|                                                                                                           | 0 = No write                          | collision is dete                                                                            | ected         |                                         |                  |        |        |  |  |  |

|                                                                                                           |                                       |                                                                                              |               |                                         |                  |        |        |  |  |  |

# REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| R/W-0         | R/W-0                                                                                                   | R/W-0                                                                                                   | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |  |  |

|---------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|--|--|

| T5MD          | T4MD                                                                                                    | T3MD                                                                                                    | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |  |  |

| bit 15        |                                                                                                         |                                                                                                         |         |                   |                       |                      | bit   |  |  |

|               |                                                                                                         |                                                                                                         |         |                   |                       |                      |       |  |  |

| R/W-0         | R/W-0                                                                                                   | R/W-0                                                                                                   | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |  |  |

| I2C1MD        | U2MD                                                                                                    | U1MD                                                                                                    | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |  |  |

| bit 7         |                                                                                                         |                                                                                                         |         |                   |                       |                      | bit   |  |  |

| Legend:       |                                                                                                         |                                                                                                         |         |                   |                       |                      |       |  |  |

| R = Readabl   | e bit                                                                                                   | W = Writable                                                                                            | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |  |  |

| -n = Value at | POR                                                                                                     | '1' = Bit is set                                                                                        |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |  |  |

| bit 15        | 1 = Timer5 m                                                                                            | 5 Module Disal<br>odule is disable<br>odule is enable                                                   | ed      |                   |                       |                      |       |  |  |

| bit 14        | 1 = Timer4 m                                                                                            | <b>T4MD:</b> Timer4 Module Disable bit<br>1 = Timer4 module is disabled<br>0 = Timer4 module is enabled |         |                   |                       |                      |       |  |  |

| bit 13        | <b>T3MD:</b> Timer3 Module Disable bit<br>1 = Timer3 module is disabled<br>0 = Timer3 module is enabled |                                                                                                         |         |                   |                       |                      |       |  |  |

| bit 12        | 1 = Timer2 m                                                                                            | 2 Module Disal<br>odule is disable<br>odule is enable                                                   | ed      |                   |                       |                      |       |  |  |

| bit 11        | 1 = Timer1 m                                                                                            | 1 Module Disal<br>odule is disable<br>odule is enable                                                   | ed      |                   |                       |                      |       |  |  |

| bit 10        | 1 = QEI1 mod                                                                                            | 11 Module Disa<br>Iule is disablec<br>Iule is enabled                                                   |         |                   |                       |                      |       |  |  |

| bit 9         | 1 = PWM mod                                                                                             | /M Module Dis<br>dule is disabled<br>dule is enabled                                                    | 1       |                   |                       |                      |       |  |  |

| bit 8         | Unimplemen                                                                                              | ted: Read as '                                                                                          | כי      |                   |                       |                      |       |  |  |

| bit 7         | 1 = I2C1 mod                                                                                            | 1 Module Disal<br>ule is disabled<br>ule is enabled                                                     | ble bit |                   |                       |                      |       |  |  |

| bit 6         | <b>U2MD:</b> UART2 Module Disable bit<br>1 = UART2 module is disabled<br>0 = UART2 module is enabled    |                                                                                                         |         |                   |                       |                      |       |  |  |

| bit 5         | 1 = UART1 m                                                                                             | 1 Module Disa<br>odule is disabl<br>odule is enable                                                     | ed      |                   |                       |                      |       |  |  |

| bit 4         | 1 = SPI2 mod                                                                                            | 2 Module Disa<br>lule is disabled<br>lule is enabled                                                    | ole bit |                   |                       |                      |       |  |  |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

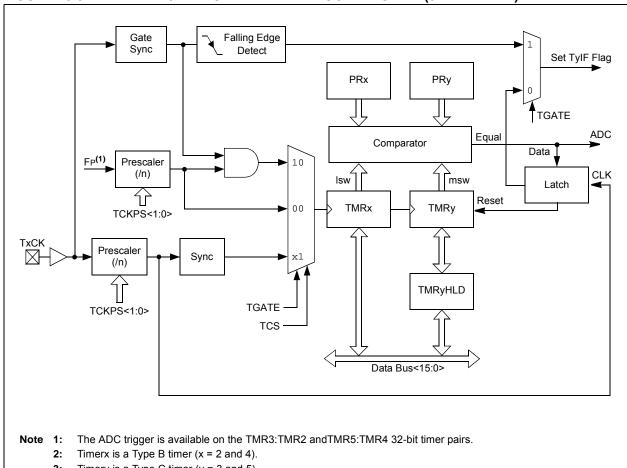

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0             | U-0          | U-0                                    | U-0                               | U-0      | R/W-0   |  |  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|----------------------------------------|-----------------------------------|----------|---------|--|--|--|

| —                                 | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —               |              | —                                      | _                                 | —        | ADDMAEN |  |  |  |

| bit 15                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |              |                                        |                                   |          | bit 8   |  |  |  |

| U-0                               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0             | U-0          | U-0                                    | R/W-0                             | R/W-0    | R/W-0   |  |  |  |

| 0-0                               | 0-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0-0             | 0-0          | 0-0                                    |                                   |          | -       |  |  |  |

|                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —               | —            | —                                      | DMABL2                            | DMABL1   | DMABL0  |  |  |  |

| bit 7                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |              |                                        |                                   |          | bit 0   |  |  |  |

| Legend:                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |              |                                        |                                   |          |         |  |  |  |

| R = Readab                        | le bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable b  | bit          | U = Unimpler                           | mented bit, read                  | 1 as '0' |         |  |  |  |

| n = Value at POR '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |              | 0' = Bit is cleared x = Bit is unknown |                                   |          |         |  |  |  |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |              |                                        |                                   |          |         |  |  |  |

| bit 15-9                          | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ted: Read as '0 | 3            |                                        |                                   |          |         |  |  |  |

| bit 8                             | ADDMAEN: A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ADC1 DMA Ena    | ıble bit     |                                        |                                   |          |         |  |  |  |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |              | 0                                      | ster for transfer<br>ADC1BUFF reg | 0        |         |  |  |  |

| bit 7-3                           | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ted: Read as '0 | ,            |                                        |                                   |          |         |  |  |  |

| bit 2-0                           | DMABL<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Selects Numb    | per of DMA B | uffer Locations                        | per Analog Inpu                   | ut bits  |         |  |  |  |

|                                   | <ul> <li>111 = Allocates 128 words of buffer to each analog input</li> <li>110 = Allocates 64 words of buffer to each analog input</li> <li>101 = Allocates 32 words of buffer to each analog input</li> <li>100 = Allocates 16 words of buffer to each analog input</li> <li>011 = Allocates 8 words of buffer to each analog input</li> <li>010 = Allocates 4 words of buffer to each analog input</li> <li>010 = Allocates 2 words of buffer to each analog input</li> <li>000 = Allocates 1 word of buffer to each analog input</li> </ul> |                 |              |                                        |                                   |          |         |  |  |  |

# REGISTER 23-4: AD1CON4: ADC1 CONTROL REGISTER 4

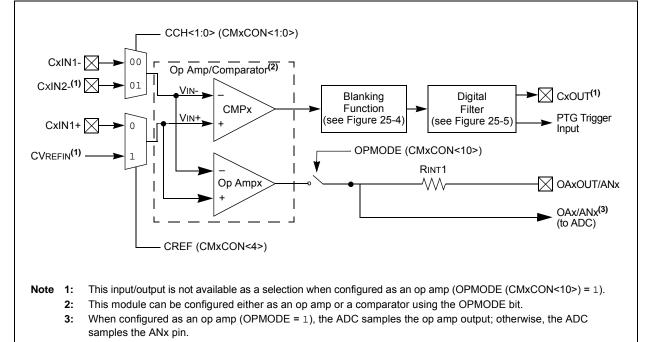

# 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

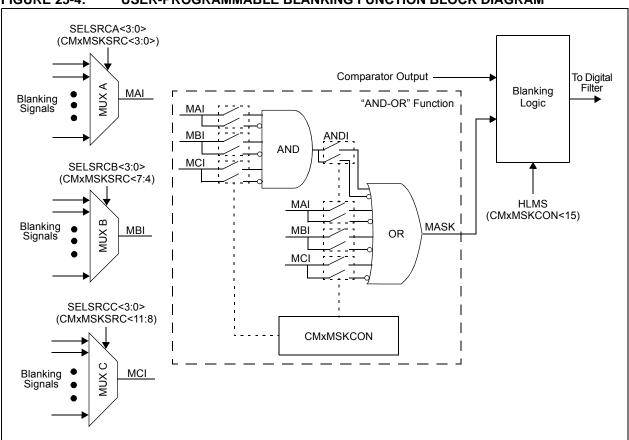

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

# FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

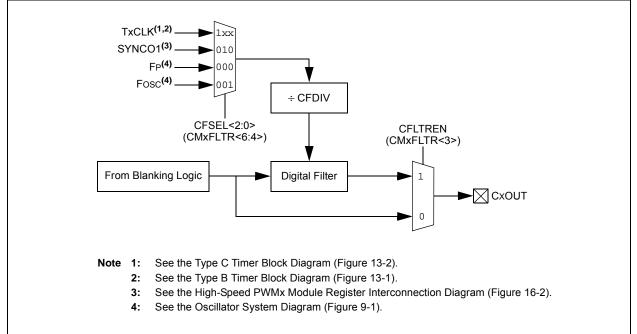

# DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

## REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)                                                                                                                             |

|         | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                          |

|         | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                       |

|         | 00 = Trigger/event/interrupt generation is disabled                                                                                                                                                                                                           |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 4   | <b>CREF:</b> Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                                      |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage<sup>(2)</sup></li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                          |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                                                |

|         | <ul> <li>11 = Unimplemented</li> <li>10 = Unimplemented</li> <li>01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup></li> <li>00 = Inverting input of the op amp/comparator connects to the CxIN1- pin</li> </ul>                 |

|         |                                                                                                                                                                                                                                                               |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER      | 25-3: CM40                                                                                                                                                                                                                                                    | CON: COMPA                                                                           | RATOR 4 CO          | ONTROL RE        | GISTER           |                     |                     |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------|------------------|------------------|---------------------|---------------------|--|--|--|--|

| R/W-0         | R/W-0                                                                                                                                                                                                                                                         | R/W-0                                                                                | U-0                 | U-0              | U-0              | R/W-0               | R/W-0               |  |  |  |  |

| CON           | COE                                                                                                                                                                                                                                                           | CPOL                                                                                 | —                   | —                | —                | CEVT                | COUT                |  |  |  |  |

| bit 15        |                                                                                                                                                                                                                                                               |                                                                                      |                     |                  |                  |                     | bit 8               |  |  |  |  |

| R/W-0         | DAM 0                                                                                                                                                                                                                                                         | U-0                                                                                  | DAM 0               | U-0              | U-0              |                     | R/W-0               |  |  |  |  |

|               | R/W-0                                                                                                                                                                                                                                                         | 0-0                                                                                  | R/W-0               | 0-0              | 0-0              | R/W-0               |                     |  |  |  |  |

| EVPOL1        | EVPOL0                                                                                                                                                                                                                                                        | —                                                                                    | CREF <sup>(1)</sup> | —                | _                | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |  |  |  |  |

| bit 7         |                                                                                                                                                                                                                                                               |                                                                                      |                     |                  |                  |                     | bit (               |  |  |  |  |

| Legend:       |                                                                                                                                                                                                                                                               |                                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                         | W = Writable                                                                         | bit                 | U = Unimple      | mented bit, rea  | d as '0'            |                     |  |  |  |  |

| -n = Value at |                                                                                                                                                                                                                                                               | '1' = Bit is se                                                                      |                     | '0' = Bit is cle |                  | x = Bit is unkr     | iown                |  |  |  |  |

|               |                                                                                                                                                                                                                                                               |                                                                                      |                     | 0 200000         |                  |                     |                     |  |  |  |  |

| bit 15        | CON: Comp                                                                                                                                                                                                                                                     | arator Enable b                                                                      | oit                 |                  |                  |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                                                                                               | ator is enabled                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                                                                                               | ator is disabled                                                                     |                     |                  |                  |                     |                     |  |  |  |  |

| bit 14        | COE: Comp                                                                                                                                                                                                                                                     | arator Output E                                                                      | nable bit           |                  |                  |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                                                                                               | ator output is pr<br>ator output is in                                               |                     | xOUT pin         |                  |                     |                     |  |  |  |  |

| bit 13        | CPOL: Com                                                                                                                                                                                                                                                     | parator Output                                                                       | Polarity Select     | bit              |                  |                     |                     |  |  |  |  |

|               | 1 = Compara                                                                                                                                                                                                                                                   | ator output is in                                                                    | verted              |                  |                  |                     |                     |  |  |  |  |

|               | 0 = Compara                                                                                                                                                                                                                                                   | ator output is no                                                                    | ot inverted         |                  |                  |                     |                     |  |  |  |  |

| bit 12-10     | Unimpleme                                                                                                                                                                                                                                                     | nted: Read as                                                                        | '0'                 |                  |                  |                     |                     |  |  |  |  |

| bit 9         | CEVT: Comparator Event bit                                                                                                                                                                                                                                    |                                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               | interrup                                                                                                                                                                                                                                                      | ts until the bit is                                                                  | cleared             | POL<1:0> set     | tings occurred;  | disables future     | e triggers and      |  |  |  |  |

|               | •                                                                                                                                                                                                                                                             | ator event did r                                                                     |                     |                  |                  |                     |                     |  |  |  |  |

| bit 8         | COUT: Comparator Output bit                                                                                                                                                                                                                                   |                                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               | When CPOL = 0 (non-inverted polarity):<br>1 = VIN+ > VIN-                                                                                                                                                                                                     |                                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               | 1 = VIN + > VIN - 0 = VIN + < VIN - 0                                                                                                                                                                                                                         |                                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                                                                                               | When CPOL = 1 (inverted polarity):                                                   |                     |                  |                  |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                                                                                               | 1 = VIN+ < VIN-                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               | 0 = VIN+ > V                                                                                                                                                                                                                                                  | 'IN-                                                                                 |                     |                  |                  |                     |                     |  |  |  |  |

| bit 7-6       | EVPOL<1:0                                                                                                                                                                                                                                                     | >: Trigger/Ever                                                                      | t/Interrupt Pola    | arity Select bit | S                |                     |                     |  |  |  |  |

|               | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |                                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               | If CPO                                                                                                                                                                                                                                                        | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output. |                     |                  |                  |                     |                     |  |  |  |  |

|               | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |                                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)                                                                                                                             |                                                                                      |                     |                  |                  |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                                                                                               | L = 1 (inverted                                                                      |                     | ator output.     |                  |                     |                     |  |  |  |  |

|               |                                                                                                                                                                                                                                                               | L = 0 (non-inve<br>-high transition                                                  |                     | ator output.     |                  |                     |                     |  |  |  |  |

|               | 00 = Trigger                                                                                                                                                                                                                                                  | /event/interrupt                                                                     | generation is       | disabled         |                  |                     |                     |  |  |  |  |

| Note 1: In    | puts that are se                                                                                                                                                                                                                                              | lected and not a                                                                     | available will be   | e tied to Vss. S | See the "Pin Dia | agrams" sectior     | n for available     |  |  |  |  |

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

# 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F. The PIC24EP instruction set is almost identical to that of the PIC24F and PIC24H.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

# TABLE 30-48:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                          |    |       |                             |  |

|--------------------|-----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----|-------|-----------------------------|--|