Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 16                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc206t-i-mr |

# **Table of Contents**

| 1.0   | Device Overview                                                                                    | 25  |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             | 123 |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           | 153 |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

| 16.0  | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     | 225 |

| 17.0  | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) | 249 |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

| 19.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      | 273 |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                                 | 281 |

| 21.0  | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    | 287 |

| 22.0  | Charge Time Measurement Unit (CTMU)                                                                | 315 |

| 23.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    | 321 |

| 24.0  | Peripheral Trigger Generator (PTG) Module                                                          | 337 |

|       | Op Amp/Comparator Module                                                                           |     |

| 26.0  | Programmable Cyclic Redundancy Check (CRC) Generator                                               | 373 |

| 27.0  | Special Features                                                                                   | 379 |

| 28.0  | Instruction Set Summary                                                                            | 387 |

| 29.0  | Development Support                                                                                | 397 |

| 30.0  | Electrical Characteristics                                                                         | 401 |

| 31.0  | High-Temperature Electrical Characteristics                                                        | 467 |

| 32.0  | DC and AC Device Characteristics Graphs                                                            | 475 |

| 33.0  | Packaging Information                                                                              | 479 |

|       | endix A: Revision History                                                                          |     |

| Index | X                                                                                                  | 517 |

| The I | Microchip Web Site                                                                                 | 525 |

| Cust  | omer Change Notification Service                                                                   | 525 |

| Cust  | omer Support                                                                                       | 525 |

| Prod  | uct Identification System                                                                          | 527 |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS | Description                                                    |

|-------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------|

| U2CTS                                     | - 1         | ST             | No  | UART2 Clear-To-Send.                                           |

| U2RTS                                     | 0           | _              | No  | UART2 Ready-To-Send.                                           |

| U2RX                                      | - 1         | ST             | Yes | UART2 receive.                                                 |

| U2TX                                      | 0           | _              | Yes | UART2 transmit.                                                |

| BCLK2                                     | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                     |

| SCK1                                      | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                |

| SDI1                                      | I           | ST             | No  | SPI1 data in.                                                  |

| SDO1                                      | 0           | _              | No  | SPI1 data out.                                                 |

| SS1                                       | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                 |

| SCK2                                      | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                |

| SDI2                                      | I           | ST             | Yes | SPI2 data in.                                                  |

| SDO2                                      | 0           | _              | Yes | SPI2 data out.                                                 |

| SS2                                       | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                 |

| SCL1                                      | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                |

| SDA1                                      | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                 |

| ASCL1                                     | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.      |

| ASDA1                                     | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.       |

| SCL2                                      | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                |

| SDA2                                      | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                 |

| ASCL2                                     | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.      |

| ASDA2                                     | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.       |

| TMS <sup>(5)</sup>                        | - 1         | ST             | No  | JTAG Test mode select pin.                                     |

| TCK                                       | I           | ST             | No  | JTAG test clock input pin.                                     |

| TDI                                       | I           | ST             | No  | JTAG test data input pin.                                      |

| TDO                                       | 0           | _              | No  | JTAG test data output pin.                                     |

| C1RX <sup>(2)</sup>                       | - 1         | ST             | Yes | ECAN1 bus receive pin.                                         |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes | ECAN1 bus transmit pin.                                        |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | - 1         | ST             | Yes | PWM Fault Inputs 1 and 2.                                      |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | - 1         | ST             | No  | PWM Fault Inputs 3 and 4.                                      |

| FLT32 <sup>(1,3)</sup>                    | - 1         | ST             | No  | PWM Fault Input 32 (Class B Fault).                            |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | - 1         | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                 |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | _              | No  | PWM Low Outputs 1 through 3.                                   |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | _              | No  | PWM High Outputs 1 through 3.                                  |

| SYNCI1 <sup>(1)</sup>                     | - 1         | ST             | Yes | PWM Synchronization Input 1.                                   |

| SYNCO1 <sup>(1)</sup>                     | 0           | _              | Yes | PWM Synchronization Output 1.                                  |

| INDX1 <sup>(1)</sup>                      | I           | ST             | Yes | Quadrature Encoder Index1 pulse input.                         |

| HOME1 <sup>(1)</sup>                      | - 1         | ST             | Yes | Quadrature Encoder Home1 pulse input.                          |

| QEA1 <sup>(1)</sup>                       | - 1         | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |

| (4)                                       |             |                |     | external clock/gate input in Timer mode.                       |

| QEB1 <sup>(1)</sup>                       | I           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer |

| ONTO 45 (1)                               |             |                | .,  | external clock/gate input in Timer mode.                       |

| CNTCMP1 <sup>(1)</sup>                    | 0           | _              | Yes | Quadrature Encoder Compare Output 1.                           |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levels<br/>PPS = Peripheral Pin SelectAnalog = Analog input<br/>O = Output<br/>TTL = TTL input bufferP = Power<br/>I = Input

- Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

- 3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

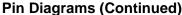

- 4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

- 5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB® PICkit™ 3, MPLAB ICD 3, or MPLAB RFALICE™.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB® ICD 3" (poster) DS51765

- "MPLAB® ICD 3 Design Advisory" DS51764

- "MPLAB® REAL ICE™ In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

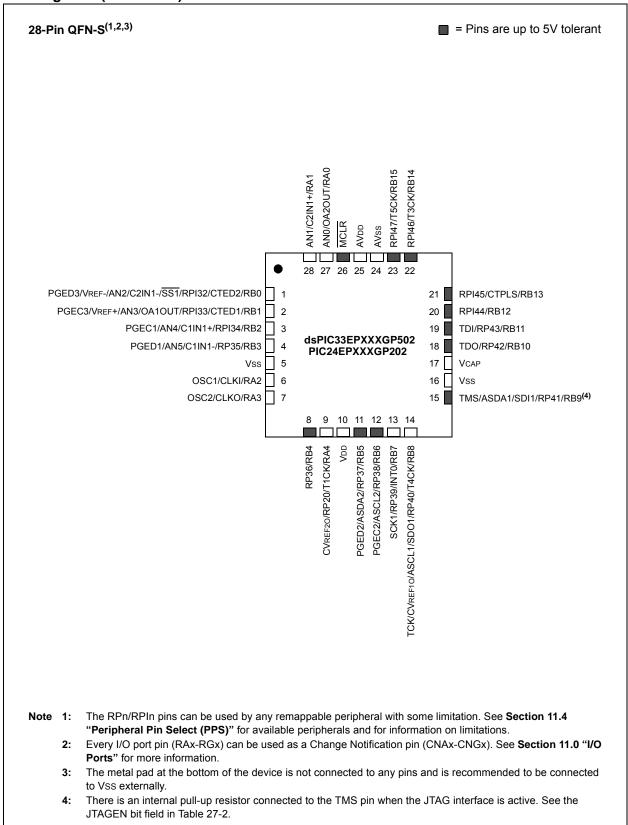

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0** "Oscillator Configuration" for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

FIGURE 2-3: SUGGESTED PLACEMENT

OF THE OSCILLATOR

CIRCUIT

TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      | ,      | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     | _     | _       | -           | 1       | _       | _      | _           | -      | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | -      | PT     | GWDTIP<    | 2:0>  | -     | PT      | GSTEPIP<2   | :0>     | _       | -      | _           | ı      | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | -      | F      | PTG3IP<2:0 | 0>    | -     | l       | PTG2IP<2:0> | >       | _       | ı      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | -      | -      | 1      | -          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | 1      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | -      | -      | 1      | -          | _     | _     | _       | _           | ı       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | _          | -      | -      | 1      | -          | _     | _     | _       | DAE         | DOOVR   | _       | _      | _           | 1      | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | 1      | _          | _     | _     | _       | _           | ı       | _       | _      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _          | -      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|------------|------------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        | RP35R<5:0> |        |        |       |       |       | _     | RP20R<5:0> |            |       |        |       |       |               |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       |       | _     |            |            | RP36F | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        | RP39R<5:0> |        |        |       |       | _     | _     |            | RP38R<5:0> |       |        |       |       |               |

| RPOR3        | 0686  | ı      | _      |        | RP41R<5:0> |        |        |       |       | _     | _     |            |            | RP40F | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | -      | _      |        | RP43R<5:0> |        |        |       |       | _     | _     | RP42R<5:0> |            |       |        |       | 0000  |               |

| RPOR5        | 068A  | -      | _      |        | RP55R<5:0> |        |        |       |       | _     | _     | RP54R<5:0> |            |       |        |       | 0000  |               |

| RPOR6        | 068C  | _      | _      |        | RP57R<5:0> |        |        |       |       |       | _     | •          | •          | RP56F | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5       | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|-------------|--------|--------|-------|-------|-------|-------|-------------|------------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        | RP35R<5:0>  |        |        |       |       |       | _     | RP20R<5:0>  |            |       |        |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |             | RP37F  | R<5:0> |       |       | _     | _     |             |            | RP36F | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |             | RP39F  | R<5:0> |       |       | _     | _     |             |            | RP38F | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0>  |        |        |       |       | _     | _     |             |            | RP40F | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |             | RP43F  | R<5:0> |       |       | _     | _     |             |            | RP42F | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        |             | RP55F  | R<5:0> |       |       | _     | _     |             | RP54R<5:0> |       |        |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |        | RP57R<5:0>  |        |        |       |       |       | _     |             |            | RP56F | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        | RP97R<5:0>  |        |        |       |       | _     | _     | _           | _          | _     | _      | _     | _     | 0000          |

| RPOR8        | 0690  | ı      | _      |        | RP118R<5:0> |        |        |       |       | _     | _     | 1           | _          | _     | _      | _     | _     | 0000          |

| RPOR9        | 0692  | _      | _      | _      |             |        |        |       |       |       |       | RP120R<5:0> |            |       |        |       | 0000  |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

# 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2 where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- · Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

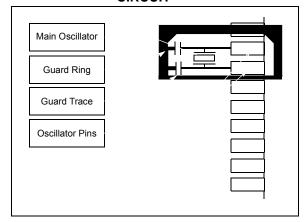

FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- · A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- · The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- · Any device Reset

- A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

# 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

# REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 |  |  |

|--------|-------|-------|-------|-------|-------|-------|-------|--|--|

| _      |       |       | )>    |       |       |       |       |  |  |

| bit 15 | bit 8 |       |       |       |       |       |       |  |  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 SYNCI1R<6:0>: Assign PWM Synchronization Input 1 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7-0 **Unimplemented:** Read as '0'

# REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|

| _      | DTCMP3R<6:0> |       |       |       |       |       |       |  |  |

| bit 15 | bit 8        |       |       |       |       |       |       |  |  |

| U-0   | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|

| _     | DTCMP2R<6:0> |       |       |       |       |       |       |  |  |

| bit 7 | bit 0        |       |       |       |       |       |       |  |  |

| Leg | end: |

|-----|------|

|-----|------|

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 **DTCMP3R<6:0>:** Assign PWM Dead-Time Compensation Input 3 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 DTCMP2R<6:0>: Assign PWM Dead-Time Compensation Input 2 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

# **REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8**

| U-0    | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-------|-------------|-------|-------|-------|-------|--|

| _      | _   |       | RP118R<5:0> |       |       |       |       |  |

| bit 15 |     |       |             |       |       |       | bit 8 |  |

| U-0   | U-0      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|----------|-----|-----|-----|-----|-----|-------|

| _     | _        | _   | _   | _   | _   | _   | _     |

| bit 7 | it 7 bit |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP118R<5:0>: Peripheral Output Function is Assigned to RP118 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-0 **Unimplemented:** Read as '0'

# REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|--------|----------|-----|-----|-----|-----|-----|-----|

| _      | _        | _   | _   | _   | _   | _   | _   |

| bit 15 | t 15 bit |     |     |     |     |     |     |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------------|-------|-------|-------|-------|-------|

| _     | _   | RP120R<5:0> |       |       |       |       |       |

| bit 7 | _   | _           |       |       | _     | _     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 RP120R<5:0>: Peripheral Output Function is Assigned to RP120 Output Pin bits

(see Table 11-3 for peripheral function numbers)

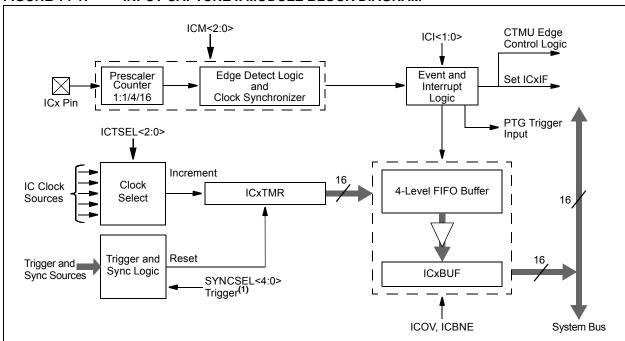

# 14.0 INPUT CAPTURE

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- · Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

# FIGURE 14-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

Note 1: The Trigger/Sync source is enabled by default and is set to Timer3 as a source. This timer must be enabled for proper ICx module operation or the Trigger/Sync source must be changed to another source option.

#### **REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-----|--------|--------|-------|-------|

| IVRIE | WAKIE | ERRIE | _   | FIFOIE | RBOVIE | RBIE  | TBIE  |

| bit 7 |       |       |     |        |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7 IVRIE: Invalid Message Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 6 WAKIE: Bus Wake-up Activity Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 5 **ERRIE:** Error Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 4 Unimplemented: Read as '0'

bit 3 FIFOIE: FIFO Almost Full Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 2 RBOVIE: RX Buffer Overflow Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled RBIE: RX Buffer Interrupt Enable bit

bit 1

1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 0 TBIE: TX Buffer Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

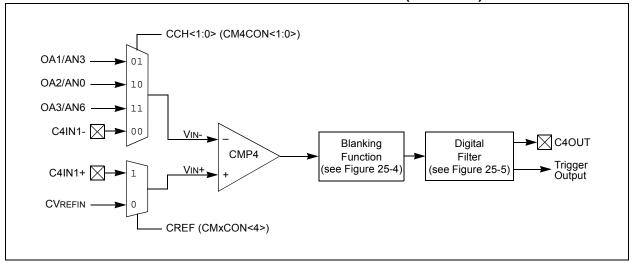

FIGURE 25-2: COMPARATOR MODULE BLOCK DIAGRAM (MODULE 4)

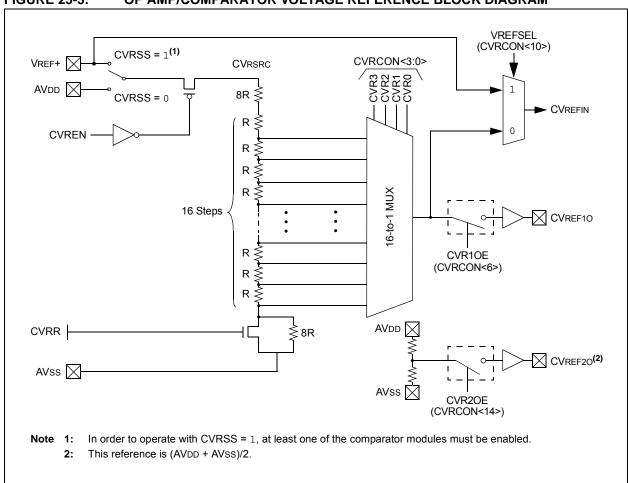

FIGURE 25-3: OP AMP/COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

# REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

bit 7-6 **EVPOL<1:0>:** Trigger/Event/Interrupt Polarity Select bits

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

Low-to-high transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

High-to-low transition of the comparator output.

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

Low-to-high transition of the comparator output

00 = Trigger/event/interrupt generation is disabled

- bit 5 **Unimplemented:** Read as '0'

- bit 4 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage(2)

- 0 = VIN+ input connects to CxIN1+ pin

- bit 3-2 **Unimplemented:** Read as '0'

- bit 1-0 CCH<1:0>: Op Amp/Comparator Channel Select bits<sup>(1)</sup>

- 11 = Unimplemented

- 10 = Unimplemented

- 01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup>

- 00 = Inverting input of the op amp/comparator connects to the CxIN1- pin

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either

two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note:

For more details on the instruction set, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

For more information on instructions that take more than one instruction cycle to execute, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", particularly the "Instruction Flow Types" section.

TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                       |

|-----------------|-----------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                   |

| (text)          | Means "content of text"                                                           |

| [text]          | Means "the location addressed by text"                                            |

| {}              | Optional field or operation                                                       |

| a ∈ {b, c, d}   | a is selected from the set of values b, c, d                                      |

| <n:m></n:m>     | Register bit field                                                                |

| .b              | Byte mode selection                                                               |

| .d              | Double-Word mode selection                                                        |

| .S              | Shadow register select                                                            |

| .w              | Word mode selection (default)                                                     |

| Acc             | One of two accumulators {A, B}                                                    |

| AWB             | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}           |

| bit4            | 4-bit bit selection field (used in word addressed instructions) ∈ {015}           |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero              |

| Expr            | Absolute address, label or expression (resolved by the linker)                    |

| f               | File register address ∈ {0x00000x1FFF}                                            |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                    |

| lit4            | 4-bit unsigned literal ∈ {015}                                                    |

| lit5            | 5-bit unsigned literal ∈ {031}                                                    |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                   |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode            |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                             |

| None            | Field does not require an entry, can be blank                                     |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate       |

| PC              | Program Counter                                                                   |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                 |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                             |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                    |

| Wb              | Base W register ∈ {W0W15}                                                         |

| Wd              | $Destination\ W\ register \in \{\ Wd,\ [Wd],\ [Wd++],\ [Wd],\ [++Wd],\ [Wd]\ \}$  |

| Wdo             | Destination W register ∈ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax    | Description                        | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|--------|--------------------|------------------------------------|---------------|-------------------------------|--------------------------|

| 72                 | SL                   | SL     | f                  | f = Left Shift f                   | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | f,WREG             | WREG = Left Shift f                | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Ws,Wd              | Wd = Left Shift Ws                 | 1             | 1                             | C,N,OV,Z                 |

|                    |                      | SL     | Wb, Wns, Wnd       | Wnd = Left Shift Wb by Wns         | 1             | 1                             | N,Z                      |

|                    |                      | SL     | Wb,#lit5,Wnd       | Wnd = Left Shift Wb by lit5        | 1             | 1                             | N,Z                      |

| 73                 | SUB                  | SUB    | Acc <sup>(1)</sup> | Subtract Accumulators              | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | SUB    | f                  | f = f – WREG                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | f,WREG             | WREG = f – WREG                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | #lit10,Wn          | Wn = Wn – lit10                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,Ws,Wd           | Wd = Wb – Ws                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUB    | Wb,#lit5,Wd        | Wd = Wb – lit5                     | 1             | 1                             | C,DC,N,OV,Z              |

| 74                 | SUBB                 | SUBB   | f                  | $f = f - WREG - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | f,WREG             | WREG = $f - WREG - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | #lit10,Wn          | $Wn = Wn - lit10 - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,Ws,Wd           | $Wd = Wb - Ws - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBB   | Wb,#lit5,Wd        | $Wd = Wb - lit5 - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 75                 | SUBR                 | SUBR   | f                  | f = WREG – f                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | f,WREG             | WREG = WREG – f                    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,Ws,Wd           | Wd = Ws – Wb                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBR   | Wb,#lit5,Wd        | Wd = lit5 – Wb                     | 1             | 1                             | C,DC,N,OV,Z              |

| 76                 | SUBBR                | SUBBR  | f                  | $f = WREG - f - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | f,WREG             | WREG = WREG – $f - (\overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,Ws,Wd           | $Wd = Ws - Wb - (\overline{C})$    | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | SUBBR  | Wb,#lit5,Wd        | $Wd = lit5 - Wb - (\overline{C})$  | 1             | 1                             | C,DC,N,OV,Z              |

| 77                 | SWAP                 | SWAP.b | Wn                 | Wn = nibble swap Wn                | 1             | 1                             | None                     |

|                    |                      | SWAP   | Wn                 | Wn = byte swap Wn                  | 1             | 1                             | None                     |

| 78                 | TBLRDH               | TBLRDH | Ws,Wd              | Read Prog<23:16> to Wd<7:0>        | 1             | 5                             | None                     |

| 79                 | TBLRDL               | TBLRDL | Ws,Wd              | Read Prog<15:0> to Wd              | 1             | 5                             | None                     |

| 80                 | TBLWTH               | TBLWTH | Ws,Wd              | Write Ws<7:0> to Prog<23:16>       | 1             | 2                             | None                     |

| 81                 | TBLWTL               | TBLWTL | Ws,Wd              | Write Ws to Prog<15:0>             | 1             | 2                             | None                     |

| 82                 | ULNK                 | ULNK   |                    | Unlink Frame Pointer               | 1             | 1                             | SFA                      |

| 83                 | XOR                  | XOR    | f                  | f = f .XOR. WREG                   | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | f,WREG             | WREG = f .XOR. WREG                | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | #lit10,Wn          | Wd = lit10 .XOR. Wd                | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | Wb,Ws,Wd           | Wd = Wb .XOR. Ws                   | 1             | 1                             | N,Z                      |

|                    |                      | XOR    | Wb,#lit5,Wd        | Wd = Wb .XOR. lit5                 | 1             | 1                             | N,Z                      |

| 84                 | ZE                   | ZE     | Ws, Wnd            | Wnd = Zero-extend Ws               | 1             | 1                             | C,Z,N                    |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

<sup>2:</sup> Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| dsPIC33EPXXXGP50 | X, dsPIC33EPXXXMC | 20X/50X AND PIC2 | 4EPXXXGP/MC20X |

|------------------|-------------------|------------------|----------------|

| NOTES:           |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

|                  |                   |                  |                |

| DSPIC33EPXXXGP50X, DSPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X |

|-----------------------------------------------------------------|

| NOTES:                                                          |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |

|                                                                 |