Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc502-h-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

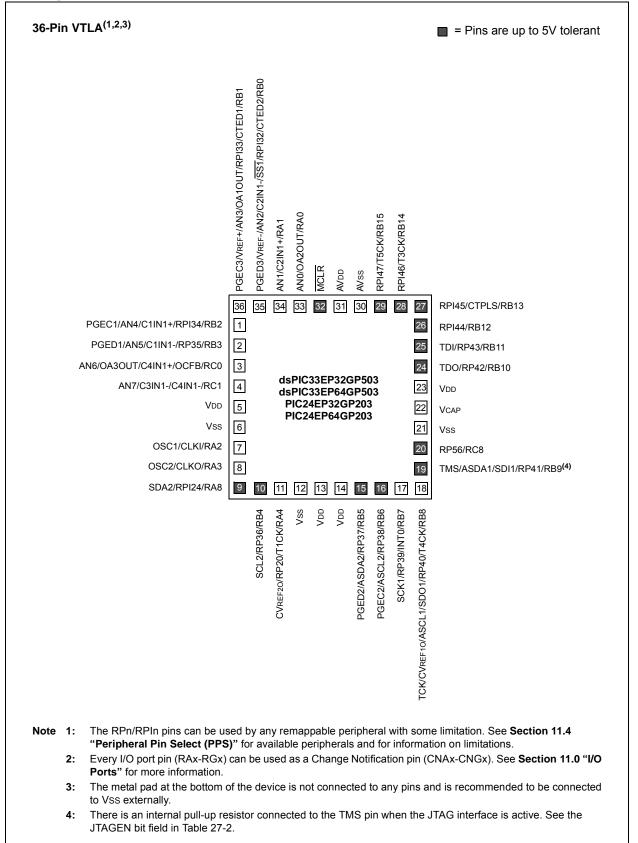

#### **Pin Diagrams (Continued)**

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

## 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

## 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

#### 3.3 Data Space Addressing

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in **Section 4.2 "Data Address Space"**.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "**Data Memory**" (DS70595) and "**Program Memory**" (DS70613) sections in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

## TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7       | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |             | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |             | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |             |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _           | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |             | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |             | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _           | _       | _           | _       | —       | —      | —           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       | VECNUM<7:0> |         |             |         |         |        | 0000        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4   | -12:     | PWM RI         | EGISTE      | R MAP      | FOR de      | sPIC33E      | PXXXN   | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE  | S ONI | _Y    |            |       |               |

|-----------|----------|----------------|-------------|------------|-------------|--------------|---------|----------|----------|---------|-------|--------|---------|-------|-------|------------|-------|---------------|

| File Name | Addr.    | Bit 15         | Bit 14      | Bit 13     | Bit 12      | Bit 11       | Bit 10  | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

| PTCON     | 0C00     | PTEN           | —           | PTSIDL     | SESTAT      | SEIEN        | EIPU    | SYNCPOL  | SYNCOEN  | SYNCEN  | SY    | NCSRC< | 2:0>    |       | SEV   | /TPS<3:0>  |       | 0000          |

| PTCON2    | 0C02     | _              | —           | _          | _           | _            | —       | —        | —        | —       | _     | —      | _       | —     |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER     | 0C04     |                |             |            |             |              |         |          | PTPER<15 | :0>     |       |        |         |       |       |            |       | 00F8          |

| SEVTCMP   | 0C06     |                |             |            |             |              |         |          | SEVTCMP< | 5:0>    |       |        |         |       |       |            |       | 0000          |

| MDC       | 0C0A     |                |             |            |             |              |         |          | MDC<15:  | )>      |       |        |         |       |       |            |       | 0000          |

| CHOP      | 0C1A     | CHPCLKEN       | _           | _          | _           | _            | _       |          |          |         |       | CHOPCI | _K<9:0> |       |       |            |       | 0000          |

| PWMKEY    | 0C1E     |                |             |            |             |              |         |          | PWMKEY<1 | 5:0>    |       |        |         |       |       |            |       | 0000          |

| Legend: - | – = unir | mplemented, re | ead as '0'. | Reset valu | es are show | vn in hexade | ecimal. |          |          |         |       |        |         |       |       |            |       |               |

#### TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |         |                                                                                       |          | I OIT U                                        |        |           |          |        | 1102-   |               |      |          |       |        |      |

|-----------|-------|---------|--------|---------|---------------------------------------------------------------------------------------|----------|------------------------------------------------|--------|-----------|----------|--------|---------|---------------|------|----------|-------|--------|------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | t 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |          |                                                |        |           |          |        |         | All<br>Resets |      |          |       |        |      |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                                                | CLIEN    | TRGIEN                                         | ITB    | MDCS      | DTC<     | :1:0>  | DTCP    | _             | MTBS | CAM      | XPRES | IUE    | 0000 |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | POLL                                                                                  | PMOD     | <1:0>                                          | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTDA   | T<1:0>        | CLDA | T<1:0>   | SWAP  | OSYNC  | C000 |

| FCLCON1   | 0C24  | _       |        | (       | CLSRC<4:                                                                              | 0>       |                                                | CLPOL  | CLMOD     |          | FL     | TSRC<4: | )>            |      | FLTPOL   | FLTMO | D<1:0> | 0000 |

| PDC1      | 0C26  |         |        |         |                                                                                       |          |                                                |        | PDC1<15:0 | )>       |        |         |               |      |          |       |        | FFF8 |

| PHASE1    | 0C28  |         |        |         |                                                                                       |          |                                                |        | PHASE1<15 | :0>      |        |         |               |      |          |       |        | 0000 |

| DTR1      | 0C2A  | _       | _      |         |                                                                                       |          |                                                |        |           | DTR1<13: | 0>     |         |               |      |          |       |        | 0000 |

| ALTDTR1   | 0C2C  | _       | _      |         |                                                                                       |          |                                                |        | А         | LTDTR1<1 | 3:0>   |         |               |      |          |       |        | 0000 |

| TRIG1     | 0C32  |         |        |         |                                                                                       |          |                                                |        | TRGCMP<18 | 5:0>     |        |         |               |      |          |       |        | 0000 |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |                                                                                       | _        | _                                              | _      | _         | _        | _      |         |               | TRG  | STRT<5:0 | >     |        | 0000 |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLF                                                                                   | FLTLEBEN | CLLEBEN                                        | _      | _         | _        | _      | BCH     | BCL           | BPHH | BPHL     | BPLH  | BPLL   | 0000 |

| LEBDLY1   | 0C3C  | _       | _      | —       | —                                                                                     |          |                                                |        |           |          | LEB<11 | :0>     |               |      |          |       |        | 0000 |

| AUXCON1   | 0C3E  | —       | —      | _       |                                                                                       |          | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN |        |           |          |        |         |               | 0000 |          |       |        |      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

#### REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

NOTES:

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 17-17: INT1TMRH: INTERVAL 1 TIMER HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | R<31:24>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTTM | R<23:16>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

#### REGISTER 17-18: INT1TMRL: INTERVAL 1 TIMER LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | IR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTT  | /IR<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

| U-0                     | U-0                                  | U-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |  |  |

|-------------------------|--------------------------------------|------------------------------------|---------|------------------|-----------------|-----------------|---------|--|--|--|--|--|

| _                       | _                                    |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1         | FILHIT0 |  |  |  |  |  |

| bit 15                  | <b>I</b>                             | •                                  |         |                  |                 |                 | bit 8   |  |  |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |  |  |

| U-0                     | R-1                                  | R-0                                | R-0     | R-0              | R-0             | R-0             | R-0     |  |  |  |  |  |

| _                       | ICODE6                               | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1          | ICODE0  |  |  |  |  |  |

| bit 7                   |                                      |                                    |         |                  |                 |                 | bit     |  |  |  |  |  |

| Logondi                 |                                      |                                    |         |                  |                 |                 |         |  |  |  |  |  |

| Legend:<br>R = Readable | - hit                                |                                    | hit.    |                  | nonted hit rea  | d aa 'O'        |         |  |  |  |  |  |

| -n = Value at           |                                      | W = Writable                       |         | '0' = Bit is cle | mented bit, rea |                 |         |  |  |  |  |  |

| -n = value at           | POR                                  | '1' = Bit is set                   |         | 0 = Bit is cie   | ared            | x = Bit is unkr | IOWN    |  |  |  |  |  |

| bit 15-13               | Unimplemen                           | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |  |  |

| bit 12-8                | =                                    | Filter Hit Num                     |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | 1 = Reserved                       |         |                  |                 |                 |         |  |  |  |  |  |

|                         | 01111 <b>= Filte</b>                 | r 15                               |         |                  |                 |                 |         |  |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | - 1                                |         |                  |                 |                 |         |  |  |  |  |  |

|                         | 00001 = Filte<br>00000 = Filte       |                                    |         |                  |                 |                 |         |  |  |  |  |  |

| bit 7                   |                                      | ted: Read as '                     | 0'      |                  |                 |                 |         |  |  |  |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | 1000101-1111111 = Reserved           |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | IFO almost full                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | eceiver overflo                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | 1000010 = K<br>1000001 = E           | /ake-up interru<br>rror interrupt  | μ       |                  |                 |                 |         |  |  |  |  |  |

|                         | 1000000 = N                          |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | 11111 = Rese                       |         |                  |                 |                 |         |  |  |  |  |  |

|                         | •                                    | B15 buffer inte                    | inupt   |                  |                 |                 |         |  |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | •                                    |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | 0001001 <b>= R</b>                   | B9 buffer inter                    | rupt    |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | B8 buffer inter                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | RB5 buffer inte                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | RB4 buffer inte                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         | 0000011 <b>= T</b>                   | RB3 buffer inte                    | errupt  |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      |                                    |         |                  |                 |                 |         |  |  |  |  |  |

|                         |                                      | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                 |         |  |  |  |  |  |

#### REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PTGSD | LIM<15:8>         |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PTGSE | )LIM<7:0>         |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0     | R/W-0 |

|-----------------------------------|-------|------------------|-------|-------------------|-----------------|-----------|-------|

|                                   |       |                  | PTGC0 | LIM<15:8>         |                 |           |       |

| bit 15                            |       |                  |       |                   |                 |           | bit 8 |

|                                   |       |                  |       |                   |                 |           |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0     | R/W-0 |

|                                   |       |                  | PTGC  | )LIM<7:0>         |                 |           |       |

| bit 7                             |       |                  |       |                   |                 |           | bit 0 |

|                                   |       |                  |       |                   |                 |           |       |

| Legend:                           |       |                  |       |                   |                 |           |       |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplem      | nented bit, rea | ad as '0' |       |

| -n = Value at P                   | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | nown      |       |

bit 15-0 **PTGC0LIM<15:0>:** PTG Counter 0 Limit Register bits May be used to specify the loop count for the PTGJMPC0 Step command or as a limit register for the General Purpose Counter 0.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0    | RW-0     |

|--------|-----|-----|-----|----------|----------|----------|----------|

| —      | —   | —   | —   | SELSRCC3 | SELSRCC2 | SELSRCC1 | SELSRCC0 |

| bit 15 |     |     |     |          |          |          | bit 8    |

|        |     |     |     |          |          |          |          |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| SELSRCB3 | SELSRCB2 | SELSRCB1 | SELSRCB0 | SELSRCA3 | SELSRCA2 | SELSRCA1 | SELSRCA0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

## bit 15-12 Unimplemented: Read as '0'

| DIL 10-12 | Uninpienenteu. Reau as 0                                                                                                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 11-8  | SELSRCC<3:0>: Mask C Input Select bits                                                                                                                                                                                                         |

|           | 1111 <b>= FLT4</b>                                                                                                                                                                                                                             |

|           | 1110 <b>= FLT2</b>                                                                                                                                                                                                                             |

|           | 1101 <b>= PTGO19</b>                                                                                                                                                                                                                           |

|           | 1100 = PTGO18                                                                                                                                                                                                                                  |

|           | 1011 = Reserved                                                                                                                                                                                                                                |

|           | 1010 = Reserved                                                                                                                                                                                                                                |

|           | 1001 = Reserved                                                                                                                                                                                                                                |

|           | 1000 = Reserved                                                                                                                                                                                                                                |

|           | 0111 = Reserved                                                                                                                                                                                                                                |

|           | 0110 = Reserved                                                                                                                                                                                                                                |

|           | 0101 = PWM3H                                                                                                                                                                                                                                   |

|           | 0100 = PWM3L                                                                                                                                                                                                                                   |

|           | 0011 = PWM2H                                                                                                                                                                                                                                   |

|           | 0010 = PWM2L                                                                                                                                                                                                                                   |

|           | 0001 = PWM1H                                                                                                                                                                                                                                   |

|           | 0000 = PWM1L                                                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                                |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits                                                                                                                                                                                                         |

| bit 7-4   | SELSRCB<3:0>: Mask B Input Select bits 1111 = FLT4                                                                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2                                                                                                                                                                                                                     |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19                                                                                                                                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18                                                                                                                                                                                   |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved                                                                                                                                                                |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved                                                                                                                                             |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved                                                                                                                          |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved                                                                                                       |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved                                                                                    |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>1000 = Reserved<br>0111 = Reserved<br>0110 = Reserved                                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H                                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L                                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0101 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H<br>0010 = PWM2L |

| bit 7-4   | 1111 = FLT4<br>1110 = FLT2<br>1101 = PTGO19<br>1100 = PTGO18<br>1011 = Reserved<br>1010 = Reserved<br>1001 = Reserved<br>0111 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0110 = PWM3H<br>0100 = PWM3L<br>0011 = PWM2H                 |

## 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F. The PIC24EP instruction set is almost identical to that of the PIC24F and PIC24H.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| DC CHARACTI       | ERISTICS            |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |            |        |            |  |  |

|-------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------------|--|--|

| Parameter<br>No.  | Тур.                | Max. | Units                                                                                                                                                                                                                                                                             | Conditions |        |            |  |  |

| Idle Current (III | dle) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                   |            |        |            |  |  |

| DC40d             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                | -40°C      |        |            |  |  |

| DC40a             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                | +25°C      | - 3.3V | 10 MIPS    |  |  |

| DC40b             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                | +85°C      | 3.3V   | 10 101195  |  |  |

| DC40c             | 3                   | 8    | mA                                                                                                                                                                                                                                                                                | +125°C     |        |            |  |  |

| DC42d             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                | -40°C      |        |            |  |  |

| DC42a             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                | +25°C      | 3.3V   | 20 MIPS    |  |  |

| DC42b             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                | +85°C      |        | 20 1011 3  |  |  |

| DC42c             | 6                   | 12   | mA                                                                                                                                                                                                                                                                                | +125°C     |        |            |  |  |

| DC44d             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                | -40°C      |        | 40 MIPS    |  |  |

| DC44a             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                | +25°C      | 3.3V   |            |  |  |

| DC44b             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                | +85°C      | 5.5 V  | 40 10117 3 |  |  |

| DC44c             | 11                  | 18   | mA                                                                                                                                                                                                                                                                                | +125°C     |        |            |  |  |

| DC45d             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                | -40°C      |        |            |  |  |

| DC45a             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                | +25°C      | - 3.3V | 60 MIPS    |  |  |

| DC45b             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                | +85°C      | 5.30   | 00 1011-5  |  |  |

| DC45c             | 17                  | 27   | mA                                                                                                                                                                                                                                                                                | +125°C     |        |            |  |  |

| DC46d             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                | -40°C      |        |            |  |  |

| DC46a             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                | +25°C      | 3.3V   | 70 MIPS    |  |  |

| DC46b             | 20                  | 35   | mA                                                                                                                                                                                                                                                                                | +85°C      |        |            |  |  |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (lidle)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active; OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}}$  = VDD, WDT and FSCM are disabled

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- JTAG is disabled

| DC CH        | ARACTE | RISTICS                                                 | (unless o | <b>I Operatin</b><br>otherwise<br>g temperat | ture -40° | C ≤ TA ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------|--------|---------------------------------------------------------|-----------|----------------------------------------------|-----------|----------|-----------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                          | Min.      | Тур.                                         | Max.      | Units    | Conditions                                                      |

|              | VIL    | Input Low Voltage                                       |           |                                              |           |          |                                                                 |

| DI10         |        | Any I/O Pin and MCLR                                    | Vss       | —                                            | 0.2 VDD   | V        |                                                                 |

| DI18         |        | I/O Pins with SDAx, SCLx                                | Vss       | —                                            | 0.3 VDD   | V        | SMBus disabled                                                  |

| DI19         |        | I/O Pins with SDAx, SCLx                                | Vss       | —                                            | 0.8       | V        | SMBus enabled                                                   |

|              | VIH    | Input High Voltage                                      |           |                                              |           |          |                                                                 |

| DI20         |        | I/O Pins Not 5V Tolerant                                | 0.8 VDD   | —                                            | Vdd       | V        | (Note 3)                                                        |

|              |        | I/O Pins 5V Tolerant and MCLR                           | 0.8 VDD   | —                                            | 5.5       | V        | (Note 3)                                                        |

|              |        | I/O Pins with SDAx, SCLx                                | 0.8 VDD   | —                                            | 5.5       | V        | SMBus disabled                                                  |

|              |        | I/O Pins with SDAx, SCLx                                | 2.1       | _                                            | 5.5       | V        | SMBus enabled                                                   |

|              | ICNPU  | Change Notification Pull-up Current                     |           |                                              |           |          |                                                                 |

| DI30         |        |                                                         | 150       | 250                                          | 550       | μA       | VDD = 3.3V, VPIN = VSS                                          |

|              | ICNPD  | Change Notification<br>Pull-Down Current <sup>(4)</sup> |           |                                              |           |          |                                                                 |

| DI31         |        |                                                         | 20        | 50                                           | 100       | μA       | Vdd = 3.3V, Vpin = Vdd                                          |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (VSS 0.3). Characterized but not tested.

**5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- 8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

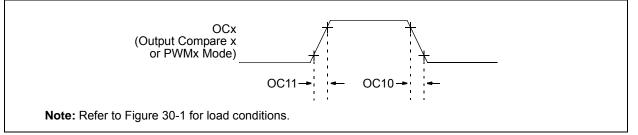

#### FIGURE 30-7: OUTPUT COMPARE x MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 30-27: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                    |

|--------------------|--------|-------------------------------|-------------------------------------------------------|------|------|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min.                                                  | Тур. | Max. | Units | Conditions         |

| OC10               | TccF   | OCx Output Fall Time          | _                                                     |      | _    | ns    | See Parameter DO32 |

| OC11               | TccR   | OCx Output Rise Time          | _                                                     | _    | —    | ns    | See Parameter DO31 |

Note 1: These parameters are characterized but not tested in manufacturing.