Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc502-h-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

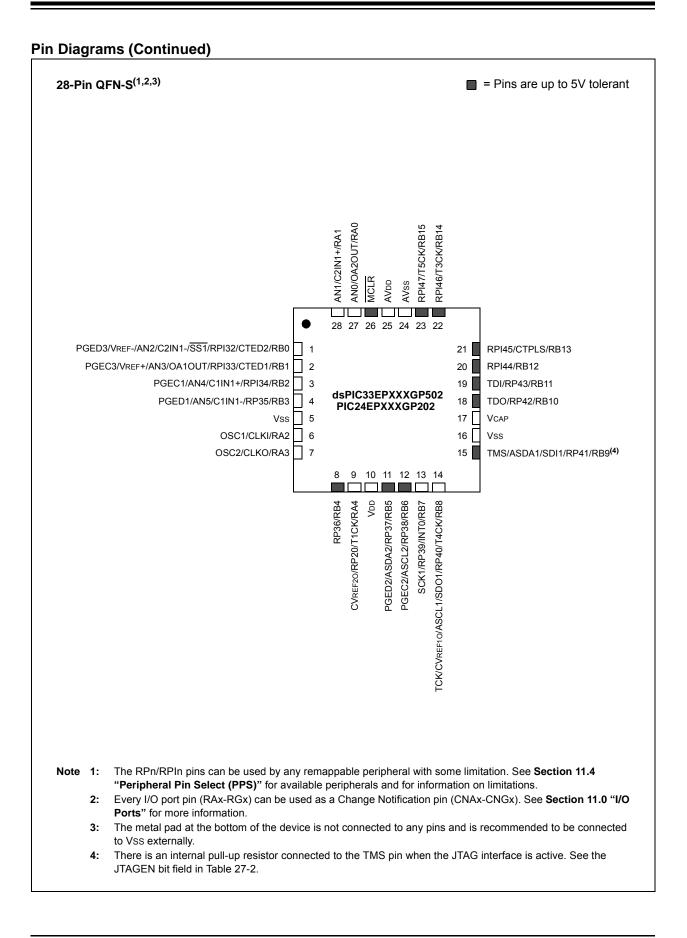

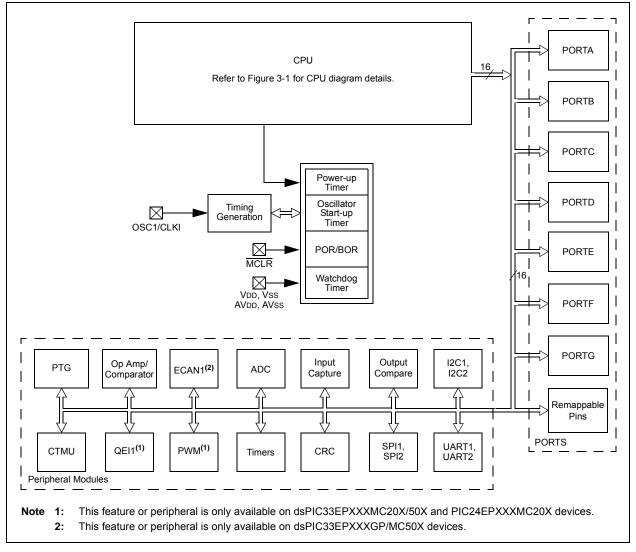

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

## FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

# 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

## FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|--------|-------|-------|----------|---------|---------|---------|---------|--------|---------|--------|---------------|

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR | COVAERR | COVBERR | OVATE  | OVBTE | COVTE | SFTACERR | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP | _       | _       | _      | _     | _     | _        | —       | _       | _       | —       | INT2EP | INT1EP  | INT0EP | 8000          |

| INTCON3      | 08C4  |        | _      | _      | —       | _       | _      |       | _     | _        | —       | DAE     | DOOVR   | —       | _      | _       |        | 0000          |

| INTCON4      | 08C6  |        | _      |        |         |         | Ι      | _     |       |          | —       | _       |         | —       |        |         | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _      | _       |         | ILR<   | 3:0>  |       |          |         |         | VECNU   | M<7:0>  |        |         |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-34: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3    | Bit 2 | Bit 1   | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|----------|-------|-------|--------|----------|-------|---------|-------|---------------|

| NVMCON    | 0728  | WR     | WREN   | WRERR  | NVMSIDL | _      | _      | —     | _     | _        | _     | _     | —      |          | NVMC  | )P<3:0> |       | 0000          |

| NVMADRL   | 072A  |        |        |        |         |        |        |       | NVMAD | )R<15:0> |       |       |        |          |       |         |       | 0000          |

| NVMADRH   | 072C  | _      | _      | _      | _       | -      | _      | _     | _     |          |       |       | NVMADF | R<23:16> |       |         |       | 0000          |

| NVMKEY    | 072E  |        |        | _      | —       | _      |        | —     | -     |          |       |       | NVMKE  | Y<7:0>   |       |         |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-35: SYSTEM CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4   | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|--------|--------|-----------|-------|---------|--------|--------|---------|-------|--------|-------|-------|---------------|

| RCON      | 0740  | TRAPR  | IOPUWR | _         | _      | VREGSF | _      | СМ        | VREGS | EXTR    | SWR    | SWDTEN | WDTO    | SLEEP | IDLE   | BOR   | POR   | Note 1        |

| OSCCON    | 0742  | _      | 0      | COSC<2:0> |        | —      |        | NOSC<2:0> |       | CLKLOCK | IOLOCK | LOCK   | _       | CF    | _      | _     | OSWEN | Note 2        |

| CLKDIV    | 0744  | ROI    | [      | OOZE<2:0> |        | DOZEN  | F      | RCDIV<2:0 | >     | PLLPOS  | T<1:0> | _      |         | F     | LLPRE< | 4:0>  |       | 0030          |

| PLLFBD    | 0746  | _      | _      | _         | _      | —      | _      | _         |       |         |        | PLLD   | IV<8:0> |       |        |       |       | 0030          |

| OSCTUN    | 0748  | _      | _      | _         | _      | —      | _      | _         | _     | _       |        |        |         | TUN≤  | <5:0>  |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses.

## TABLE 4-36: REFERENCE CLOCK REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON   | 074E  | ROON   | —      | ROSSLP | ROSEL  |        | RODI   | V<3:0> |       | _     | _     | —     | _     | _     | —     | _     | -     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 11.4.4.2 Output Mapping

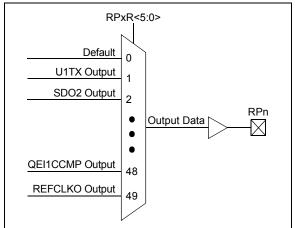

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

## 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

## TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nown                                                                                                                                                                                                                                                                                                                                                                                                |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Unimplemer                   | nted: Read as '0                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| (see Table 11<br>1111001 = I | I-2 for input pin's nput tied to RPI1                                                                                                                                  | election num<br>21                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          | onding RPn Pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              | e bit<br>POR<br>Unimplemen<br>IC2R<6:0>: /<br>(see Table 11<br>1111001 = I<br>0000001 = I<br>0000000 = I<br>Unimplemen<br>IC1R<6:0>: /<br>(see Table 11<br>1111001 = I | e bit W = Writable b<br>POR '1' = Bit is set<br>Unimplemented: Read as '0<br>IC2R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s<br>1111001 = Input tied to RPI1<br>0000001 = Input tied to CMP<br>0000000 = Input tied to Vss<br>Unimplemented: Read as '0<br>IC1R<6:0>: Assign Input Cap<br>(see Table 11-2 for input pin s | e bit W = Writable bit<br>POR '1' = Bit is set<br>Unimplemented: Read as '0'<br>IC2R<6:0>: Assign Input Capture 2 (IC2)<br>(see Table 11-2 for input pin selection num<br>1111001 = Input tied to RPI121 | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>       IC1R<6:0>         e bit       W = Writable bit       U = Unimplem         POR       '1' = Bit is set       '0' = Bit is clear         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Correspond (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>         e bit       W = Writable bit       U = Unimplemented bit, real         POR       '1' = Bit is set       '0' = Bit is cleared         Unimplemented:       Read as '0'         IC2R<6:0>:       Assign Input Capture 2 (IC2) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         0000001 = Input tied to CMP1         0000000 = Input tied to Vss         Unimplemented:         Read as '0'         IC1R<6:0>:         Assign Input Capture 1 (IC1) to the Corresponding RPn Pi (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . | R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         IC1R<6:0>    e bit W = Writable bit U = Unimplemented bit, read as '0' POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkr Unimplemented: Read as '0' IC2R<6:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 <p< td=""></p<> |

## REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

## REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0       | >               |                 |        |

| bit 15       |              |                                                        |               |                  |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0           | 5444.0          |                 | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>      | >               |                 |        |

| bit 7        |              |                                                        |               |                  |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                  |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen     | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                  |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                  |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                  |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                  |                 |                 |        |

NOTES:

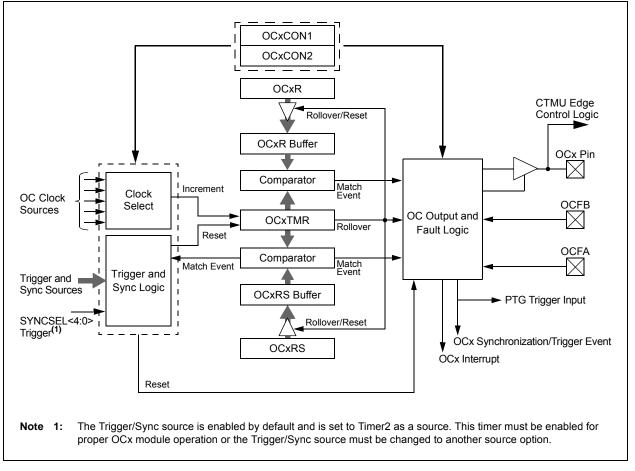

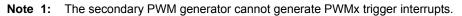

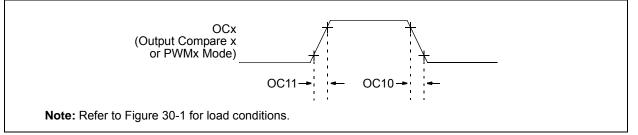

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

| R/W-0        | R/W-0             | R/W-0                                  | R/W-0          | U-0               | U-0                 | U-0              | U-0          |

|--------------|-------------------|----------------------------------------|----------------|-------------------|---------------------|------------------|--------------|

|              | TRGD              | V<3:0>                                 |                | —                 |                     | —                | _            |

| bit 15       |                   |                                        |                |                   |                     |                  | bit 8        |

|              |                   |                                        |                |                   |                     |                  |              |

| U-0          | U-0               | R/W-0                                  | R/W-0          | R/W-0             | R/W-0               | R/W-0            | R/W-0        |

| _            |                   |                                        |                | TRGSTF            | RT<5:0> <b>(1)</b>  |                  |              |

| bit 7        |                   |                                        |                |                   |                     |                  | bit          |

|              |                   |                                        |                |                   |                     |                  |              |

| Legend:      | 1. 1.4            |                                        |                |                   |                     |                  |              |

| R = Readab   |                   | W = Writable                           |                | •                 | nented bit, read    |                  |              |

| -n = Value a | t POR             | '1' = Bit is set                       |                | '0' = Bit is clea | ared                | x = Bit is unkn  | own          |

|              |                   |                                        |                |                   |                     |                  |              |

| bit 15-12    |                   | <b>)&gt;:</b> Trigger # Ou             | -              |                   |                     |                  |              |

|              |                   | per output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev<br>ger output for ev |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | per output for ev                      |                |                   |                     |                  |              |

|              |                   | per output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              | 0100 = Trigg      | ger output for ev                      | ery 5th trigge | r event           |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              |                   | ger output for ev                      |                |                   |                     |                  |              |

|              | 0000 = Trigg      | ger output for ev                      | ery trigger ev | ent               |                     |                  |              |

| bit 11-6     | -                 | nted: Read as '                        |                |                   |                     |                  |              |

| bit 5-0      | TRGSTRT<          | 5:0>: Trigger Po                       | stscaler Start | Enable Select     | bits <sup>(1)</sup> |                  |              |

|              | 111111 <b>=</b> W | aits 63 PWM cy                         | cles before g  | enerating the fir | st trigger event    | after the modu   | le is enable |

|              |                   |                                        |                |                   |                     |                  |              |

|              | •                 |                                        |                | ·                 |                     |                  |              |

|              | •                 |                                        |                | -                 |                     |                  |              |

|              | •                 |                                        |                | -                 |                     |                  |              |

|              | •<br>•<br>•       | aits 2 PW/M ava                        | les hefore co  | nerating the fire | t trigger event :   | after the module | a is anabled |

|              |                   | /aits 2 PWM cyc<br>/aits 1 PWM cyc     |                |                   |                     |                  |              |

# REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

| U-0             | U-0   | U-0              | U-0   | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

| —               | -     | —                | —     |                   | LEB             | <11:8>          |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | LEE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | id as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

# REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

## REGISTER 17-7: VEL1CNT: VELOCITY COUNTER 1 REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | VELC  | NT<15:8>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | VELC  | NT<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | oit   | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 VELCNT<15:0>: Velocity Counter bits

## REGISTER 17-8: INDX1CNTH: INDEX COUNTER 1 HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------------------|----------|-------|-------|-------|

|        |       |       | INDXCN <sup>®</sup> | T<31:24> |       |       |       |

| bit 15 |       |       |                     |          |       |       | bit 8 |

|        |       |       |                     |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0               | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | INDXCN              | T<23:16> |       |       |       |

| bit 7  |       |       |                     |          |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 INDXCNT<31:16>: High Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

## REGISTER 17-9: INDX1CNTL: INDEX COUNTER 1 LOW WORD REGISTER

'1' = Bit is set

| R/W-0          | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------|-------|------------------|-------|--------------|------------------|----------|-------|

|                |       |                  | INDXC | NT<15:8>     |                  |          |       |

| bit 15         |       |                  |       |              |                  |          | bit 8 |

|                |       |                  |       |              |                  |          |       |

| R/W-0          | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                |       |                  | INDXC | NT<7:0>      |                  |          |       |

| bit 7          |       |                  |       |              |                  |          | bit 0 |

|                |       |                  |       |              |                  |          |       |

| Legend:        |       |                  |       |              |                  |          |       |

| R = Readable b | oit   | W = Writable bit | t     | U = Unimpler | mented bit, read | l as '0' |       |

|                |       |                  |       |              |                  |          |       |

'0' = Bit is cleared

bit 15-0 INDXCNT<15:0>: Low Word Used to Form 32-Bit Index Counter Register (INDX1CNT) bits

-n = Value at POR

x = Bit is unknown

#### 18.3 SPIx Control Registers

#### R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0 U-0 SPIEN SPISIDL SPIBEC<2:0> \_\_\_\_\_ bit 15 R/W-0 R/W-0 R/W-0 R/C-0, HS R/W-0 R/W-0 R-0, HS, HC R-0, HS, HC SRMPT SPIROV SRXMPT SISEL2 SISEL1 SISEL0 SPITBF SPIRBF bit 7 Legend: C = Clearable bit HS = Hardware Settable bit HC = Hardware Clearable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 SPIEN: SPIx Enable bit 1 = Enables the module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables the module bit 14 Unimplemented: Read as '0' bit 13 SPISIDL: SPIx Stop in Idle Mode bit 1 = Discontinues the module operation when device enters Idle mode 0 = Continues the module operation in Idle mode bit 12-11 Unimplemented: Read as '0' bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode) Master mode: Number of SPIx transfers that are pending. Slave mode: Number of SPIx transfers that are unread. SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode) bit 7 1 = SPIx Shift register is empty and Ready-To-Send or receive the data 0 = SPIx Shift register is not empty bit 6 SPIROV: SPIx Receive Overflow Flag bit

#### REGISTER 18-1: SPIxSTAT: SPIx STATUS AND CONTROL REGISTER

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register 0 = No overflow has occurred SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode) 1 = RX FIFO is empty 0 = RX FIFO is not empty

#### bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

- 111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

- 110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

- 101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

- 100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

- 011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)