Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

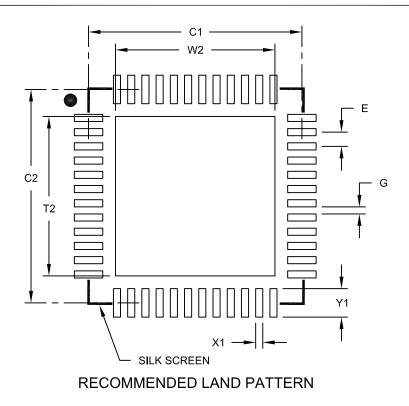

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep128mc502-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

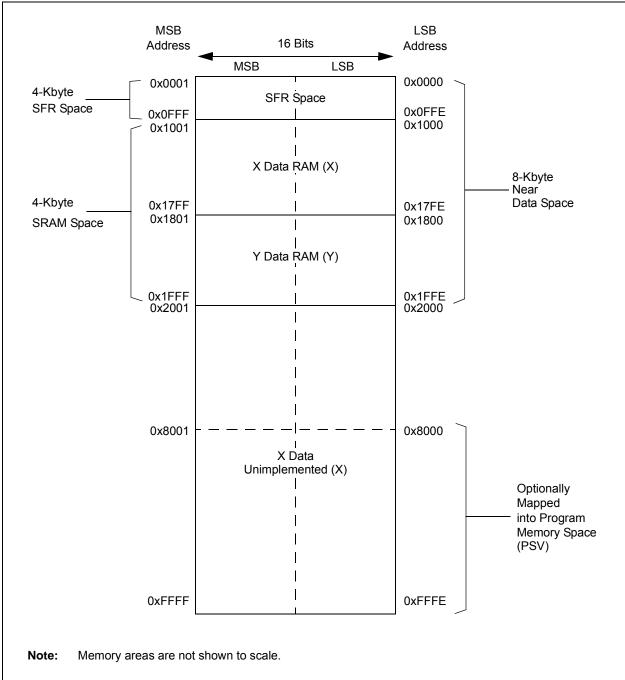

# 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

# 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

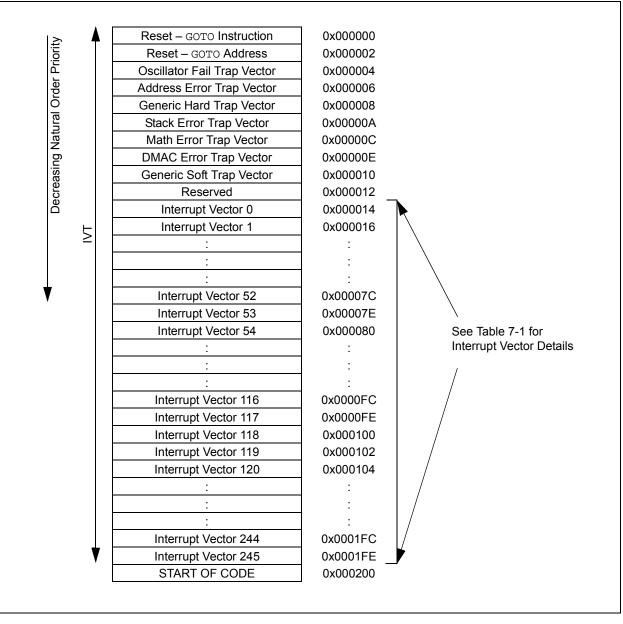

#### FIGURE 7-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X INTERRUPT VECTOR TABLE

## 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 7.3.1 KEY RESOURCES

- "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

### 7.4 Interrupt Control and Status Registers

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement the following registers for the interrupt controller:

- INTCON1

- INTCON2

- INTCON3

- INTCON4

- INTTREG

#### 7.4.1 INTCON1 THROUGH INTCON4

Global interrupt control functions are controlled from INTCON1, INTCON2, INTCON3 and INTCON4.

INTCON1 contains the Interrupt Nesting Disable bit (NSTDIS), as well as the control and status flags for the processor trap sources.

The INTCON2 register controls external interrupt request signal behavior and also contains the Global Interrupt Enable bit (GIE).

INTCON3 contains the status flags for the DMA and DO stack overflow status trap sources.

The INTCON4 register contains the software generated hard trap status bit (SGHT).

## 7.4.2 IFSx

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.4.3 IECx

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

#### 7.4.4 IPCx

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number bits (VECNUM<7:0>) and Interrupt Priority Level bits (ILR<3:0>) fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence as they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having Vector Number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0> and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

#### 7.4.6 STATUS/CONTROL REGISTERS

Although these registers are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. For more information on these registers refer to "**CPU**" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual".

- The CPU STATUS Register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user software can change the current CPU Interrupt Priority Level by writing to the IPLx bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-3 through Register 7-7 in the following pages.

| R/W-0           | R/W-0                                                                                                                       | R/W-1                             | R/W-1                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------|------------------------|--------------------|-----------------|-----------|--|--|--|--|

| ROI             | DOZE2 <sup>(1)</sup>                                                                                                        | DOZE1 <sup>(1)</sup>              | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2            | FRCDIV1         | FRCDIV0   |  |  |  |  |

| bit 15          |                                                                                                                             |                                   | •                    |                        |                    |                 | bit 8     |  |  |  |  |

|                 |                                                                                                                             |                                   |                      |                        |                    |                 |           |  |  |  |  |

| R/W-0           | R/W-1                                                                                                                       | U-0                               | R/W-0                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |  |  |  |  |

| PLLPOST1        | PLLPOST0                                                                                                                    | —                                 | PLLPRE4              | PLLPRE3                | PLLPRE2            | PLLPRE1         | PLLPRE0   |  |  |  |  |

| bit 7           |                                                                                                                             |                                   |                      |                        |                    |                 | bit (     |  |  |  |  |

|                 |                                                                                                                             |                                   |                      |                        |                    |                 |           |  |  |  |  |

| Legend:         |                                                                                                                             |                                   |                      |                        |                    |                 |           |  |  |  |  |

| R = Readable    |                                                                                                                             | W = Writable                      |                      | -                      | nented bit, read   |                 |           |  |  |  |  |

| -n = Value at F | POR                                                                                                                         | '1' = Bit is set                  |                      | '0' = Bit is cle       | ared               | x = Bit is unkr | nown      |  |  |  |  |

| h:+ 45          |                                                                                                                             | on Interview h                    |                      |                        |                    |                 |           |  |  |  |  |

| bit 15          |                                                                                                                             | on Interrupt bis will clear the l |                      |                        |                    |                 |           |  |  |  |  |

|                 |                                                                                                                             | s have no effect                  |                      | EN bit                 |                    |                 |           |  |  |  |  |

| bit 14-12       | •                                                                                                                           | Processor Clo                     |                      |                        |                    |                 |           |  |  |  |  |

|                 | 111 = Fcy div                                                                                                               |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 110 = Fcy divided by 64                                                                                                     |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 101 = Fcy divided by 32                                                                                                     |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 100 = FCY divided by 16<br>011 = FCY divided by 8 (default)                                                                 |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 010 = FCY divided by 8 (default)<br>010 = FCY divided by 4                                                                  |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 001 = Fcy divided by 2                                                                                                      |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 000 = Fcy div                                                                                                               | •                                 |                      |                        |                    |                 |           |  |  |  |  |

| bit 11          |                                                                                                                             | e Mode Enable                     |                      |                        |                    |                 |           |  |  |  |  |

|                 |                                                                                                                             |                                   |                      |                        | pheral clocks a    | nd the process  | or clocks |  |  |  |  |

|                 |                                                                                                                             | -                                 | -                    | ratio is forced to     |                    |                 |           |  |  |  |  |

| bit 10-8        |                                                                                                                             |                                   | RC Oscillator        | r Postscaler bit       | S                  |                 |           |  |  |  |  |

|                 | 111 = FRC di                                                                                                                |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 110 = FRC divided by 64<br>101 = FRC divided by 32                                                                          |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 100 <b>= FRC d</b> i                                                                                                        | vided by 16                       |                      |                        |                    |                 |           |  |  |  |  |

|                 | 011 = FRC di                                                                                                                |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 010 = FRC divided by 4<br>001 = FRC divided by 2                                                                            |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 |                                                                                                                             | •                                 | fault)               |                        |                    |                 |           |  |  |  |  |

| bit 7-6         | 000 = FRC divided by 1 (default)<br>PLLPOST<1:0>: PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler) |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 11 = Output divided by 8                                                                                                    |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | 10 = Reserve                                                                                                                |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 |                                                                                                                             | livided by 4 (de                  | efault)              |                        |                    |                 |           |  |  |  |  |

| bit 5           | 00 = Output d                                                                                                               | ted: Read as '                    | o'                   |                        |                    |                 |           |  |  |  |  |

|                 | •                                                                                                                           |                                   |                      |                        |                    |                 |           |  |  |  |  |

|                 | e DOZE<2:0> b<br>ZE<2:0> are ig                                                                                             |                                   | written to whe       | en the DOZEN           | bit is clear. If D | OZEN = 1, any   | writes to |  |  |  |  |

| <b>2:</b> This  | s bit is cleared                                                                                                            | when the ROI I                    | oit is set and a     | an interrupt occ       | urs.               |                 |           |  |  |  |  |

|                 | DOJENUS                                                                                                                     |                                   |                      |                        | ~ ~                |                 | <i>.</i>  |  |  |  |  |

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                             | R/W-0           | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|

| ROON          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ROSSLP                                                            | ROSEL           | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       | •                     | bit                   |  |  |

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                               | U-0             | U-0                   | U-0                   | U-0                   | U-0                   |  |  |

|               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                 |                 | _                     |                       | _                     |                       |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       |                       | bit                   |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |                 |                       |                       |                       |                       |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable                                                      | bit             | U = Unimpler          | nented bit, read      | l as '0'              |                       |  |  |

| -n = Value at |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                  |                 | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |  |  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as ' | out is disabled |                       | .K pin <sup>(2)</sup> |                       |                       |  |  |

| bit 13        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ference Oscilla                                                   |                 | en hit                |                       |                       |                       |  |  |

|               | 1 = Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e oscillator out                                                  | out continues   | to run in Sleep       |                       |                       |                       |  |  |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | crystal is used                                                   | as the refere   | nce clock             |                       |                       |                       |  |  |

| bit 11-8      | <ul> <li>0 = Reference oscillator output is disabled in Sleep</li> <li>ROSEL: Reference Oscillator Source Select bit</li> <li>1 = Oscillator crystal is used as the reference clock</li> <li>0 = System clock is used as the reference clock</li> <li>RODIV&lt;3:0&gt;: Reference Oscillator Divider bits<sup>(1)</sup></li> <li>1111 = Reference clock divided by 32,768</li> <li>1100 = Reference clock divided by 16,384</li> <li>1101 = Reference clock divided by 8,192</li> <li>1100 = Reference clock divided by 4,096</li> <li>1011 = Reference clock divided by 2,048</li> <li>1010 = Reference clock divided by 1,024</li> <li>1001 = Reference clock divided by 256</li> <li>0111 = Reference clock divided by 128</li> <li>0110 = Reference clock divided by 32</li> <li>010 = Reference clock divided by 32</li> <li>0111 = Reference clock divided by 32</li> <li>0112 = Reference clock divided by 32</li> <li>0131 = Reference clock divided by 40</li> </ul> |                                                                   |                 |                       |                       |                       |                       |  |  |

|               | 0000 = Refer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ence clock                                                        | -               |                       |                       |                       |                       |  |  |

#### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

## REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

# 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

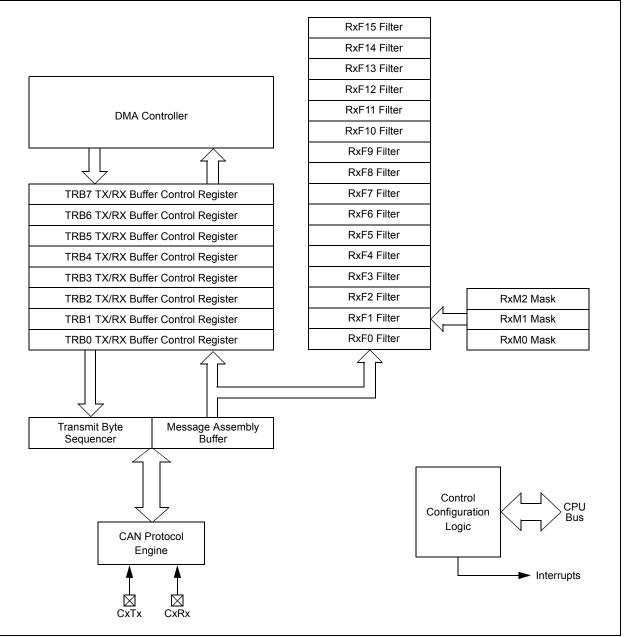

# 21.4 ECAN Control Registers

| U-0             | U-0                                                                                                              | R/W-0                                                     | R/W-0                         | R/W-0                          | R/W-1            | R/W-0           | R/W-0  |

|-----------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|--------------------------------|------------------|-----------------|--------|

| —               | —                                                                                                                | CSIDL                                                     | ABAT                          | CANCKS                         | REQOP2           | REQOP1          | REQOP0 |

| bit 15          |                                                                                                                  |                                                           |                               |                                |                  |                 | bit 8  |

| R-1             | R-0                                                                                                              | R-0                                                       | U-0                           | R/W-0                          | U-0              | U-0             | R/W-0  |

| OPMODE2         | OPMODE1                                                                                                          | OPMODE0                                                   | _                             | CANCAP                         |                  |                 | WIN    |

| bit 7           |                                                                                                                  |                                                           |                               |                                |                  |                 | bit (  |

| Legend:         |                                                                                                                  |                                                           |                               |                                |                  |                 |        |

| R = Readable    | bit                                                                                                              | W = Writable I                                            | oit                           | U = Unimpler                   | mented bit, read | d as '0'        |        |

| -n = Value at F | OR                                                                                                               | '1' = Bit is set                                          |                               | '0' = Bit is cle               |                  | x = Bit is unkr | nown   |

|                 |                                                                                                                  |                                                           |                               |                                |                  |                 |        |

| bit 15-14       | Unimplemen                                                                                                       | ted: Read as 'o                                           | )'                            |                                |                  |                 |        |

| bit 13          | CSIDL: ECAN                                                                                                      | Nx Stop in Idle I                                         | Node bit                      |                                |                  |                 |        |

|                 |                                                                                                                  | ues module opera module opera                             |                               | device enters I<br>ode         | dle mode         |                 |        |

| bit 12          | ABAT: Abort                                                                                                      | All Pending Tra                                           | nsmissions b                  | bit                            |                  |                 |        |

|                 |                                                                                                                  | I transmit buffe<br>ill clear this bit                    |                               | ansmission<br>smissions are a  | aborted          |                 |        |

| bit 11          | CANCKS: EC                                                                                                       | ANx Module C                                              | lock (FCAN)                   | Source Select b                | bit              |                 |        |

|                 | 1 = FCAN is e<br>0 = FCAN is e                                                                                   | ·                                                         |                               |                                |                  |                 |        |

| bit 10-8        | 111 = Set Lis<br>110 = Reserv<br>101 = Reserv<br>100 = Set Co<br>011 = Set Lis<br>010 = Set Loc<br>001 = Set Dis | ed<br>nfiguration mod<br>ten Only mode<br>opback mode     | es mode<br>le                 | bits                           |                  |                 |        |

| bit 7-5         | 111 = Module<br>110 = Reserv<br>101 = Reserv<br>100 = Module                                                     |                                                           | Messages n<br>ation mode      | node                           |                  |                 |        |

|                 | 010 = Module<br>001 = Module<br>000 = Module                                                                     | e is in Loopback<br>e is in Disable n<br>e is in Normal C | mode<br>node<br>operation mod | de                             |                  |                 |        |

| bit 4           | -                                                                                                                | ted: Read as '                                            |                               |                                |                  |                 |        |

| bit 3           |                                                                                                                  | nput capture ba                                           |                               | Capture Event<br>message recei |                  |                 |        |

| bit 2-1         |                                                                                                                  | ted: Read as '(                                           | ı'                            |                                |                  |                 |        |

| bit 0           | -                                                                                                                | ap Window Sele                                            |                               |                                |                  |                 |        |

| UIL U           | 1 = Uses filter                                                                                                  | -                                                         | יטו אונ                       |                                |                  |                 |        |

### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0               | R/W-x         | R/W-x                                   | R/W-x            | R/W-x    | R/W-x |

|---------------|---------------------------|-------------------|---------------|-----------------------------------------|------------------|----------|-------|

|               | —                         | _                 | SID10         | SID9                                    | SID8             | SID7     | SID6  |

| bit 15        |                           |                   |               |                                         |                  |          | bit 8 |

| R/W-x         | R/W-x                     | R/W-x             | R/W-x         | R/W-x                                   | R/W-x            | R/W-x    | R/W-x |

| SID5          | SID4                      | SID3              | SID2          | SID1                                    | SID0             | SRR      | IDE   |

| bit 7         |                           |                   |               |                                         | •                |          | bit 0 |

| Legend:       |                           |                   |               |                                         |                  |          |       |

| R = Readabl   | e bit                     | W = Writable      | bit           | U = Unimpler                            | mented bit, read | l as '0' |       |

| -n = Value at | POR                       | '1' = Bit is set  |               | '0' = Bit is cleared x = Bit is unknown |                  |          |       |

|               |                           |                   |               |                                         |                  |          |       |

| bit 15-13     | Unimplemen                | ted: Read as '    | כי            |                                         |                  |          |       |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | Standard Identifi | ier bits      |                                         |                  |          |       |

| bit 1         | SRR: Substitu             | ute Remote Re     | quest bit     |                                         |                  |          |       |

|               | When IDE =                | 0:                |               |                                         |                  |          |       |

|               | 1 = Message               | will request rer  | note transmis | ssion                                   |                  |          |       |

|               | 0 = Normal m              | nessage           |               |                                         |                  |          |       |

|               | When IDE = 1              | <u>1:</u>         |               |                                         |                  |          |       |

|               | The SRR bit r             | must be set to '  | 1'.           |                                         |                  |          |       |

| bit 0         | IDE: Extende              | d Identifier bit  |               |                                         |                  |          |       |

|               | 1 = Message               | will transmit Ex  | tended Ident  | ifier                                   |                  |          |       |

|               | 0 = Message               | will transmit St  | andard Identi | fier                                    |                  |          |       |

|               |                           |                   |               |                                         |                  |          |       |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0             | U-0                                                                 | U-0            | U-0   | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

|-----------------|---------------------------------------------------------------------|----------------|-------|------------------------------------|-------|-------|-------|--|

| —               | —                                                                   | —              |       | EID17                              | EID16 | EID15 | EID14 |  |

| bit 15          |                                                                     |                |       |                                    |       |       | bit 8 |  |

|                 |                                                                     |                |       |                                    |       |       |       |  |

| R/W-x           | R/W-x                                                               | R/W-x          | R/W-x | R/W-x                              | R/W-x | R/W-x | R/W-x |  |

| EID13           | EID12                                                               | EID11          | EID10 | EID9                               | EID8  | EID7  | EID6  |  |

| bit 7           |                                                                     |                |       |                                    |       |       | bit 0 |  |

|                 |                                                                     |                |       |                                    |       |       |       |  |

| Legend:         |                                                                     |                |       |                                    |       |       |       |  |

| R = Readable    | bit                                                                 | W = Writable I | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

| -n = Value at P | /alue at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unkno |                |       | nown                               |       |       |       |  |

| L               |                                                                     |                |       |                                    |       |       |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-x         | R/W-x                     | R/W-x                | R/W-x         | R/W-x                                   | R/W-x            | R/W-x  | R/W-x |

|---------------|---------------------------|----------------------|---------------|-----------------------------------------|------------------|--------|-------|

| EID5          | EID4                      | EID3                 | EID2          | EID1                                    | EID0             | RTR    | RB1   |

| bit 15        |                           |                      |               |                                         |                  |        | bit 8 |

|               |                           |                      |               |                                         |                  |        |       |

| U-x           | U-x                       | U-x                  | R/W-x         | R/W-x                                   | R/W-x            | R/W-x  | R/W-x |

| —             | —                         | _                    | RB0           | DLC3                                    | DLC2             | DLC1   | DLC0  |

| bit 7         |                           |                      |               |                                         |                  |        | bit 0 |

| Lonondi       |                           |                      |               |                                         |                  |        |       |

| Legend:       | l. h.:.                   |                      | L.11          |                                         |                  | -l (O) |       |

| R = Readab    |                           | W = Writable         |               | •                                       | mented bit, read |        |       |

| -n = Value a  | t POR                     | '1' = Bit is set     |               | '0' = Bit is cleared x = Bit is unknown |                  |        | iown  |

|               |                           |                      |               |                                         |                  |        |       |

| bit 15-10     | EID<5:0>: E               | xtended Identifi     | er bits       |                                         |                  |        |       |

| bit 9         | RTR: Remot                | e Transmission       | Request bit   |                                         |                  |        |       |

|               | When IDE =                | 1:                   |               |                                         |                  |        |       |

|               | •                         | e will request re    | mote transmis | ssion                                   |                  |        |       |

|               | 0 = Normal n              | 0                    |               |                                         |                  |        |       |

|               | When IDE =<br>The RTR bit |                      |               |                                         |                  |        |       |

| <b>h</b> :+ 0 | RB1: Reserv               |                      |               |                                         |                  |        |       |

| bit 8         |                           |                      | or CAN proto  |                                         |                  |        |       |

|               |                           | et this bit to '0' p | •             | 0001.                                   |                  |        |       |

| bit 7-5       | •                         | nted: Read as '      | 0             |                                         |                  |        |       |

| bit 4         | RB0: Reserv               |                      | <b></b>       |                                         |                  |        |       |

|               | User must se              | et this bit to '0' p | per CAN proto | ocol.                                   |                  |        |       |

| hit 2 0       |                           | Jota Longth Co.      | da hita       |                                         |                  |        |       |

#### BUFFER 21-3: ECAN™ MESSAGE BUFFER WORD 2

bit 3-0 DLC<3:0>: Data Length Code bits

#### BUFFER 21-4: ECAN<sup>™</sup> MESSAGE BUFFER WORD 3

| R/W-x                              | R/W-x | R/W-x        | R/W-x | R/W-x                                   | R/W-x           | R/W-x    | R/W-x |  |

|------------------------------------|-------|--------------|-------|-----------------------------------------|-----------------|----------|-------|--|

|                                    |       |              | Ву    | /te 1                                   |                 |          |       |  |

| bit 15                             |       |              |       |                                         |                 |          | bit 8 |  |

| R/W-x                              | R/W-x | R/W-x        | R/W-x | R/W-x                                   | R/W-x           | R/W-x    | R/W-x |  |

|                                    |       |              | Ву    | rte 0                                   |                 |          |       |  |

| bit 7                              |       |              |       |                                         |                 |          | bit 0 |  |

| Legend:                            |       |              |       |                                         |                 |          |       |  |

| R = Readable                       | bit   | W = Writable | bit   | U = Unimplen                            | nented bit, rea | d as '0' |       |  |

| -n = Value at POR '1' = Bit is set |       |              |       | '0' = Bit is cleared x = Bit is unknown |                 |          |       |  |

bit 15-8 Byte 1<15:8>: ECAN Message Byte 1 bits

bit 7-0 Byte 0<7:0>: ECAN Message Byte 0 bits

# 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0   | U-0     | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0                  |

|---------|---------|---------|---------|-----|-----------------------|------------------------|------------------------|

| PTGEN   | —       | PTGSIDL | PTGTOGL | —   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS                |

| bit 15  |         |         |         |     |                       |                        | bit 8                  |

|         |         |         |         |     |                       |                        |                        |

| R/W-0   | HS-0    | U-0     | U-0     | U-0 | U-0                   | R/V                    | V-0                    |

| PTGSTRT | PTGWDTO | _       | _       | _   | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7 |

|-------|

|-------|

| Legend:           | HS = Hardware Settable bi | t                           |                    |

|-------------------|---------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  |    | PTGEN: Module Enable bit                                                                                                                                                                                                      |

|---------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |    | 1 = PTG module is enabled                                                                                                                                                                                                     |

|         |    | 0 = PTG module is disabled                                                                                                                                                                                                    |

| bit 14  |    | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 13  |    | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                            |

|         |    | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                       |

| bit 12  |    | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                      |

|         |    | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul> |

| bit 11  |    | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 10  |    | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                               |

|         |    | 1 = Triggers the PTG module                                                                                                                                                                                                   |

|         |    | 0 = No action (clearing this bit will have no effect)                                                                                                                                                                         |

| bit 9   |    | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                            |

|         |    | 1 = Enables Single-Step mode                                                                                                                                                                                                  |

|         |    | 0 = Disables Single-Step mode                                                                                                                                                                                                 |

| bit 8   |    | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                             |

|         |    | 1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their<br>corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)                                                                   |

|         |    | <ul> <li>Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written<br/>to those limit registers</li> </ul>                                                                                    |

| bit 7   |    | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                              |